ZL30406

OC-48 STM-16 SONET/SDH Clock Multiplier PLL

NOT RECOMMENDED FOR NEW DESIGNS

Overview

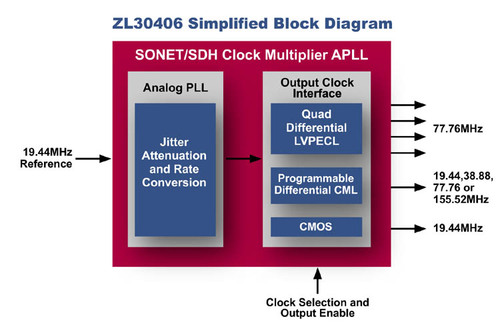

The ZL30406 is a SONET (synchronous optical network) and SDH (synchronous digital hierarchy) clock multiplier analog phase locked loop (APLL) providing six output clocks from a single device with jitter performance that surpasses OC-48 and STM-16 system requirements. The ZL30406 APLL accepts a single reference input at 19.44 MHz and generates ultra-low jitter clock outputs in compliance with ITU-T and Telcordia jitter generation requirements for SONET/SDH equipment. With multiple clocks supporting CMOS, CML and LVPECL outputs, the ZL30406 eliminates external circuitry to save cost, board space and design resource requirements.

Features & Benefits

- Ultra-low jitter generation of 0.46 ps rms surpasses world-wide system requirements

- Meets jitter requirements of Telcordia GR-253-CORE for OC-48, OC-12, OC-3, and OC-1 rates

- Meets jitter requirements of ITU-T G.813 for STM-16, STM-4 and STM-1 rates

- Enables glueless interface to SONET/SDH devices such as framers, mappers and SERDES

- Simultaneously generates up to three different output frequencies from a standard CMOS reference input at 19.44 MHz

- Multiple LVPECL output clocks at 77.76 MHz eliminate external circuitry

- Provides a CML differential clock programmable to 19.44, 38.88, 77.76 and 155.52 MHz

- Provides a single-ended CMOS clock at 19.44MHz

- Independent power down control of all output clocks optimizes power consumption

- 3.3 V supply

Resources

Documentation

Application Notes

- ZLAN-35 - SONET/SDH Linecard Solutions (ZL30406 & MT9046)

- ZLAN-34 - SONET/SDH Linecard Solutions (ZL30406 & MT90401)

Product Previews

Downloads, Firmware and Drivers

- IBIS Models:

- Zl30406

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |