MT90401

SONET/SDH System Synchronizer

NOT RECOMMENDED FOR NEW DESIGNS

Overview

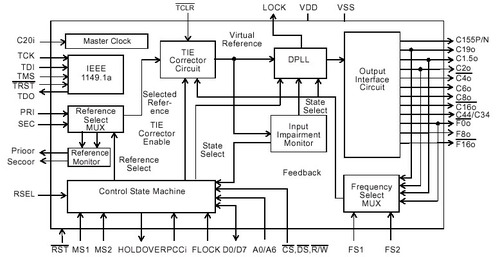

The MT90401 is a digital phase locked loop (DPLL) that is designed to synchronize SDH (Synchronous Digital Hierarchy) and SONET (Synchronous Optical Network) networking equipment. The MT90401 is used to ensure that the timing of outgoing signals remains within the limits specified by Telcordia, ANSI and the ITU during normal operation and in the presence of disturbances on the incoming synchronization signals. The MT90401 can operate in free-run, locked or holdover mode. The loop filter corner frequency can be selected to suit SONET applications or to suit SDH applications. The MT90401 uses an external 20 MHz oscillator as its master clock and it does not require external loop filter components.

Features & Benefits

- Meets requirements of Telcordia GR-253-CORE for SONET internal clocks and GR-1244 CORE for Stratum 3 clocks

- Meets requirements of ITU-T G.813 Option 1 and Option 2 for SDH Equipment Clocks (SEC)

- Provides OC-3/STM-1, DS3, E3, 19.44 MHz, DS2, E1, T1, 8 kHz and ST-BUS clock outputs

- Accepts two independent reference inputs

- Selectable 1.544 MHz, 2.048 MHz, 19.44 MHz or 8 kHz input reference frequencies

- Holdover accuracy of 0.02 ppm

- Output clock phase can be trimmed to support master-slave arrangements

- Hardware Mode, or optional Microport Mode with 8 bit microprocessor port access

- 3.3 V supply

- JTAG boundary scan

Resources

Documentation

Application Notes

- ZLAN-68 - List of Oscillators & Crystals that can be used with Microsemi's PLL, Digital Switches with Embedded PLL & Timing over Packet Devices

- ZLAN-71-Applications of the Digital PLLs Design Guidelines for Using Oscillators

Product Previews

Applications

Typical Applications

- SONET/SDH Add/Drop multiplexers

- SONET/SDH uplinks

- Integrated access devices

- ATM edge switches

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |