ZL30414

OC-192 STM-64 SONET/SDH Clock Multiplier PLL

NOT RECOMMENDED FOR NEW DESIGNS

Overview

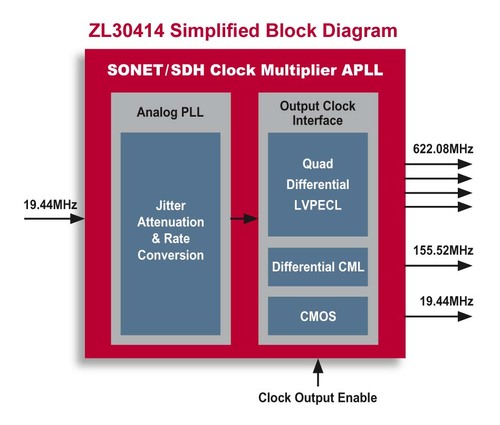

The ZL30414 is an analog phase-locked loop (APLL) designed to provide jitter attenuation and rate conversion for SDH (Synchronous Digital Hierarchy) and SONET (Synchronous Optical Network) networking equipment. The ZL30414 generates very low jitter clocks that meet the jitter requirements of Telcordia GR-253-CORE OC-192, OC-48, OC-12, OC-3 rates and ITU-T G.813 STM-64, STM-16, STM-4 and STM-1 rates. The ZL30414 accepts a CMOS compatible reference at 19.44 MHz and generates four LVPECL differential output clocks at 622.08 MHz, a CML differential clock at 155.52 MHz and a single-ended CMOS clock at 19.44 MHz. The output clocks can be individually enabled or disabled. The ZL30414 provides a LOCK indication.

Features & Benefits

- Meets jitter requirements of Telcordia GR-253-CORE for OC-192, OC-48, OC-12, and OC-3 rates

- Meets jitter requirements of ITU-T G.813 for STM-64, STM-16, STM-4 and STM-1 rates

- Provides four LVPECL differential output clocks at 622.08 MHz

- Provides a CML differential clock at 155.52 MHz

- Provides a single-ended CMOS clock at 19.44 MHz

- Lock Indicator

- Provides enable/disable control of output clocks

- Accepts a CMOS reference at 19.44 MHz

- 3.3 V supply

.

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |