MT9044

Dual Reference Frequency Selectable Digital PLL with Multiple Clock Outputs for T1/E1 (ITU-T G.812 type IV), Stratum (3, 4, 4E) and STS-3/OC3 Systems

NOT RECOMMENDED FOR NEW DESIGNS

Overview

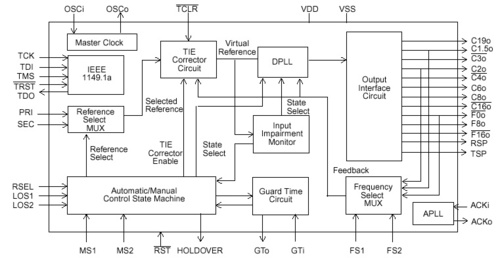

The MT9044 T1/E1/OC3 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization signals for multitrunk T1 and E1 primary rate transmission links and STS-3/0C3 links. The MT9044 generates ST-BUS clock and framing signals that are phase locked to either a 2.048 MHz, 1.544 MHz, or 8 kHz input reference. The MT9044 is compliant with AT&T TR62411 and Bellcore GR-1244-CORE Stratum 3, Stratum 4 Enhanced, and Stratum 4; and ETSI ETS 300 011; and ITU-T G.813 Option 1 for 2048 kbps interfaces. It will meet the jitter/wander tolerance, jitter/wander transfer, intrinsic jitter/wander, frequency accuracy, capture range, phase change slope, holdover frequency and MTIE requirements for these specifications.

Features & Benefits

- Supports AT&T TR62411 and Bellcore GR-1244-CORE Stratum 3, Stratum 4 Enhanced and Stratum 4 timing for DS1 interfaces

- Supports ITU-T G.813 Option 1 clocks for 2048 kbps interfaces

- Supports ITU-T G.812 Type IV clocks for 1,544 kbps interfaces and 2,048 kbps interfaces

- Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 timing for E1 interfaces

- Selectable 1.544 MHz, 2.048 MHz or 8 kHz input reference signals

- Provides 5 different 8 KHz framing pulses

- Holdover frequency accuracy of 0.05 PPM

- Holdover indication

- Attenuates wander from 1.9 Hz

- Provides Time Interval Error (TIE) correction

- Accepts reference inputs from two independent sources

- JTAG Boundary Scan

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |