ZL30101

T1/E1 Stratum 3 System Synchronizer

Overview

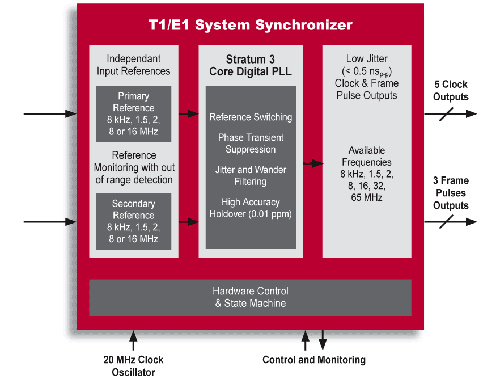

| The ZL30101 Stratum 3 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization for multi-trunk T1 and E1 transmission equipment. The ZL30101 generates ST-BUS and other TDM clock and framing signals that are phase locked to one of two input references. It helps ensure system reliability by monitoring its references for accuracy and stability and by maintaining stable output clocks during reference switching operations and during short periods when a reference is unavailable. The ZL30101 is intended to be the central timing and synchronization resource for network equipment that complies with Telcordia, ETSI, ITU-T and ANSI network specifications. |

Simplified Block Diagram

Typical Applications

- Synchronization and timing control for multi-trunk DS1/E1 systems such as DSLAMs, gateways and PBXs Clock and frame pulse source for ST-BUS, GCI and other time division multiplex (TDM) buses

Features & Benefits

- Supports Telcordia GR-1244-CORE Stratum 3

- Supports G.823 and G.824 for 2048 kbps and 1544 kbps interfaces

- Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces

- Simple hardware control interface

- Accepts two input references and synchronizes to any combination of 8 kHz, 1.544 MHz, 2.048 MHz, 8.192 MHz or 16.384 MHz inputs

- Provides a range of clock outputs: 1.544 MHz, 2.048 MHz, 16.384 MHz and either 4.096 MHz and 8.192 MHz or 32.768 MHz and 65.536 MHz

- Provides 5 styles of 8 kHz framing pulses

- Holdover frequency accuracy of 1 x 10-8

- Lock, Holdover and Out of Range indication

- Selectable loop filter bandwidth of 1.8 Hz or 922 Hz

- Less than 0.5 nspp jitter on all output clocks

- External master clock source: clock oscillator or crystal

Resources

Documentation

Application Notes

- ZLAN-68 - List of Oscillators & Crystals that can be used with Zarlink's PLL, Digital Switches with Embedded PLL & Timing over Packet Devices

- ZLAN-178 - Synchronizer Power Supply Decoupling and Layout Practices

Product Previews

Downloads, Firmware and Drivers

- BSDL Files:

- zl30101qdc.bsd

- IBIS Models:

- zl30101qdc.ibs

Applications

Typical Applications

- Synchronization and timing control for multi-trunk DS1/E1 systems such as DSLAMs, gateways and PBXs Clock and frame pulse source for ST-BUS, GCI and other time division multiplex (TDM) buses

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |

This category has no Parametric Data! please try other Categories

Ordering

TQFP-64(10x10) Clock / Timing - Application Specific ROHS

| Distributor | SKU | Stock | MOQ | Pkg | |

|---|---|---|---|---|---|

| Microchip Technology Inc. | .. | .. | .. | .. | Buy Now |

| DigiKey | ZL30101QDG1-ND | 160 | Tray | No Stock |