ASIC Design Services

Overview

|

|

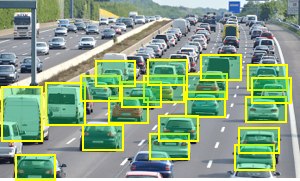

Virtual FenceASIC Design Services launches its PolarFire FPGA based Person Presence Detector and Virtual Fence application. The Virtual Fence application is accompanied with an intuitive GUI that enables easy set up and use. Take a look at the video on the right. Core Deep Learning (CDL) IP FrameworkThe Core Deep Learning (CDL) Framework allows your trained machine learning inference engine to be run in PolarFire FPGAs. |

|

|

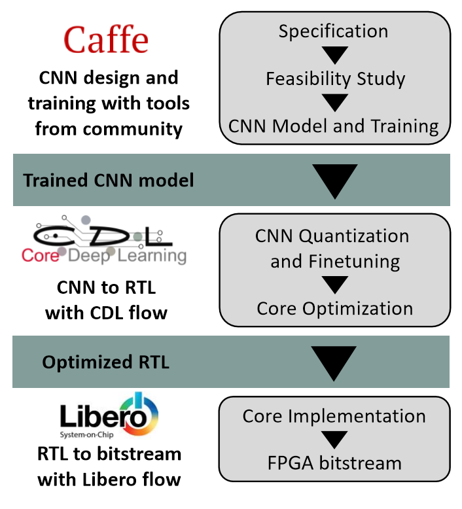

Core Deep Learning (CDL) from ASIC Design Services is a scalable and flexible Convolutional Neural Network (CNN) solution for PolarFire FPGAs. CDL accelerates a wide range of layers typically associated with Convoluted Neural Networks (CNNs). The configurable nature, small real estate, and low-power properties of PolarFire FPGAs allow for computationally expensive CNNs to be moved to the node. CDL is the product of a scalable framework that offers the opportunity to stipulate the desired performance, platform specifications, and resource constraints for an application and platform-specific optimized solution. CDL can fit into any FPGA design by scaling to unique customer requirements while supporting the following features:

|

|

Low Power Benchmarks using PolarFire FPGAs

| CNN | Lenet | Squeezenet | Pose | VGG | GVV (SVD) | Tiny-Yolo v2 |

| Network GOPS | 0.005 | 0.782 | 3.587 | 30.941 | 30.764 | 6.970 |

| Fabric 4LUT | 59469 | 78268 | 73000 | 85531 | 68484 | 59991 |

| Fabric DFF | 80968 | 84048 | 84782 | 96103 | 77554 | 76674 |

| uSRAM Blocks (64x12) | 1440 | 1024 | 1024 | 1008 | 1024 | 1024 |

| LSRAM Blocks (20k bit) | 126 | 578 | 578 | 550 | 434 | 306 |

| Total RAM (Mbits) | 3.52 | 12.04 | 12.04 | 11.48 | 9.23 | 6.73 |

| Math Blocks (18x18 MACC) | 720 | 512 | 512 | 504 | 512 | 512 |

| FPS | 2747.25 | 155.02 | 23.14 | 5.67 | 8.51 | 39.47 |

| Power (mW) | 3653.53 | 4522.60 | 4422.43 | 4181.42 | 3803.46 | 3456.16 |

| Performance (GOPs/s) | 12.60 | 121.19 | 82.79 | 175.43 | 261.80 | 275.11 |

| Power Efficiency (GOPs/s/W) | 3.45 | 26.80 | 18.72 | 41.96 | 68.83 | 79.60 |

| DSP Efficiency (GOPs/s/DSP) | 0.02 | 0.24 | 0.16 | 0.35 | 0.51 | 0.54 |

Check out our CNN demos with PolarFire FPGAs

| Tiny Yolo v2 Object Detection | Pose Estimation | Person Detection | |

| Demo |  |

|

|

| Supported Kit |  PolarFire Splash Kit PolarFire Splash Kit |

PolarFire Splash Kit PolarFire Splash Kit |

PolarFire Video Kit PolarFire Video Kit |

| Demo Files | Tiny Yolo v2 Programming File | CDL Pose Estimation MPF300-Splash-Kit | CDL Person Detection Reference Design MPF300-Video-Kit |

| Need help? | Request for more information | ||

The Core Deep Learning framework currently supports Caffe with plans to support TensorFlow. Download the Core Deep Learning Brochure from ASIC Design Services for more info.

Tested and Validated CNNs

| Network | Function |

| ResNet50 | Image Classification |

| VGG16 | Image Classification |

| SqueezeNet | Image Classification |

| Cifar10 | Image Classification |

| Tiny Yolov2 | Object Detection |

| LeNet5 | Digit Classification |

| OpenPose | Pose Estimation |

| Origami | Scene Labelling |

| CNNGestureRecognizer | Hand Gesture Recognition |

About ASIC Design Services

ASIC Design Services is a private company based in Midrand, South Africa. The company is a design house for ASIC, FPGA and ASSP devices and staffs a high proportion of design engineers. ASIC Design Services is also the South African distributor for Microsemi Corporation and Siemens Corporation. Download the Core Deep Learning Brochure from ASIC Design Services for more info. ASIC Design Services uses search simulation algorithms to provide optimal solutions on a per-implementation basis. For information about pricing and licensing CDL, please contact ASIC Design Services directly.

ASIC Design Services uses search simulation algorithms to provide optimal solutions on a per-implementation basis. For information about pricing and licensing CDL, please contact ASIC Design Services directly.

Standard Deliverables

- Microsemi target specific encrypted, or RTL source code

- Complete documentation

Contact Information

For additional information, contact ASIC Design Services at:|

ASIC Design Services |

Postal address (for mail):P.O. Box 5485 Midrand 1685 South Africa |

Note: CompanionCores are Semiconductor Intellectual Property cores provided by Microsemi's strategic IP partners that are targeted for use in Microsemi programmable logic devices and that meet Microsemi's rigorous technical and sales standards. Such core verification includes ensuring seamless implementation through Microsemi's suite of internal and third-party EDA development tools and the availability of accurate and complete technical documentation.