ZL30771,ZL30772,ZL30773

IEEE 1588 & Synchronous Ethernet Packet Clock Network Synchronizers

Overview

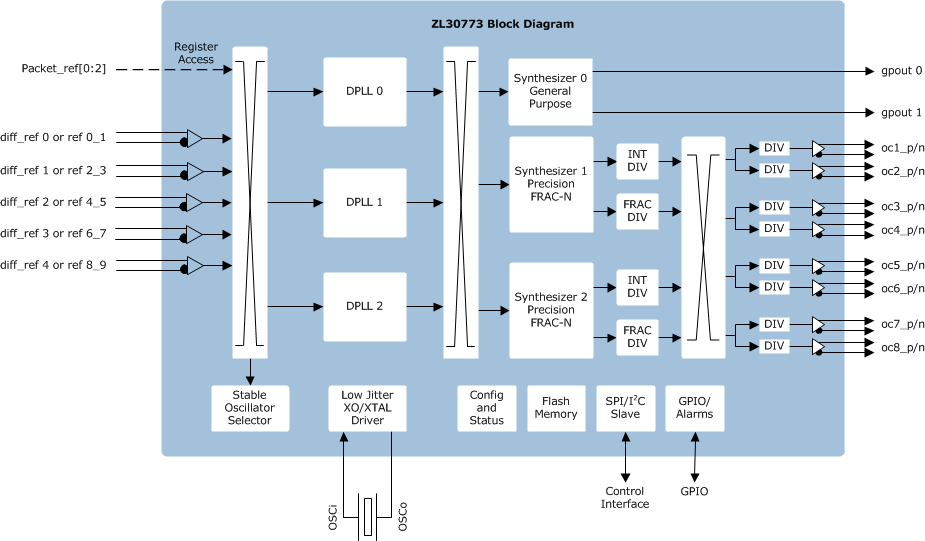

The ZL30771, ZL30772, and ZL30773 offer one to three independent timing channels of a combined hardware and software platform including IEEE 1588-2008 Precision Time Protocol Stack and Synchronization Algorithms. Using Microsemi’s miTimePLL timing technology, these devices offer new and improved features for 5G transport and wireless infrastructure equipment. These devices are ideal for timing card applications in systems that need to support 10G/40G and 100G Phys.

Key Features

- Up to three independent DPLL channels

- Precise phase/frequency measurement and tuning lower system latency to meet 4G LTE, 5G & Wireless Infrastructure

- Ultra-fast lock to GPS/GNSS and 1PPS for faster power-up time for 4G LTE, 5G & Wireless Infrastructure

- Precise chip-to-chip time interfaces use less backplane traces for 1PPS distribution for chassis systems

- Split oscillator option lowers cost, lowers jitter, and provides redundancy

- SyncE assist for high-accuracy IEEE 1588 provide lower cost end applications to assist IEEE1588 for time

- Sophisticated packet clock recovery algorithms are field proven and most widely deployed by Carriers

- Fully compliant to EEC (G.8262), SEC (G.813), GR-253 SMC and GR-1244 Stratum 3/3E

- Excellent jitter performance of <300 fs RMS in the 12 kHz to 20 MHz band meets jitter requirements for 10G/40G and 100G PHYs

- Two programmable ultra-low jitter synthesizers generate any frequency from 0.5 Hz to 1045 MHz

- One programmable general purpose synthesizer generates any clock from 0.5 Hz to 180 MHz

- 8 differential or 16 single ended ultra-low jitter outputs plus two general purpose CMOS outputs

- Programmable output advancement/delay to accommodate trace delays or compensate for system routing paths

- Up to three programmable digital PLLs/NCOs with loop bandwidth from 0.1 mHz to 470 Hz synchronize to any clock rate from 0.5 Hz to 900 MHz

- Accepts up to 10 differential or 10 single ended input references

- Full reference monitoring of electrical failures

- Automatic hitless reference switching and digital holdover on reference fail with initial holdover accuracy better than 0.1 ppb

- Any input reference can be fed with clock, sync (frame pulse), clock /sync pair or clock modulated with sync pulse (embedded PPS ePPS and embedded PP2S ePP2S)

- Easy Configuration and dynamic programming via SPI/I2C interface

- Factory programming available

- Operates from a single crystal resonator or clock oscillator

Resources

Applications

Applications/Uses

- Central timing function for carrier network equipment compliant to ITU-T G.8262, G.8273.2, G.8273.4

- Communications systems timed by any combination of Synchronous Ethernet, IEEE 1588 PTP, or GPS/GNSS

- 5G wireless CU, DU, and RU systems

- 5G systems with precise time requirements driven by advanced services such as carrier aggregation, coordinated multipoint, OTDOA location, etc.

- Integrated basestation reference clock for 2G through 4G LTE-A macro and micro cells

- Carrier routers, access aggregation, wireless backhaul

- SONET/SDH systems

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |