ZL30721

Single Channel IEEE 1588 and SyncE Network Synchronizer

Overview

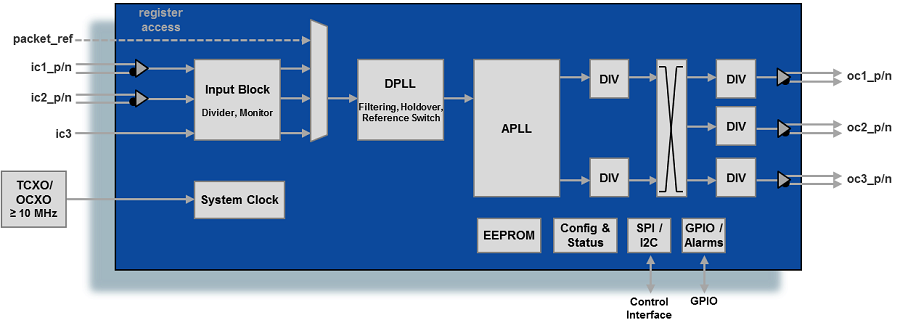

The ZL30721 is a combined hardware and software platform including IEEE 1588TM-2008 Precision Time Protocol Stack, Synchronization Algorithm and Microsemi's integrated System Synchronizer Clock Generation hardware. The device combines a DPLL/NCO with an ultra-low jitter APLL, three fully programmable inputs and outputs to provide a compact Synchronous Ethernet / 1588 timing solution.

Key Features

- Single High Quality DPLL Channel

- Packet Network Frequency and Phase Sync

- Frequency accuracy for GSM, WCDMA-FDD, LTE-FDD base stations and small cells

- Frequency performance for ITU-T G.823 and G.824 synchronization interface, G.8261 PNT, PEC and CES interfaces and G.8263 PEC-S-F

- Phase synchronization performance for WCDMA-TDD, TD-SCDMA, CDMA2000, LTE-TDD and LTE-A applications

- Client holdover and reference switching between multiple servers

- Support for new ITU-T packet clock, drafts or recs: G.8263 PEC, G.8273.2 T-BC & T-TSC w/o SyncE and G.8273.4 T-BC-P, T-TSC-P

- Hybrid Mode for mixing SyncE and IEEE 1588

- Physical Layer Clock Synchronization

- ITU-T G.8262 SyncE EEC options 1 and 2

- Low-Bandwidth DPLL

- Low-jitter operation from any ≥10MHz TCXO

- Master clock jitter attenuator reduces cost by removing TCXO/OCXO low-jitter requirement

- Hitless reference switching

- High-resolution holdover averaging

- Numerically controlled oscillator mode

- Input Clocks

- Up to 3 inputs, 2 differential/CMOS, 1 CMOS

- Any input frequency from 8kHz to 1250MHz (8kHz to 300MHz for CMOS)

- Per-input activity and frequency monitoring

- Low-jitter Fractional-N APLL and 3 Outputs

- Any output frequency from <1Hz to 1035MHz

- High-resolution fractional frequency conversion with 0ppm error

- Encapsulated design requires no external VCXO or loop filter components

- Output jitter as low as 0.25ps RMS (12kHz-20MHz integration band)

- Outputs are CML or 2xCMOS, can interface to LVDS, LVPECL, HSTL, SSTL and HCSL

- Per-output supply pin with CMOS output voltages from 1.5V to 3.3V

- Precise output alignment circuitry and per-output phase adjustment

- Per-output enable/disable and glitchless start/stop (stop high or low)

- General Features

- Automatic self-configuration at power-up from internal EEPROM; up to four configurations

- Input-to-output alignment with external feedback

- SPI/I2C processor interface

- Easy-to-use evaluation software

- 64 pin 5 x 10mm LGA package

Resources

Applications

- ITU-T G.8262 system timing cards for Synchronous Ethernet systems

- System timing cards which support ITU-T G.781 SETS (SDH Equipment Timing Source)

- Integrated base station reference synchronization for air interfaces for

- GSM, WCDMA, TD-SCDMA, LTE and LTE-A

- FDD or TDD mobile technology

- Femtocells, small cells (residential, urban, rural, enterprise), picocells and macrocells

- Mobile backhaul NID, cell-site router, edge switch/router, microwave or access aggregation node

- EPON/GPON OLT and ONU/ONT

- DSLAM and RT-DSLAM

- 10G, 40G and 100G line cards

- SONET/SDH, Fibre channel, XAUI

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |