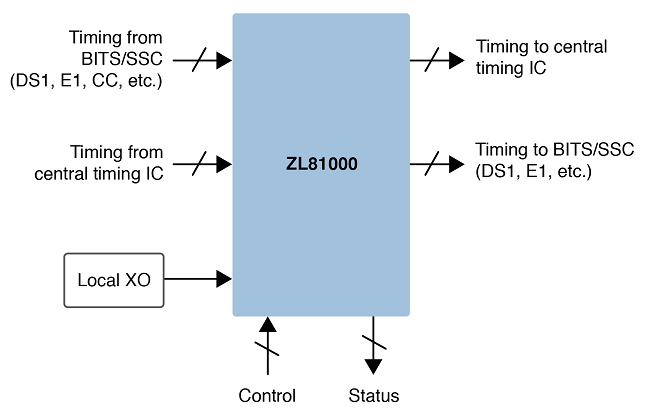

ZL81000

Dual BITS Transceiver and CC Receiver

Overview

ZL81000 provides two DS1/E1/2048kHz transceivers (transmitters plus receivers) specifically designed for BITS/SSU timing in carrier-class telecommunications equipment. Each transceiver provides full support for DS1, E1 and G.703 2048kHz synchronization signals in and out and includes SSM message insertion and extraction. The device also includes two composite clock (CC) receivers and two general-purpose CMOS clock inputs to provide additional support as needed for legacy interfaces.

Applications/Uses

- SONET/SDH ADMs, MSPPs, and MSSPs

- Digital Cross-Connects

- Service Provider Routers

- Any carrier-grade telecom equipment with DS1, E1, 2048kHz or CC external timing interfaces

Key Features

-

Two Independent Multi-Protocol BITS/SSU Transmitters and Receivers

• Receive and transmit DS1, E1, 2048 kHz, and 6312 kHz timing signals

• Insert and extract SSM messages (DS1, E1)

• DS1 SF or ESF formats

• E1 FAS, CAS and/or CRC-4 framing

• J1 support (DS1 with Japanese CRC-6 & RAI)

• Short-haul and long-haul line interfaces

• Internal software-selectable termination (75Ω, 100Ω, 110Ω, or 120Ω) or external termination

• High-impedance receive inputs and transmit outputs for no-relay redundancy

• Local and remote loopbacks

• Jitter attenuator with configurable buffer depth, can be inserted into Tx path or Rx path

• Receiver automatic receive sensitivity adjustment and signal level indication

• Receiver LOS, OOF, RAI and AIS status

• Transmitter flexible waveform generation

• Transmitter DSX-1 line build-outs

• Transmitter E1 waveforms include G.703 waveshapes for both 75Ω coax and 120Ω twisted pair cables

• Transmitter AIS and alternating ones and zeros generation

• Transmitter and receiver power-down controls

• Transmitter and receiver short-circuit detection

• Transmitter open-circuit detection

▪ Internal loopbacks between transmitter and receiver for fault detection -

Two Composite Clock Receivers

• Compliant with Telcordia GR-378 composite clock, G.703 centralized clock, and G.703 Appendix II.1) Japanese sync interfaces

• Configurable for 50% or 5/8 duty cycle, 1V or 3V pulse amplitude, and 110Ω/120Ω/133Ω termination

• Monitored for LOS, AMI violations, presence or absence of 8 kHz component, and optionally the Japanese 400 Hz component

• Followed by DPLL+APLL for jitter filtering and optional frequency conversion -

Two programmable-frequency inputs

-

Operates from a single 12.8MHz local oscillator

-

Processor interface: 8-bit Parallel or SPI serial

-

1.8V operation with 3.3V I/O (5V tolerant)

-

Industrial operating temperature range

- Similar feature set to DS26502 and DS26504 BITS Elements

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |