ZL30611,ZL30612,ZL30614

One, Two and Four Channel Clock Translator

Overview

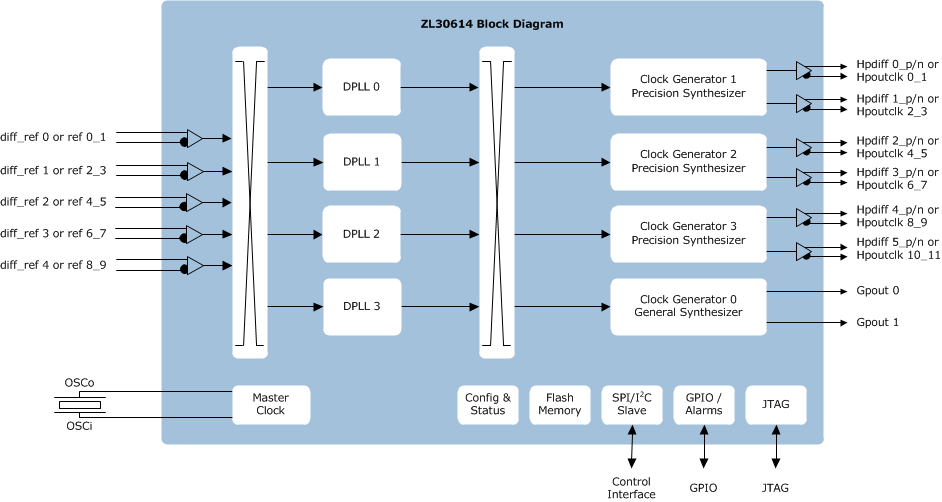

The ZL30611, ZL30612, and ZL30614 offer one, two, or four independent channels of Synchronous Ethernet (SyncE) clock translation. Fourth generation timing technology provides one third the jitter of the previous generation devices with a 40% smaller footprint. Excellent jitter performance makes these devices ideally suited for SyncE/Sonet/SDH timing and line card applications needing to support 10G/40G and 100G PHYs. Features supported include hitless reference switching between active and redundant timing cards, frequency translation from backplane clock to frequencies required by PHY devices, jitter filtering, and holdover in case both active and redundant timing cards fail.

Key Features

- Up to four independent clock channels

- Excellent jitter performance of 180 fs RMS in 12 kHz to 20 MHz band meets jitter requirements of 10G/40G and 100G PHYs

- Three programmable ultra-low jitter synthesizers generate any frequency from 0.5 Hz to 900 MHz

- One programmable general purpose synthesizer generates any clock from 0.5 Hz to 180 MHz

- 6 differential (CML) or 12 single ended (CMOS) ultra-low jitter outputs plus two general purpose CMOS outputs

- Accepts up to 10 LVPECL/LVDS/HCSL/LVCMOS inputs

- Any input reference can be fed with clock, sync (frame pulse), clock /sync pair or clock modulated with sync pulse (embedded PPS ePPS and embedded PP2S ePP2S)

- Up to four programmable digital PLLs/NCOs with loop bandwidth from 14 Hz to 470 Hz synchronize to any clock rate from 1 kHz to 900 MHz and to clock plus sync pulse

- Automatic hitless reference switching and digital holdover on reference fail with initial holdover accuracy better than 1 ppb with post holdover filter

- Easy Configuration and dynamic programming via SPI/I2C interface

- Operates from a single crystal resonator or clock oscillator

Resources

| Datasheet | ZL30611_612_614 Short Form Datasheet ZL30611_612_614 Full Datasheet |

|---|---|

| Application Notes | ZLAN-442 Crystals and Oscillators for Next Generation Timing Solutions ZLAN-517 ZL3070X/60X/61X/174 Power Supply Decoupling and Layout Guidelines ZLAN-527 Assembly and PCB Layout Guidelines for Dual Row aQFN100 Package ZLAN-600 ZL3060x, ZL3061x, ZL3070x, and ZL30174 Cycle to Cycle Jitter |

| Firmware and Drivers | |

| Software URLS | ZLS3061X GUI Software |

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |