ZL30623

Dual Channel Ultra Low Jitter Network Synchronizer

Overview

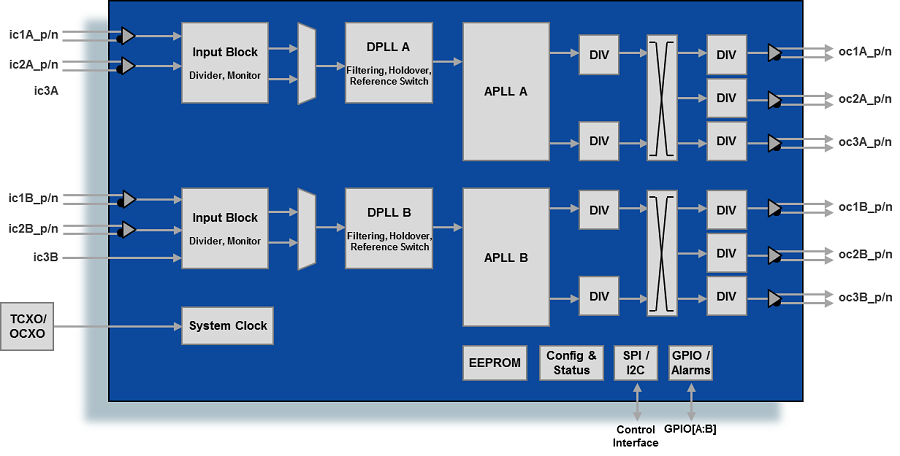

The ZL30623 is a fully compliant SEC (G.813) and EEC (G.8262) dual channel Network Synchronizer with ultra-low jitter performance of 250fs RMS. The device accepts up to 6 input references and generates up to 6 differential or 12 single-ended CMOS output clocks . Dual, independent, digital phase locked loops (DPLLs) have programmable loop bandwidths from 0.1Hz to 500Hz and provide G.8262 compliance including hitless reference switching, holdover and jitter filtering. Dual, independent fractional-N analog PLLs (APLLs) generate ultra-low jitter output clocks programmable to any frequency between <1Hz to 1035MHz.

Key Features

- Two Independent Channels

- Input Clocks (Per Channel)

- Three inputs, two differential/CMOS, one CMOS

- Any input frequency from 8kHz to 1250MHz (8kHz to 300MHz for CMOS)

- Per input activity and frequency monitoring

- Automatic or manual reference switching

- Low-Bandwidth DPLL (Per Channel)

- ITU-T G.813/G.8262 compliance (options 1 & 2)

- Low- jitter operation from any ≥10MHz TCXO

- Master clock jitter attenuator reduces cost by removing TCXO/OCXO low-jitter requirement

- Programmable bandwidth, 0.1Hz to 10Hz

- Attenuates jitter up to several UI

- Hitless Reference Switching

- High-resolution holdover averaging

- Digitally controlled phase adjustment

- Low-Jitter Fractional-N APLL and 3 Outputs (Per Channel)

- Any output frequency from <1Hz to 1035MHz

- High resolution fractional frequency conversion with 0ppm error

- Encapsulated design requires no external VCXO or loop filter components

- Each output has independent dividers

- Output jitter as low as 0.25ps RMS (12kHz - 20MHz integration band)

- Each output is CML or 2 x CMOS, can interface to LVDS, LVPECL, HSTL, SSTL and HCSL

- In 2 x CMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz)

- Per-output supply pin with CMOS output voltages from 1.5V to 3.3V

- Precise output alignment circuitry and per-output phase adjustment

- Per-output enable/disable and glitchless start/stop (stop high or low)

- General Features

- Automatics self-configuration at power-up from internal EEPROM; up to four pin selectable configurations

- Numerically controlled oscillator mode

- Input-to-output phase alignment with external feedback

- SPI or I2C processor interface

- Easy-to-use evaluation software

- 64 pin 5 x 10mm LGA package

Resources

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |