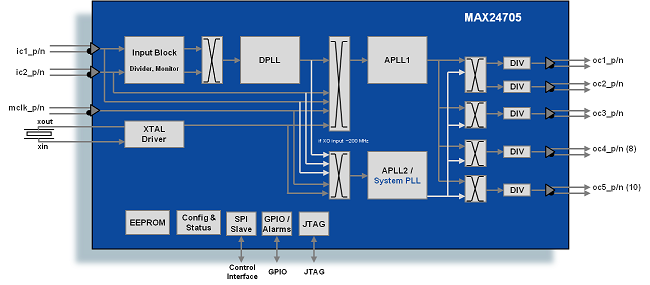

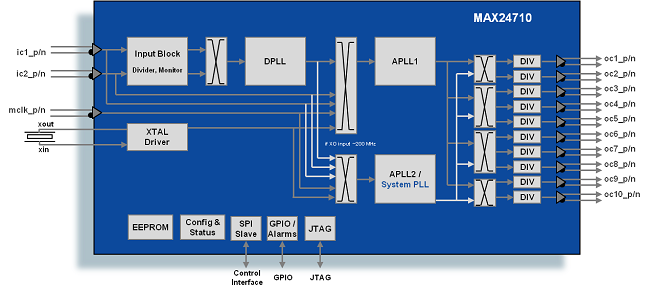

MAX24705,MAX24710

5- or 10-Output Any-Rate Line Card Timing ICs with Internal EEPROM

Overview

The MAX24705 and MAX24710 are flexible, high-performance timing and clock synthesizer ICs that include a DPLL and two independent APLLs. When locked to one of two input clock signals, the device performs any-to-any frequency conversion. From any input clock frequency 2kHz to 750MHz the device can produce frequency-locked APLL output frequencies up to 750MHz and as many as 10 differential (20 CMOS) output clock signals that are integer divisors of the APLL frequencies. Input jitter can be attenuated by an internal low-bandwidth DPLL. The DPLL also provides truly hitless switching between input clocks and a high-resolution holdover capability. Input switching can be manual or automatic. Using only a low-cost crystal or oscillator, the devices can also serve as frequency synthesizer ICs. Output jitter is typically 0.18 to 0.3ps RMS for an APLL-only integer multiply and .25 to 0.4ps RMS for APLL-only fractional multiply or DPLL+APLL operation.

For telecom systems, the device has all required features and functions to serve as a line card timing IC.

Applications/Uses

- Frequency Conversion and Synthesis Applications in a Wide Variety of Equipment Types

- Telecom Line Cards for SONET/SDH, Synchronous Ethernet and Similar Applications

Key Features

- Input Clocks

- One Crystal Input

- Two Differential or CMOS/TTL Inputs

- Differential to 750MHz, CMOS/TTL to 125MHz

- Continuous Input Clock Quality Monitoring

- Automatic or Manual Clock Selection

- Hitless Reference Switching on Loss of Input

- Low-Bandwidth DPLL

- All Features Needed for SyncE or OTN Line Card Timing IC

- Programmable Bandwidth, 4Hz to 400Hz

- Attenuates Jitter up to Several UI

- Free-Run or Holdover on Loss of All Inputs

- Hitless Reference Switching on Loss of Input

- Manual Phase Adjustment

- Two APLLs Plus 5 or 10 Output Clocks

- APLLs Perform High Resolution Fractional-N Clock Multiplication

- Any Output Frequency from <1Hz to 750MHz

- Each Output Has an Independent Divider

- Output Jitter Typically 0.18 to 0.3ps RMS for APLL-only Integer Multiply and 0.25 to 0.4ps RMS for Other Modes (12kHz to 20MHz)

- Outputs are CML or 2xCMOS, Can Interface to LVDS, LVPECL, CMOS, HSTL, SSTL and HCSL

- CMOS Output Voltage from 1.5V to 3.3V

- General Features

- Suitable Line Card IC for Stratum 2/3E/3/4E/4, SMC, SEC/EEC, or SSU

- Automatic Self-Configuration at Power-Up from Internal EEPROM Memory

- Uses External Crystal, Oscillator or Clock Signal As Master Clock

- Internal Compensation for Local Oscillator Frequency Error

- SPI Processor Interface

- 1.8V + 3.3V Operation (5V Tolerant)

- -40 to +85°C Operating Temp. Range

- 10mm x 10mm CSBGA Package

Key Specifications:

| Part Number | Indep. DPLLs | Input Clocks | Differential Input Clocks | Differential Output Clocks | CMOS Output Clocks | Input Frequency Range | Output Frequency Range | DPLL BW (Hz) | |

|---|---|---|---|---|---|---|---|---|---|

| min | max | ||||||||

| MAX24705 | 1 | 4 | 3 | up to 5 | up to 10 | 2kHz-750MHz | <1Hz-750MHz | 4 | 400 |

| MAX24710 | 1 | 4 | 3 | up to 10 | up to 20 | 2kHz-750MHz | <1Hz-750MHz | 4 | 400 |

Resources

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |