ZL30162

Quad Channel Network Synchronization Clock Translator

Overview

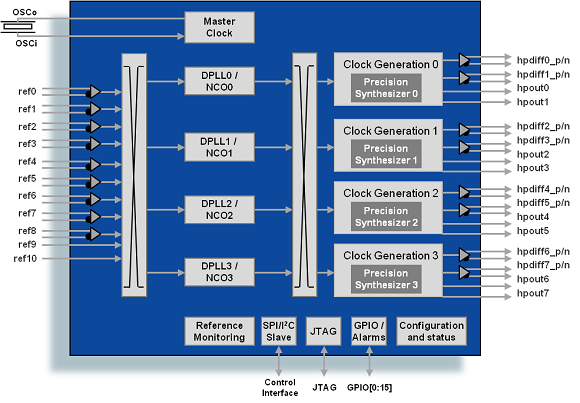

The ZL30162 is Microsemi's most integrated timing card device combining four programmable DPLLs / NCOs with four programmable synthesizers. The deivce is a fully compliant SEC (G.813) and EEC (G.8262) flexible rate conversion DPLL. It is capable of accepting or generating any frequency from 1Hz to 750MHz on up to eleven input references and up to sixteen output clocks.

Key Features

- Fully compliant SEC (G.813) and EEC (G.8262) flexible rate conversion Digital Phase Locked Loop (DPLL)

- Four independent, programmable DPLLs/Numerically Controlled Oscillators (NCOs) synchronize to any clock rate from 1 Hz to 750 MHz

- Four programmable synthesizers generate any clock rate from 1 Hz to 750 MHz with maximum jitter below 0.61 ps rms

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- Digital PLLs filter jitter 0.1 mHz up to 1 kHz

- Programmable DPLLs can synchronize to sync pulse and sync pulse/clock pair

- Automatic hitless reference switching and digital holdover on reference fail

- Reference inputs:

- Nine reference inputs configurable as single ended or differential

- Two additional single ended reference inputs

- Any Output Frequency:

- Eight LVPECL output clocks

- Eight LVCMOS output clocks

- Up to four unique customer defined default configurations, including input/output frequencies, are available via OTP (One Time Programmable) memory

- Easy Configuration and dynamic programming via SPI/I2C interface

- Operates from a single crystal resonator or clock oscillator

Resources

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |

Ordering

| Distributor | SKU | Stock | MOQ | Pkg | |

|---|---|---|---|---|---|

| Arrow Electronics | ZL30162GDG2 | 50 | 1 | .. | Buy Now |

| DigiKey | ZL30162GDG2-ND | .. | Tray | No Stock |