ZL30166

Triple Channel Precision Clock Translator with Frame Sync Capability

Overview

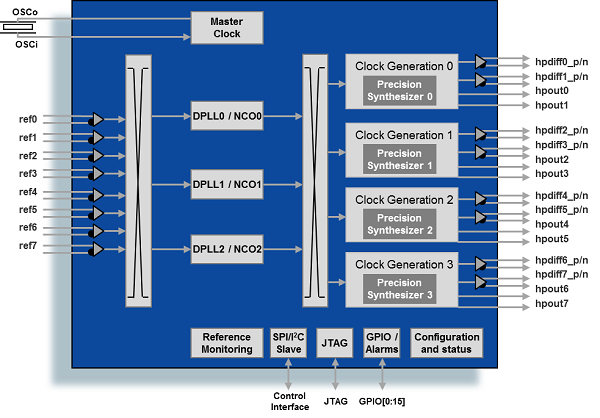

The ZL30166 is a triple channel Clock Translator combining three programmable DPLLs / NCOs with four programmable precision synthesizers. Each channel accepts any frequency from 1kHz to 750MHz and generates any frequency from 1Hz to 750MHz to support any communication service over optical networks. For applications that require synchronizing to a 1PPS input, the ZL30166 supports a sync pulse/clock pair feature. Any of the inputs can be used for a 1PPS signal shared with any other input for a reference frequency. The output will be synchronized to the input reference and will be phase aligned to the 1PPS input. This unique feature allows a line card with a crystal to be used for synchronizing to a 1PPS input. This normally requires a PLL with a 30mHz bandwidth and TCXO. With very low power consumption, the ZL30166 operates from a single crystal resonator or clock oscillator supporting eight input references configurable as single ended or differential. It provides eight high performance LVPECL outputs and eight high performance LVCMOS outputs.

Applications/Uses

- OTN muxponders and transponders

- 10 Gigabit Line cards

- Synchronous Ethernet, 10 GBASE-R and 10 GBASE-W

- SONET/SDH, Fibre channel, XAUI

Key Features

- Three Independent clock channels

- Three programmable digital PLLs/Numerically Controlled Oscillators (NCOs)

- Programmable synthesizers generate any clock rate from 1 Hz to 750 MHz

- Programmable digital PLLs synchronizes to any clock rate from 1 kHz to 750 MHz

- Any input reference can be fed with sync (frame pulse) or clock

- Programmable DPLLs can synchronize to sync pulse and sync pulse/clock pair

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC

- Digital PLLs filter jitter at 5 Hz, 14 Hz, 28 Hz, 56 Hz, 112 Hz, 224 Hz, 448 Hz or 896 Hz

- Automatic hitless reference switching and digital holdover on reference fail

- Reference input:

- Eight reference inputs configurable as single ended or differential

- LVCMOS (1kHz to 177.5 MHz)

- LVDS or LVPECL (1kHz to 750MHz)

- Any Output Frequency:

- configurable for LVDS, LVPECL, LVCMOS

- Frequency Range: 1 Hz – 750 MHz

- Dynamic Frequency programming

- Easy Configuration: field programmable via SPI/I2C interface

- Modes of Operation:

- Integer, Fractions or Ratio (FEC support)

- Each clock channel can work as either PLL or NCO

- Reduces BOM Cost and Board Space:

- Replaces three devices with single channel PLLs

- Package: 13 x 13mm

- Low Power: < 2W

- Increases Design efficiency:

- Easy programming: SPI/I2C

- Up to four unique customer defined default configurations, including input/output frequencies, are available via OTP (One Time Programmable) memory

Resources

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |

Ordering

| Distributor | SKU | Stock | MOQ | Pkg | |

|---|---|---|---|---|---|

| Microchip Technology Inc. | .. | .. | .. | .. | Buy Now |

| DigiKey | ZL30166GDG2-ND | 160 | Tray | No Stock |