High Speed Serial Interface

Overview

Microsemi provides comprehensive high-speed serial interface solutions comprised of configurable functional blocks, IPs and reference designs. The solution is ideal for developing high performance low power applications across verticals from communications and consumer electronics to mission critical applications in commercial aviation.

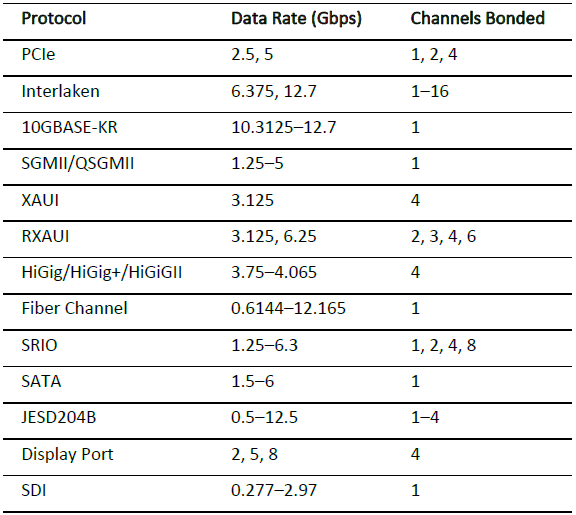

Many Microsemi FPGA families include transceivers SmartFusion2 Soc FPGAs, IGLOO2, RTG4 and PolarFire FPGAs, each with slightly different capabilities and protocols. Please refer to individual documentation for details. The high-speed serial interface blocks, integrate several functional blocks to support multiple high speed serial protocols like PCIe, Gbe, XAUI and JESD204B.

PolarFire FPGAs

All PolarFire FPGAs contain state-of-the-art low-power transceiver lane capabilities from speeds as low as 250 Mbps up to 12.7 Gbps. The PMA is designed to support multiple protocols (as listed in the following table) with state-of-the-art control and debug features. PCI Express Gen1 or Gen2 support is provided by a hard macro. All other protocols are implemented with a soft IP. Serial Gigabit Ethernet is also supported with GPIO 3.3 V LVDS differential pairs.

SmartFusion2 SoC FPGAs

Demo guides, tutorials and reference designs are updated with each software revision and can all be found on the SmartFusion2 SoC FPGAs - Documents page, select High Speed Serial Interface from the Document feature list to see the full list of documents.

IGLOO2 FPGAs

Demo guides, tutorials and reference designs are updated with each software revision and can all be found on the IGLOO2 FPGAs - Documents page, select High Speed Serial Interface from the Document feature list to see the full list of documents.

RTG4 FPGAs

Demo guides, tutorials and reference designs are updated with each software revision and can all be found on the RTG4 FPGAs

PCI Express

Microsemi offers implementation of PCIe protocol using the transceivers available in the PolarFire, RTG4, SmartFusion2 or IGLOO2 device families. Microsemi also provides user guides, reference designs, application notes and tools to increase productivity and reduce user development time.

PolarFire PCI Express Features

Each PolarFire FPGA integrates two low-power built-in PCIe Gen2 controllers, allowing seamless and easy connectivity to one or more host processors. Details are provided in PolarFire FPGA documentation. The following are PCIe features:

- ×1, ×2, and ×4 lane support

- Suitable for root port, native endpoint

- PCI Express base specification revision 2.0 and 1.1 compliant

- AXI4 master and slave interfaces to the FPGA fabric

- Single function capability

- Advanced error reporting (AER) support

- Integrated clock domain crossing (CDC) to support user-selected AXI4 frequency

- Lane reversal support

- Legacy PCI power management support

- Native active state power management L0s and L1 state support

- Power management event (PME message)

- MSI and legacy INT message support

- Latency tolerance reporting (LTR)

- L1 PM sub-states with CLKREQ

- Address translation tables between the PCIe and AXI4 domains

SmartFusion2 and IGLOO2 PCIe Features

The SmartFusion2 and IGLOO2 transceivers provide full support for PCI Express Gen 2.0. Details are provided in SmartFusion2 Documents and IGLOO2 Documents. Features include:

- Gen1/Gen2 rates at x1, x2 and x4 links

- Endpoint Topology

- Single-Function/Single-VC

- Receiver and Transmit buffers support error correction and coding (ECC)

- Fabric Interface options of AXI3 Master/Slave or AHB32 Master/Slave

- Address translation window support between PCIe and local device address space

PCI-SIG Compliance

Multiple solutions from Microsemi solutions have passed PCI-SIG compliance suites. Please refer to the integrators list to view Microsemi PCI Solutions

JESD204B

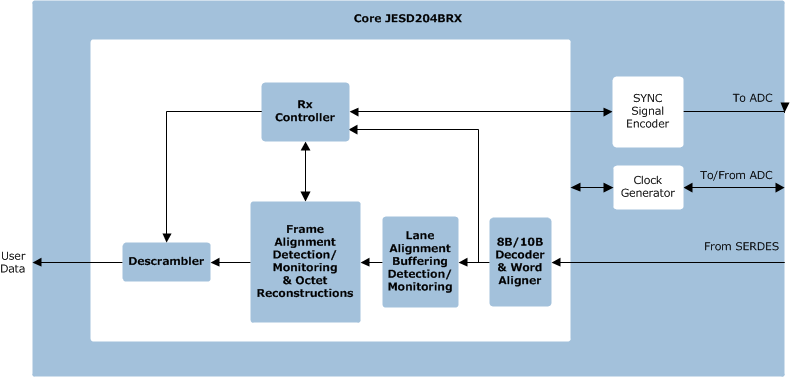

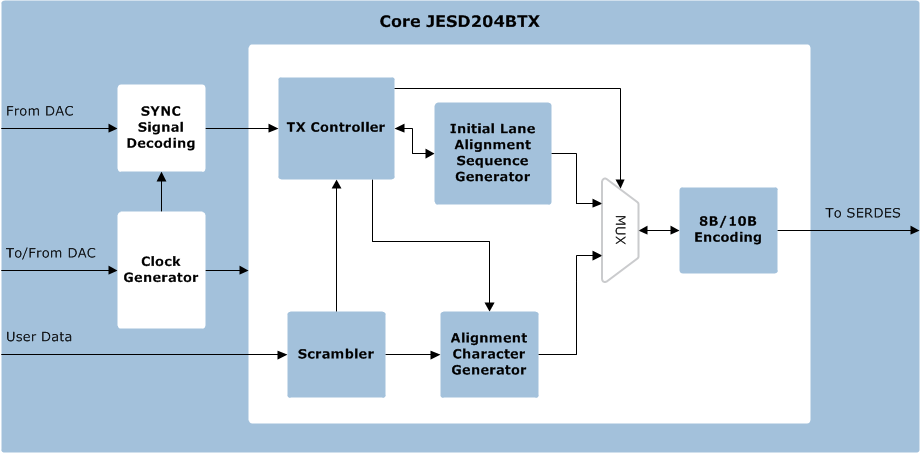

Microsemi provides a complete solution for implementing the JEDEC JESD204B serial interface standard. This specification describes a high speed serial for data converters.The CoreJESD204BTX (Transmitter) can be used to interface to DAC devices transmitting digital data to be converted to analog signals and CoreJESD204BRX (Receiver) can be used to interface to ADC devices receiving digital data which can be sampled by the ADC.

Both CoreJESD204BTX and CoreJESD204BRX IP cores support data rates from 250Mbps to 12.5Gbps Gbps for link widths of x1 to x8. The cores can be reconfigured through the APB interface to allow EPCS mode to achieve a higher data rates.

Key Features

- Enables interfacing of JESD204B compliant ADC/DAC converters with SmartFusion2, and IGLOO2 devices

- Supports 1, 2 or 4 lanes

- Supports JESD204B subclasses 0, 1 and 2

- Performs word alignment and 8B/10B decoding and encoding

- Recovers link configuration parameters and sources it with user-selected parameter values during initial lane synchronization sequence

- Lane alignment sequence generation, buffering, monitoring and correction

- Performs user-enabled frame alignment, monitoring, and correction

- Performs octet reconstruction, user-enabled descrambling/scrambling, alignment character generation and error detection

JESD204B IP Cores

| Name | Function | Device | Resources |

| CoreJESD204BRX |

Bus Interfaces | PolarFire IGLOO2 SmartFusion2 |

|

| CoreJESD204BTX |

Bus Interfaces | PolarFire IGLOO2 SmartFusion2 |

Interoperability Test Report

- TR0036: PolarFire FPGA CoreJESD204BRX Interoperability for ADS54J60 Test Report

- TR0035: PolarFire FPGA CoreJESD204BRX and CoreJESD204BTX Interoperability for AD9680 and AD9144 Test Report

- TR0034: PolarFire FPGA CoreJESD204BRX Interoperability for AD9680 Test Report

- TR0033: PolarFire FPGA JESD204B Interoperability for AD9371 Test Report

- TR0022: SmartFusion2 and IGLOO2 CoreJESD204BRX and CoreJESD204BTX Interoperability Test Report

- TR0030: RTG4 FPGA CoreJESD204BRX Interoperability Test Report

Ethernet

Ethernet, specified by IEEE 802.3 and ranging in data rates from 10Mbps up to 10Gbps is the most widely used wired networking standard across the verticals from computing to industrial.

Microsemi provides Ethernet solutions comprising of soft IP, hard IP blocks, hardware validated reference designs and demos which enable rapid development of Ethernet interfaces for high performance applications using our PolarFire FPGAs, SmartFusion2 SoC FPGAs and IGLOO2 FPGAs device families.

Microsemi PolarFire FPGA devices support Ethernet data transfer rates ranging from 10 Mbps to 10 Gbps on a single interface. PolarFire Ethernet solutions includes a complete range of solutions for implementing IEEE 802.3 standard-compliant Ethernet interfaces for chip-to-chip, board-to-board, and backplane interconnects. The high-speed serial interface and soft IP blocks available in PolarFire devices enable designers to build Ethernet solutions for use in embedded systems and systems connected over copper or optical cabling. Also, the PolarFire devices have an integrated CDR (clock data recovery) in every GPIO bank lane which provides clock and data recovery for 1GbE data transfer rates.

SmartFusion2 and IGLOO2 Ethernet Solutions

The SmartFusion2 Microcontroller Subsystem (MSS) contains an embedded or hard Ethernet MAC and PCS layer, which supports either GMII using FPGA MSIO or SGMII using the SERDESIF. The Ethernet MAC is tightly coupled to the ARM Cortex-M3 of the MSS for Ethernet termination and application layer functions.

IGLOO2 and SmartFusion2 also utilize soft IP blocks to support rates from 10Mbps up to 1000Mbps. Both SmartFusion2 and IGLOO2 provide an embedded XAUI block as part of the SERDESIF.

Microsemi Ethernet Solutions

| Ethernet | PolarFire | SmartFusion2 | IGLOO2 |

| 10BASE | Soft IP MAC CoreTSE and CoreTSE AHB | Embedded MAC or Soft IP MAC | Soft IP MAC |

| 100BASE | |||

| 1000BASE/SGMII | Embedded MAC or Soft IP PCS/MAC | Soft IP PCS/MAC | |

| 10GBASE | Soft IP MAC- Core10GMAC | Embedded XAUI and Soft IP MAC1 | Embedded XAUI and soft IP MAC1 |

Note :

1. The 10G MAC is supplied from a 3rd party IP

The SmartFusion2 embedded MAC can be used with either SGMII or GMII/RGMII physical layer interface. In SmartFusion2 and IGLOO2 a soft IP MAC can be used with an either an SGMII, 1000BASE-X/T, GMII/RGMII or MII/RMM phsical layer interface.

RGMII is embedded in PolarFire GPIO and so can be configured directly using Libero SoC PolarFire software tool.

In PolarFire devices, 10G Ethernet is implemented using the Core10GMAC soft IP media access control (MAC) core, which can be configured in 10GBASE-KR and 10GBASE-R modes. The SmartFusion2 and IGLOO2 support Ethernet using a mix of embedded IP and soft IP which are pre-designed and verified for 10/100/1000Mbps and 10Gbps applications.

- Core10GMAC – Configurable Ethernet MAC IP core with MAC and PHY layer. Provides support for 10GBASE-R and 10GBASE-KR interfaces

- CoreTSE_AHB – 10/100/1000M Ethernet MAC with either a TBI or GMII physical layer. Also includes an embedded DMA controller with AHB interfaces.

- Core10100 – 10/100M Ethernet MAC with MII physical layer

- CoreSGMII – SGMII interface IP for ten bit interface (TBI) or gigabit media independent interface (G/MII) based designs

- CoreRGMII – GMII to RGMII interface IP

- CoreRMII – MII to RMII interface IP

- CoreTSE – 10/100/1000M Ethernet MAC with either a TBI or GMII physical layer

- SmartFusion2 Microcontroller Subsystem Ethernet MAC – fully embedded MAC with SGMII or GMII physical layer interface.

- SmartFusion2 and IGLOO2 XAUI – Supported as part of the SERDESIF block.

- CoreRISCV_AXI4 and CoreABC : Processor/controllers IP cores which can be used for MAC initialization and configuration in Ethernet applications

- UG0687: PolarFire FPGA 1G Ethernet Solutions User Guide

- UG0727: PolarFire FPGA 10G Ethernet Solutions User Guide

- DG0757: PolarFire FPGA 10GBASE-R Ethernet Loopback Demo Guide

- DG0634: Running CoreTSE_AHB IP based Webserver on SmartFusion2 using lwIP and FreeRTOS – Libero SoC v11.6 Demo Guide

LiteFast

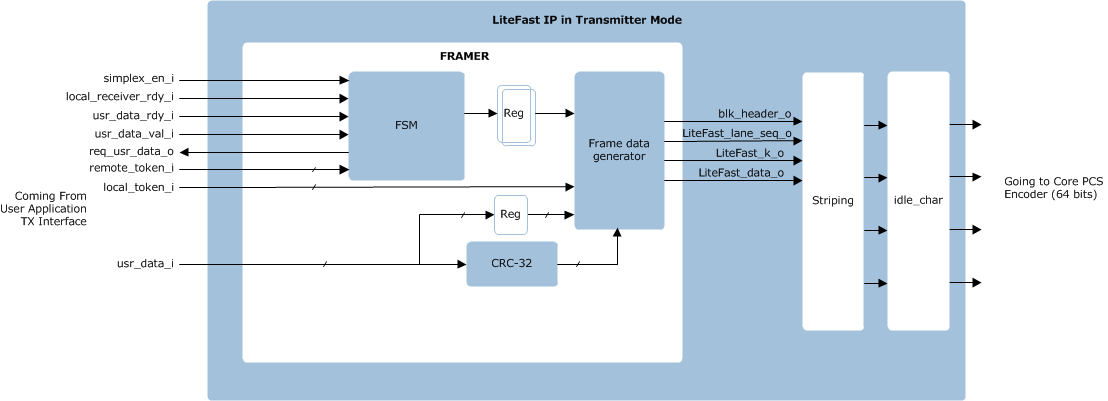

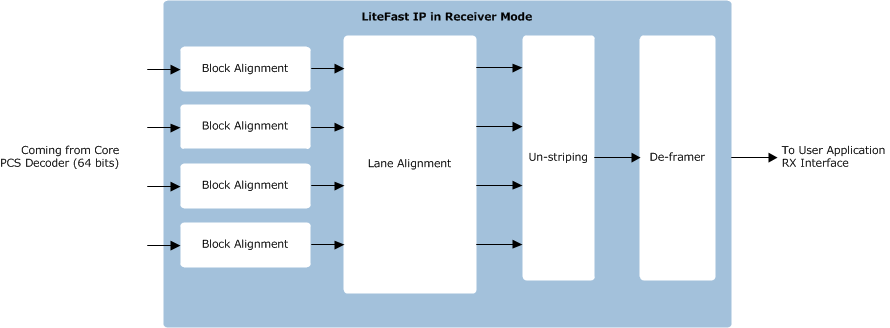

LiteFast is Microsemi's serial, point-to-point, light-weight protocol for high-speed serial communication. LiteFast enables designers to easily implement high-speed serial links using the SERDES blocks available in Microsemi's PolarFire, SmartFusion2, IGLOO2 and RTG4 devices. The solution comes with pre-synthesized and validated IP cores (Transmitter and Receiver), demo design, and complete documentation which reduces the design and validation time.

Microsemi's LiteFast solution is validated with hardware platform using PolarFire Evaluation Kit (300K LE PolarFire FPGA on board) and SmartFusion2 Security Evaluation Kit (90K LE SmartFusion2 SoC FPGA on board).

Key Features

- Supports x 1, x 2 and x 4 lanes per SERDES

- Very little utilization of FPGA logic resources (light weight)

- Idle frame for link establishment and data frame for data transfer

- Idle frame when no data is transmitted

- In-built flow control, word alignment, block alignment, lane alignment and hot-plug support

- Serial full-duplex or simplex operation

- Flow control through token exchange

LiteFast IP Transmitter and Receiver Block Diagram

IP User Guide

Demo Design for PolarFire

The Demo Guide and Design Files are available in the PolarFire FPGA Family page

Demo Design for SmartFusion2 and IGLOO2

Demo Design for RTG4

DG0729: LiteFast IP RTG4 Demo Guide

DG0729: LiteFast IP RTG4 Demo Guide

- LiteFast RTG4 8bit External Loopback Demo- Design and Programming files (RAR, 93.4 MB)

- LiteFast RTG4 8bit Internal Loopback Demo-Design and Programming files (RAR, 93.5 MB)

- LiteFast RTG4 16bit External Loopback Demo-Design and Programming files (RAR, 97.6 MB)

- LiteFast RTG4 16bit Internal Loopback Demo-Design and Programming Files (RAR, 97.6 MB)

- LiteFast Demo GUI Installer (RAR, 194MB)