KK

Lowest Power, Cost-Optimized, Bringing Real-Time to Linux

Overview

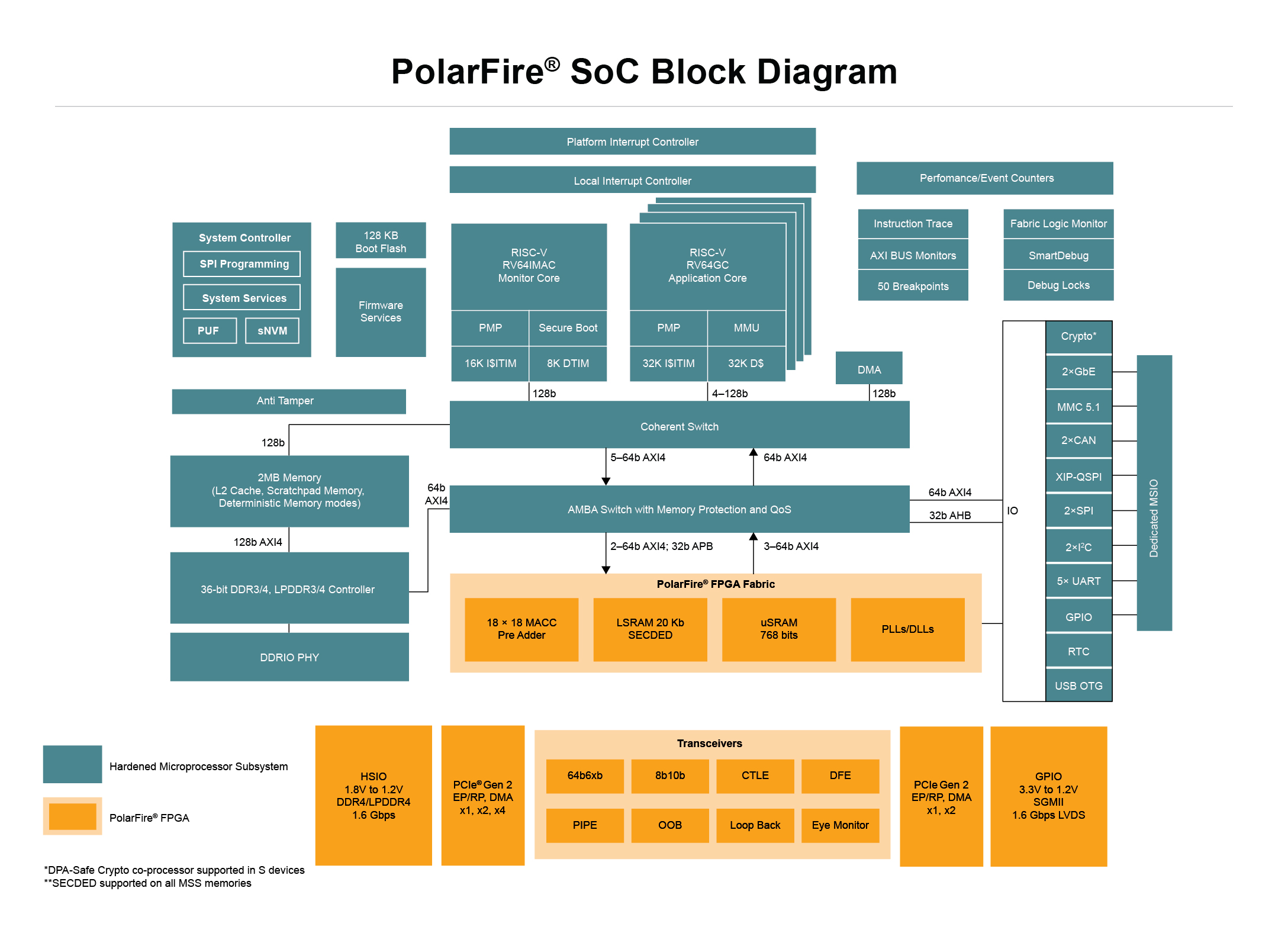

PolarFire® SoC FPGA is the industry's first RISC-V SoC FPGA. PolarFire SoC is built upon the award winning PolarFire FPGA FPGA platform and features a Linux capable RISC-V processor subsystem delivering up to 50% lower power than equivalent SRAM based SoC FPGAs.

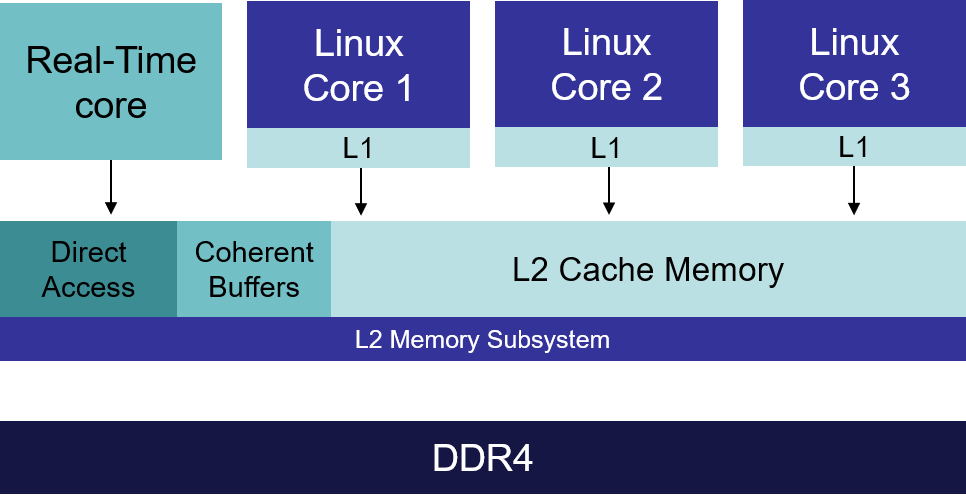

The product family spans from 25k logic elements (LEs) to 460k LEs, features 12.7G transceivers, five-core coherent CPU subsystem with built-in Secure Boot, innovative Linux and Real Time modes, a large flexible L2 memory subsystem and a rich set of embedded peripherals.

PolarFire SoC is ideally suited for secure, power efficient compute in a wide range of applications within Imaging, Artificial Intelligence / Machine Learning (AI/ML), Internet of Things (IoT), Industrial Automation, Automotive, Aerospace and Defense, Wireline Access Networks & Cellular Infrastructure.

|

|

|

Imaging / AI / ML |

Internet of Things |

Industrial Automation |

|

|

|

|

|

|

Automotive |

Defense |

Communications |

|

|

|

Advantage

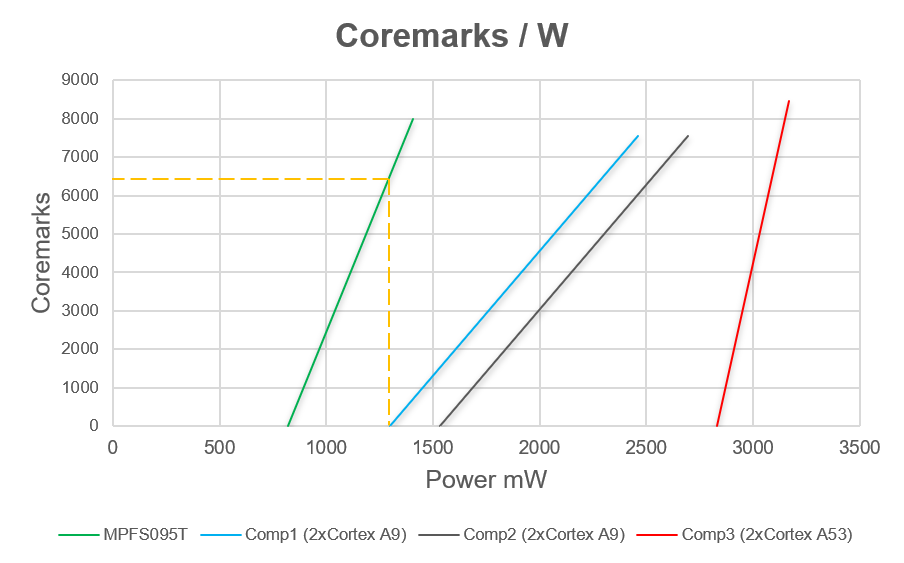

Lowest Power & Superior Performance |

|

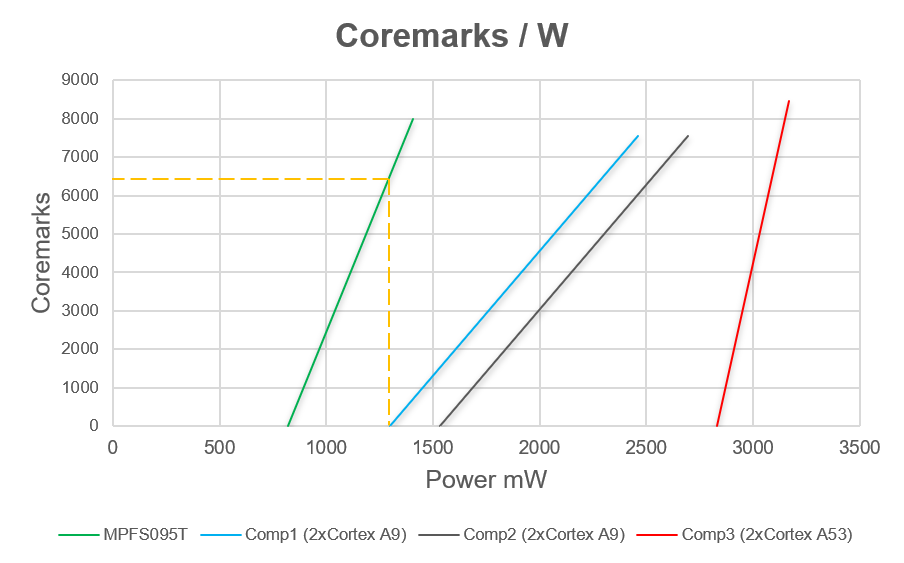

| PolarFire SoC delivers significant power saving while outperforming SRAM based SoC FPGAs. PolarFire SoC offers

|

|

|

|

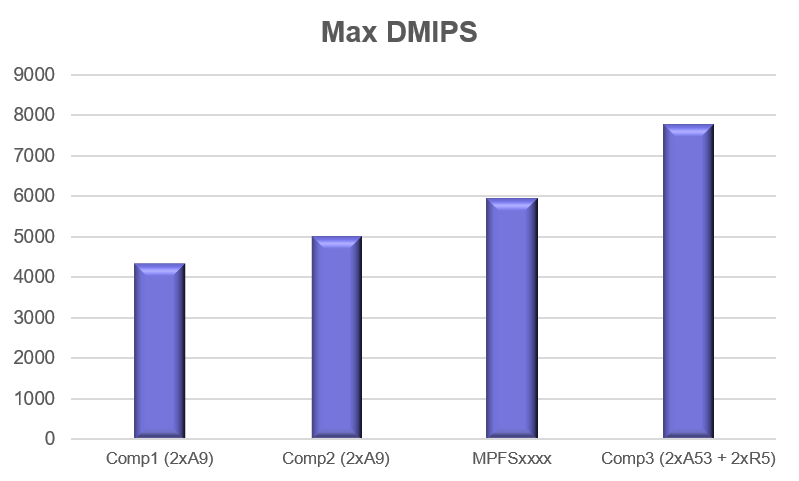

PolarFire SoC delivers more total DMIPS compared to competitive SRAM based SoC FPGAs.

|

|

|

|

|

|

|

|

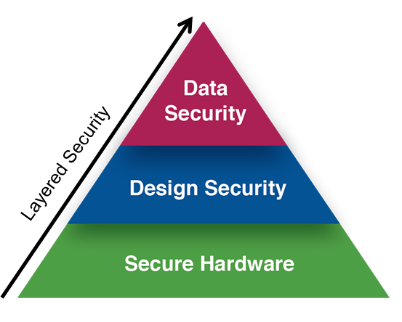

Secure Hardware

Design Security

Data Security

|

|

Want to learn more? Please email PolarFireSoC@microchip.com.

Lowest Power

Lowest Power & Superior Performance |

|

|

|

PolarFire SoC delivers significant power saving while outperforming SRAM based SoC FPGAs.

|

Security

Defense-grade Security

Security starts during silicon manufacturing and continues through system deployment and operations. Microchip’s PolarFire SoC FPGAs represent the industry’s most advanced secure programmable FPGAs.

- Secure Hardware

- Secure wafer-sort and packaging

- Spectre and Meltdown immune CPUs

- Design Security

- DPA-Safe bitstream programming

- Anti-tamper

- DPA-Safe secure boot

- Data Security

- CRI DPA countermeasures pass-through license

- DPA-safe crypto-coprocessor

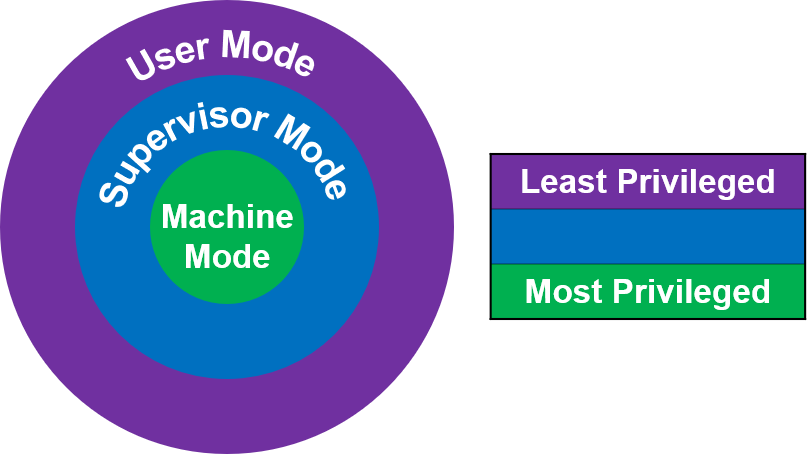

RISC-V Physical Memory Protection (PMP)

PolarFire SoC has PMP implemented in each of the processor cores. PMP is used to enforce (Read / Write / Execute) restrictions on less privileged modes.

Security Leadership

| Features | PolarFire SoC | Competitor 1 | Competitor 2 | Competitor 3 |

|---|---|---|---|---|

| TRNG | Hard-IP (SP800-90A CTR_DRBG-256; SP800-90B (draft) NRBG) | ✖ | ✖ | Soft-IP |

| AES | AES-128/192/256 (ECB, CBC, CTR, OFB, CFB, GCM, KeyWrap) | AES-256 (CBC) | AES-256 (CBC) | AES-256 (ECB, GCM) |

| SHA | SHA-1/224/256/384/512, Key Tree | SHA-256 | SHA-256 | SHA-384 |

| HMAC | HMAC-SHA-1/224/256/384/512; GMAC-AES; CMAC-AES | HMAC-SHA2-256 | HMAC-SHA2-256 | ✖ |

| RSA | SigGen (ANSI X9.31, PKCS v1.5), SigVer (ANSI X9.31, PKCS v1.5)-1024/1536/2048/3072/4096 | Soft-RSA –(2048), SigGen(PKCS v1.5), SigVer (PKCS v1.5) |

Soft-RSA –(2048), SigGen(PKCS v1.5), SigVer (PKCS v1.5) |

Software library: RSA primitive (2048) |

| ECDSA | KeyGen, KeyVer, SigGen & SigVer - NIST & Brainpool (P256/384/521); KAS - ECC CDH, PKG, PKV | ✖ | ✖ | ✖ |

| FFC | KAS - DH, DSA SigGen & SigVer (1024/1536/2048/3072/4096) | ✖ | ✖ | ✖ |

| Tamper Sense | Voltage, Temperature, Clock Frequency, Clock Glitch, Active Mesh | ✖ | ✖ | Only Voltage & Temperature |

| PUF | PUF protection for Secure Key storage (Secure Boot and Data communication) | ✖ | ✖ | For secure boot key |

| Bitstream Protection | DPA resistant Encrypted bit-stream programming | ✖ | ✖ | ✔ |

| DPA Resistance | DPA resistant hard crypto co-processor supporting all above Crypto algorithms | ✖ | ✖ | ✖ |

Architecture

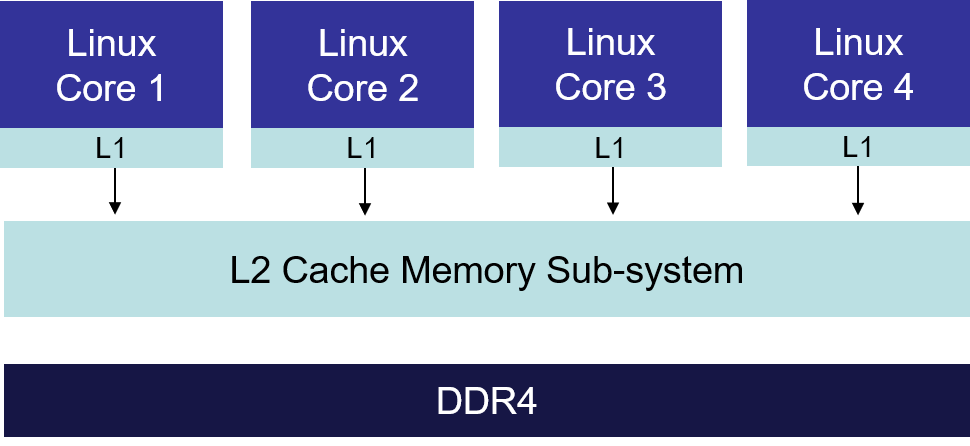

PolarFire SoC is based on the award winning PolarFire FPGA architecture and integrates a versatile, low-power, 64-bit, multi-core RISC-V processor subsystem.

- Linux and Real-Time capable in a deterministic and coherent CPU cluster

- Integrated DDR3/4, LPDDR3/4 controllers and Phy

- Defense-grade Secure boot

- Spectre and Meltdown immune

- Physical Memory protection

- SECDED on all memories

PolarFire SoC delivers industry's lowest power at mid-range densities with exceptional security and reliability.

Real-Time with Linux

Safety Critical, System Control and Security applications use the flexibility that Linux offers and need Real-Time Determinism to control hardware.

|

|

|

|

|

| Safety Critical systems | AI / ML | Industrial IoT | Robotics | Smart Weapons and UAV |

| Typical SMP implementations may offer the flexibility of a rich operating systems but are terrible for running real-time systems needing deterministic performance. | |

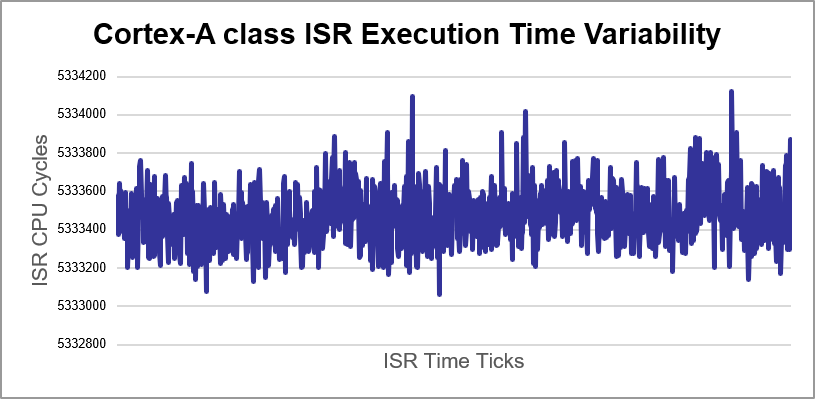

Quad-core Cortex-A class processor in SMP mode |

ISR execution times vary significantly |

|

|

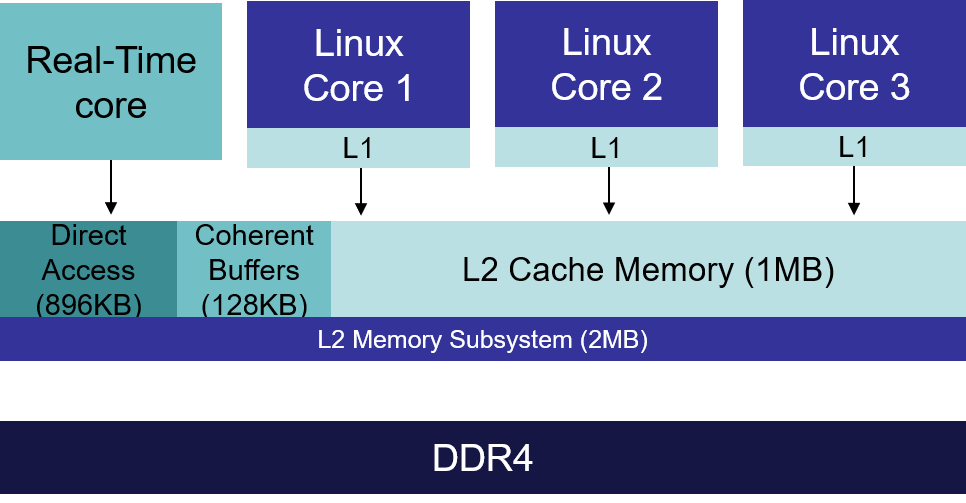

Designing a deterministic, Linux capable SoC requires a multi-dimensional approach needing architectural innovation, a coherent memory subsystem across cores and configurable branch prediction capabilities.

PolarFire SoC features a multi-core Linux capable processor that is coherent with the memory subsystem allowing a versatile mix of deterministic real-time systems and Linux in a single multi-core CPU cluster.

PolarFire SoC enables you to create a fully deterministic real-time system alongside Linux that executes on-time every time.

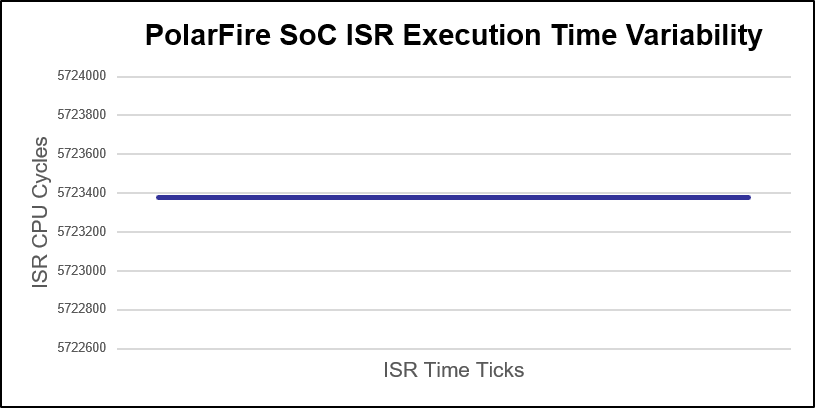

AMP Implementation on PolarFire SoC |

The ISR execution times are deterministic |

|

|

Product Family

PolarFire SoC Product Family

| Features | PolarFire SoC FPGA | |||||

|---|---|---|---|---|---|---|

| MPFS025T | MPFS095T | MPFS160T | MPFS250T | MPFS460T | ||

| FPGA Fabric | k Logic Elements (4LUT + DFF) | 23 | 93 | 161 | 254 | 461 |

| Math Blocks (18x18 MACC) | 68 | 292 | 498 | 784 | 1420 | |

| LSRAM Blocks (20k bit) | 84 | 308 | 520 | 812 | 1460 | |

| uSRAM Blocks (64x12) | 204 | 876 | 1494 | 2352 | 4260 | |

| Total RAM Mbits | 1.8 | 6.7 | 11.3 | 17.6 | 31.6 | |

| uPROM Kbits | 194 | 387 | 415 | 470 | 553 | |

| User DLL's/PLL's | 8 each | 8 each | 8 each | 8 each | 8 each | |

| High Speed IO | 12.5 Gbps SERDES Lanes | 4 | 4 | 8 | 16 | 20 |

| PCIe Gen2 End Points/Root Ports | 2 | 2 | 2 | 2 | 2 | |

| Total FPGA IO | HSIO+GPIO | 108 | 276 | 312 | 372 | 468 |

| Total MSS IO | MSS IO | 136 | 136 | 136 | 136 | 136 |

| MSS DDR | Data Bus | 16 | 32 | 32 | 32 | 32 |

| Packaging | Type (Size, Pitch) | Total User I/O: MSS-IO / HSIO / GPIO / XCVRs | ||||

| FCSG325 (11x11, 11x14.5*, 0.5 mm) | 102 / 32 / 48 / 2 | 102 / 32 / 48 / 2 | 102 / 32 / 48 / 2 * | |||

| FCSG536 (16x16, 0.5 mm) | 136 / 60 / 108 / 4 | 136 / 60 / 108 / 4 | 136 / 60 / 108 / 4 | |||

| FCVG484 (19x19, 0.8 mm) | 136 / 60 / 48 / 4 | 136 / 60 / 84 / 4 | 136 / 60 / 84 / 4 | 136 / 60 / 84 / 4 | ||

| FCVG784 (23x23, 0.8 mm) | 136 / 144 / 168 / 8 | 136 / 144 / 168 / 8 | 136 / 144 / 180 / 8 | |||

| FCG1152 (35x35, 1.0 mm) | 136 / 144 / 228 / 16 | 136 / 180 / 288 / 20 | ||||

Extended Commercial (0°C to 100°C) and Industrial (–40°C to 100°C) Temperature Support for all Die Package Combinations.

PolarFire SoC offers the Smallest Form Factors

PolarFire SoC FPGAs offer best-in-class form factors at 25k, 95k, 160k and 250k LEs.

Getting Started

Step 1: Download and Install the Latest Tools

| Downloads | Description |

| Libero SoC Design Suite | Libero SoC design suite is a comprehensive tool for designing with Microsemi FPGAs and SoCs |

| SoftConsole | SoftConsole is a free software development environment for embedded firmware development |

Step 2: Choose a Target to view the compatible reference material

|

Renode

|

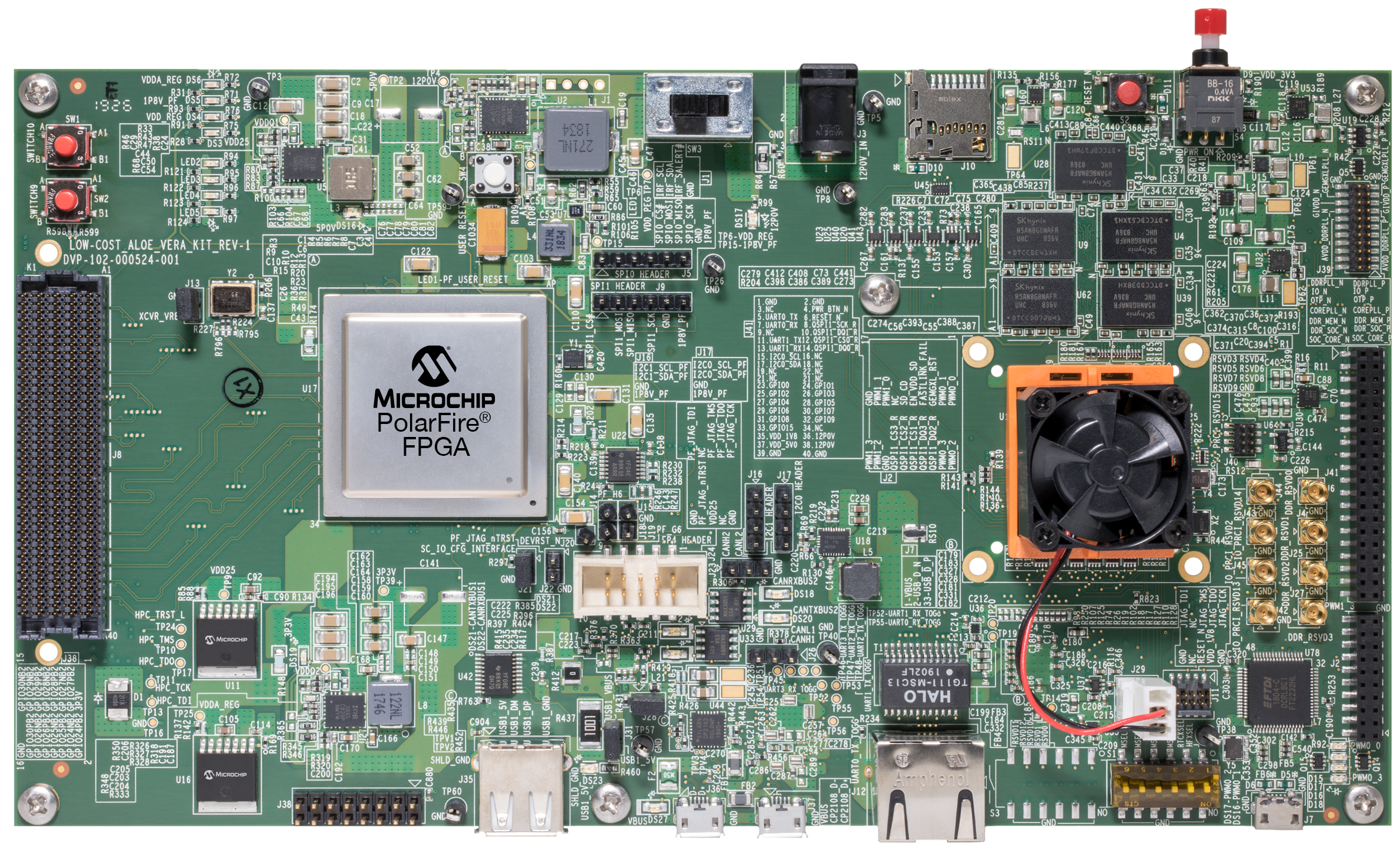

LC_MPFS_DEV_KIT

|

MPFS-DEV-KIT

|

||

|

|

|

||

|

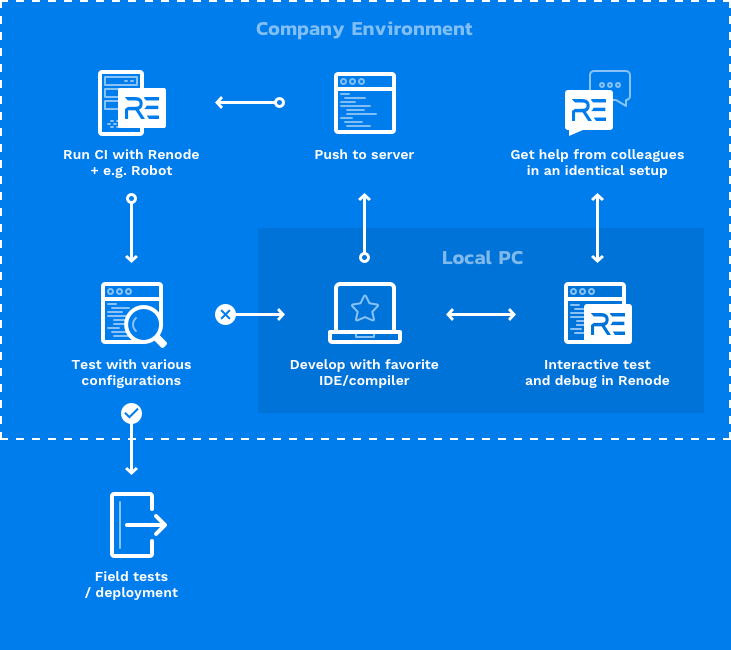

Renode provides a simulation model for PolarFire SoC and Mi-V soft-CPUs and can be used to debug firmware. Renode is bundled with SoftConsole v6.x and can be downloaded for free.

The LC-MPFS-DEV-KIT is a pre-silicon development platform for PolarFire SoC. It is available for early access customers. Contact PolarFireSoC@microchip.com for more information.

The MPFS-DEV-KIT is a pre-silicon development platform for PolarFire SoC. It is available in limited quantity to select early access customers. Contact PolarFireSoC@microchip.com for more information.

|

||||

Step 3: Download the reference material compatible with your target

Renode |

||

| Reference Material | Description | |

| Renode Webinar Series | View Getting started videos and register for Renode Webinar Series | |

| SoftConsole Release Notes | SoftConsole and Renode installation instructions and release notes | |

| Renode Documentation Renode Website |

Complete documentation on Renode | |

| RISC-V ISA Specification RISC-V ISA Privileged Specification RISC-V Debug Specification |

RISC-V Specification Documentation | |

| Target: SoftConsole | SoftConsole Software and documentation | |

LC-MPFS-DEV-KIT |

|

| Reference Material | Description |

| User Guide: LC-MPFS-DEV-KIT | A complete user guide to program and boot Linux on the LC-MPFS-DEV-KIT |

| Schematics: LC-MPFS-DEV-KIT | Schematics for the LC-MPFS-DEV-KIT |

| Libero Project: VERA_IOFPGA | A sample Libero project to get started with the LC-MPFS-DEV-KIT |

| Bitstream File: VERA_IOFPGA_STP | The bitstream pre-programmed in the LC-MPFS-DEV-KIT |

| RISC-V ISA SpecificationRISC-V ISA Privileged SpecificationRISC-V Debug Specification | RISC-V Specification Documentation |

| PolarFireSoC@microchip.com | Contact for more information |

MPFS-DEV-KIT |

|

| Reference Material | Description |

| User Guide: MPFS-DEV-KIT | A complete user guide to program and boot Linux on the MPFS-DEV-KIT |

| Schematics: HiFive Unleashed Kit Schematics: HiFive Unleashed Expansion Board |

Schematics for the MPFS-DEV-KIT |

| Libero Project: HFU_EXP_MSS1_110918 | A sample Libero Project to get started with the MPFS-DEV-KIT |

| Bitstream File: (.job) Bitstream File: (.stp) |

The bitstream pre-programmed on the MPFS-DEV-KIT |

| Linux: SDK | Download link for the Linux SDK for MPFS-DEV-KIT |

| RISC-V ISA Specification RISC-V ISA Privileged Specification RISC-V Debug Specification |

RISC-V Specification Documentation |

| PolarFireSoC@microchip.com |

Contact for more information |

Downloads

User Guide

| HiFive Unleashed Platform User Guide | 10/2018 |

| LC-MPFS-DEV-KIT User Guide | 11/2019 |

Libero Project

| Libero Project for HiFive Unleashed Platform: HFU_EXP_MSS1_110918 | 09/2018 |

| Libero Project for LC-MPFS-DEV-KIT: VERA_IOFPGA | 09/2019 |

Bitstream Files

| HiFive Unleashed Platform JOB file | 09/2018 |

| HiFive Unleashed Platform STP file | 09/2018 |

| LC-MPFS-DEV-KIT Bitstream | 09/2019 |

Schematics

| HiFive Unleashed Kit Schematics | 08/2018 |

| HiFive Unleashed Expansion Board Schematics | 08/2018 |

| LC-MPFS-DEV-KIT Schematics | 05/2019 |

Linux SDK

| HiFive Unleashed Platform Linux SDK | 10/2018 |

Mi-V Ecosystem

Mi-V Embedded Experts

Mi-V Embedded Experts is a network of qualified third-party design houses available to help customers with their PolarFire SoC designs. They have expertise in various fields including IP design, Embedded Firmware, Operating Systems, RTOS, Drivers, BSP support and System-on-Module (SOM) design. These partners provide support through the entire lifecycle of your project. Get help to jump-start your design and get your product to market quickly with these Mi-V Embedded Experts.

Want to join the Mi-V Embedded Experts Network? Please email PolarFireSoC@microchip.com.