VSC9803

Overview

100G CI-BCH-3™ eFEC Encoder/Decoder Core and Design Package

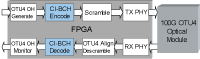

Microsemi is a leading provider of transport processing technology with widely deployed 10G OTN Mapper devices that use enhanced FEC (eFEC). The Microsemi VSC9803 100G Continuously Interleaved BCH-3 (CI-BCH-3™) design package enables integration of eFEC encoder/decoder algorithms optimized for 100G OTN transport applications. The algorithms support the G.709 standard 6.7% FEC overhead ratio. FEC bytes are generated in the encoder using BCH (1020, 988) 3-error correcting code. FEC byte locations in the OTU4 signal are overwritten with computed CI-BCH-3™ FEC bytes.The decoder applies hard-decision CI-BCH-3™ FEC decoding to a received OTU4 signal. The corrected OTU4 signal is delivered at the output of the decoder. Decoding latency can be varied for FEC error-correcting performance and reduced latency tradeoffs. FEC statistic outputs such as corrected 1s, corrected 0s, and uncorrectable code words are generated for performance monitoring. The VSC9803 CI-BCH-3™ eFEC core can be targeted to FPGA or ASIC implementations including support for 40GOTU3.

Related Products

Key Features

- 100G CI-BCH-3™ eFEC

- NECG: 9.15 dB at 6.7% overhead

- Supports G.709 OTU4

- FPGA technology

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |

Ordering

| Distributor | SKU | Stock | MOQ | Pkg | |

|---|---|---|---|---|---|

| DigiKey | VSC9803-01-ND | .. | Bulk | No Stock |