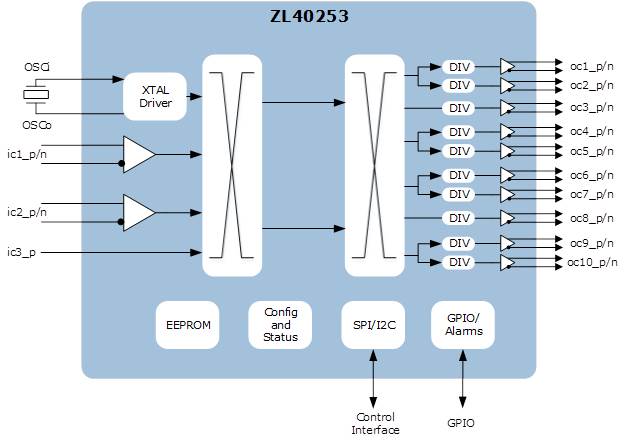

ZL40250,ZL40251,ZL40252,ZL40253

miSmartBuffer 6- or 10-Output Programmable Fanout Buffers with Multi-Format I/O and Dividers

Overview

|

Microsemi’s miSmartBuffer ZL4025x Family of devices give the ability to create multiple copies of a clock signal and distribute them among several loads with minimal additive jitter. The miSmartBuffer family of devices are synergistic with Microsemi® industry-leading timing portfolio and when combined can create a complete clock tree, replacing a number of multipliers, synthesizers, and oscillators on the board, improving design reliability while reducing BOM costs and simplifying design. The miSmartBuffer ZL4025x Family of devices also feature an intuitive graphical user interface (GUI) and the ability to create factory pre-programmed devices with ease using Microsemi’s web tool, miClockDesigner. These pre-programmed devices—which have pin-selectable configurations at power-up—ensure clock availability and proper system bring-up for all applications. |

miSmartBuffer™ ZL4025x Family Product Preview

White Paper: PCI Express Refclk Jitter Compliance

Applications/Uses

- Clock signal fanout, format conversion, frequency division and skew adjustment in a wide variety of equipment types including Processors, NPUs, FPGAs, 10G CDRs, high-speed ADCs and DACs, PCIe interface devices, Ethernet switches and PHYs

- Clock trees for optical, OTN, SONET,/SDH, WDM, storage, networking and broadcast video applications

Key Features

- Four Flexible Input Clocks

- One crystal/CMOS input

- Two differential/CMOS inputs

- One single-ended/CMOS input

- Any input frequency up to 1GHz (300MHz max for CMOS)

- Manual clock switching by pin or register

- 6 or 10 Universal Output Clocks with Dividers

- Each output has independent divider

- Low additive jitter <200fs RMS (12kHz-20MHz for input frequencies >100MHz)

- Each output configurable as LVDS, LVPECL, HCSL, 2xCMOS or HSTL

- Output jitter from integer multiply and dividers as low as 0.17ps RMS (12kHz-20MHz)

- Output jitter from fractional dividers is typically < 1ps RMS, many frequencies <0.5ps RMS

- Each output has an independent divider

- Each output configurable as LVDS, LVPECL, HCSL, 2xCMOS or HSTL

- In 2xCMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz)

- Multiple output supply voltage banks with CMOS output voltages from 1.5V to 3.3V

- Precise output alignment circuitry from GPIO pin or register bit

- Per-output skew adjustment

- Per-output enable/disable and glitchless start/stop (stop high or low)

General Features

- Automatic self-configuration at power-up from internal or external EEPROM; up to 8 configurations pin-selectable

- Four multi-purpose I/O pins

- SPI or I2C processor interface

- Core supply voltage options: 2.5V only, 3.3V only, 1.8V+2.5V or 1.8V+3.3V

- Space-saving 8x8mm QFN56 (0.5mm pitch)

- Easy-to-use evaluation/programming software

- Create factory pre-programmed devices using Microsemi’s web tool, miClockDesigner.

Resources

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |