ZL30256

3-Channel, 10-Input, 18-Output General Purpose Jitter Attenuator and Frequency Multiplier

Overview

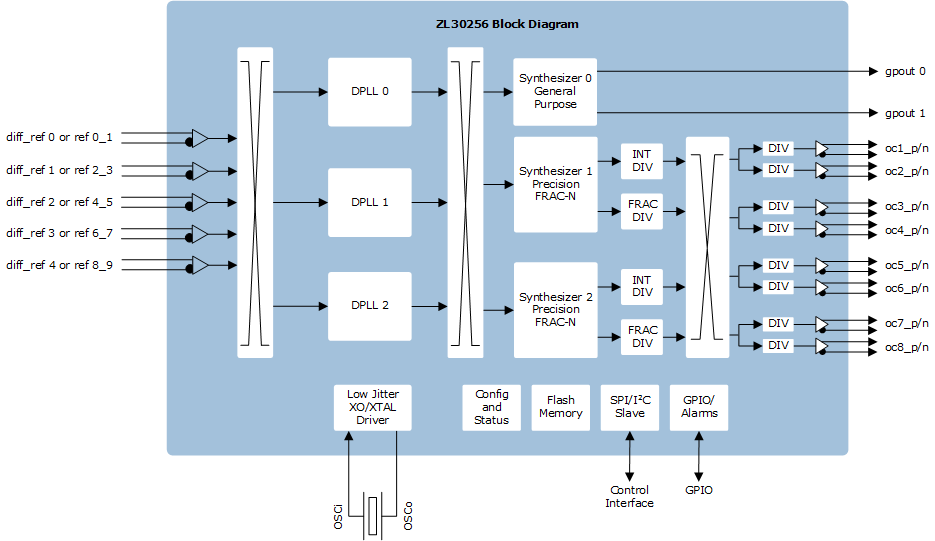

The ZL30256 is multi-channel high-performance, any-rate multiplier and jitter attenuator which simplifies board design by generating ultra-low-jitter clock signals from or attenuating clock signals while generating additional independent frequency families.With 3 independent jitter attenuating DPLL channels, the ability to create 5 different frequency families and best-in-class jitter performance, the ZL30256 can create complete clock-trees, improving design reliability, reducing bill of materials (BOM) cost, and simplifying design by replacing multiple PLLs and peripheral timing components.

Key Features

- Up to 3 independent DPLL channels

- Excellent jitter performance of 180 fs RMS in 12 kHz to 20 MHz band meets jitter requirements of 10G/40G and 100G PHYs

- Two programmable ultra-low jitter synthesizers generate any frequency from 1 Hz to 1045 MHz

- One programmable general purpose synthesizer generates any clock from 1Hz to 180 MHz

- 8 differential or 16 single ended (CMOS) ultra-low jitter outputs plus two general purpose CMOS outputs

- Accepts up to 10 LVPECL/LVDS/HCSL/LVCMOS inputs

- Any input reference can be fed with clock, sync (frame pulse), clock /sync pair or clock modulated with sync pulse (embedded PPS ePPS and embedded PP2S ePP2S)

- Up to four programmable digital PLLs/NCOs with loop bandwidth from 14 Hz to 470 Hz synchronize to any clock rate from 1 kHz to 900 MHz and to clock plus sync pulse

- Automatic hitless reference switching and digital holdover on reference fail with initial holdover accuracy better than 1 ppb with post holdover filter

- Easy Configuration and dynamic programming via SPI/I2C interface

- Operates from a single crystal resonator or clock oscillator

Resources

Parametric Search

- {{n+1}} Showing per page

| Parts | Part Status | package Type | Package Carrier | {{attribute.name | noComma}} ({{attribute.type}}) |