# Quad 46V, 2.5A/1.25A RLCL Power Switches for Space

# Description

The LX7714 is a quad power switch with line protection that is radiation-hardened-by-design and is used for spacecraft power distribution. It provides a means to turn on and off four independent DC loads with continuous currents up to 2.5A.

The LX7714 comprises 4 independent protected power switch sections, each capable of driving a load up to 1.25A or 2.5A, depending on the version.

The internal PMOS power switches use slew limiting when turned on and off to control power switching to capacitive loads, and to manage the switching off of inductive loads. A power switch automatically opens the circuit in the event of an overload condition. The overload condition is a function of fault current over time; more severe fault conditions cause the switch to open faster.

Each power switch has an individual differential ON/OFF control input pair which directly interfaces to singleended logic or an RS-422 type bus. Power switches default to the ON state with open-circuit control inputs.

A tripped power switch enters hiccup mode, that allows a die cool-down period for 10s with the load disconnected before retrying. Up to 4,096 cool-down/retry cycles are attempted before the power switch latches OFF.

Each channel includes complementary Power Good and In Reset logic status outputs for telemetry purposes. Power Good is asserted when the device is supplying nominal power to the load. In Reset status is asserted when the device is in hiccup fault recovery mode.

Each power switch has thermal shutdown for secondary protection in the unlikelihood of a malfunction with the primary overload protection function.

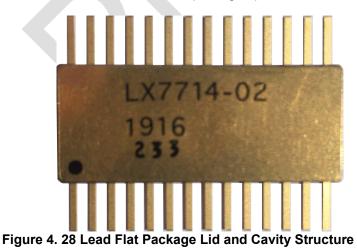

The LX7714 is packaged in a 28-pin hermetic ceramic flatpack (CFP) package. It operates over a -55°C to 125°C temperature range and is radiation tolerant to a minimum of 100krad(Si) TID and a minimum of 50krad(Si) ELDRS, as well as single event effects.

# Features

- Four internal 2.5A or 1.25A rated power switches

- Power switches can be paralleled up to 10A

- Switches voltages to 46V

- Built-in fuse-like I<sup>2</sup>t current limiting

- Safe management of soft overload faults

- Automatic hiccup retry timer to clear faults

- Power Good and Fault status outputs

- Differential ON and OFF control inputs

- Low power switch voltage drop

- Over temperature shutdown

- Load current slew rate control

- Small hermetic 28 lead ceramic flatpack package

- Radiation tolerant: 100krad(Si) TID, 50krad(Si)

ELDRS, SEL immune up to 60 MeV.cm<sup>2</sup>/mg and 125°C (fluence of 10<sup>7</sup> particles/cm<sup>2</sup>)

# Applications

Spacecraft power control and distribution

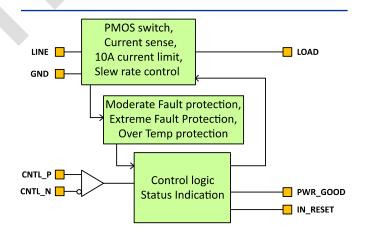

#### One of Four Independent Power Switches

#### <u>Notes</u>

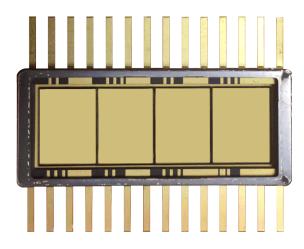

- 1. The LX7714 comprises 4 independent die bonded within a common package

- 2. The metal package top is electrically isolated from the body of the package, and should either remain isolated or be connected to GND if the four power switch ground pins share a common GND connection

- 3. Use the base of the package as the surface for conducting heat from the package. The metal package top is attached to the package body at the top of relatively thin cavity walls, and so is inferior to the base of the package for heat removal. The leads can be formed to mount the package upside down on the PCB if convenient

### 2 Ordering Information

| Operating<br>Temperature | Package<br>Type                  | Package   | Part Number     | Current<br>Rating | SMD Number | Flow                  | Shipping<br>Type      |     |

|--------------------------|----------------------------------|-----------|-----------------|-------------------|------------|-----------------------|-----------------------|-----|

|                          | Hermetic<br>Ceramic<br>Elat Pack |           | LX7714-25MFB-EV |                   | TBD        | MIL-PRF-38535 Class V |                       |     |

|                          |                                  | Hormotio  |                 | LX7714-25MFB-EQ   | 2.5A       | TBD                   | MIL-PRF-38535 Class Q |     |

| -55°C to 125°C           |                                  | CFP-28    | LX7714-25MFB-ES |                   | -          | Engineering Samples   | Tray                  |     |

| -55 0 10 125 0           |                                  | Flat Pack |                 | LX7714-12MFB-EV   |            | TBD                   | MIL-PRF-38535 Class V | пау |

|                          | T Iat T ack                      |           | LX7714-12MFB-EQ | 1.2A              | TBD        | MIL-PRF-38535 Class Q |                       |     |

|                          |                                  |           | LX7714-12MFB-ES |                   | -          | Engineering Samples   |                       |     |

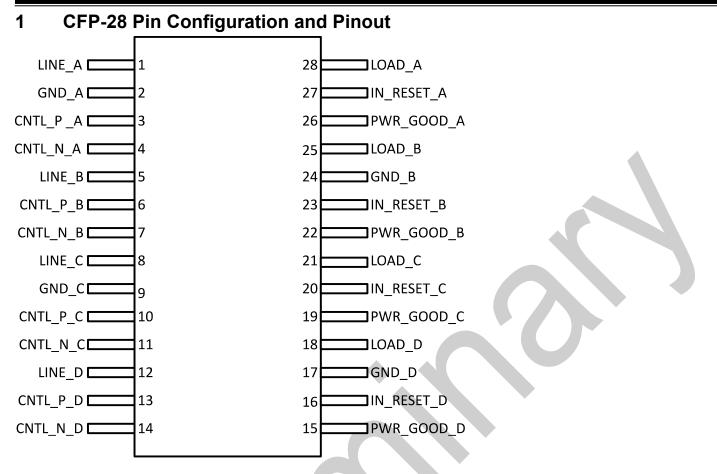

# 3 Pin Numbering and Pin Descriptions

| Pin | Name       | Pin Type        | Pin Function                                | Description                                                                                                                                                                                                                                                                                  |

|-----|------------|-----------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LINE_A     | Power           | Power switch A input supply                 | Connect to the power supply to be switched by power switch A. This is also the supply to the switch's control section. Bypass with a $\geq$ 47nF capacitor to GND_A                                                                                                                          |

| 2   | GND_A      | Power           | Power switch A GND                          | Ground for power switch A                                                                                                                                                                                                                                                                    |

| 3   | CNTL_P_A   | Logic<br>Input  | Power switch A active high ON/OFF control   | Active high enable input for power switch A. CNTL_P_A is half of the differential enable input comprising active high CNTL_P_A and active low CNTL_P_A. Turn power switch A on by either setting {CNTL_P_A = high, CNTL_N_A = low) or leaving both CNTL_P_A and CNTL_N_A open                |

| 4   | CNTL_N_A   | Logic<br>Input  | Power switch A active<br>low ON/OFF control | Active low enable input for power switch A. $CNTL_N_A$ is half of the differential enable input comprising active low $CNTL_P_A$ and active high $CNTL_P_A$ . Turn power switch A on by either setting { $CNTL_P_A$ = high, $CNTL_N_A$ = low) or leaving both $CNTL_P_A$ and $CNTL_N_A$ open |

| 5   | LINE_B     | Power           | Power switch B input<br>supply              | Connect to the power supply to be switched by power switch B. This is also the supply to the switch's control section. Bypass with a $\geq$ 47nF capacitor to GND_B                                                                                                                          |

| 6   | CNTL_P_B   | Logic<br>Input  | Power switch B Active high ON/OFF control   | Active high enable input for power switch B. CNTL_P_B is half of the differential enable input comprising active high CNTL_P_B and active low CNTL_P_B. Turn power switch B on by either setting {CNTL_P_B = high, CNTL_N_B = low) or leaving both CNTL_P_B and CNTL_N_B open                |

| 7   | CNTL_N_B   | Logic<br>Input  | Power switch B Active<br>low ON/OFF control | Active low enable input for power switch B. CNTL_N_B is half of the differential enable input comprising active low CNTL_P_B and active high CNTL_P_B. Turn power switch B on by either setting {CNTL_P_B = high, CNTL_N_B = low} or leaving both CNTL_P_B and CNTL_N_B open                 |

| 8   | LINE_C     | Power           | Power switch C input<br>supply              | Connect to the power supply to be switched by power switch C. This is also the supply to the switch's control section. Bypass with a $\geq$ 47nF capacitor to GND_C                                                                                                                          |

| 9   | GND_C      | Power           | Power switch C GND                          | Ground for power switch C                                                                                                                                                                                                                                                                    |

| 10  | CNTL_P_C   | Logic<br>Input  | Power switch C Active high ON/OFF control   | Active high enable input for power switch C. CNTL_P_C is half of the differential enable input comprising active high CNTL_P_C and active low CNTL_P_C. Turn power switch C on by either setting {CNTL_P_C = high, CNTL_N_C = low) or leaving both CNTL_P_C and CNTL_N_C open                |

| 11  | CNTL_N_C   | Logic<br>Input  | Power switch C Active<br>low ON/OFF control | Active low enable input for power switch C. $CNTL_N_C$ is half of the differential enable input comprising active low $CNTL_P_C$ and active high $CNTL_P_C$ . Turn power switch C on by either setting { $CNTL_P_C$ = high, $CNTL_N_C$ = low) or leaving both $CNTL_P_C$ and $CNTL_N_C$ open |

| 12  | LINE_D     | Power           | Power switch D input supply                 | Connect to the power supply to be switched by power switch D. This is also the supply to the switch's control section. Bypass with a $\geq$ 47nF capacitor to GND_D                                                                                                                          |

| 13  | CNTL_P_D   | Logic<br>Input  | Power switch D Active high ON/OFF control   | Active high enable input for power switch D. CNTL_P_D is half of the differential enable input comprising active high CNTL_P_D and active low CNTL_P_D. Turn power switch D on by either setting {CNTL_P_D = high, CNTL_N_D = low} or leaving both CNTL_P_D and CNTL_N_D open                |

| 14  | CNTL_N_D   | Logic<br>Input  | Power switch D Active<br>low ON/OFF control | Active low enable input for power switch D. CNTL_N_D is half of the differential enable input comprising active low CNTL_P_D and active high CNTL_P_D. Turn power switch D on by either setting {CNTL_P_D = high, CNTL_N_D = low} or leaving both CNTL_P_D and CNTL_N_D open                 |

| 15  | PWR_GOOD_D | Logic<br>Output | Power switch D status-<br>good indicator    | Active low open drain status output indicating that power switch D is enabled and is operating normally                                                                                                                                                                                      |

|     |            | Logic<br>Output | High side rail power source                 | Active low open drain status output indicating that power switch D is in fault recovery (hiccup) mode                                                                                                                                                                                        |

| 17  | GND_D      | Power           | Power switch D GND                          | Ground for power switch D                                                                                                                                                                                                                                                                    |

| 18  | LOAD_D     | Power           | Power switch D load                         | Connect to the load to be switched by power switch D                                                                                                                                                                                                                                         |

| 19  | PWR_GOOD_C | Logic<br>Output | Power switch C status-<br>good indicator    | Active low open drain status output indicating that power switch C is enabled and is operating normally                                                                                                                                                                                      |

| 20  | IN_RESET_C | Logic<br>Output | High side rail power source                 | Active low open drain status output indicating that power switch C is in fault recovery (hiccup) mode                                                                                                                                                                                        |

| 21  | LOAD_C     | Power           | Power switch C load                         | Connect to the load to be switched by power switch C                                                                                                                                                                                                                                         |

| 22  | PWR_GOOD_B | Logic<br>Output | Power switch B status-<br>good indicator    | Active low open drain status output indicating that power switch B is enabled and is operating normally                                                                                                                                                                                      |

| 23  | IN_RESET_B | Logic<br>Output | High side rail power source                 | Active low open drain status output indicating that power switch B is in fault recovery (hiccup) mode                                                                                                                                                                                        |

| 24  | GND_B      | Power           | Power switch B GND                          | Ground for power switch B                                                                                                                                                                                                                                                                    |

| 25  | LOAD_B     | Power           | Power switch B load                         | Connect to the load to be switched by power switch B                                                                                                                                                                                                                                         |

| 26  | PWR_GOOD_A | Logic<br>Output | Power switch A status-<br>good indicator    | Active low open drain status output indicating that power switch A is enabled and is operating normally                                                                                                                                                                                      |

| 27  | IN_RESET_A | Logic<br>Output | High side rail power<br>source              | Active low open drain status indicating that power switch A is in fault recovery (hiccup) mode                                                                                                                                                                                               |

| 28  | LOAD_A     | Power           | Power switch A load                         | Connect to the load to be switched by power switch A                                                                                                                                                                                                                                         |

### 4 Absolute Maximum Ratings

Stresses above those listed in ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

| Parameter                                                                                   | Min  | Max  | Units |

|---------------------------------------------------------------------------------------------|------|------|-------|

| Line voltage (V <sub>LINE_x</sub> ) relative to GND_x                                       | -0.7 | 58   | V     |

| Load voltage relative to line voltage (VLOAD_x - VLINE_x)                                   | -58  | 0.7  | V     |

| Ground voltage (GND_x) of any section relative to GND_x of any other section                | -TBD | TBD  | V     |

| Logic input voltage (V <sub>CNTL_P_x</sub> , V <sub>CNTL_N_x</sub> ) relative to GND_x      | -7   | 12   | V     |

| Logic output voltage (V <sub>IN_RESET_x</sub> , V <sub>PWR_GOOD_x</sub> ) relative to GND_x | -0.7 | 13   | V     |

| Output current (I <sub>IN_RESET_x</sub> , I <sub>PWR_GOOD_X</sub> ) for digital outputs     |      | 5    | mA    |

| Load current (I <sub>LOAD</sub> ) for LX7714-25MFB. Positive current is internally limited  | -0.1 | 12.5 | A     |

| Load current (I <sub>LOAD</sub> ) for LX7714-12MFB. Positive current is internally limited  | -0.1 | 6.2  | А     |

| Operating junction temperature                                                              | -55  | 150  | °C    |

| Storage junction temperature                                                                | -65  | 160  | °C    |

| Peak lead solder temperature (10 seconds)                                                   |      | 275  | °C    |

## 5 Electrostatic Discharge Ratings

JEDEC JEP155 states that 500V HBM allows safe manufacturing with a standard ESD controlled process. JEDEC JEP157 states that 250V CDM allows safe manufacturing with a standard ESD controlled process. ESD ratings apply to all pins.

| ESD Test                                              | Minimum Capability |

|-------------------------------------------------------|--------------------|

| HBM: Human Body Model, per MIL-STD-883 TM3015         | ±2kV               |

| CDM: Charged Device Model, per ANSI/ESDA/JEDEC JS-002 | ±TBDV              |

# 6 Operating Ratings

Performance is generally guaranteed over this range as further detailed below under Electrical Characteristics.

| Parameter                                                                                     | Min  | Max  | Units |

|-----------------------------------------------------------------------------------------------|------|------|-------|

| Line voltage (V <sub>LINE_x</sub> ) and load voltage (V <sub>LOAD_x</sub> ) relative to GND_x | 14   | 46   | V     |

| Continuous load current (ILOAD) for LX7714-25MFB (single channel)                             | -0.1 | 2.5  | Α     |

| Continuous load current (ILOAD) for LX7714-25MFB (two channels paralleled)                    | -0.2 | TBD  | Α     |

| Continuous load current (ILOAD) for LX7714-25MFB (three channels paralleled)                  | -0.3 | TBD  | Α     |

| Continuous load current (ILOAD) for LX7714-25MFB (four channels paralleled)                   | -0.4 | TBD  | Α     |

| Continuous load current (ILOAD) for LX7714-12MFB (single channel)                             | -0.1 | 1.25 | Α     |

| Logic input voltage (V <sub>CNTL_P_x</sub> , V <sub>CNTL_N_x</sub> ) relative to GND_x        | TBD  | TBD  | V     |

| Logic output voltage (VIN_RESET_x, VPWR_GOOD_x) relative to GND_x                             | TBD  | TBD  | V     |

| Output current (I <sub>IN_RESET_X</sub> , I <sub>PWR_GOOD_X</sub> ) for digital outputs       |      | TBD  | mA    |

### 7 Electrical Characteristics

The following specifications apply over the operating ambient temperature of -55°C  $\leq T_A \leq 125$ °C except where otherwise noted with the following test conditions:  $V_{\text{LINE}_x} = 28V$ ,  $V_{\text{CNTL}_P_x} = 5V$ ;  $V_{\text{CNTL}_N_x} = 0V$ ; external 10k $\Omega$  pullup resistor to 5V on IN\_RESET\_x and PWR\_GOOD\_x outputs. Typical parameters refer to  $T_J = 25$ °C. Positive currents flow into pins.

| Symbol                                        | Parameter                                                                                    | Test Conditions/Comments                                                                | Min  | Тур   | Max  | Units |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|-------|------|-------|

| <b>Operating Current</b>                      | (for one channel only)                                                                       |                                                                                         |      |       |      |       |

| I                                             | Normal current                                                                               |                                                                                         | -10  | -5    | 0    | mA    |

| I <sub>GND</sub>                              | Standby current                                                                              | $V_{CNTL_P_x} = 0V; V_{CNTL_N_x} = 5V$                                                  | -0.5 | -0.25 | 0    | mA    |

| POR Detection                                 |                                                                                              | · · · · · · · · · · · · · · · · · · ·                                                   |      |       |      | •     |

| V <sub>LINE</sub>                             | LINE power on reset<br>Threshold                                                             | Voltage rising relative to GND                                                          | 8    | 10    | 12   | V     |

| T <sub>POR</sub>                              | Power on reset delay                                                                         | Step V <sub>LINE_x</sub> to V <sub>LOAD_x</sub> = 5% of VLINE                           | 100  | 200   | 300  | μs    |

| Switch Characteris                            | stics                                                                                        |                                                                                         |      |       |      |       |

| \/                                            | Power switch voltage<br>drop LX7714-25MFB                                                    |                                                                                         |      |       | 250  | mV    |

| VLINE-LOAD                                    | Power switch voltage<br>drop LX7714-12MFB                                                    | Power switch voltage                                                                    |      |       | 500  | mV    |

| R <sub>LINE-LOAD</sub>                        | Power switch resistance<br>LX7714-25MFB                                                      | Between LINE x and LOAD x: Loss = 14                                                    |      |       | 250  | mΩ    |

| INLINE-LOAD                                   | Power switch resistance<br>LX7714-12MFB Between LINE_x and LOAD_x; I <sub>LOAD_x</sub> = -1A |                                                                                         |      |       | 500  | mΩ    |

| I <sub>LOAD</sub>                             | Power switch off leakage                                                                     | $V_{CNTL_P_x} - V_{CNTL_N_x} < 1.2V; V_{LOAD_x} = GND$                                  |      |       | 10   | μA    |

| toplay                                        | Turn off delay                                                                               | From CNTL_x_x to $V_{LOAD_x} = 23V$ , $I_{LOAD_x} = 1A$                                 | 7    | 50    | 150  | μs    |

| t <sub>delay</sub>                            | Turn on delay                                                                                | From CNTL_x_x to $V_{LOAD_x} = 5V$ , $I_{LOAD_x} = 1A$                                  | 5    | 30    | 100  | μs    |

| dV/dt <sub>LOAD</sub>                         | Rising load slew rate                                                                        | Off to On transition (20% to 80%)                                                       | 1.0  | 2.5   | 4.0  | V/ µs |

|                                               | Falling load slew rate                                                                       | On to Off transition (80% to 20%)                                                       | -4.0 | -2.5  | -1.0 | v/ µ5 |

|                                               | Load current limit<br>LX7714-25MFB                                                           | Momentary output fault                                                                  |      | 10    | 12.5 | А     |

| ILOAD                                         | Load current limit<br>LX7714-12MFB                                                           | Momentary output fault                                                                  |      | 5     | 6.2  | А     |

| I <sub>TRIP</sub>                             | Trip current LX7714-<br>25MFB                                                                | Continuous load current to guarantee trip                                               | >2.5 |       | 3.5  | А     |

| TRIP                                          | Trip current LX7714-<br>12MFB                                                                |                                                                                         |      |       | 1.75 | А     |

| Logic                                         |                                                                                              |                                                                                         |      |       |      |       |

| V <sub>CNTL_DIFF</sub>                        | Positive Differential Input<br>Logic Threshold                                               | V <sub>CNTL_P_x</sub> - V <sub>CNTL_N_x</sub> ; ON state                                | 2    |       |      | v     |

| VCNTL_DIFF                                    | Inverted Differential Input<br>Logic Threshold                                               | V <sub>CNTL_P_x</sub> - V <sub>CNTL_N_x</sub> ; OFF state                               |      |       | 0.8  | v     |

| V <sub>CNTL_OPEN</sub>                        | Open circuit voltage                                                                         | V <sub>CNTL_P_x</sub> - V <sub>CNTL_N_x</sub> ; less than ±100nA                        |      | 5     |      | V     |

| V <sub>CNTL_CM</sub>                          | Common Mode Range                                                                            | $(V_{CNTL_P_x} + V_{CNTL_N_x})/2; V_{CNTL_DIFF} = 2V$                                   | -6   |       | 9    | V     |

| I <sub>CNTL_P_x</sub>                         | Input Current                                                                                | $V_{CNTL_P_x} = 0V$                                                                     | -27  | -8    | -1   | μA    |

| I <sub>CNTL_N_x</sub>                         | Input Current                                                                                | $V_{CNTL_N_x} = 5V$                                                                     | -27  | -8    | -1   | μA    |

| I <sub>CNTL_P_x</sub> , I <sub>CNTL_N_x</sub> | Cold spare current                                                                           | $V_{\text{LINE}} = 0V$ ; $0V < V_{\text{CNTL}_{P_x}}$ or $V_{\text{CNTL}_{N_x}} < 5V$   | -12  |       | 12   | μA    |

| VIN_RESET,                                    |                                                                                              | High level; $10k\Omega$ external pullup resistor to 5V                                  | 4.7  |       | 5    |       |

| VIN_RESET,<br>Vpwr_good                       | Logic Output Levels                                                                          | Low output voltage; $I_{IN\_RESET}$ = 1mA and/or $I_{PWR\_GOOD}$ = 1mA                  | 0    |       | 0.3  | V     |

| In_reset, Ipwr_good                           | Cold spare current                                                                           | $V_{\text{LINE}} = 0V;$<br>$0V < V_{\text{IN RESET}}$ and/or $V_{\text{PWR GOOD}} < 5V$ | -1   |       | 1    | μA    |

| Symbol                  | Parameter                      | Test Conditions/Comments                                                                                   | Min  | Тур  | Max  | Units |  |

|-------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Timing                  |                                |                                                                                                            |      |      |      |       |  |

|                         |                                | CNTL_x_x to PWR_GOOD (with no fault)                                                                       | 0    | 10   | 100  | μs    |  |

| tsettling               | Turn on indicator              | From fault removal to PWR_GOOD_x.<br>Depends on when the fault is removed with<br>respect to hiccup timing |      |      | 15   | s     |  |

| t <sub>FAULT</sub>      | Fault indicator                | From application of short circuit fault to PWR_<br>GOOD_x and IN_RESET_x                                   | 0    | 0.1  | 1    | ms    |  |

| Tovld_int25             | Overload interrupt time at     | From application of 250% rated current to<br>current falling below 10% or rated current<br>LX7714-25MFB    | 0.37 | 0.73 | 1.34 | s     |  |

|                         | 250%                           | From application of 250% rated current to<br>current falling below 10% or rated current<br>LX7714-12MFB    | TBD  | TBD  | TBD  |       |  |

| T <sub>OVLD_INT40</sub> | Overload interrupt time at     | From application of 400% rated current to<br>current falling below 10% or rated current 23<br>LX7714-25MFB |      | 54   | 122  | - ms  |  |

|                         | 400%                           | From application of 400% rated current to<br>current falling below 10% or rated current<br>LX7714-12MFB    | TBD  | TBD  | TBD  | 1115  |  |

| <b>-</b>                | Overload interrupt time at     | From application of 600% rated current to                                                                  | 6    | 12   | 24   |       |  |

| T <sub>OVLD_INT60</sub> | 600%                           | From application of 600% rated current to                                                                  | TBD  | TBD  | TBD  | ms    |  |

| t <sub>COOL</sub>       | Hiccup cool down               | From LOAD_x fault to LOAD_x recovery                                                                       | 5    | 10   | 15   | S     |  |

| # <sub>HICCUP</sub>     | Maximum hiccup cycles          | Continuous cycles prior to shutdown                                                                        |      | 4096 |      | count |  |

| <b>Over Temperat</b>    | ture Detect                    |                                                                                                            |      |      |      |       |  |

| TEMP <sub>OT</sub>      | Over temperature threshold     | Shutdown (die temperature rising)                                                                          | 150  |      | 175  | °C    |  |

| TEMP <sub>OT</sub>      | Over temperature<br>hysteresis | Reset (die temperature falling)                                                                            |      | TBD  |      | °C    |  |

| t <sub>TEMP</sub>       | Reaction time                  | Delay from die temperature threshold event to<br>OT fault detection                                        |      | TBD  |      | ms    |  |

### 8 Thermal Properties

Thermal resistance,  $\theta_{JB}$ , is provided from die to the back surface of the package. Junction temperature  $T_J$  is calculated using  $T_J = T_B + (PD \times \theta_{JB})$ , where  $T_B$  is the temperature maintained on the back surface of the package.

| Package | Thermal Resistance | Тур | Units |

|---------|--------------------|-----|-------|

| CFP-28  | θ <sub>JB</sub>    | TBD | °C/W  |

### 9 Heatsink Recommendations

The LX7714 dissipates up to about 3W: ({250mV per output} x 2.5A x {4 circuits}) for the four switches at full load, plus (46V x 10mA) operating power and so thermal considerations are usually necessary. The base of the ceramic package should be used as the heat conducting surface for all but light duty applications. The metal package top is attached to the package body at the top of relatively thin cavity walls, and so has a much higher thermal resistance from the die than the base of the package. It is recommended to apply a thermal interface material between the base of the package and the heat dissipater can be copper layers within a multilayer circuit board to spread heat laterally across the board, or a direct mounted dissipation element.

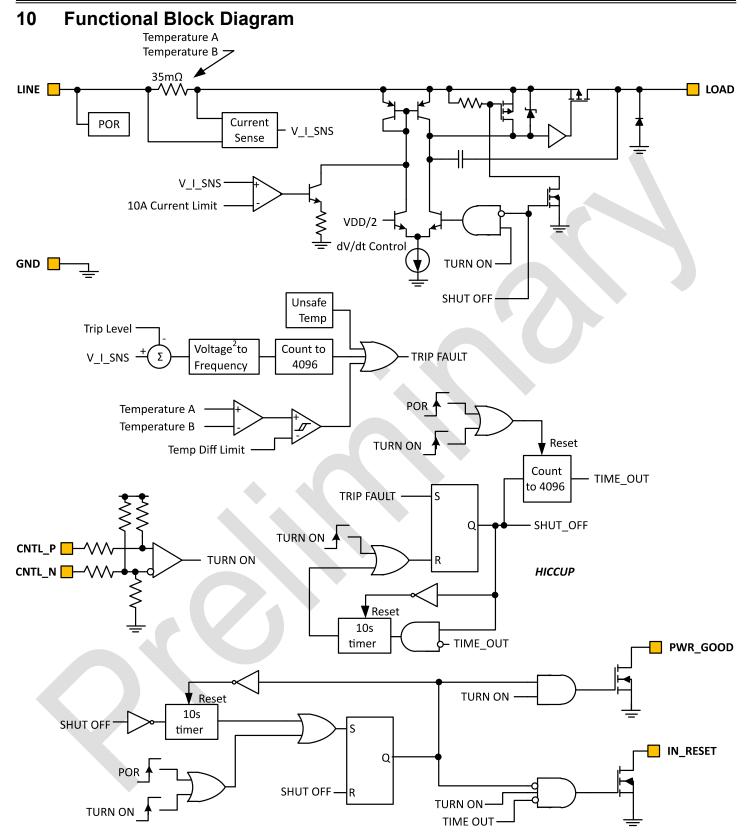

Figure 1. Functional Block Diagram (One of four independent circuits)

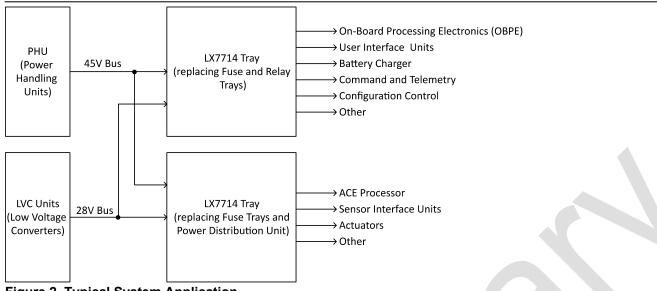

Figure 2. Typical System Application

### 11 LX7714 Operation

### 11.1 General Design Architecture

The LX7714 comprises 4 identical die mounted on electrically isolated pads within a common package. Each die contains a protected power switch section capable of driving a load up to 1.25A (LX7714-12MFB) or 2.5A (LX7714-25MFB).

The functional block architecture is shown in Figure 1 on page 7. The major functional blocks are:

- PMOS power switch with rise time control and maximum current limit

- On and off controls (CTRL\_P\_x and CTRL\_N\_x)

- Fault detection

- · Fault management, status outputs, and hiccup mode timing

#### 11.2 PMOS Power Switch

The power switch consists of a P channel MOSFET in series with a current sense resistor connecting LINE\_x to LOAD\_x pins. An internal current limit circuit limits the load current when the voltage drop across the sense resistor exceeds 350mV. The slew rate of the PMOS power switch turning on and off is controlled to  $\pm 1V/\mu$ s, whether the power switch is enabled on application of LINE\_x power or controlled after power-up by the CTRL\_P\_x and CTRL\_N\_x logic inputs.

The four power switch sections may be paralleled in any permutation to increase load current carrying capability. The CTRL\_P\_x and CTRL\_N\_x logic inputs for paralleled power sections must be paralleled also, to ensure that paralleled power switches turn on and off together. For example, one LX7714-25MFB package can be configured to provide a single 10A switch, two 5A switches, or a 7.5A switch plus a 2.5A switch. The intrinsic positive temperature coefficient of the PMOS power switch aids current sharing, presuming that the package base is evenly attached to a heat dissipater.

### 11.3 On and Off Controls

The differential CTRL\_P\_x and CTRL\_N\_x logic inputs turn the respective power switch on and off. A positive differential control signal (CTRL\_P\_x = high, CTRL\_N\_x = low) turns the power switch on. An inverted differential control signal (CTRL\_P\_x = low, CTRL\_N\_x = high) turns the power switch off. The TTL 0.8V/2V input voltage levels are compatible with both 3.3V and 5V signal levels

Each control input includes an internal weak pullup (1 to 27µA) to an internal nominal 10V rail. Each power switch defaults to the ON state when both its CTRL\_P\_x and CTRL\_N\_x inputs are open circuit, achieved by internal biasing.

#### 11.3.1 DIFFERENTIAL SIGNALING

The -7V to +12V input voltage range is compatible with standard EIA-485 and EIA-422A differential signaling. Switching logic with a differential signal connection is shown in Table 1 below.

Fitting a  $100k\Omega$  (or as appropriate) pulldown resistor from CTRL\_N\_x to GND improves noise immunity for the power switch defaulting to the ON state, when both CTRL\_P\_x and CTRL\_N\_x inputs are open circuit.

Fitting a  $100k\Omega$  (or lower) pulldown resistor from CTRL\_P\_x to GND causes the power switch to default to the OFF state when both CTRL\_P\_x and CTRL\_N\_x inputs are open circuit. The resistor pulls the open circuit CTRL\_P\_x down towards GND (sinking 1 to  $27\mu$ A), while the open circuit CTRL\_N\_x input is internally pulled up to about 10V.

| CNTL_P_x                               | Power Switch Condition                            |     |

|----------------------------------------|---------------------------------------------------|-----|

| Specification                          | Example Operation                                 |     |

| $V_{CNTL_P_x} - V_{CNTL_N_x} \le 0.8V$ | $V_{CNTL_P_x}$ = GND, $V_{CNTL_N_x}$ = 3.3V or 5V | OFF |

| $V_{CNTL_P_x} - V_{CNTL_N_x} \ge 2V$   | $V_{CNTL_P_x}$ = 3.3V or 5V, $V_{CNTL_N_x}$ = GND | ON  |

Table 1. CTRL\_P\_x and CTRL\_N\_x Logic Inputs Truth Table (Differential Signaling)

#### 11.3.2 SINGLE-ENDED SIGNALING

Connect CTRL\_N\_x to GND to use a single logic output connected to CTRL\_P\_x as the active-high control signal. (Table 2 below). A power switch will default to the ON state when the CTRL\_P\_x input is open circuit since the open circuit CTRL\_P\_x input will be internally pulled up to about 10V while the CTRL\_N\_x input is grounded.

| CNTL_P_x                           | CNTL_N_x | <b>Power Switch Condition</b> | Default with CNTL_P_x = Hi-Z |

|------------------------------------|----------|-------------------------------|------------------------------|

| Logic high: $V_{CNTL_P_x} \ge 2V$  | GND      | ON                            | Power switch ON              |

| Logic low: $V_{CNTL_P_x} \le 0.8V$ | GND      | OFF                           | Tower switch ON              |

#### Table 2. CTRL\_P\_x and CTRL\_N\_x Logic Inputs Truth Table (Control by Single Active High Logic Level)

Table 3 below shows the truth table to use a single logic output connected to  $CTRL_N_x$  for an active-low control signal. Bias  $CTRL_P_x$  to 3V with a potential divider to an appropriate supply. A power switch will default to the OFF state when the  $CTRL_N_x$  input is open circuit, since the open circuit  $CTRL_N_x$  input will be internally pulled up to about 10V while the  $CTRL_P_x$  input is connected to 3V or lower, depending on the condition of the bias supply.

| CNTL_P_x                    | CNTL_N_x (3.3V or 5V logic)                            | <b>Power Switch Condition</b> | Default with CNTL_N_x = Hi-Z |

|-----------------------------|--------------------------------------------------------|-------------------------------|------------------------------|

| Bias to V <sub>B</sub> = 3V | $V_{CNTL_N_x} = Iow. V_B - V_{CNTL_N_x} \ge 2V$        | ON                            | Power switch OFF             |

|                             | $V_{CNTL_N_x}$ = high. $V_B$ - $V_{CNTL_N_x} \le 0.8V$ | OFF                           | Tower switch Of T            |

Table 3. CTRL\_P\_x and CTRL\_N\_x Logic Inputs Truth Table (Control by Single Active Low Logic Level)

#### 11.4 Fault Detection

The circuit breaker can be tripped in one of three ways depending on the type of fault:

- If the LX7714 becomes detached from the heat sink and overheats, it will trigger an internal over-temperature shutdown somewhere between 150°C and 175°C

- A hard overload will cause the LX7714 to current limit, increasing dissipation in the power switch. A differential temperature sensor with a  $k_{H} = i^{2}t$  profile detects the fault before the die overheats

- A soft overload current is processed with a k<sub>L</sub> = i<sup>2</sup>t profile to provide a trip time inversely proportional to the square of the current in excess of the rated current

### 11.5 Fault Management, Status Outputs, and Hiccup Mode Timing

Two active low, open drain logic outputs PWR\_GOOD\_x and IN\_RESET\_x indicate the state of the power switch:

- When the power switch is off, both PWR\_GOOD\_x and IN\_RESET\_x are high-Z

- When the power switch is on, and operating normally, PWR\_GOOD\_x is active low and IN\_RESET\_x is high-Z

PWR GOOD x and IN RESET x may be indeterminate during turn-on into a heavy load as the current limits

- When a fault occurs PWR GOOD x is high-Z, and IN RESET x is active low during automatic fault recovery

When a fault occurs, the LX7714 enters hiccup mode. Hiccup mode begins by turning off the power switch, followed by a 10 second cool off period. Then the power switch will attempt to ramp up the output voltage. If the fault is still present, it will be sensed and the hiccup cycle will repeat. Hiccup cycles repeat for up to 4096 attempts, after which the power switch remains latched off. The power switch can be reset back to normal operation by either toggling the power input LINE\_x, or by toggling the control signals CTRL\_P\_x and CTRL\_P\_x off and then back on again.

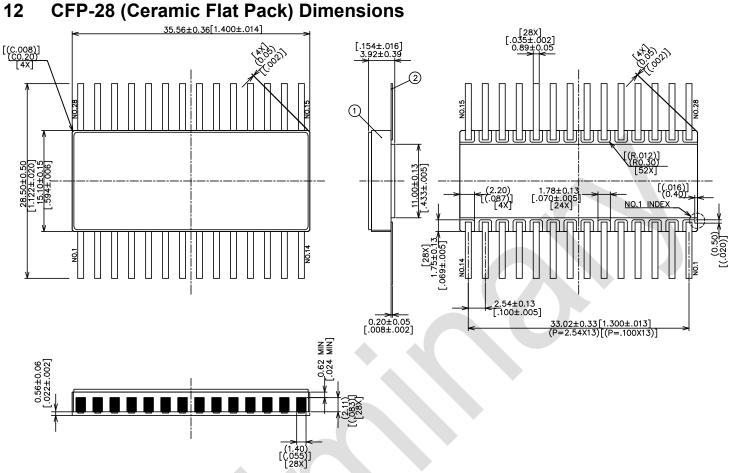

Figure 3. CFP-28 Package Dimensions

Note:

- 1. Controlling dimensions are in mm. Imperial (inch) equivalents are shown for general information

- 2. Parts are shipped with unformed leads

- 3. Package mass is 6.5g typical with un-cropped leads

- 4. Ceramic package body is NTK BA-914 HTCC Alumina (Al<sub>2</sub>O<sub>3</sub>)

- 5. Lead and lid material are Kovar with NiAu plating (nickel under-plate followed by gold plating)

- 6. Lid is electrically isolated from the leads, and is bonded hermetically to the ceramic body using AuSn solder

- 7. Use the base of the package as the surface for conducting heat from the package. The lid is attached to the package body at the top of relatively thin cavity walls, and so is inferior to the base of the package for heat removal. The leads can be formed to mount the package upside down on the PCB if convenient

# 13 Revision History

### 13.1 Revision 0.3 - January 2021

Pre-release. Changes not logged.

### 13.2 Revision 1 - xxx 2021

First release.

### The Microchip Website

Microchip provides online support via our website at <u>http://www.microchip.com/</u>. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to http://www.microchip.com/pcn and follow the registration instructions.

### **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: http://www.microchip.com/support

### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their Microchip Data Sheet

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions

- There are dishonest and possibly illegal methods used to breach the code protection feature. All these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable"

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

### Legal Notice

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

### **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit http://www.microchip.com/quality.

# Worldwide Sales and Service

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/support Web Address: http://www.microchip.com Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455 Austin, TX Tel: 512-257-3370 Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088 Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075 Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924 Detroit Novi. MI Tel: 248-848-4000 Houston, TX Tel: 281-894-5983 Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380 Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800 Raleigh, NC Tel: 919-844-7510 New York, NY Tel: 631-435-6000 San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270 Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

ASIA/PACIFIC Australia - Sydney Tel: 61-2-9868-6733 China - Beijing Tel: 86-10-8569-7000 China - Chengdu Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588 China - Dongguan Tel: 86-769-8702-9880 China - Guangzhou Tel: 86-20-8755-8029 China - Hangzhou Tel: 86-571-8792-8115 China - Hong Kong SAR Tel: 852-2943-5100 China - Nanjing Tel: 86-25-8473-2460 China - Qingdao Tel: 86-532-8502-7355 China - Shanghai Tel: 86-21-3326-8000 China - Shenyang Tel: 86-24-2334-2829 China - Shenzhen Tel: 86-755-8864-2200 China - Suzhou Tel: 86-186-6233-1526 China - Wuhan Tel: 86-27-5980-5300 China - Xian Tel: 86-29-8833-7252 China - Xiamen Tel: 86-592-2388138 China - Zhuhai Tel: 86-756-3210040

India - Bangalore Tel: 91-80-3090-4444 India - New Delhi Tel: 91-11-4160-8631 India - Pune Tel: 91-20-4121-0141 Japan - Osaka Tel: 81-6-6152-7160 Japan - Tokyo Tel: 81-3-6880- 3770 Korea - Daegu Tel: 82-53-744-4301 Korea - Seoul Tel: 82-2-554-7200 Malaysia - Kuala Lumpur Tel: 60-3-7651-7906 Malaysia - Penang Tel: 60-4-227-8870 Philippines - Manila Tel: 63-2-634-9065 Singapore Tel: 65-6334-8870 Taiwan - Hsin Chu Tel: 886-3-577-8366 Taiwan - Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei Tel: 886-2-2508-8600 Thailand - Bangkok Tel: 66-2-694-1351 Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

ASIA/PACIFIC

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829 Finland - Espoo Tel: 358-9-4520-820 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany - Garching Tel: 49-8931-9700 Germany - Haan Tel: 49-2129-3766400 Germany - Heilbronn Tel: 49-7131-72400 Germany - Karlsruhe Tel: 49-721-625370 Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44 Germany - Rosenheim Tel: 49-8031-354-560 Israel - Ra'anana Tel: 972-9-744-7705 Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781 Italy - Padova Tel: 39-049-7625286 **Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340 Norway - Trondheim Tel: 47-72884388 Poland - Warsaw Tel: 48-22-3325737 Romania - Bucharest Tel: 40-21-407-87-50 Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 Sweden - Gothenberg Tel: 46-31-704-60-40 Sweden - Stockholm Tel: 46-8-5090-4654 UK - Wokingham Tel: 44-118-921-5800 Fax: 44-118-921-5820