## **AN19**

# LX1672 PRODUCT DESIGN GUIDE

Protected by US Patents: 6,285,571 & 6,292,378

### **TABLE OF CONTENTS**

### Sections

| 1.0  | Introduction                        | 3   |

|------|-------------------------------------|-----|

| 2.0  | Theory Of Operation                 |     |

| 3.0  | Bootstrap                           |     |

| 4.0  | Soft Start and Enable               | 7   |

| 5.0  | Over Current Protection             | 8   |

| 6.0  | Component Selection                 | 8   |

| 7.0  | FET Selection                       |     |

| 8.0  | Upper FET Power Dissipation         |     |

| 9.0  | Lower FET Power Dissipation         | 9   |

| 10.0 | General FET Considerations          | 9   |

|      | ) FET Gate Drive                    |     |

| 12.0 | FET Thermal Considerations          | .10 |

| 13.0 | Inductor Selection                  | .11 |

| 14.0 | Output Capacitor Selection          | .12 |

| 15.0 | Input Capacitor Selection           | .12 |

| 16.0 | ) Efficiency                        | .13 |

|      | Loop Compensation                   |     |

|      | Transient Response                  |     |

|      | Circuit Board Layout                |     |

|      | Bi-Phase PWM Current Sharing        |     |

|      | ) LoadSHARE                         |     |

|      | Other Multiphase Methods            |     |

| 23.0 | DDR VTT Termination Supply          | .20 |

| Figu | ros                                 |     |

| _    |                                     | _   |

|      | Synchronous Buck Regulator          |     |

|      | PWM Block Diagram4                  |     |

|      | Buck Regulator Waveforms            |     |

|      | Bootstrap Circuit                   |     |

|      | Simplified Soft Start Circuit       |     |

|      | Over Current Protection             |     |

|      | RMS Ripple Current                  |     |

|      | Rode Plot                           |     |

|      | Control Loop Block Diagram          |     |

|      | PWM Switch and Output Filter        |     |

|      | _oadSHARE Block diagram             |     |

| 401  | and CHADE Uning Industry ECD Mothod | 10  |

|      | LoadSHARE Using Inductor ESR Method |     |

| 13 l | LoadSHARE Using Inductor ESR Method | .17 |

### 1.0 Introduction

This document is intended to be used with the LX1672 data sheet as a guide to designing buck regulators with the LX1672 controller. Information is presented on operation of the complete circuit and selection of critical components that should allow the design of a complete regulator.

### 2.0 THEORY OF OPERATION

Buck regulators are used in a variety of applications where the input must be stepped down to a lower output voltage. The increasing power demands of microprocessors and their support chips require power levels that would be impractical with linear regulators. The demand for better efficiency is another driving factor in the use of switching regulators. The LX1672 contains two synchronous buck regulators in a single package.

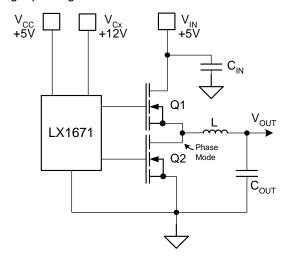

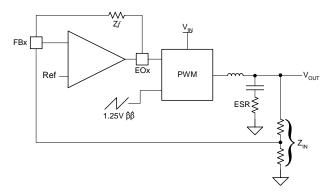

Figure (1) - Synchronous Buck Regulator

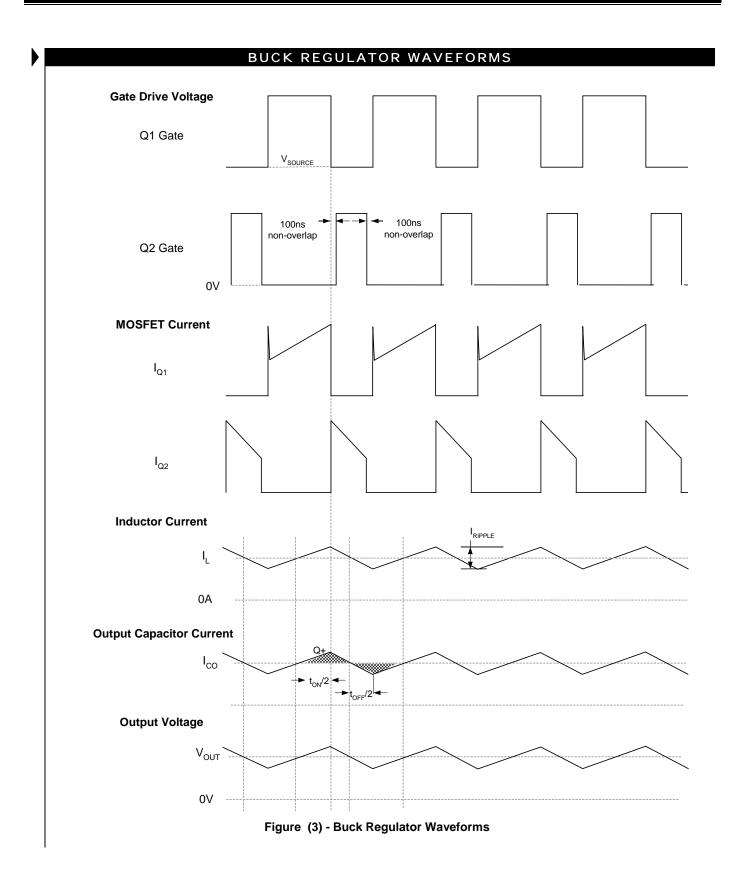

The inductor is used as an energy storage device and acts as a current source. When the main FET (Q1) is turned on, current from the input flows through the inductor and into the load. When the output voltage reaches the control point, the main FET (Q1) will be turned off and the sync FET (Q2) will be driven on. There is a short non-overlap period at all switching transitions to insure that there can be no instance where both FETs are on at the same time.

Both FETs are constantly switching at the PWM frequency to maintain regulation.

The control loop consists of an error amplifier with the non-inverting input connected to a reference voltage and the inverting input connected to the output voltage through a resistor network that determines the output voltage.

The error amplifier output is used to drive a comparator with a voltage ramp on its other input. The error amplifier output will move up and down on the ramp voltage causing the comparator to generate a timing signal that determines the PWM duty cycle. See Figure (2a)

Since the inductor current cannot change instantly when the main FET switches off the body diode in the sync FET will conduct and current will flow up from ground to maintain the inductor current at its previous value. Inductor current ramps up at a linear rate when Q1 is on and down at a linear rate when Q2 is on because in both cases there is constant voltage forcing function.

When the body diode is conducting there will be a negative voltage on the drain of Q2 due to the direction of current flow and the body diode drop. The voltage drop across the source to drain will be much less than across the diode. Hence, when Q2 turns on the phase node voltage (Q1 source - Q2 drain) will be approximately equal to ground.

When Q1 turns on, the body diode of Q2 is still conducting so current must be commutated from the diode to the upper FET. Due to slow recovery time and stored charge in the Q2 body diode a current spike will be present on the leading edge of Q1 drain current. This condition can be greatly helped by putting a Schottky diode in parallel with the synchronous FET.

Figure (3) shows some waveforms at key nodes. High frequency details have been omitted for ease of understanding.

The inductor also works with the output capacitor to form a low pass filter that filters the voltage pulses present on the phase node and results in a clean DC output. The voltage on the top of the output capacitor is a saw-tooth that is centered on the output voltage and has an amplitude equal to the inductor ripple current times the capacitor ESR.

#

APPLICATION INFORMATION (CONTINUED)

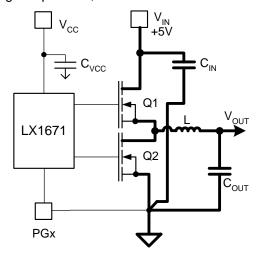

Figure (2a) PWM Block Diagram Phase 1

PWGD (MLP Only)

SS/ENABLE

DIS1

# APPLICATION INFORMATION (CONTINUED) Restricted by the second of the sec

Figure (2b) - PWM Block Diagram Phase 2 Connected in LoadSHARE mode

### 3.0 BOOTSTRAP

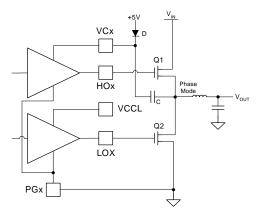

The bootstrap circuit will add approximately 5 volts to the PWM input (high side FET drain) to provide sufficient voltage to enhance the high side FET. See Figure (4a)

The bootstrap circuit consists of a capacitor (C) that charges to 5 volts through the bootstrap diode (D) when the lower FET (Q2) turns on. When the upper FET (Q1) turns on, the five volt charge on the capacitor is coupled to the VCX pin and added to the FET source voltage. This back biases the diode to allow the VCX pin to float up to Q1 source potential plus 5 volts. The diode must have a low stored charge to prevent partial discharge of the capacitor, Schottky diodes are quite often used for this reason. The capacitor must store enough charge over a PWM cycle to keep the driver supply voltage from drooping. For most applications a .1 uf capacitor is sufficient. As long as the bootstrap capacitor is substantially larger than the FET input capacitance it will store enough charge for proper operation. A value that is 50 to 100 times the FET gate capacitance (Ciss) will be adequate.

Figure (4a) - Bootstrap Circuit

When using this bootstrap configuration the voltage on the VCX pin is a square wave between the PWM input voltage and +5 volts.

The LX1672 LDO power comes from the VC1 pin and if a bootstrap circuit is used for phase 1 the LDO supply will not be a filtered DC and the LDO will not function properly. A solution is to use the rectifier / filter in Figure 4b which will give a clean DC output due to the second diode and capacitor.

When using the bootstrap or rectifier / filter the voltage on the VCX pin must not reach a level where excessive current will flow into the internal zener diodes on the VCX pins.

Figure (4b) - Bootstrap with Rectifier / Filter

### 4.0 SOFT START, ENABLE

Each PWM phase has a soft start pin SSX that is used to connect an external soft start capacitor Css. Css is charged by an internal  $20 \text{K}\Omega$  resistor (Rss) connected to the reference voltage. The SSX pin also provides an enable function, holding the SSX pin low disables the corresponding phase.

The LDO has an enable pin LDDIS that disables the LDO output when it is held high.

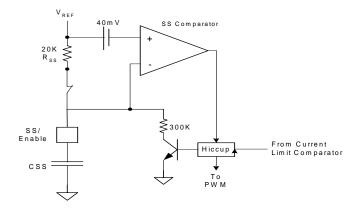

Figure (5) - Simplified Soft Start

At power on the under voltage lockout conditions, see data sheet for values, for VCC, VCCL and VCX must be met before Css will begin to charge. The output voltage will then increase from zero volts towards Vout and track the Css voltage until the soft start circuit is switched out after three time constants of Rss-Css. The three time constants allow Vout to be within 95% of the correct value at the termination of soft start, an internal comparator monitors the soft start pin and terminates the soft start cycle.

During the soft start ramp period the Over Current Protection is functional but the hiccup function is disabled till the soft start interval is complete.

When the soft start interval begins the PWM is disabled. No PWM pulses will be generated until the ramp has reached a 300mV level where a comparator enables the PWM. This will result in a current spike into the output capacitor that may result in a series of over current commands for a few cycles until the output capacitor has charged up to the same level as the soft start ramp.

If more than one phase is using the same input rail then the soft start timing should insure that they do not come up at the same time to prevent loading the input during startup. If phases 1 and 2 are used in Bi-Phase phase 2 is controlled by the output of phase 1 so it automatically tracks the rise in phase 1 output, however a phase 2 soft start capacitor is still required to insure that the internal comparator for phase 2 does not attempt to terminate the start up sequence early.

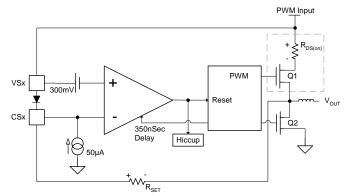

### 5.0 OVER CURRENT PROTECTION AND HICCUP

The external resistor  $R_{\text{SET}}$  along with Q1  $R_{\text{DS(ON)}}$  will determine the current limit set point. See Figure (6), the voltage drop across Q1  $R_{\text{DS(ON)}}$  plus the drop developed across  $R_{\text{SET}}$  by the internal 50uA current source must exceed the internal 300 mv threshold to initiate a current limit. There is a 350nSec delay in the current limit comparator to prevent false triggering due to ringing and noise. Note that the  $R_{\text{DS(ON)}}$  of any FET has a positive temperature coefficient, be sure to use the value corresponding to the expected operating temperature, usually at least 100 ° C, at the FET die. Once the upper FET  $R_{\text{DS(ON)}}$  is known the value of  $R_{\text{SET}}$  can be calculated.

$$R_{SET} = \frac{300 \,\text{mV} - \left(I_{CL} \times R_{DS(ON)}\right)}{50 \,\text{uA}}$$

Where I<sub>CL</sub> is the current limit threshold.

Note: The minimum value for  $R_{SET}$  is 1K $\Omega$  to prevent damage to the LX1672 input, the maximum value is 6K $\Omega$  where V<sub>CL</sub> equals zero (50uA x 6K $\Omega$  = 300mV).

At low duty cycles where the upper gate drive is less than 350nS wide the 350nS delay for current limit enable may result in current pulses exceeding the desired current limit set point. If the upper MOSFET on time is less than 350nS and a short circuit condition occurs, the duty cycle will increase since Vout will be low. The current limit circuit will be enabled when the upper gate drive exceeds 350nS. The actual peak current limit value will be higher than calculated with the above equation.

Short circuit protection still exists due to the narrow pulse width even though the magnitude of the current pulses will be higher than the calculated value.

Figure (6) - Over Current Protection

The  $R_{\text{SET}}$  resistor and VCs pin should be as close to a Kelvin connection to the FET source and drain terminals as possible. Very low  $R_{\text{DS(ON)}}$  values will result is significant errors otherwise.

The Over Current Protection is functional during the soft start ramp period. If currents in access of  $I_{CL}$  are detected the PWM will be commanded off for the remainder of that cycle but will restart on the next PWM cycle.

If no current limit is wanted the  $R_{\text{SET}}$  resistor can be left out and the CSX and VSX pins connected together and tied to VCC. A floating VSX pin will result in operation resembling a hiccup condition.

The hiccup function is disabled during the soft start ramp period. Once the soft start ramp has been terminated the hiccup function will be enabled. If an over current command is issued after the termination of soft start the soft start capacitor will be pulled low by the  $300 \text{K}\Omega$  resistor, Figure 5, the switch in series with RSS will open during this time to allow discharging CSS. The voltage on CSS will drop till it reaches a lower limit of 200 mV when a comparator will begin the soft start interval again.

The hiccup process will continue indefinitely if the load is greater than the current limit threshold determined by  $R_{\text{SET}}$ .

### **6.0 COMPONENT SELECTION**

Component selection in a DC to DC converter requires a lot of consideration and tradeoffs since there are a number of conflicting requirements such as size, cost, and performance. The components that are the most critical and require the most effort are the switching FETs , inductor , and input / output capacitors. The output filter is generally designed with output ripple and load transients as the main consideration but it has a very important role in loop compensation that should be considered.

The LX1672 is a voltage-mode controller intended for use in the continuous mode (i.e., inductor current never reaches zero). All equations presented in this document are based on these conditions.

### 7.0 FET SELECTION

Because the PWM FETs are the primary active power handling components they must be carefully chosen and properly sized for the power that will be dissipated. In many cases the main and synchronous FETs can be the same part number but as switching frequencies and currents become higher it is often desirable to use different devices that are optimized for each circuit application. The upper FET is commonly called the main switch and the lower FET is typically referred to as the synchronous switch since it is used as a synchronous rectifier.

Eq (1) Main FET Duty cycle

$$D = \frac{V_{OUT}}{V_{IN}}$$

Eq (2) Sync FET Duty Cycle

$$= \frac{V_{IN} - V_{OUT}}{V_{IN}} = 1 - \frac{V_{OUT}}{V_{IN}} = 1 - D$$

In a buck regulator topology there are no high transients that require a drain to source voltage much in access of the PWM input voltage. On resistance, maximum drain current, and thermal performance are closely related and must be considered together. Thermal management is a key element in a buck regulator design and requires careful component selection and board layout. The gate threshold voltage must be low enough to guaranty that the FET will be fully enhanced with the available gate drive voltage. Gate charge, Qg, should be less that 40nC.

### **8.0 Upper FET Power Dissipation**

The power dissipation in the upper FET, Q1 is the sum of the switching loss and conduction or I<sup>2</sup> R loss. As a close approximation it can be assumed that the current through the upper FET is a linear ramp during the switching interval.

Eq (3)

$$P_{Q1} = \left[ \left( \frac{I_{D}}{2} \right) \times V_{IN} \times \left( t_{r} + t_{f} \right) \times f \right] + \left[ I_{D}^{2} \times R_{DS(on)} \times D \right]$$

Where  $I_D$  is the FET drain current, tr and tf are the rise and fall times, f is the PWM switching frequency, and D is the duty cycle. For some typical numbers we will pick:

- Vin = 5 V

- Vout = 1.5 V

- lout = 5 A

This gives a duty cycle of (1.5V)/(5VA) = 0.3 or 30%. Using the Si4842DY with the circuit values given above, the switching loss in the main FET is [(5/2)(5)(80nS + 80nS) (300KHz) = 0.60W. Note: These turn on and off times are approximate in-circuit values. Using RDS(ON) at 100 °C the conduction loss is  $(5A^2)(0.0084\Omega)(0.3) = 0.063W$ .

Total main FET power dissipation equals (0.60+0.063) = 0.663W.

### 9.0 LOWER FET POWER DISSIPATION

The lower FET has no significant switching loss due to the parallel diode. All power dissipation is from the I<sup>2</sup>R loss during conduction; the formula for power dissipation reduces to:

Eq (4)

$$P_{Q2} = \left[ I_D^2 \times R_{DS(on)} \times (1 - D) \right]$$

With the previous operating conditions, the conduction loss equals  $(5A^2 \times .0084\Omega) \times (1-0.3) = 0.147W$ . The sync FET body diode will start to conduct immediately after the main FET turns off and before the synchronous FET turns on. Hence, there is always a short non-overlap period to prevent simultaneous conduction of both FETs. The body diode causes the sync FET to transition with a low drain to source voltage while the main FET transitions with a drain to source voltage of approximately Vin. When the synchronous FET turns off, the body diode will conduct for a short period of time before the main FET turns on. Due to this it is assumed that the switching losses in the synchronous FET are negligible. There is some power dissipation in the body diode but the conduction time is so short that these losses are also very low. The body diode in most FETs is a very non-ideal diode with a long recovery time and high stored charge.

### **10.0 GENERAL FET CONSIDERATIONS**

In the above example the  $I^2R$  losses in the main FET are less than one half that of the synchronous FET (i.e., the switching losses are dominate). Note that the temperature, drain current, and gate-to-source voltage all have an effect upon the  $R_{DS(ON)}$  value and should be taken into account. A common practice is to pick a main FET that is optimized for switching losses and a sync FET that has low  $R_{DS(ON)}$  to minimize conduction losses. As currents get higher it is possible to parallel several FETs to get a lower effective  $R_{DS(ON)}$  and spread the heat over a larger area to get better heat sinking from the circuit board.

The reverse transfer capacitance, Crss, is another critical parameter that effects FET switching by requiring more gate drive. Also when the upper FET turns on it will attempt to pull the lower gate high through Crss of the lower FET. If this effect is to great the lower FET can turn back on causing cross conduction.

### 11.0 FET GATE DRIVE

Any FET used in a switching application should have a low total gate charge to minimize the peak current required to charge and discharge the gate capacitance each cycle. If the gate charge is too high it places a greater demand on the driver causing possible thermal problems and slow switching. Increasing FET transition times further degrades the circuit's switching losses. The FET drivers in the LX1672 must charge and discharge the input capacitance of the external FET switches on every PWM cycle. Due to the very fast switching times needed for efficiency, the peak current required to charge the gate is significant. Charging a 2500pf gate capacitor to 5 volts in 50ns requires an average current of 0.25A. This current flows through the controller output transistors and results in internal power dissipation. It is common to use total gate charge rather that gate capacitance to calculate drive power. As a guideline 40nC should be considered the maximum FET input charge to be driven. The input capacitance of a FET is not a simple capacitor but rather a combination of several internal capacitors that change value with operating conditions. FET data sheets show a total gate charge Qg that accounts for this complexity and can be used to calculate the power required to drive the gate.

The charge on a capacitor is:

Eq (5)

$$Q = CV$$

The power required to charge a capacitor is:

Eq (6)

$$P = CV^2 f$$

By substituting terms the power required to drive the FET gate is:

Eq (7)

$$P = QgV f$$

Where Qg is the total gate capacitance from the FET data sheet, V is gate drive voltage, and f is the PWM frequency.

The LX1672 evaluation board is typically delivered from the factory with the lower gate drivers powered by 5 volts on the VCCL pin. The upper gate drivers for phase 1 and 2 (VC1 and VC2) are connected to 12

volts. Using these numbers we can calculate the power required to drive the FETs. Assuming a gate charge of 40nC and a 300KHz LX1672 we have:

- Lower gate drivers = 40nC x 5V x 300KHz = 60mW each.

- Upper drivers phase 1 and 2 = 40nC x 12V x 300KHz = 144mW each.

- The total gate drive power is 2(60)+(2)144mW = 408mW.

With Vcc at 5 volts and an lcc of 15ma there is an additional 75mW of package dissipation that must be added to the 408mW for gate drive. This equals 483 mW total for the LX1672 TSSOP package. The data sheet specifies the TSSOP package junction-to-ambient ( $\theta$ ja) thermal resistance at 85°C per watt. This value assumes that the TSSOP package is mounted to a circuit board. The junction temperature can be calculated from:

Eq (8)

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Assuming an ambient temperature of 23°C we get a junction temperature of:

$$T_I = 23 + (.483 \times 85) = 64C$$

The 150°C maximum operating junction temperature allows a maximum rise of:

$$150 - 64 = 86^{\circ}$$

C.

It is clear from the above that all output driver stages should be operated on the lowest voltage that will properly enhance the FETs.

The LX1672 can be operated with up to 16 volts DC on the VCCL pin but that would be inadvisable from a power dissipation perspective.

### 12.0 FET THERMAL CONSIDERATIONS

Since it is always desirable to avoid the use of heat sinks (other than the circuit board itself) careful consideration should be given to component selection and layout from a thermal point of view. FET package selection is a significant part of the overall thermal picture and has a significant effect on thermal performance. For example, large cases like the D² package have a much lower junction to circuit board thermal resistance than the popular S08.

Another popular surface mount package is the D pack slightly smaller than the D<sup>2</sup> and has a corresponding lower current handling capability. The tried and true

TO220 is always worth looking at if the mounting tab is acceptable, it is a low cost package with good performance. The TO220 is quite often used with no heat sink on the tab but the thermal resistance to air is fairly high so this requires careful consideration. For surface mount components the maximum allowable thermal resistance from the circuit board to air  $R\theta_{\text{(CB-A)}}$  can be calculated by.

$$R\theta_{(CB-A)} \leq \frac{\left(T_{J}max - T_{A}max\right)}{P_{D}max} - R\theta_{(J-C)}$$

Eq (9)

This formula assumes that the FET case and the circuit board are at the exact same temperature which is valid only for surface mount components. Once the power dissipation of each FET has been determined and a maximum operating junction temperature chosen the required thermal resistance of the circuit board to air can be calculated.

If we look at the example where an Si4842DY FET dissipates 1 watt at a maximum ambient of 85  $^{\circ}$  C, and allow the junction temperature to reach the maximum data sheet spec of 150  $^{\circ}$  C,  $\theta$ j-c of the Si4842DY is 16 $^{\circ}$  C per watt.

$$R\theta_{(CB-A)} \le \frac{(150-85)}{1} - 16 = 49^{\circ} C/W$$

The circuit board to air thermal resistance  $R\theta_{(CB-A)}$  must be less than 49 degrees C per watt. The thermal resistance to air of a 1 in² circuit board, with properly designed copper power and ground planes to help spread the heat, will typically be 45°C per watt. Keep in mind that adjacent heat generating components will add to the thermal load on the circuit board and require more area. Small clip-on heat sinks and airflow will help reduce component heat dissipation considerably.

### 13.0 INDUCTOR SELECTION

The inductor is usually one of the largest components in a buck regulator and has a large influence on performance. There are two loss mechanisms copper loss and core loss both of which must be considered in order to maximize circuit efficiency. Since it is often desirable to use off the shelf components some compromises are usually made with the inductor. Selecting an inductor with a low series resistance is always desirable. Further, make sure that the core material will perform properly at the PWM switching frequency.

The core must be able to handle the maximum output current plus one half of the ripple current without a significant drop in inductance. If the core is allowed to saturate, the inductance will drop dramatically and result in a significant increase in ripple current.

A lower inductance value will provide better transient response and a smaller package at the expense of increasing the ripple current. As the inductance value transient response degrades increases. component size increases; however, the ripple current decreases. Ripple current is an important factor since it must flow into the output filter capacitor and will result in an output ripple voltage that is the product of the capacitor ESR and the inductor ripple current. Inductor ripple current is usually set to be within 10% to 30% of the output current and typical inductance values range from 1 to 10uH. The output inductor and capacitor play a critical role in determining overall regulator performance. Hence, it may be necessary to do an iterative design if the first inductor choice results in an unacceptable capacitor value. The relationship for voltage across an inductor takes the well recognized form of:

$$V = L \frac{di}{dt} \label{eq:V}$$

Eq (10)

In a buck regulator the forcing function is always a constant voltage source resulting in a linear ramp of current so we can use the  $\Delta I$  and  $\Delta T$  terms rather than be concerned with integrating a nonlinear function. The rate of change, or slew rate, that can be achieved for an inductor is then

$$\Delta I = \frac{V\Delta \, t}{L} \label{eq:deltaI}$$

Eq (11)

Substituting terms used in a buck PWM regulator

$$\Delta I = \frac{V_{IN} - V_{OUT}}{L} \times \frac{D}{f\,s} \label{eq:deltaI}$$

Eq (12)

and rearranging terms to calculate inductance

$$L = \frac{V_{IN} - V_{OUT}}{\Delta I} \times \frac{D}{f \, s}$$

Eq (13)

Where fs is the PWM switching frequency, L is the inductance and D is the Duty Cycle.

To examine the inductor slew rate for a step change in output current

Eq(14a)

$$Trise = L \bullet \frac{CurrentStep}{Vin - Vout}$$

$$Tfall = L \bullet \frac{CurrentStep}{Vout}$$

Equations 14 a and b are useful because they give us the maximum slew rate that can be achieved for a given inductor.

An important point on slew rate is that the above number does not represent loop response. The final rate of change of the output voltage in response to a step change in current is determined by the frequency response of the closed loop and the loop phase margin. The control loop will always respond slower than the inductor current ramp.

The following example calculations use the conditions listed below:

Vin = 5 V

Vout = 1.5 V

D = 1.5/5 = 30%

I out = 8 A

Inductor ripple current = 20%

PWM frequency = 300 KHz

Maximum load step = 4A

Output ripple < 50mV

Total output change due to 4 A step < 100 mV

Using equation 13, the inductance value is determined as follows:

$$L = \frac{5 - 1.5}{8 \times .2} \times \frac{D}{f \text{ s}} = 2.18 \,\mu\text{H}$$

### 14.0 OUTPUT CAPACITOR SELECTION

Once the inductor value has been determined an output capacitor can be chosen. The ESR value is the main selection criteria for this capacitor. Package size at the required voltage and capacitance will also need to be determined after the ESR is known. The output ripple voltage and allowable error for a step change are important since both of these influence the required ESR of the capacitor.

If no load step is specified

Capacitor ESR

$$\leq \frac{\text{Output Ripple Voltage}}{\text{Inductor Ripple Current}}$$

For the 50mV ripple voltage:

$$ESR \le \frac{50 \,\text{mV}}{1.6 \,\text{A}} \le .031 \,\Omega$$

This will not be a difficult ESR to achieve with good quality capacitors. A 4A load step will give a drop in the output of .031 $\Omega$  x 4A =125mV which is greater than the total 100mV allowed so we will need a lower

ESR due to the current step and output ripple combined.

When a step change is load current is known:

Eq (16)

$$Capacitor \ ESR \leq \frac{Total \ Allowable \ Voltage \ Drop}{Inductor \ Ripple \ Current+Load \ Step}$$

The total allowable drop will be the amount allocated to the load step minus one half of the ripple voltage.

Capacitor ESR

$$\leq \frac{100 \text{ mV} - 25 \text{ mV}}{1.6 \text{ A} + 4 \text{ A}} = .0134 \Omega$$

This ESR value is easily achieved. It is almost always true that once the ESR requirement is met the bulk capacitance will be adequate for energy storage. Some common capacitor types are the Sanyo MV-GX, and Sanyo OS-CON. Others like the surface mount Panasonic SP-CAP also have low ESR. It is common practice to parallel a number of capacitors to get the required ESR while maintaining acceptable package size. Do not overlook the reliability of the capacitor at the required temperature, operating voltage, and ripple current.

### 15.0 INPUT CAPACITOR SELECTION

The main criteria for selecting the input capacitor is ripple current. When the PWM main FET switches on it places a high current demand on the input rail. The energy must be supplied by the input capacitor because the input path typically has sufficient impedance such that it cannot supply the peak demand made by the PWM.

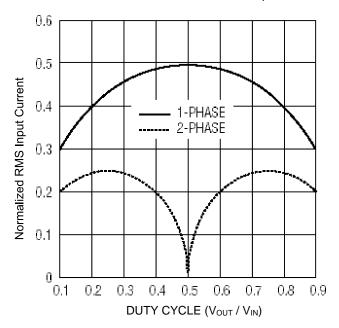

For a single phase PWM the worst case input current condition occurs when the duty cycle is 50% resulting in an RMS current of lout/2.

A two phase (or Bi-Phase) PWM improves this by a factor of two at its worst-case point. The worst case condition will occur at 25% and 75% duty cycle with the RMS input current equal to lout/4.

The RMS input current for a single phase PWM is given by

Eq(17)

$$I_{IN}(RMS) = I_{OUT} \sqrt{D(1-D)}$$

For a Bi-Phase PWM the input ripple current can be calculated by

Eq(17a)

$$I_{\rm IN}({\rm RMS}) = I_{\rm OUT} \sqrt{D(0.5-D)}$$

for D  $\leq$  0.5

As shown in Figure (7) for duty cycles greater than 50% the curve folds over around the 50% point.

### Figure (7) RMS Ripple Current

The values shown above are for a steady state condition when the control loop is regulating Vout to the proper value. During startup the duly cycle can approach 100% for short periods and a short circuit condition can result in a very low duty cycle since the on time of the upper MOSFET will be limited by the 350nSec delay for the current limit circuit. If possible it is advisable to pick input capacitors that are capable of handling the worst case RMS ripple current.

For a single phase Buck PWM and the 8A output in our previous example with a duty cycle of 30% the actual input ripple current from Eq 17 would be 3.67A RMS. Since the input voltage is always higher than the output this puts an additional burden on the input capacitor.

Several capacitors connected in-parallel will be required to meet the 3.67A RMS ripple current and voltage constraint. For example, the Sanyo MVGX series 10 volt 1500uF capacitor has a ripple current of 1.3Arms. This would require 3 devices in-parallel to meet the 3.67A RMS input ripple requirement.

Figure (7) shows that considerable deviation from a 50% duty cycle is required to gain any significant reduction in RMS input current from the worst case of 0.5 x lout. If the input voltage is not well controlled be

careful to use the maximum input voltage when sizing the input capacitor.

As with the output capacitor the bulk capacitance will be more than adequate once the main criteria of ripple current has been met. ESR should also be considered because it results in an overall loss of efficiency, the power loss in the capacitor is equal to (I2 x ESR). This loss should not be ignored if maximum efficiency is a goal. The ripple current in the capacitor will also cause component heating, adversely effecting reliability.

Always consider temperature and voltage stress at the worst case conditions when picking a

### 16.0 EFFICIENCY

The key components that significantly effect overall efficiency are the power handling components in the PWM output stage. The switching FETs have the greatest effect on overall efficiency. In order to maximize efficiency, the selected FETs must have the lowest possible switching and conduction losses. These factors are covered in the Component Selection section. FET gate drive can require significant power, always pick FETs with low gate charge and use the lowest practical gate drive voltage. PWM frequency is a significant factor in overall design. At higher PWM frequencies the switching losses become greater. However, at higher PWM frequencies, other components become smaller.

A trend in FET development is to improve switching and conduction losses hence, better components continually become available. The Inductor can dissipate a significant amount of power if the I<sup>2</sup>R losses are too high or if the inductor core has a lot of loss at the PWM frequency. Always pick an inductor with low ESR and be certain that it will operate efficiently at the maximum PWM frequency. If the core begins to saturate the core loss and ripple current will increase. Be certain that the inductor is rated for the full output current plus one half of the ripple current. Remember that the ESR of input and output capacitors dissipate power and should be taken into account.

Even with good power planes and wide traces drop across the circuit board copper can be significant.

The MOSFET upper driver supply voltage (VCX) should be kept as low as possible for best efficiency.

### 17.0 LOOP COMPENSATION

A complete mathematical analysis of a buck PWM is possible however, due to the number of component tolerances and variations in input voltage a simple graphical method using a Bode plot will generally give satisfactory results.

A buck regulator using the LX1672 controller is quite forgiving and generally does not require any additional compensation components to implement a stable system with sufficient phase margin. The evaluation board component values result in a stable system with superior transient response. One version of the factory delivered eval board has phase 1 and 2 operating in Bi-Phase, the feedback for the phase 1 error amplifier is a resistor that sets a fixed gain. The phase 2 error amplifier has a capacitor in the feedback path to form an integrator that gives a very high gain at low frequencies so that it can track phase 1. This is one example of how the feedback components can be used.

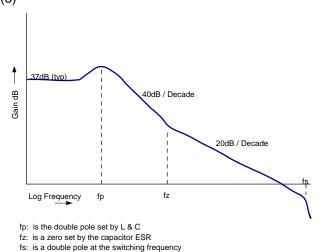

The output inductor and capacitor are the primary components that determine the frequency response of the closed loop by creating a double pole and a zero that set the dominant break points and determine the unity gain crossover point (unless frequency compensation components are added). Loop gain is another variable used to determine the unity gain crossover frequency and overall loop stability.

A common design goal is to have the unity gain crossing occur at a slope of -20dB per decade. It is possible to cross through zero gain at -40 dB per decade if the ESR zero is close enough to the zero crossing to provide sufficient phase margin. The unity gain crossing should be below the switching frequency pole by a factor of 5 if possible. Once the break points have been calculated a Bode plot can be drawn on semi log paper to obtain a graphical representation of the loop response. A Bode plot for a PWM regulator using the LX1672 is shown in Figure (8)

Figure (8) - PWM Bode Plot

A double pole at a break point frequency (fp) is determined by the output inductor and capacitor:

$$f(p) = \frac{1}{2\pi\sqrt{LC}}$$

A zero is set by the output capacitor at the frequency (fz):

$$f(z) = \frac{1}{(2\pi)ESR \times C_{OUT}}$$

Figure (9) shows the blocks in the control loop that effect frequency response and gain. The error amplifier is the primary gain block and can be treated like any operational amplifier. The PWM and FET switches are considered one stage. The amplifier gain is simply the feedback impedance between the FBX and EOX pins divided by the input impedance. The resistors connecting the PWM output to the amplifier input at the FBX pin ( ZIN) must be considered as a Thevinin equivalent to calculate the correct gain.

Figure (9) - LX1672 Control Loop Block Diagram

Amplifier Gain =

$$\frac{Z f}{Z_{IN}}$$

Eq (20)

Eq (21)

The gain of the PWM stage is:

$$PWM Gain = \frac{PWM Vin}{RampVoltage}$$

Loop gain is the product of the amplifier and PWM gains calculated with equations 20 and 21. Note that these equations give a unitless numerical gain (A). The gain in db is  $20\log(A)$ , gain in db is added for cascaded stages.

A very import point is that the input voltage is a gain term in the loop transfer function so that varying the voltage on the main FET drain will have an effect on loop gain and stability. The difference in gain going from 3.3 to 12 volts input is 20log12/3.3 = 11.2db, a considerable change in loop gain.

### **18.0 TRANSIENT RESPONSE**

A useful check of performance is to apply a step change of current to the output using a FET switch with a series load resistor and observe the response of the output voltage and inductor current. A large overshoot that takes a number of cycles to settle indicates low phase margin. A system with greater phase margin will have less overshoot but take longer to correct the error introduced into the feedback loop.

### 19.0 CIRCUIT BOARD LAYOUT

Switching regulators operating at multiple amps of output current are very sensitive to layout due to the high current pulses and fast rise times when the FETs are switched. It is important to keep the currents in the FET switching and filtering section confined to their own ground plane and use a single point ground connection to the analog and digital ground pins on the LX1672.

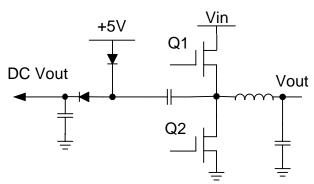

The connection between the lower FET drain and upper FET source should be as short as possible and properly sized for current. Inductance in this path will result in unwanted transients that will impair proper switching operation. The input and output capacitor ground leads should be returned to the source of the lower FET. The PGX pins should also be connected at the lower FET source. Large traces are required in all output filter connections. A good layout keeps all circulating currents produced by the output switching and filter sections away from the low signal level analog circuitry. Feedback lines going to the LX1672 for voltage and current should be routed on a lower layer protected from the output section by a ground or power plane. Separate bypass capacitors should be used on the VCC and VCCL pins to prevent possible UVLO problems during startup. All filtering components on lines bringing signals back to the controller should be located near the controller and tied to the ground plane for the analog ground pin. The evaluation board is a six-layer design with separate power planes for each supply voltage and a ground plane. It would be possible to reduce this without significant compromise in performance if very careful attention is paid to critical high current paths. The evaluation board uses a separate analog ground plane located on the +5V PWB layer, this is an important feature that should be included in any lavout. Figure (10) shows the output filter components and FETs, the heavy traces should be

sized in accordance with the current requirements, be as large as possible, and connected as shown.

Figure (10) - PWM Switch and Output Filter

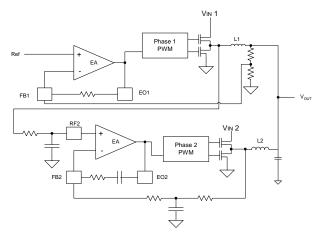

# 20.0 Bi-Phase PWM current sharing methods

There are several methods used to control the current sharing in multiphase PWM regulators. Multiphase controllers can have as few as two phases and in many cases four or even six. The goal of any multiphase controller is to proportion the current between multiple phases to achieve a specified ratio from L1 to Lx. By dividing the output current among several phases it is possible to get much higher total output current than could be achieved with a single phase. The trend towards lower supply voltages and higher currents has made the multiphase PWM controller popular. Multi-phase designs offer significant thermal advantages by spreading the heat out over a larger area by using a number of FETs. An additional advantages is reduced ripple current in the input and output capacitors. The reduced ripple current in the input capacitor is especially important since there is less chance of disturbing the input rail and finding input capacitors with low ESR and small size can be difficult.

### 21.0 LOADSHARE

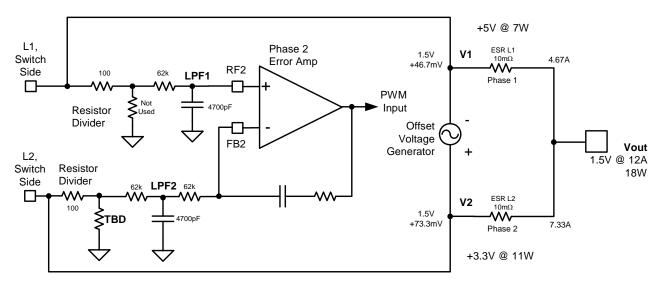

The LX1672 uses a Ratio Current Sharing method (LoadSHARETM) that forces the currents through the inductors to be proportional to the inductor DC resistance. For Bi-Phase operation Phase 1 and 2 are always the two that are used. Phase 1 is the control phase and phase 2 is forced to follow. Phase 1 works in a typical PWM configuration with the output side of the inductor divided down and used as feedback to the

negative input of the error amplifier, the positive side of the error amplifier is tied to the reference so the loop is closed.

The phase 2 error amplifier has a filtered feedback from the phase 1 phase node connected to its positive input to act as a reference and a filtered feedback from the phase 2 phase node connected to its negative input. The corner frequency of the filters is much lower that the PWM frequency so a DC voltage is present on both error amplifier inputs. With phase 1 acting as a reference the filtered feedback from phase 2 closes the loop and forces the duty cycle of phase 2 to produce an average voltage that is identical to that produced by phase 1. The output ends of the two inductors are connected together and the input ends have equal average voltages impressed on them so the average current in each inductor is proportional to the inductor resistance. If identical inductors are used the current contribution for both phases will be equal. This method has good feedback for current balancing and can be modified to imbalance the average currents if desired. By using different input voltages and unbalancing the currents in the two phases the power drawn from each input rail can be controlled to fit within the available limits. Figure (11) shows this configuration.

Figure (11) - LX1672 LoadSHARE Block Diagram

There are four variants of the LoadSHARETM topology that are explained in detail in the following pages.

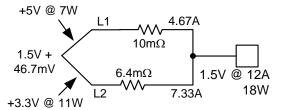

### Bi-Phase, LoadSHARE (ESR Method)

The first method is to change the ratio of the inductors equivalent series resistance, (ESR). As can be seen in the previous example, if the offset error is zero and the ESR of the two inductors are identical, then the two inductor currents will be identical. To change the ratio of current between the two inductors, the value of the inductor's ESR can be changed to allow more

current to flow through one inductor than the other. The inductor with the lower ESR value will have the larger current. The inductor currents are directly proportional to the ratio of the inductor's ESR value.

The following circuit description shows how to select the inductor ESR for each phase where a different amount of power is taken from two different input power supplies. A typical configuration will have a +5V rail connected to the phase 1 half bridge driver and a +3.3V rail connected to the phase 2 half bridge driver. The combined output power for this core voltage is 18W (+1.5V @ 12A). For this example the +5V power supply will supply 7W and the +3.3V power supply will supply the other 11W. 7W @ 1.5V is a 4.67A current through the phase 1 inductor. 11W @ 1.5V is a 7.33A current through the phase 2 inductor. The ratio of inductor ESR is inversely proportional to the current ratio between phases.

$$\frac{ESR1}{ESR2} = \frac{I2}{I1}$$

The lower ESR value will have the higher inductor current. If the ESR of the phase 1 inductor is selected as  $10m\Omega$ , then the ESR value of the phase 2 inductor is calculated as:

$$\left(\frac{4.67A}{7.33A}\right) \times 10\,\text{m}\Omega = 6.4\,\text{m}\Omega$$

Depending on the required accuracy of this power sharing; inductors can be chosen from standard vendor tables with an ESR ratio close to the required values. Inductors can also be designed for a given application so that there is the least amount of compromise in the inductor's performance.

Figure (12) - LoadSHARE Using Inductor ESR

### Bi-Phase, LoadSHARE (Feedback Divider Method)

Sometimes it is desirable to use the same inductor in both phases while having a much larger current in one phase versus the other. A simple resistor divider can be used on the input side of the Low Pass Filter that is taken off of the switching side of the inductors. If the Phase 2 current is to be larger than the current in Phase 1; the resistor divider is placed in the feedback path before the Low Pass Filter that is connected to

the Phase 2 inductor. If the Phase 2 current needs to be less than the current in Phase 1; the resistor divider is then placed in the feedback path before the Low Pass Filter that is connected to the Phase 1 inductor.

As in Figure (12), the millivolts of DC offset created by the resistor divider network in the feedback path, appears as a voltage generator between the ESR of the two inductors.

A divider in the feedback path from Phase 2 will cause the voltage generator to be positive at Phase 2. With a divider in the feedback path of Phase 1 the voltage generator becomes positive at Phase 1. The Phase with the positive side of the voltage generator will have the larger current. Systems that operate continuously above a 30% power level can use this method, a down side is that the current difference between the two inductors still flows during a no load condition.

This produces a low efficiency condition during a no load or light load state, this method should not be used if a wide range of output power is required.

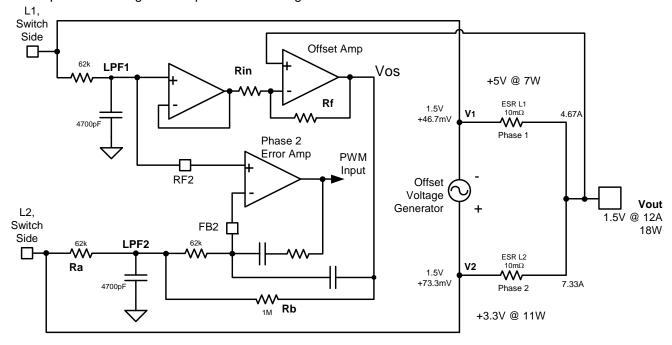

The following description and Figure (13) show how to determine the value of the resistor divider network required to generate the offset voltage necessary to produce the different current ratio in the two output inductors. The power sharing ratio is the same as that of Figure (12). The Offset Voltage Generator is symbolic for the DC voltage offset between Phase 1 & 2. This voltage is generated by small changes in the duty cycle of Phase 2. The output of the LPF is a DC voltage proportional to the duty cycle on its input. A small amount of attenuation by a resistor divider before the LPF of Phase 2 will cause the duty cycle of Phase 2 to increase to produce the added offset at V2. The high DC gain of the error amplifier will force LPF2 to always be equal to LPF1. The following calculations determine the value of the resistor divider necessary to satisfy this example.

Figure (13) - LoadSHARE Using Feedback Divider Offset

Where V1 = 1.5467 ; V2 = 1.5733 and

$$K = \frac{V1}{V2}$$

then  $TBD = \frac{K \times 100}{1 - K} = 5.814 K$

### Bi-Phase, LoadSHARE (Proportional Method)

The best topology for generating a current ratio at full load and proportional between full load and no load is shown in Figure (14). The DC voltage difference between LPF1 and VOUT is a voltage that is proportional to the current flowing in the Phase 1 inductor. This voltage can be amplified and used to

offset the voltage at LPF2 through a large impedance that will not significantly alter the characteristics of the low pass filter. At no load there will be no offset voltage and no offset current between the two phases. This will give the highest efficiency at no load.

A speed up capacitor can be used between the offset amplifier output and the negative input of the Phase 2

error amplifier. This will improve the transient response of the Phase 2 output current, so that it will share more equally with phase 1 current during a transient condition.

The use of a FET input amplifier is required for the buffer to prevent loading the low pass filter. The gain

of the offset amplifier, and the value of Ra and Rb, will determine the ratio of currents between the phases at full load. Two external amplifiers are required or this method.

Figure (14) - LoadSHARing Using Proportional Control

The circuit in Figure (14) sums a current through a  $1M\Omega$  resistor (Rb) offsetting the phase 2 error amplifier to create an imbalance in the L1 and L2 currents. Although there are many ways to calculate component values the approach taken here is to pick Ra, Rb, Rin, Vout, and inductor ESR. A value for the remaining resistor Rf can then be calculated.

The first decision to be made is the current sharing ratio, follow the previous examples to understand the basics of LoadSHARE. The most common reason to imbalance the currents in the two phases is because of limitations on the available power from the input rails for each phase. Use the available input power and total required output power to determine the inductor currents for each phase.

All references are to Figure (14)

Calculate the voltages V1 and V2.

$V1 = L1 Current \times L1 ESR + Vout$

$V2 = L2 Current \times L2 ESR + Vout$

Select values for Ra and Rb (Ra is typically  $62K\Omega$ ; Rb is typically  $1M\Omega$ )

3) Calculate the offset voltage Vos at the output of the offset amplifier

$$Vos = V 2 - \left(\frac{V 2 - V 1}{Ra}\right) \times \left(Ra + Rb\right)$$

4) Calculate the value for Rf

(select a value for Rin typically  $5K\Omega$ )

$$Rf = Rin \left( \frac{Vos - Vout}{Vout - V1} \right)$$

Due to the high impedances in this circuit layout can effect the actual current ratio by allowing some of the switching waveforms to couple into the current summing path. It may be necessary to make some adjustment in Rf after the final layout is evaluated. Also the equation for Rf requires very accurate numbers for the voltages to insure an accurate result.

### Bi-Phase, LoadSHARE (Series Resistor Method)

A fourth but less desirable way to produce the ratio current between the two phases is to add a resistor in

series with one of the inductors. This will reduce the current in the inductor that has the resistor and increase the current in the inductor of the opposite phase. The example of Figure 7 can be used to determine the current ratio by adding the value of the series resistor to the ESR value of the inductor. The added resistance will lower the overall efficiency

### .

### 22.0 OTHER MULTIPHASE METHODS

### **Digital Control Logic**

Internal digital control logic can be used to break the PWM cycle into a large number of clock cycles at a frequency much higher than the PWM switching frequency and then predict the switch points for the next PWM cycle of each phase. Due to the open loop nature of this approach it is prone to errors and may not divide the current equally between phases. There is no ability to compensate for differences in the external components.

### RDS(ON)

A method using the  $R_{\text{DS(ON)}}$  of a FET has had success. It actively measures the current through each leg for proper balance. A downside to this is that the  $R_{\text{DS(ON)}}$  of every FET must be equal for accurate current sharing. If all parts are from the same lot number and operating at the same temperature this will work well. Fortunately the positive temperature coefficient of a FET helps to balance the current over temperature. As FET  $R_{\text{DS(ON)}}$  values become lower the feedback signal continues to get lower in amplitude and can be difficult to filter out of the ambient noise. This method does have feedback to control current but the low input signal levels may cause problems.

### Inductor Feedback

A different technique using inductor resistance has been implemented by taking the AC and DC components of the inductor current and using them to drive a current sense amplifier. This technique works well on paper but has the disadvantage of requiring close tolerance components that must track over temperature to work properly. With proper component values it can work well and has active feedback to control each phase.

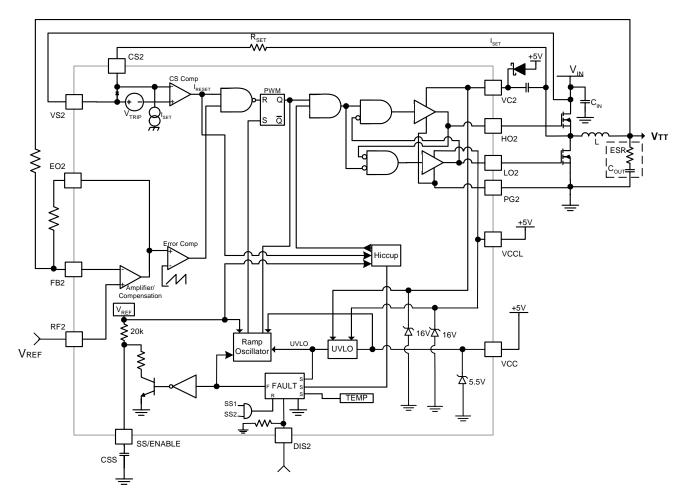

### 23.0 DDR VTT TERMINATION SUPPLY

DDR memory systems require a termination voltage (VTT) in addition to the line driver supply voltage (VDDQ) and receiver supply voltage (VDD). The JEDEC standard (EIA/JESD8-9A) for SSTL\_2 does not require that VDD and VDDQ be equal but it is common practice to use the same voltage for both. A unique feature of the VTT supply is that it must be able to source and sink current as the signals on the bus change states.

The LX1672 can supply both VTT and VDDQ by using two of the three PWM phases. Since the currents for VTT and VDD-VDDQ combined are generally a significant number of amperes a switching regulator is the only practical topology.

VTT for DDR SDRAM can be generated with the LX1672 by using the positive input of the phase 2 error amplifier (RF2) as a reference input. Using VREF, which is defined as one half of VDDQ, for the phase 2 reference input will insure that VTT equals VREF and that all voltages will track each other as required by the JEDEC specification.

See Microsemi Application Note 17 for details on DDR termination requirements and circuit configurations.

Figure 15 - DDR V<sub>TT</sub> Supply using Phase 2