# Radiation-Tolerant FPGAs Update Space Forum 2017

Minh Nguyen Senior Marketing Manager, Space

#### **Company Overview**

- Leading-edge semiconductor solutions differentiated by:

- Performance

- Reliability

- Security

- Power

- Solid financial foundation

- FY2016 revenue: \$1.6B

- 4800 employees today

- Major focus products

- FPGAs and ASIC

- Timing and OTN

- Mixed-signal and RF

- Switches and PHYs

- Storage controllers

© 2017 Microsemi Corporation. Company Proprietary

Discretes and integrated power solutions

#### Microsemi's Space Pedigree

#### Extensive Space Heritage

- Developing space solutions for six decades

- Proven track record of innovation, quality, and reliability

#### **Broad Solutions Portfolio**

Power, mixed-signal, and digital for bus and payload applications

## Expanding our Product Portfolio through Continuous Innovation

#### A Partner for the Long Run

60-year space heritage

## **Delivering A Comprehensive Space Portfolio**

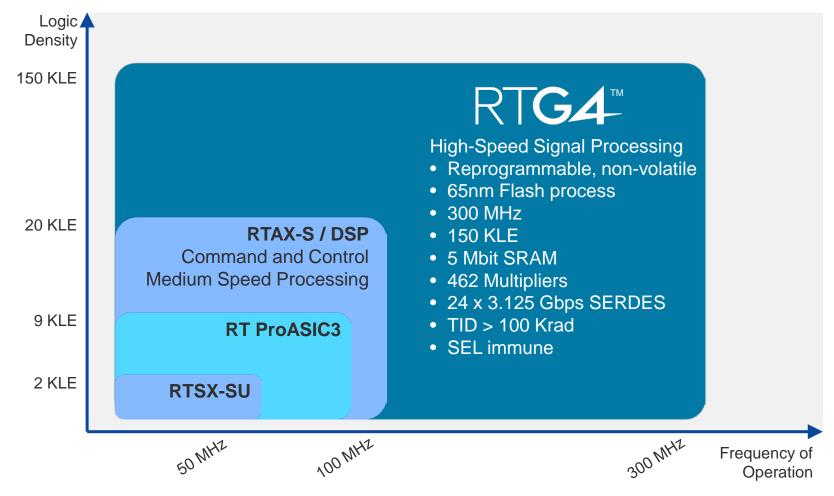

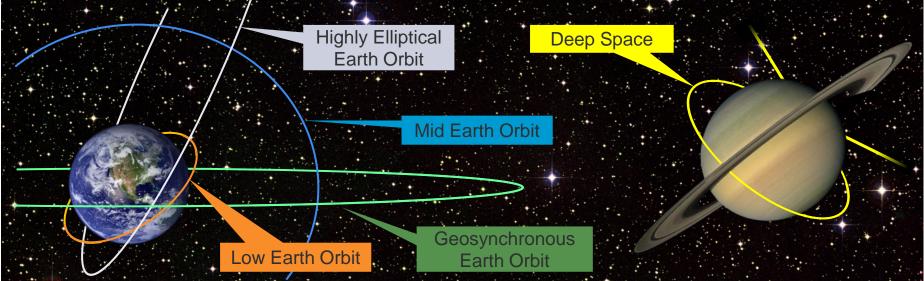

Radiation-Tolerant **FPGAs**

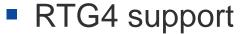

High performance, high density, low power TID up to 300 Krad, SEL immune RTG4 FPGAs up to 300 MHz and 150K LE RTProASIC3, RTAX, and RTSX-SU QML qualified

Rad-Hard Mixed Signal Integrated Circuits Telemetry and motor control space system managers High-side drivers Regulators and PWMs Extensive custom IC capability

Space-Qualified **Oscillators**

Ovenized Quartz oscillators Hybrid voltage controlled and temperature-compensated crystal oscillators Cesium clocks

© 2017 Microsemi Corporation. Company Proprietary

Rad-Hard **Power Solutions**  Rad-hard JANS diodes, bi-polar small signal transistors, and MOSFETs Rad-hard isolated DC-DC converter modules Custom power supplies: 2 W to > 5 KW Linear and POL hybrids Electromechanical relays

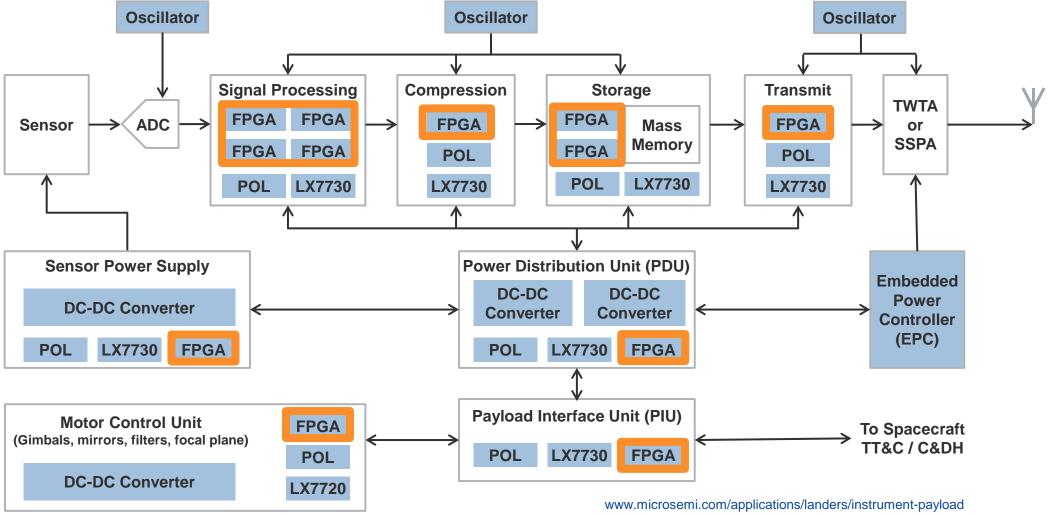

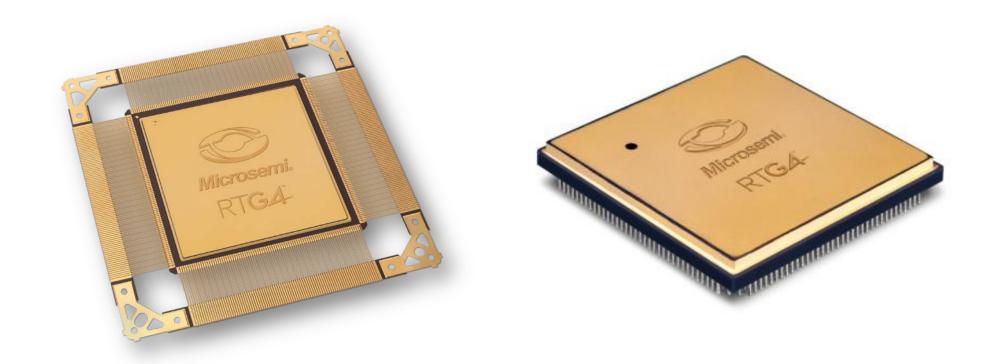

## Portfolio Breadth: Example Signal Processing Payload

#### FPGAs

## **Agenda**

- RTG4 Product Update

- **Introducing CQ352 Package**

- **Qualification Update**

- Software and IP

- RT FPGA Heritage Update

- Export Control Status

## **RTG4 Product Update**

## RTG4 High-Speed RT FPGAs

RTG4 mitigates the risks of ASICs and SRAM FPGAs, and has 20x improvement in signal processing throughput

## Introducing the CQ352 Package

| Resources                                                                                                                                                                  | RT4G150       |                                                 |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------|--|

| Logic Elements (TMR Register + 4-Input C Logic)                                                                                                                            | 151,824       | 151,824                                         |  |

| 18x18 Multiply-Accumulate Blocks                                                                                                                                           | 462           | 462                                             |  |

| RAM Mbits (1.5 Kbit and 24 Kbit Blocks, with ECC)                                                                                                                          | 5.2           | 5.2                                             |  |

| UPROM Kbits                                                                                                                                                                | 381           | 381                                             |  |

| DDR2/3 SDRAM Controller (with ECC)                                                                                                                                         | 2 x 32        | 0                                               |  |

| PCI Express Endpoints                                                                                                                                                      | 2             | 1                                               |  |

| Globals                                                                                                                                                                    | 24            | 24                                              |  |

| PLLs (Rad Tolerant)                                                                                                                                                        | 8             | 8                                               |  |

| SpaceWire Clock and Data Recovery Circuits                                                                                                                                 | 16            | 4                                               |  |

| User IO (excluding SERDES)                                                                                                                                                 | 720           | 166                                             |  |

| SERDES lanes (3.125 Gbps)                                                                                                                                                  | 24            | 4                                               |  |

| Hermetic, Ceramic Packages                                                                                                                                                 |               |                                                 |  |

| CG1657 (Ceramic Column Grid Array, Six Sigma Columns)<br>LG1657 (Ceramic Land Grid Array, No Solder Termination)<br>CB1657 (Ceramic Ball Grid Array, For Prototyping Only) | Available now |                                                 |  |

| CQ352 (Ceramic Quad Flat Pack)                                                                                                                                             |               | Samples in July '17<br>Flight units in July '18 |  |

## **CQ352 Package Update**

- CQ352 package will feature:

- 166 MSIO supporting up to 3.3 V

- 4 SpaceWire ports

- 4 SerDes transceivers supporting EPCS and PCIE

- Embedded Presidio Precious Metal Electrode (PME) 0508 decoupling capacitors

- Package size and weight:48 mm x 48 mm x 2.25 mm, 17.5 g

- Pin assignment table and package drawing available on the Microsemi website

- Software support available in Libero SoC v11.7

SP3 and later

## **RTG4 Qualification Update**

- MIL-STD-883B qualification completed successfully

- Qualification:

- 3 wafer lots, 54 units

- 54 units were functional during and after 1,000-hour life test at T<sub>J</sub> ≥ 125 °C, successfully completing qualification group C test

- All units continued additional life test exceeding MIL-STD-883B requirements:

54 units were functional during and after 4,000-hour life test at T<sub>J</sub> ≥ 125 °C

- Extensive reliability data set collected for 65nm Flash process from UMC

- Overall 65nm product FIT rate calculated < 3.11 FIT (60% confidence level, EA = 0.7eV)

- For more information see <u>Reliability Report Rev. 14</u>

- ESD Class 1A

- VDDAIO passed 250 V, other pins passed 2000 V

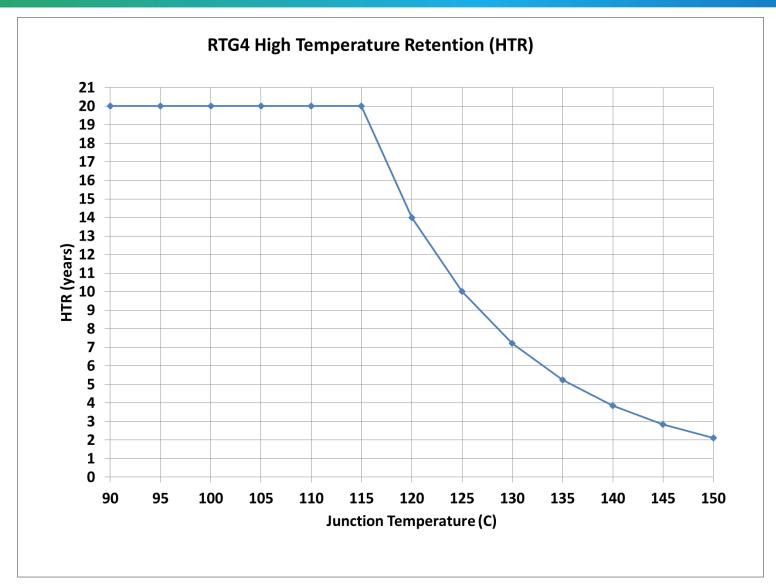

- Product retention: 20 years at Tj ≤ 115° C, or 10 years at Tj ≤ 125° C

## **RTG4 High Temperature Retention**

| Tj(C) | HTR (Years) |

|-------|-------------|

| 90    | 20          |

| 95    | 20          |

| 100   | 20          |

| 105   | 20          |

| 110   | 20          |

| 115   | 20          |

| 120   | 14          |

| 125   | 10          |

| 130   | 7.2         |

| 135   | 5.3         |

| 140   | 3.9         |

| 145   | 2.8         |

| 150   | 2.1         |

#### **RTG4** Reliability Summary

- High Temperature Operating Life (HTOL)

- 78 units from 4 wafer lots

- 54 out of 78 units went through 2000-hour life test

- $\Rightarrow$  Total 132,000 test hours at T<sub>J</sub> > 125 °C. Zero failures observed

- High Temperature Data Retention

- 54 units from 6 wafer lots went through 470+ programming test cycles for Non-Volatile Memory Cycling Endurance (NVCE)

- Total test cycles go beyond datasheet limit of 200 programming cycles

- After NVCE, 54 units went through 1000-hour life test

- ⇒ Total 54,000 test hours at T<sub>J</sub> > 125 °C. Zero failures observed

Reference: Reliability Report Rev. 14

Note: The latest 4000-hour data will be added in the next Reliability Report revision

#### **RTG4 QML Qualification Status**

- QML qualification planning and preparation

- Technology insertion plan has been approved

- Audits completed at Microsemi and at fab, bump, assembly, column subs

- Standard Microcircuit Drawing (SMD) draft in progress

- QML Class Q qualification

- Completion target: mid 2017

- Qualification data submitted to DLA, using MIL-STD-883B qualification data

- QML Class V qualification

- Completion target: early 2018

- Qualification will use RT4G150 in 1657-pin LGA / CCGA package

- 45 units from 1 wafer lot

- 4,000 hour life test to be completed by end of 2017

- Qualification data will be submitted to DLA after life test completion

- EV-flow flight units to be available prior to life test completion

## RTG4 Availability and Qualification Schedule

- RT4G150 PROTO FPGAs: Now

- RT4G150 development kit: Now

- Daisy chain packages: Now

- MIL-STD-883 Class B Qualification: Completed

- B-flow flight units: Available to lead time now

- E-flow flight units: Available to lead time now

- EV-flow flight units: Available to lead time now

- QML class Q qualification: Mid 2017

- QML class V qualification: Early 2018

## **RTG4 Radiation Summary**

| Total Ionizing Dose          | Stays within parametric limits > 125 Krad (Si)                      |                                                      |  |  |

|------------------------------|---------------------------------------------------------------------|------------------------------------------------------|--|--|

| Single Event Latch-Up        | No failure at facility limit of 103 MeV-cm <sup>2</sup> /mg, 100 °C |                                                      |  |  |

| Configuration Upset          | No failure at facility limit of 103 MeV-cm <sup>2</sup> /mg, 100 °C |                                                      |  |  |

| Flip-Flop Single Event Upset | 2.6E-12 errors/bit-day, GEO solar minimum, 1 MHz                    |                                                      |  |  |

| LSRAM Single Event Upset     | 2.0E-7 errors/bit-day,<br>GEO solar min (no EDAC)                   | 1.1E-11 errors/bit-day,<br>GEO solar min (with EDAC) |  |  |

| uSRAM Single Event Upset     | 3.1E-8 errors/bit-day,<br>GEO solar min (no EDAC)                   | 2.7E-13 errors/bit-day,<br>GEO solar min (with EDAC) |  |  |

#### **RTG4 Software and IP**

## **Libero SoC Software Highlights**

- 11.7 SP2—Released in October 2016

- Production Timing and Power

- Timing data update—Preliminary to Production

- Timing derating for TID 100 Krad reduced to 1% from 5%

- Power data update—Preliminary to Production

- Multiple Asynchronous Reset Placement Enhancement

- Placer ensures that no more than one asynchronous reset drives the pins in each half-row area of the chip. A detailed message is printed for each half-row with violation

- Placement algorithm was improved

- 11.7 SP3—Released in January 2017

- CQ352 package support: STD speed grade, advance timing data

- 11.8—Released in March 2017

- Include Synplify Pro ME (L2016.09M-2), which does not infer feed-through Write mode

- 11.8 SP1—Targeting August 2017

- DirectC and .DAT file generation for RTG4 inflight programming

- DirectC tool is free of charge

#### **RISC-V**

- Free and open Instruction Set Architecture (ISA)

- 32-bit instructions, optional 16-bit compressed instructions

- 32-bit, 64-bit, and 128-bit address-space options

- Quad floating point, virtualization, many cores, heterogeneous computing

- RISC-V is <u>not</u> an on open-source processor: it is an ISA <u>specification</u>

- Covered under the Berkeley Software Distribution (BSD) open source license

#### **Strong Founding Sponsor Group**

Platinum Founding Sponsors

Microsemi

#### RISC-V for RTG4

- RISC-V software tools

- GNU GCC, binutils, newlib stdc library, gdb JTAG/OpenPCD debug

- LLVM/Clang

- Linux and Windows dev environment

- Verification Suite

- Soft RISC-V IP is free of charge

- Preliminary IP is running at 70 MHz in RT4G150 "-1"

- Sample RISC-V project for RTG4 dev kit available now

- on GitHub website

- For details, refer to RISC-V website

#### **ARM Cortex M1 in RTG4**

- ARM Cortex M1

- 32-bit RISC microcontroller

- Supported by ecosystem from ARM and third-party vendors

- IP available now on MSCC website: End User Licensing Agreement (EULA) must be completed in order to download IP

- Uses DDR controller, SPI, UART, AHB to SRAM, and timer peripherals

- Performance targeting RT4G150, Dash-1 speed grade

| Design        | RTG4 LUT      | RTG4 DFF     | RTG4<br>LSRAM Blocks | RTG4<br>uSRAM Blocks | MHz |

|---------------|---------------|--------------|----------------------|----------------------|-----|

| ARM Cortex M1 | 11,600 (7.7%) | 6,900 (4.5%) | 2 (1.0%)             | 128 (61%)            | 50  |

#### Other RTG4 IP Cores

- 1553 and PCIF—available now from Microsemi

- TSE and SGMII—available now from Microsemi

- JESD204B TX and RX—available now from Microsemi

- SpaceWire

- STAR-Dundee IP available now

- SpaceFibre

- STAR-Dundee IP available now, multi-lane operation at 3.125 Gbps per lane

- LEON3-FT and LEON4-FT

- Cobham Gaisler IP available now

- Serial RapidIO—IP vendor evaluation in progress

© 2017 Microsemi Corporation. Company Proprietary

contact Microsemi for details

#### **RTG4 Summary**

- RTG4 now qualified to MIL-STD-883B

- On track to reach QML-Q in mid 2017

- On track to reach QML-V in early 2018

- New CQ352 with first samples in July 2017 and B-flow in July 2018

## **FPGAs in Remote Sensing Payload**

RTG4 complements existing Microsemi Radiation Tolerant FPGAs

## **Export Control Status**

- RT FPGAs removed from US Munitions List

- All Microsemi RT FPGAs now under EAR control

- Currently using the following Export Control Classification Numbers

- RTSX-SU 9A515.e.1

- RTAX-S/SL/DSP 9A515.e.1

- RT ProASIC3 3A001.a.1.b

- RTG4 9A515.e.1

For details, see <a href="http://www.microsemi.com/products/fpga-soc/radtolerant-fpgas/military-aerospace-certifications">http://www.microsemi.com/products/fpga-soc/radtolerant-fpgas/military-aerospace-certifications</a>

## **Your Partner for Space Technology**

- Leadership in space

- Leveraging our product breadth

- Innovative new products

- Focused on growth applications

## **Key Contacts**

Ken O'Neill

Director of Marketing, Space and Aviation 408-643-6179

ken.oneill@microsemi.com

© 2017 Microsemi Corporation. Company Proprietary

Minh Nguyen

Senior Marketing Manager, Space

408-643-6283

minh.u.nguyen@microsemi.com

#### Thank You

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

email: sales.support@microsemi.com

www.microsemi.com

©2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereing is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.