# ER0207 Errata PolarFire FPGA - ES Devices

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any pattern rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# Contents

| 1 | Revision History                         |

|---|------------------------------------------|

|   | 1.1 Revision 1.0                         |

| 2 | Errata for PolarFire Engineering Samples |

|   | 2.1 Introduction                         |

|   | 2.2 Sample Revisions                     |

|   | 2.3 PCB Designs                          |

| 3 | Summary of Device Errata                 |

| 4 | Descriptions and Workarounds5            |

| 5 | Unsupported Features                     |

| 6 | Engineering Sample Device Identification |

# **Figures**

|          | EC Islandification Markings | 10 |

|----------|-----------------------------|----|

| Figure 1 | ES Identification Markings  |    |

# **Tables**

| Table 1 | Sample Revisions Released per Device              | 2 |

|---------|---------------------------------------------------|---|

|         | PolarFire Engineering Sample Operating Conditions |   |

|         | Summary of PolarFire Devices Errata               |   |

| Table 4 | Unsupported GPIO Pins on Erased Devices,          | 6 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 1.0

Revision 1.0 is the first publication of this document.

# 2 Errata for PolarFire Engineering Samples

# 2.1 Introduction

PolarFire<sup>™</sup> FPGA engineering samples are subject to the limitations described in this errata. This document contains updated information about any known engineering samples specific issues and provides the available limitations and workarounds. Engineering sample issues identified in this errata will be corrected in subsequent revisions of the devices listed in the following table. Contact Microsemi Technical Support for more information.

# 2.2 Sample Revisions

The following table describes the sample revisions released. Errata items impact all -ES revisions listed unless specified.

| Table 1 • | Sample Revisions Released per Device |

|-----------|--------------------------------------|

|           |                                      |

| Devices | Packages           | Revisions |

|---------|--------------------|-----------|

| MPF300T | FCG1152 and FCG484 | 0, 01     |

### Table 2 • PolarFire Engineering Sample Operating Conditions

| <b>Operation Temperature Range</b> | Program/Erase | Retention Lifetime | sNVM Endurance | FPGA Endurance |

|------------------------------------|---------------|--------------------|----------------|----------------|

| 20 °C - 50 °C <sup>1</sup>         | 20 °C - 50 °C | 1 year             | 1000 cycles    | 200 cycles     |

1.  $T_J$  = Junction temperature.

# 2.3 PCB Designs

For information about how to determine proper signal pinout, see *UG0726: PolarFire FPGA Board Design User Guide*. The proper signal pinout is required for all clocking, transceiver, and FPGA pin recommendations.

# 3 Summary of Device Errata

The following table lists the summary of device errata.

Table 3 • Summary of PolarFire Devices Errata

| Errata Number | Description                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|

| 1             | Power supply sequencing, page 5                                                                                                |

| 2             | Bank3 VDDI and VDD_XCVR_CLK and XCVR_VREF[1:2], page 5                                                                         |

| 3             | Hot-swapping/cold sparing is not supported on any I/Os powered by VDDI3 0or the transceiver reference clock input pins, page 5 |

| 4             | Some I/O pins do not support hot-swapping/cold sparing on erased devices, page 6                                               |

| 5             | Calibration of FPGA I/O buffers only available at power-up, page 6                                                             |

| 6             | SmartDebug active probe speed, page 6                                                                                          |

| 7             | Missing global clock connection in XCVR Quad1, page 6                                                                          |

| 8             | Inefficient usage of Asynchronous dual-port LSRAM blocks, page 6                                                               |

| 9             | GPIO IOCDR SGMII, page 7                                                                                                       |

| 10            | SmartDebug active probe write, page 7                                                                                          |

| 11            | PCIe core is not correctly initialized, page 7                                                                                 |

| 12            | The PCIe AXI slave interface has lower than expected throughput, page 7                                                        |

| 13            | HSIO and GPIO drive strength may deviate by $\pm$ 20% from datasheet specifications, page 7                                    |

| 14            | PCIe fails to enter into transmit compliance when used with a 50 $\Omega$ load, page 7                                         |

| 15            | Voltage reference sensitivity issue with HSIOs when VDD18 and VDD25 supply voltage rail separation is too large, page 7        |

| 16            | LVDS VOS output common mode specification can vary as much as 175 mV below the datasheet specification, page 7                 |

| 17            | VDD power may be 40% higher than reported by Power Estimator, page 7                                                           |

| 18            | Transaction layer clock behavior of PCI express block, page 8                                                                  |

| 19            | The CCC-PLL Lock output can glitch after reset has occurred using the DEVRSTN pin, page 8                                      |

| 20            | LSRAM Read before Write (RBW) mode, page 8                                                                                     |

| 21            | Re-programming failure using FlashPro (JTAG programming), page 8                                                               |

| 22            | GPIO On-die termination, page 8                                                                                                |

| 23            | Transceiver Polarity Inversion, page 8                                                                                         |

| 24            | System controller suspend mode, page 9                                                                                         |

| 25            | Flash*Freeze mode, page 9                                                                                                      |

| 26            | Temperature voltage sensor (TVS), page 9                                                                                       |

| 27            | Device zeroization, page 9                                                                                                     |

| 28            | Generic I/O gearing modes, page 9                                                                                              |

| 29            | PCIe Gen 2 electrical compliance, page 9                                                                                       |

| 30            | Automated DFE, contact factory for DFE support, page 9                                                                         |

| 31            | XCVR limitations, contact factory for solutions outside defined support, page 9                                                |

# Table 3 • Summary of PolarFire Devices Errata (continued)

| Errata Number | Description                                     |

|---------------|-------------------------------------------------|

| 32            | ACJTAG IEEE 1149.6 for transceiver pins, page 9 |

# 4 **Descriptions and Workarounds**

## Power supply sequencing

#### Workaround

Engineering sample must follow this power-on sequence:

- 1.  $V_{DD}$  to  $V_{DD}$  operational minimum

- 2.  $V_{DD25}$  to  $V_{DD25}$  operational minimum

- 3. V<sub>DDI</sub> and V<sub>DDAUX</sub> must be powered up any time before V<sub>DD18</sub> or simultaneously with V<sub>DD18</sub> if supplied from same power source.

- 4. Last supply is  $V_{\text{DD18}}$  (V\_{\text{PP}}) and followed by other supplies

See the *DS0141: PolarFire FPGA Datasheet* for information about the operational minimum voltages. The V<sub>DD25</sub> power-supply can draw large currents at power-up or power cycling if this sequence is not followed.

Observe the specified power supply ramp rates specified in the DS0141: PolarFire FPGA Datasheet.

# Bank3 V<sub>DDI</sub> and V<sub>DD XCVR CLK</sub> and XCVR\_VREF[1:2]

Bank 3 V<sub>DDI</sub> and V<sub>DD XCVR CLK</sub> and XCVR\_VREF[1:2] cannot exceed 2.5 V nominal.

# Hot-swapping/cold sparing is not supported on any I/Os powered by $V_{DDI3}$ 0or the transceiver reference clock input pins

Includes the following I/O pins:

- SDO

- SDI

- FF\_EXIT\_N

- IO\_CFG\_INTFK

- SPI\_EN

- SCK

- DEVRST\_N

- SS

- тск

- TMS

- TDI

- TDO

- TRSTB

- XCVR\_#A\_REFCLK\_P/N

- XCVR\_#B\_REFCLK\_P/N

- XCVR\_#C\_REFCLK\_P/N

### Workaround

None

### Some I/O pins do not support hot-swapping/cold sparing on erased devices

The following table describes the 35 GPIO pins that do not support hot-swapping/cold sparing on erased devices. Programmed devices do not have this errata.

#### Table 4 • Unsupported GPIO Pins on Erased Devices<sup>1</sup>, <sup>2</sup>

| Bank | GPIO Pins                                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------|

| 0    | HSIO169PB0, HSIO170PB0, HSIO171PB0, HSIO173NB0                                                                              |

| 1    | HSIO72NB1, HSIO73PB1, HSIO74PB1, HSIO75PB1, HSIO79PB1, HSIO80PB1, HSIO81PB1                                                 |

| 2    | GPIO244NB2, GPIO246PB2, GPIO247PB2, GPIO248PB2, GPIO26PB2, GPIO27PB2, GPIO28PB2, GPIO32PB2, GPIO33PB2, GPIO34PB2, GPIO35NB2 |

| 4    | GPIO174PB4, GPIO180PB4, GPIO181PB4                                                                                          |

| 5    | GPIO238PB5, GPIO239PB5, GPIO241PB5                                                                                          |

| 6    | HSIO62PB6, HSIO63PB6, HSIO64PB6, HSIO68PB6, HSIO69PB6, HSIO70PB6, HSIO71NB6                                                 |

|      |                                                                                                                             |

1. Applicable only on erased parts. Programmed parts do not have the errata.

2. If these pins are used as input or bi-directional buffers, an erased device will actively drive these outputs rather than being properly disabled.

#### Workaround

Do not use these pins if required for hot-swapping/cold sparing applications, if part is not programmed.

#### Calibration of FPGA I/O buffers only available at power-up

The FPGA I/O buffers have calibration circuitry to optimize and match the I/O impedance and termination within a system. The calibration occurs every time the device is powered up. After the device power-up, recalibration is not available on command.

#### Workaround

To recalibrate, the device requires a power-cycle to correctly recalibrate.

### SmartDebug active probe speed

The live probe output cannot toggle faster than 100 MHz.

#### Workaround

None.

## Missing global clock connection in XCVR Quad1

Designs cannot utilize two global clocks for XCVR Quad1. Designs have access to only one global clock on Quad1.

#### Workaround

In the Libero<sup>®</sup> SoC PolarFire Transceiver Lane Configurator, the user can select the clock resources used for transmit and receive and Global or Regional clocks. For lanes assigned to Quad1, only a single Global connection is available. This implies that only one lane in that Quad and one direction of that lane can select Global in this interface.

### Inefficient usage of Asynchronous dual-port LSRAM blocks

For LSRAM blocks configured as Asynchronous dual-ports when Port A is greater than x20, twice the number of required LSRAM blocks are used.

#### Workaround

Two 1Kx20 LSRAM blocks are automatically instantiated by Libero SoC PolarFire to implement the single 512 × 40 LSRAM.

# **GPIO IOCDR SGMII**

This limitation prohibits IOD CDR interfaces to be used with a >0 ppm offset. For SGMII, the PHY device and PolarFire IOD CDR must use the same reference clock.

SGMII interfaces using transceivers are not affected with this limitation.

#### Workaround

SGMII can be implemented with IOCDR using 0 ppm or a common clock using the same clock configuration for both TX and RX clocks.

### SmartDebug active probe write

SmartDebug Active Probe write operation is not available. Active Probe read operation is operational as documented.

#### Workaround

None

### PCIe core is not correctly initialized

PCIe is not correctly initialized after programming the device.

#### Workaround

Device must be power-cycled after programming if PCIe Core is used in the design.

### The PCIe AXI slave interface has lower than expected throughput

Workaround

None

# HSIO and GPIO drive strength may deviate by ± 20% from datasheet specifications Workaround

None

## PCIe fails to enter into transmit compliance when used with a 50 $\Omega$ load

Workaround

None

# Voltage reference sensitivity issue with HSIOs when $V_{DD18}$ and $V_{DD25}$ supply voltage rail separation is too large

This effects the HSIO buffer banks only. This issue is managed by reducing the separation between  $V_{DD25}$  and  $V_{DD18}$ . For example, when  $V_{DD25}$  is maximum then  $V_{DD18}$  needs to be maximum or when  $V_{DD25}$  is typical then  $V_{DD18}$  needs to be typical. Respectively, if  $V_{DD18}$  and  $V_{DD25}$  are minimum and the other maximum will influence the effectiveness of the voltage references of the HSIO banks causing I/O buffers from correctly functioning.

# LVDS VOS output common mode specification can vary as much as 175 mV below the datasheet specification

## V<sub>DD</sub> power may be 40% higher than reported by Power Estimator

The PolarFire Power Estimator v3e is currently optimistic with regard to the estimated  $V_{DD}$  static power. It is expected that designs can have 40% higher current on the  $V_{DD}$  power supply compared to the provided estimation.

### Transaction layer clock behavior of PCI express block

To allow initialization of the PCIe block, PCIE\_TL\_CLK\_125 MHz must be available immediately after the device power-up. The TL\_CLK\_125 MHz must be sourced from the DIV/2 OSC160 at power-up and switched to the TxPLL DIV\_CLK while operating the PCIe. If not sourced, PCIe bridge registers and XCVR registers will not be initialized. For example implementation, see the PolarFire PCIe demo design https://www.microsemi.com/products/fpga-soc/fpga/polarfire-fpga#overview.

# The CCC-PLL Lock output can glitch after reset has occurred using the DEVRSTN pin

The PLL lock output may glitch when a device reset has occurred via the DEVRSTN pin.

#### Workaround

This glitch can be mitigated by extending the PLL LOCKCNT parameter.

PLL\_CTRL2 bits[12:9] register

See UG0684 PolarFire FPGA Clocking Resources User Guide for information about CCC register access.

### LSRAM Read before Write (RBW) mode

In RBW mode, the old read data is presented until the write is completed then will change to the newly written data on the next cycle. This LSRAM mode is not available.

#### Workaround

None

### Re-programming failure using FlashPro (JTAG programming)

Designs that are deployed device initialization to µPROM or external SPI before programming will fail reprogramming.

FlashPro Error Message:

Error: programmer 'S201Z7FK2R': Executing action PROGRAM FAILED, EXIT -38

#### Workaround

Error condition can be cleared by re-attempting programming. This issues is only identified in MPF300-ES Rev0 devices.

### **GPIO On-die termination**

The on-die pull-up of the thevenin termination can be as high as 2x. This causes a weak ODT termination.

#### Workaround

User can select a stronger termination value for the design.

### **Transceiver Polarity Inversion**

There is no programmable receiver polarity inversion possible on the transceivers for 8B10B, 64B6xB, and PMA.

### Work around

None

# **5 Unsupported Features**

System controller suspend mode Flash\*Freeze mode Temperature voltage sensor (TVS) Device zeroization Generic I/O gearing modes PCIe Gen 2 electrical compliance Automated DFE, contact factory for DFE support XCVR limitations, contact factory for solutions outside defined support ACJTAG IEEE 1149.6 for transceiver pins

# 6 Engineering Sample Device Identification

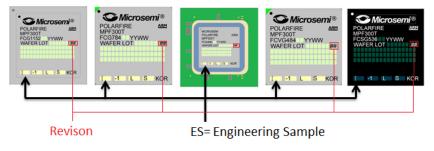

PolarFire FPGA engineering sample can be identified from the Temperature Grade field in the lower left hand corner as shown in the following figure.

## Figure 1 • ES Identification Markings