# Synphony Model<sup>™</sup> Compiler for Microsemi Edition User Guide

March 2015

## **Copyright Notice and Proprietary Information**

Copyright © 2015 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

## **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.

Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

"This document is duplicated with the permission of Synopsys, Inc., for the exclusive use of \_\_\_\_\_\_ and its employees. This is copy number \_\_\_\_\_."

## **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

## **Registered Trademarks (®)**

Synopsys, AEON, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, CODE V, Design Compiler, DesignWare, EMBED-IT!, Formality, Galaxy Custom Designer, Global Synthesis, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, LightTools, MAST, METeor, ModelTools, NanoSim, NOVeA, OpenVera, ORA, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Sonic Focus, STAR Memory System, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

## Trademarks (™)

AFGen, Apollo, ARC, ASAP, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIMplus, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Intelli, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Macro-PLUS, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, ORAengineering, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, RippledMixer, Saturn, Scirocco, Scirocco-i, SiWare, Star-RCXT, Star-SimXT, StarRC, System Compiler, System Designer, Taurus, Total-Recall, TSUPREM-4, VCSi, VHDL Compiler, VMC, and Worksheet Buffer are trademarks of Synopsys, Inc.

## Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license.

All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A March 2015

# Contents

#### **Chapter 1: Getting Started**

| About The Synphony Model Compiler Tool       20         About the Software       20         Synphony Model Compiler and MATLAB       21                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synphony Model Compiler Design Flows       22         Synphony Model Compiler FPGA Design Flow       22         Design Requirements for RTL Generation       24         FPGA Design Flow Procedure       25 |

| Finding Information                                                                                                                                                                                         |

| Getting Help                                                                                                                                                                                                |

#### Chapter 2: SMC Blocks: A to Divider

| Blocks — By Library       30         Communications       31         Control Logic       32         CORDIC       33         DSP Basics       33         Filtering       34         Floating Point       35         Math Functions       37         Memories       39         Ports & Subsystems       40         Signal Operations       41         Sources       43         Transforms       44 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blocks — Alphabetical List                                                                                                                                                                                                                                                                                                                                                                       |

| SMC Abs                                                                                                                                                                                                                                                                                                                                                                                          |

| SMC Accumulator                                                                                                                                                                                                                                                                                                                                                                                  |

| SMC Add                                                                                                                                                                                                                                                                                                                                                                                          |

| SMC ArcSinCos                   |

|---------------------------------|

| SMC Barker Code Generator63     |

| SMC Barrel Shifter              |

| SMC Binary Logic                |

| SMC Black Box                   |

| SMC Block Deinterleaver         |

| SMC Block Interleaver           |

| SMC Burst FFT                   |

| SMC Bus Master                  |

| SMC CIC                         |

| SMC CIC2                        |

| SMC Commutator                  |

| SMC Comparator                  |

| SMC Complex Abs                 |

| SMC Complex Mult                |

| SMC Concat                      |

| SMC Configurable FFT/IFFT122    |

| SMC Constant                    |

| SMC Convert                     |

| SMC Convolutional Deinterleaver |

| SMC Convolutional Encoder       |

| SMC Convolutional Interleaver   |

| SMC CORDIC Exp                  |

| SMC CORDIC Log                  |

| SMC CORDIC Polar                |

| SMC CORDIC Rotator              |

| SMC CORDIC SinCos               |

| SMC CORDIC Sqrt                 |

| SMC CORDIC2                        |

|------------------------------------|

| SMC Counter                        |

| SMC Counter2                       |

| SMC CRC Generator                  |

| SMC DDS                            |

| SMC DDS2                           |

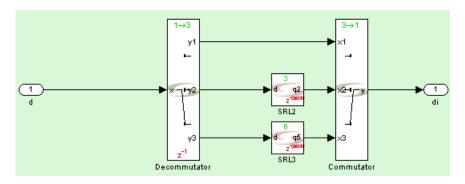

| SMC Decommutator                   |

| SMC Delay                          |

| SMC Demux                          |

| SMC Depuncture                     |

| SMC Differentiator                 |

| SMC DIT R2SDF FFT                  |

| SMC Divider                        |

| Chapter 3: Blocks: Divider2 to Log |

| SMC Divider2                      |

|-----------------------------------|

| SMC DivMod                        |

| SMC Downsample                    |

| SMC Dynamic Access Shift Register |

| SMC Dynamic Farrow Resampler      |

| SMC Edge Detector                 |

| SMC Extract                       |

| SMC Extract Input Parameters      |

| SMC FDATool                       |

| SMC FFT                           |

| SMC FFT2                          |

| SMC FIFO                          |

| SMC FIR                           |

| SMC FIR Engine                    |

| SMC FIR Rate Converter  |

|-------------------------|

| SMC FIR Resampler       |

| SMC FIR2                |

| SMC Fixed to FP         |

| SMC Flow Control Buffer |

| SMC FP Absolute         |

| SMC FP Accumulate       |

| SMC FP Add              |

| SMC FP Arc Tan          |

| SMC FP Burst FFT        |

| SMC FP Compare          |

| SMC FP Constant         |

| SMC FP Div              |

| SMC FP Format Convert   |

| SMC FP Fused Mult Add   |

| SMC FP IIR Section      |

| SMC FP Inv Sqrt         |

| SMC FP Log              |

| SMC FP Mult             |

| SMC FP Port In          |

| SMC FP Port Out         |

| SMC FP Pow              |

| SMC FP SinCos           |

| SMC FP Sqrt             |

| SMC FP Square           |

| SMC FP Tan              |

| SMC FP to Fixed         |

| SMC FP Vector Add       |

| SMC Frame FIR                                   | 421 |

|-------------------------------------------------|-----|

| SMC Frame Mean                                  |     |

| SMC Gain                                        | 427 |

| SMC Hadamard Code Generator                     | 431 |

| SMC Gold Sequence Generator                     | 433 |

| SMC HLS Subsystem                               | 437 |

| SMC Host Interface                              |     |

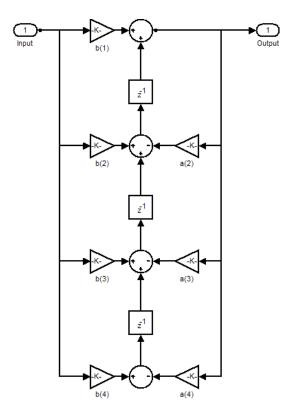

| SMC IIR                                         | 457 |

| SMC In                                          | 463 |

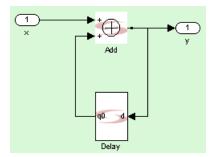

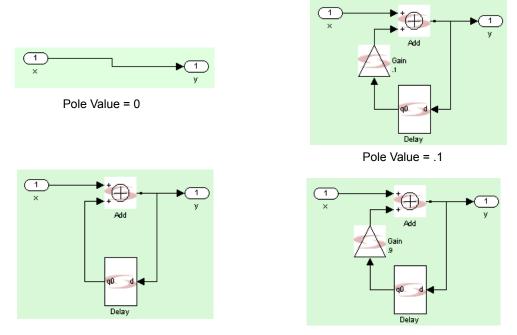

| SMC Integrator                                  | 464 |

| SMC Interleaver2                                | 468 |

| SMC Inverter                                    | 470 |

| SMC Leading Zero Counter                        | 472 |

| SMC Loadable Shift Register                     | 474 |

| SMC Log                                         | 477 |

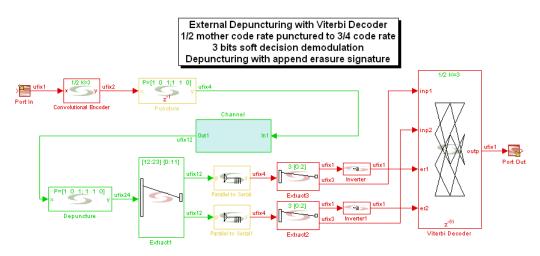

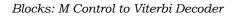

| Chapter 4: Blocks: M Control to Viterbi Decoder |     |

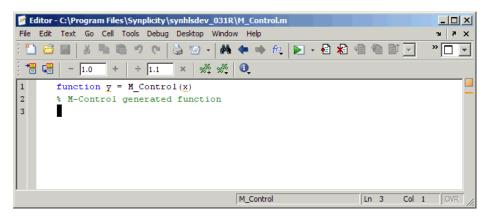

| SMC M Control                                   |     |

| SMC Matrix Mult                                 | 485 |

| SMC Mealy State Machine                         |     |

| SMC MinMax                                      | 492 |

| SMC Min Max Filter                              | 494 |

| SMC Moore State Machine                         | 497 |

| SMC Moving Average Filter                       | 500 |

| SMC MPSK Baseband Demodulator                   | 506 |

|                                                 |     |

SMC Mult

.514

SMC Mux

.518

SMC Negate

.524

| SMC Out                                  |

|------------------------------------------|

| SMC Parallel CIC2                        |

| SMC Parallel DDS2                        |

| SMC Parallel FIR                         |

| SMC Parallel to Serial                   |

| SMC Permutation                          |

| SMC PN Sequence Generator                |

| SMC Port In                              |

| SMC Port Out                             |

| SMC Pow                                  |

| SMC Pulse Extender                       |

| SMC Pulse Generator                      |

| SMC Puncture                             |

| SMC RAM                                  |

| SMC RAM Based Delay                      |

| SMC Ramp                                 |

| SMC Random                               |

| SMC Recast                               |

| SMC Rectangular QAM Baseband Demodulator |

| SMC Rectangular QAM Baseband Modulator   |

| SMC Reed-Solomon Decoder                 |

| SMC Reed-Solomon Encoder                 |

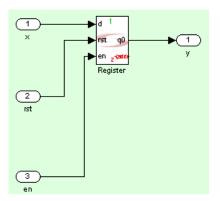

| SMC Register                             |

| SMC Reshape                              |

| SMC RFIR                                 |

| SMC ROM                                  |

| SMC RTL Encapsulation616                 |

| SMC R2SDF FFT                            |

| SMC Sample and Hold631            |

|-----------------------------------|

| SMC Saturate                      |

| SMC Scalar to Vector              |

| SMC Sequence                      |

| SMC Serial to Parallel            |

| SMC Set Target Device             |

| SMC Shift Register                |

| SMC Shifter                       |

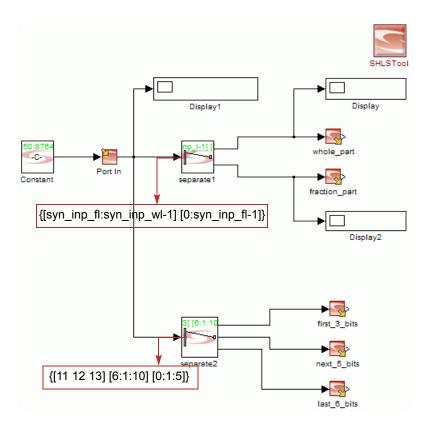

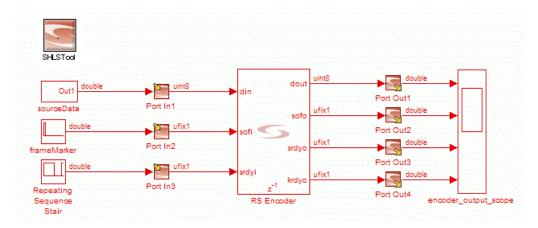

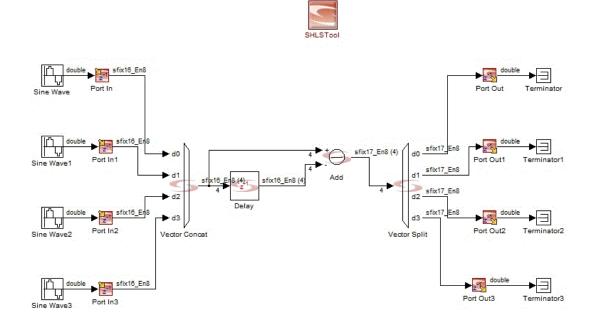

| SMC SHLSTool                      |

| Implementation Options Dialog Box |

| SMC Sign                          |

| SMC Signal Update                 |

| SMC SinCos                        |

| SMC SinCos2                       |

| SMC Single Clock Downsample       |

| SMC Single Clock Upsample         |

| SMC Smart Black Box               |

| SMC Sqrt                          |

| SMC Subsystem                     |

| SMC Sum of Products               |

| SMC Switch                        |

| SMC SynCoSimTool                  |

| SMC SynFixPtTool                  |

| SMC Test Vector Capture           |

| SMC Upsample                      |

| SMC Vector Concat                 |

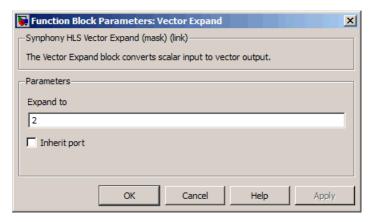

| SMC Vector Expand                 |

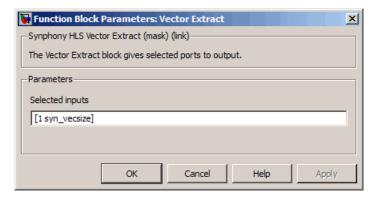

| SMC Vector Extract                |

| SMC Vector Split                                                                                                             | 742               |

|------------------------------------------------------------------------------------------------------------------------------|-------------------|

| SMC Vector to Scalar                                                                                                         | 744               |

| SMC Viterbi Decoder                                                                                                          | 746               |

| Common Parameters<br>Output Format Options<br>Overflow Saturation Options<br>Underflow Rounding Options<br>Special Variables | 757<br>759<br>759 |

| Suppressing Simulation Warnings                                                                                              | 763               |

#### **Chapter 5: SMC Functions**

| shls_bitrev          |

|----------------------|

| shls_convert         |

| shlsdemo             |

| shlsdoc              |

| shlslib              |

| shlsroot             |

| shistool             |

| shlsver              |

| syn_get_coefs        |

| syn_get_datatype     |

| syn_get_dspstartup   |

| syn_get_wordlength   |

| syn_read_hex         |

| syn_set_atm          |

| syn_set_dspstartup   |

| syn_set_portcapture  |

| syn_set_portregister |

| syn_unlink           |

| syn_write_wave       |

#### **Chapter 6: Constraints**

| HLS Constraints File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <sup>7</sup> 98                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Synphony Model Compiler Constraints       8         add_register_and_balance_parallel_paths       8         areabased_fir_arch_selection_atm Constraint       8         fir_architecture Constraint       8         multi_cycle_path Constraint       8         pattern_annotation Constraint       8         retime_across_blackbox       8         retiming_scale_factor Constraint       8         shls_retiming_lock Constraint       8         shls_retiming_lock_subsystem Constraint       8 | 300<br>301<br>301<br>302<br>304<br>305<br>306<br>306 |

| Multicycle Path Constraints       8         Specifying Multicycle Path Constraints       8         Automatically Inferring Multicycle Path Constraints       8                                                                                                                                                                                                                                                                                                                                      | 311                                                  |

| Forward-Annotation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 315                                                  |

#### **Chapter 7: Synthesizing the Design**

| Configuring Synphony Model Compiler       818         Configuring Settings for Simulink Simulation       818         Configuring SMC Timing Modes for FPGAs       818         Setting Default Display Modes       820                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic Procedures       82°         Starting a Synphony Model Compiler Design       82°         Working with Synphony Model Compiler Blocks       82°                                                                                                                         |

| Setting Options for an Implementation       824         Setting up Implementations       824         Resolving Read/Write Conflicts in FPGA RAMs       827         Including Comments in the Generated RTL       828         Keeping Signal Names in Generated RTL       830 |

| Using Constraints                                                                                                                                                                                                                                                            |

| Using Retiming                                                                                                                                                                                                                                                               |

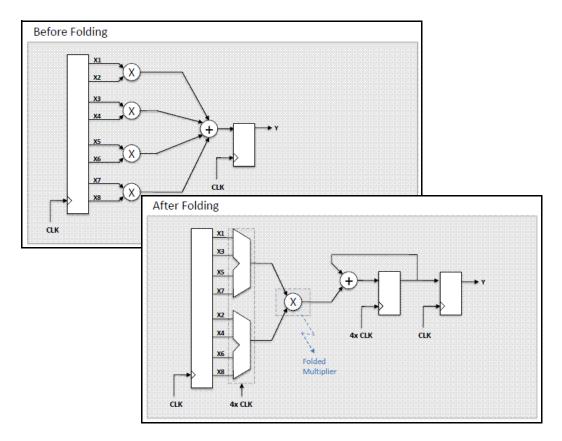

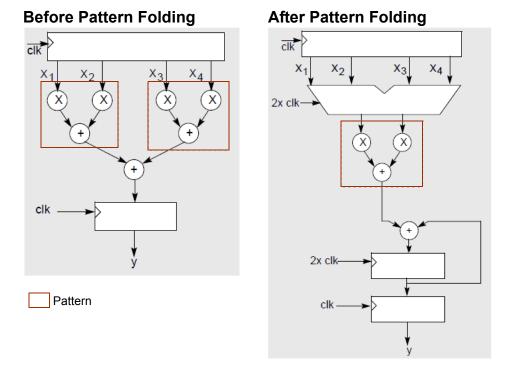

| Using Folding                                                                                                                                                                                                                                                                |

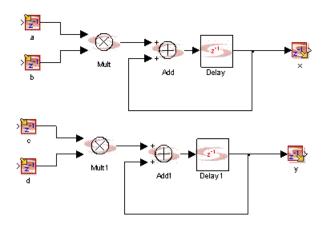

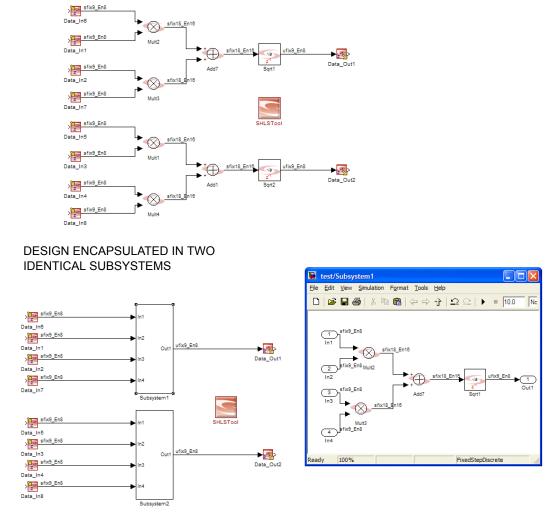

| Optimizing with Multichannelization     | 854 |

|-----------------------------------------|-----|

| Running Synthesis with SHLSTool         | 857 |

| Connecting Using a Host Interface Block | 859 |

#### **Chapter 8: Underlying DSP Fundamentals**

| Clock Domains                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

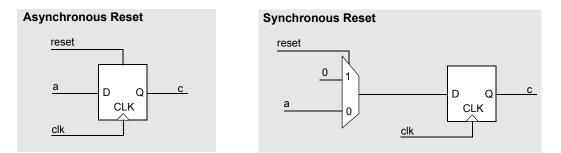

| Resets in the SMC Tool       863         Global and Local Resets       863         Synchronous and Asynchronous Resets       863         Reset Implementation in RTL Code       864         Resets and RTL Testbenches       865                                                                                                                                                                                                       |

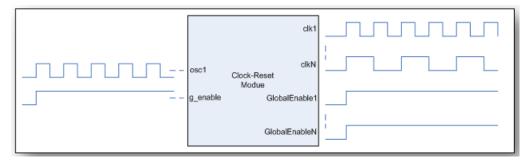

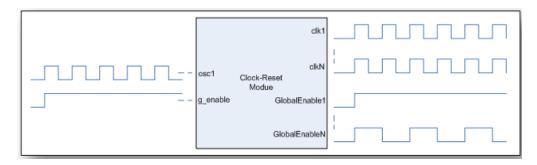

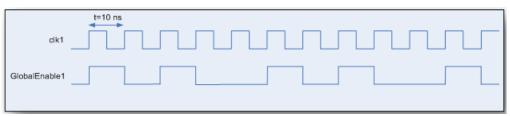

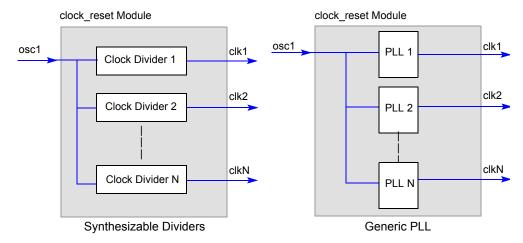

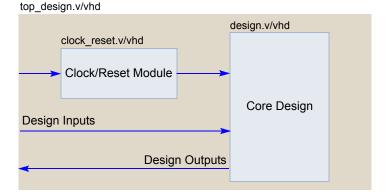

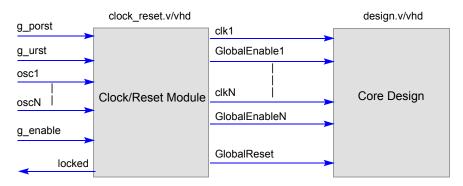

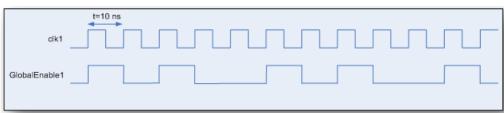

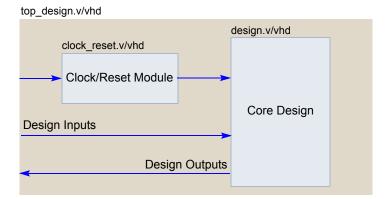

| Clock and Reset Management       866         Clock_reset Module Interface       867         Reset Functionality with the Clock_reset Module       868         Clock Functionality with the Clock_reset Module       868         Clock/Reset Circuitry Files       869         Clock_reset Module Limitations       870         Log File Messages for the Clock_reset Module       871                                                  |

| Data Types       874         Fixed-Point and Floating-Point Representation       874         Synphony Model Compiler Data Type Implementation       875         Fixed-Point Data Type       875         Data Type Casting: Setting the Output Data Type       876         Matrix Data Types       877         Floating Point Input and Output Formats for SMC FP Blocks       879         Floating-Point Interface Functions       881 |

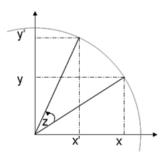

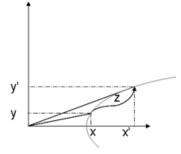

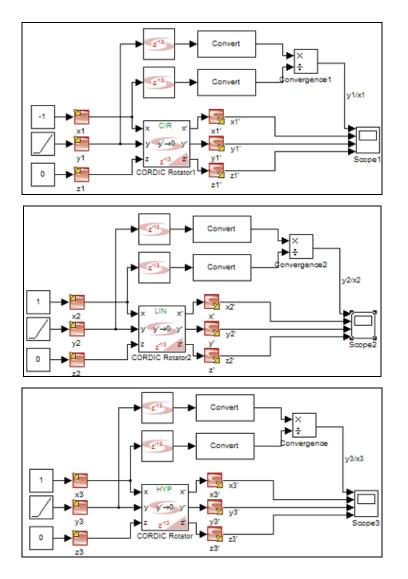

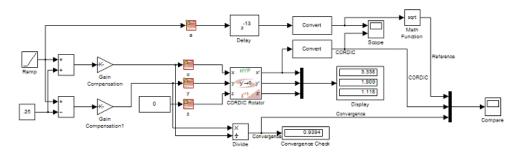

| CORDIC Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                      |

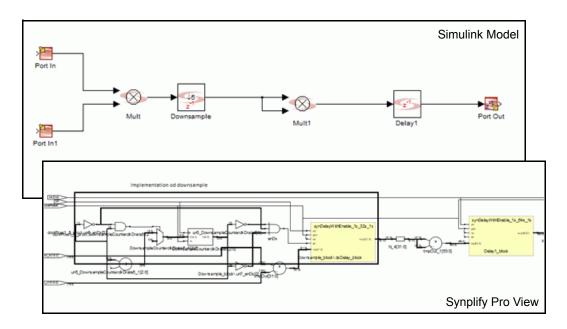

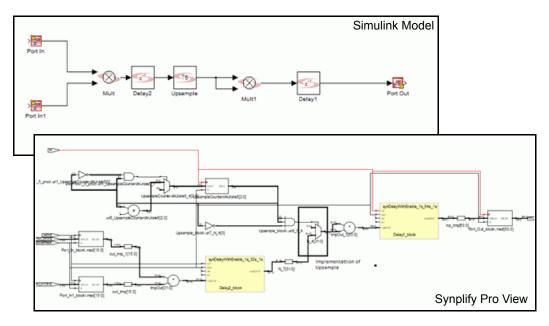

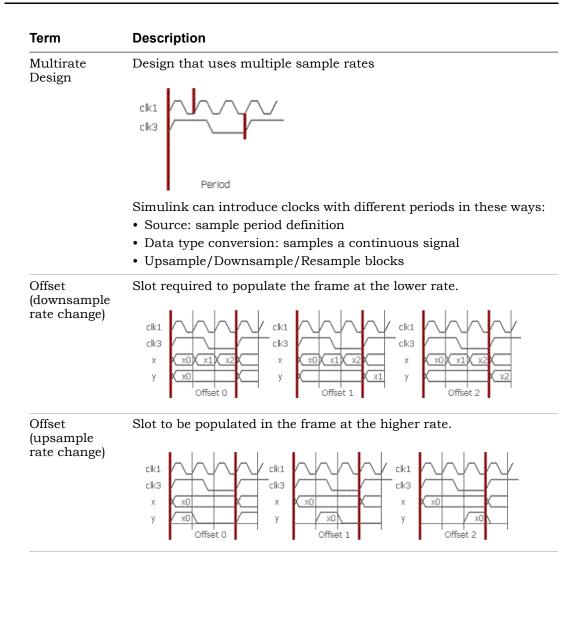

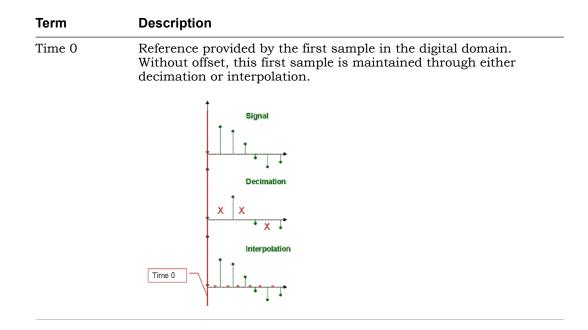

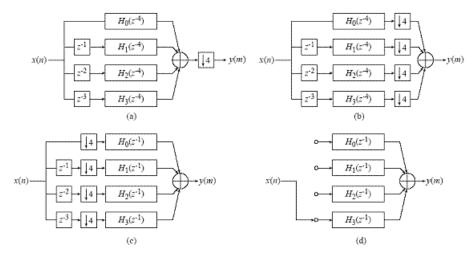

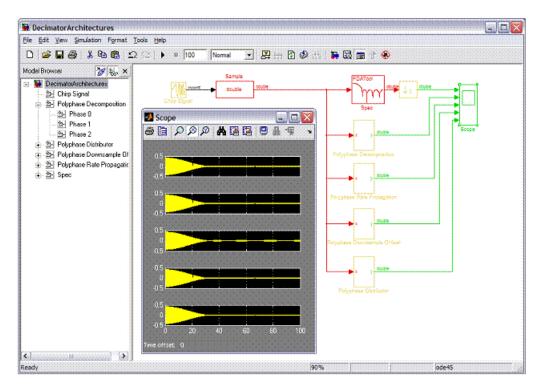

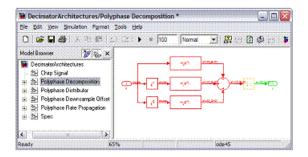

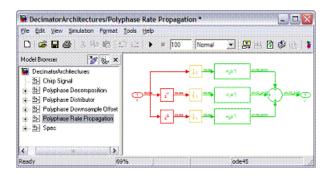

| Multi-Rate Design       899         Sample Rate Terminology       899         Clock Generation and Clock Reset       903         Polyphase Filtering       906                                                                                                                                                                                                                                                                         |

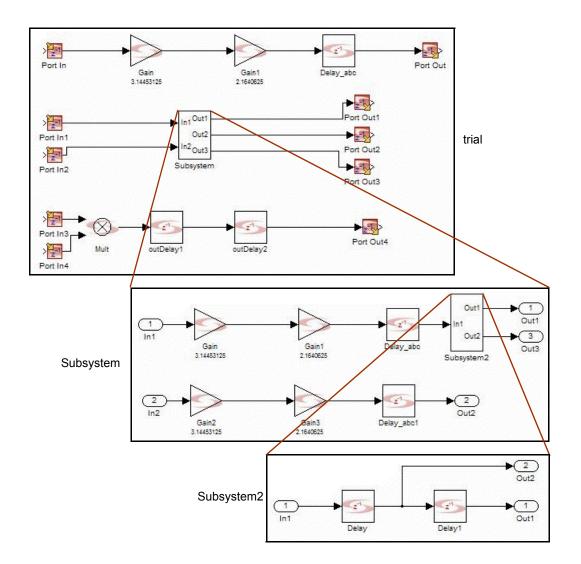

| Hierarchy Preservation                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Subsystem Consolidation                                                                                                                                                                                                                                                                                                                                                                                                                |

| Block Consolidation                                                                       | 912               |

|-------------------------------------------------------------------------------------------|-------------------|

| Constant Propagation                                                                      | 913               |

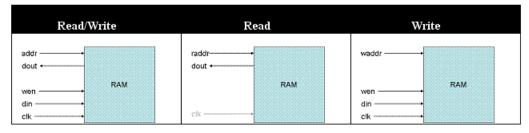

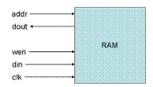

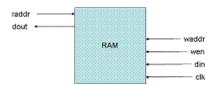

| RAMs<br>RAM Definitions<br>RAM Access Control<br>Port Use in Different RAM Configurations | 915<br>918        |

| Bus Protocols                                                                             | 920<br>925<br>927 |

#### Chapter 9: Designing with the SMC Tool

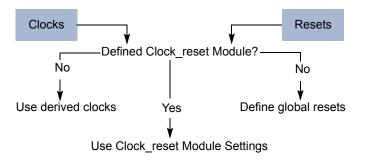

| Defining Clocks and Resets       93         Specifying a clock_reset Module       93         Defining Reset Signals       94                                                                                                                                                                                                                                                                           | 86                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

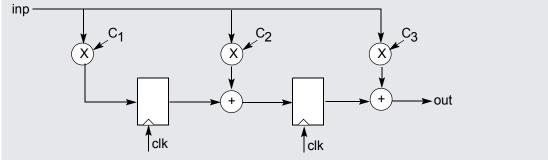

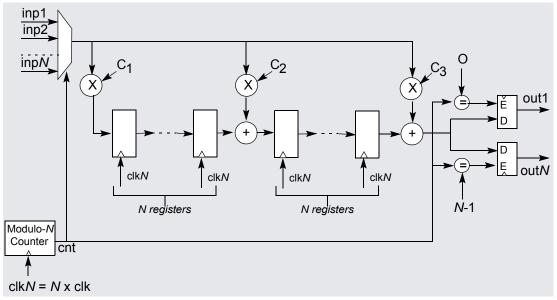

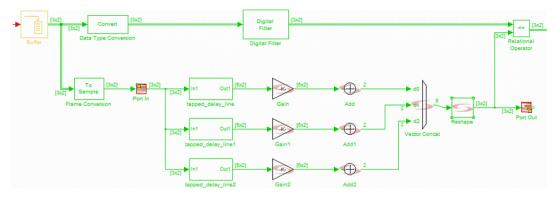

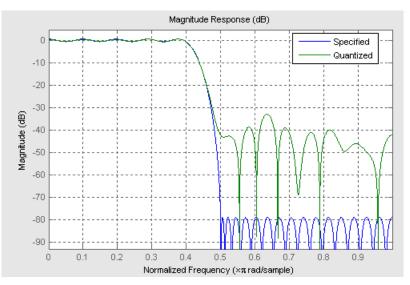

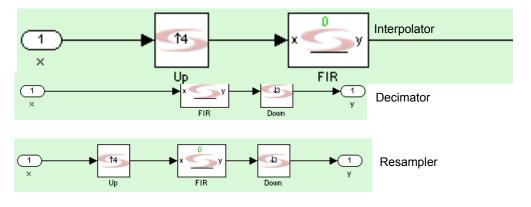

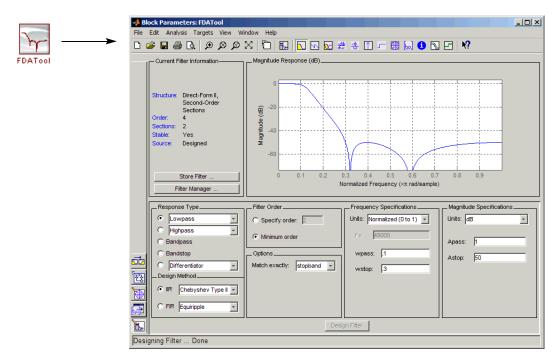

| Designing Filters       94         Implementing FIR Filters with the FIR2 Block       94         Implementing FIR Filters with the FIR Block       94         Implementing Polyphase FIR Filters       94         Defining FIR Filter Coefficients with FDATool       95         Defining IIR Filter Coefficients with FDATool       95         Defining IIR Filter Coefficients with FDATool       95 | 12<br>16<br>19<br>50 |

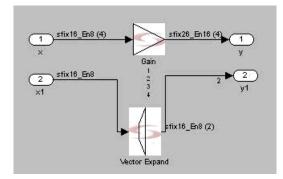

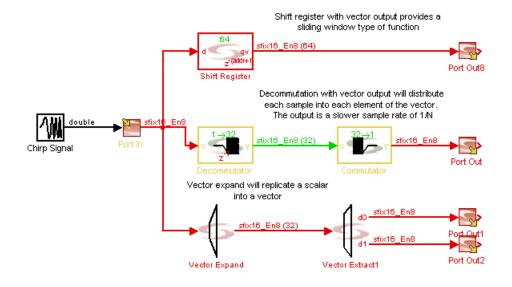

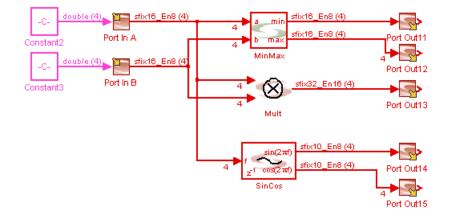

| Working with Vectors       95         Creating Vector Signals       95         Using Math Operations on Vector Signals       95                                                                                                                                                                                                                                                                        | 55                   |

| Specifying ROM Data with syn_read_hex95                                                                                                                                                                                                                                                                                                                                                                | 58                   |

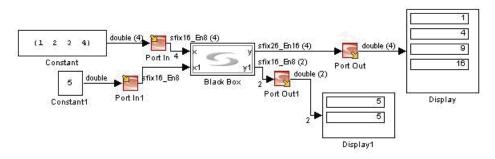

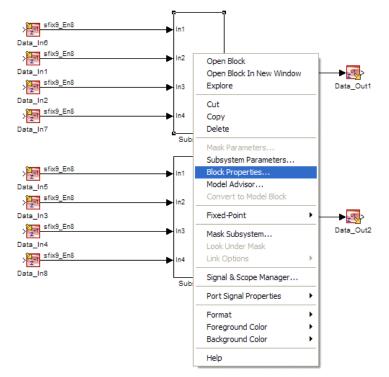

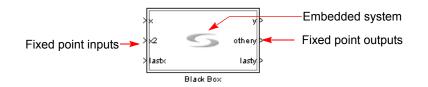

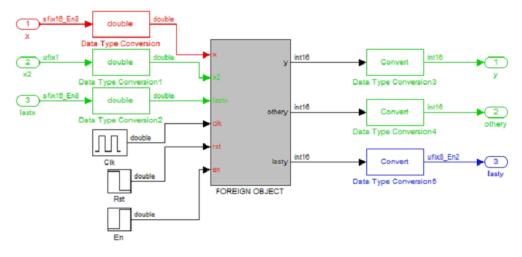

| Using Black Boxes and Third-Party IP       95         Integrating Black Boxes in the Design       95         Setting Black Box Parameters       96         Configuring a Black Box - Example       96         Using Optimizations with Black Boxes       96                                                                                                                                            | 59<br>52<br>54       |

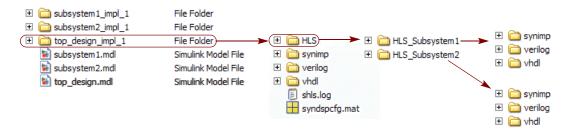

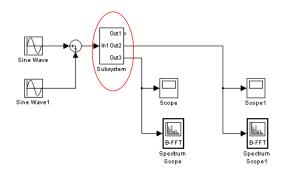

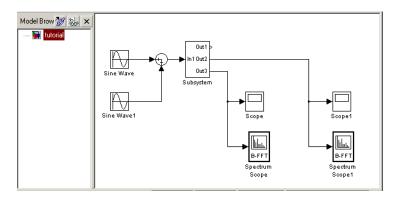

| Managing Subsystems and Hierarchy       96         Using the HLS Subsystem Block       96         Using the Synphony Subsystem Block       97         Tagging Subsystems with FPGA Synthesis Attributes       97                                                                                                                                                                                       | 88<br>75             |

| Using Simulink Accelerator Modes                                                                                                                                                                                                                                                                                                                                                                       | 32                   |

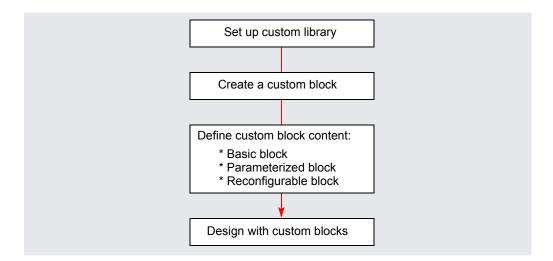

#### **Chapter 10: Working with Custom Blocks**

| Primitives and Custom Blocks              | 984 |

|-------------------------------------------|-----|

| Design Flow for Building Custom Blocks    | 986 |

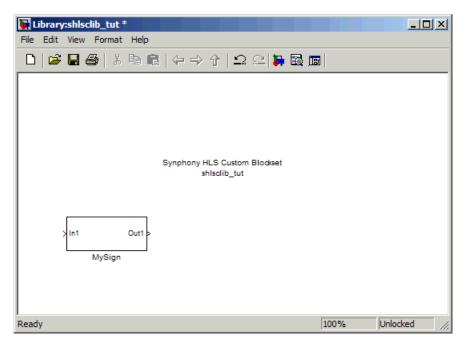

| Set up a Custom Library                   | 987 |

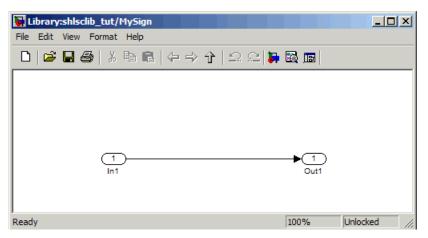

| Create a Custom Block                     | 989 |

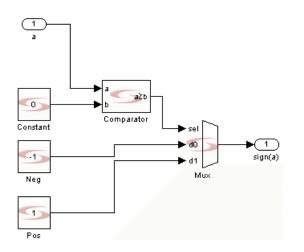

| Define Basic Content for Custom Blocks    | 994 |

| Define Content for Parameterized Blocks   | 997 |

| Define Content for Reconfigurable Blocks1 | 001 |

| Designing with Custom Blocks1             | 005 |

| Maintaining Custom Libraries1             | 006 |

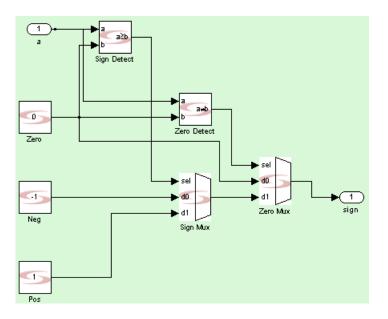

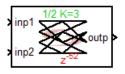

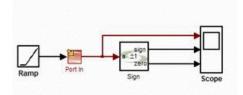

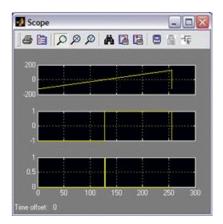

| Creating The MySign M-Generator1          | 006 |

#### Chapter 11: Analyzing and Verifying the Design

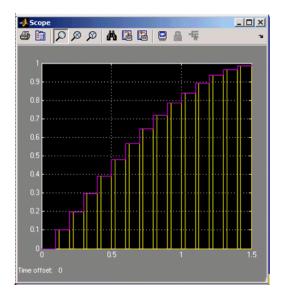

| Using Quantization Analysis Tools                                                                                                                                                                                       | 1012<br>1014         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

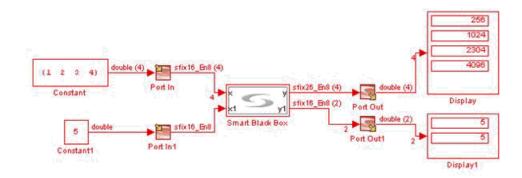

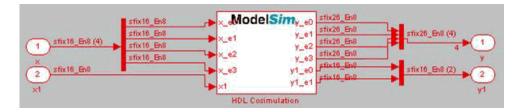

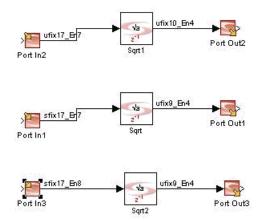

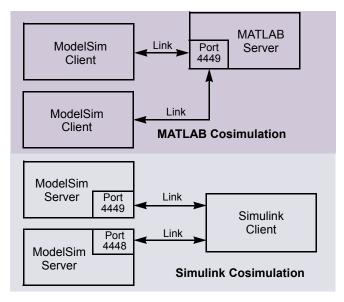

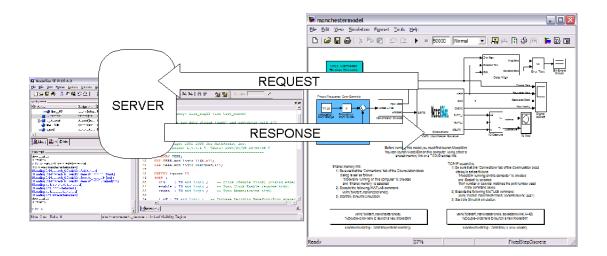

| Using Smart Black Boxes for Cosimulation<br>Incorporating Smart Black Boxes in the Design<br>Configuring the Cosimulation Interface<br>Creating Smart Black Box Configuration Files<br>About Cosimulation with ModelSim | 1017<br>1019<br>1021 |

| Simulating HLS Subsystem Blocks                                                                                                                                                                                         | 1024                 |

| Viewing Simulink Signals in a Waveform Viewer                                                                                                                                                                           | 1026                 |

#### Chapter 12: Working with SMC Output

| Checking the Log File                    | 1030 |

|------------------------------------------|------|

| Verifying the RTL with a Test Bench      | 1033 |

| Working with the Output for FPGA Designs | 1036 |

#### Chapter 13: Using M Code Blocks

| Using M Control Blocks                |        |

|---------------------------------------|--------|

|                                       |        |

| Coding for Synthesis with M Code Bloc | ks1040 |

| M Coding Style104Ports and Timing104M Code Block Data Types104Combinatorial Logic104Persistent Variables104Memories104State Machines105Counters105MATLAB Function that Evaluates to a Constant106User-Defined Functions for M Code Blocks106Overridable Parameters106                     | 42<br>48<br>49<br>49<br>50<br>58<br>60<br>60 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Using Persistent Variables       106         M Code for Persistent Variables       106         Precision Bounds for Persistent Variables       106         Access-Update Sequence for Persistent Variables       106         Conditional Assignments to Persistent Variables       107    | 63<br>65<br>68                               |

| M Code Examples                                                                                                                                                                                                                                                                           | 72                                           |

| M Language Support for M Code Blocks       107         Keywords, Variables, Functions, and Structures       107         Operator Support       107         Built-In Function Support       107         SMC Functions for M Code Blocks       107         M Language Limitations       107 | 74<br>74<br>75<br>78                         |

#### Chapter 14: Working with C Output

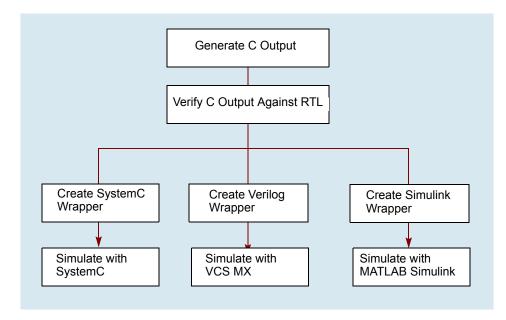

| Design Flow for Working with C Output                                                                                                    | 82       |

|------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Generating C Output Data       108         Generating C Output       108         Generating Output Data Files for C Output       108     | 83       |

| Verifying C Output Against RTL 108                                                                                                       | 86       |

| Simulating C Output                                                                                                                      | 86       |

| Supported APIs for C Output       109         CEvent       109         int CModelDeleteEvent       109         REGISTER_DESIGN       109 | 93<br>95 |

| void * CModelCreateInstance1096int CModelDeleteInstance1097int CModelSetInput1098CModelSetInputInt1099char * CModelGetOutput1100CModelGetOutputInt1101int CModelEvalNext1101CModelGetErrMsg()1103int CSimGetLicense()1105int CSimReleaseLicense()1106 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C Model API Usage                                                                                                                                                                                                                                     |

| Using C Output in Simulink                                                                                                                                                                                                                            |

| Using C Output in MATLAB                                                                                                                                                                                                                              |

| Using C Output with SystemC1115                                                                                                                                                                                                                       |

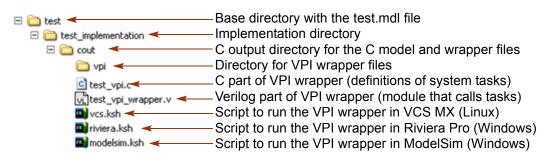

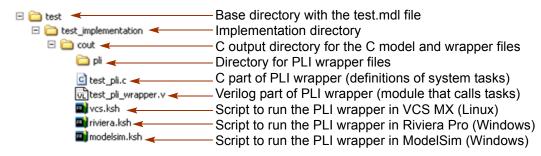

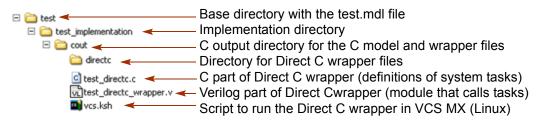

| Using C Output with Verilog-C Interfaces                                                                                                                                                                                                              |

#### Appendix A: Blockset Summary

| SMC Block Summary |  | 1130 |

|-------------------|--|------|

|-------------------|--|------|

#### CHAPTER 1

# **Getting Started**

The following topics provide a general introduction to the Synphony Model Compiler software:

- About The Synphony Model Compiler Tool, on page 20

- Synphony Model Compiler Design Flows, on page 22

- Finding Information, on page 28

- Getting Help, on page 28

## About The Synphony Model Compiler Tool

This section briefly discusses the following topics:

- About the Software, on page 20

- Synphony Model Compiler and MATLAB, on page 21

#### About the Software

The Synphony product is a high-level tool for hardware DSP design. It is an add-on to the Simulink<sup>®</sup> product from The MathWorks<sup>®</sup>, and provides the designer with an automated path from high-level design and simulation to an architecturally-optimized, synthesizable, system-level HDL implementation. This tool provides performance and productivity benefits for designers who are implementing DSP circuits into FPGA devices. The software achieves significantly higher performance than alternative solutions and provides the designer with a mechanism to evaluate high-level area/performance trade-offs. The output is synthesizable HDL code ready for use with the Synopsys<sup>®</sup> Synplify Pro<sup>®</sup> synthesis software.

The software consists of the following components:

- A Simulink blockset

- An automated mechanism to produce a bit-exact, optimized HDL implementation when a Simulink model is created using this blockset

- An automated mechanism to capture test vectors during Simulink simulation

- Automatic HDL test bench generation to verify bit accuracy

#### Value for DSP Algorithm Designers

Using FPGAs for DSP design is a complex task, and the Synphony Model Compiler software makes it easy to maximize the optimizations possible with this design flow. For DSP algorithm designers implementing in FPGAs, the Synphony Model Compiler software does the following:

• Provides a familiar working environment. The Synphony Model Compiler tool plugs into the familiar Simulink and MATLAB environment, so the DSP algorithm designer need not learn a new tool or methodology.

- Automates the design flow by smoothly transitioning from the high-level arithmetic Simulink abstractions to the Synopsys FPGA synthesis tools, with which it is tightly integrated. It eliminates the need for the algorithm designer to learn about physical issues that affect the design.

- Is the only tool that offers a vendor-independent solution for a DSP FPGA implementation. The designer can experiment with different FPGA vendor technologies.

- Includes proprietary optimizations that improve area and performance.

#### Value for Hardware Engineers

For the hardware engineer, the Synphony Model Compiler software does the following:

- Eliminates costly iterations normally required to accurately translate the DSP algorithms, because it generates the necessary RTL code. It eliminates the extra cycles normally required to generate RTL that captures the algorithmic intent of the designer and also accounts for physical issues.

- Makes the hardware engineer's job easier with built-in optimizations that account for hardware considerations. The Synphony Model Compiler tool does DSP-level optimizations (z-domain) using implementation-level constraints like target technology and timing.

- Generates an optional testbench, which can be extremely useful in verifying bit accuracy.

#### Synphony Model Compiler and MATLAB

It is assumed that you have valid licenses for the appropriate versions of the MATLAB<sup>®</sup> and Simulink software from MathWorks and that you are familiar with these products. For FPGA targets, the use model assumes that the Synphony Model Compiler output will be synthesized with the Synplify Pro product from Synopsys, so the designer must have this product and be familiar with its use.

## Synphony Model Compiler Design Flows

This section contains a flow description and a step-by-step procedure.

- Synphony Model Compiler FPGA Design Flow, on page 22

- Design Requirements for RTL Generation, on page 24

- FPGA Design Flow Procedure, on page 25

### Synphony Model Compiler FPGA Design Flow

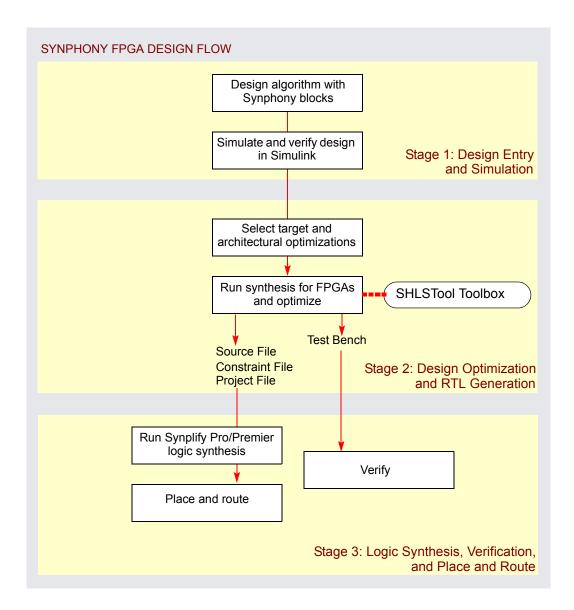

The following figure summarizes the flow for creating an FPGA design, generating RTL code, synthesis, and verification. For more details, see the procedure in FPGA Design Flow Procedure, on page 25. To step through an example using the tool for an FPGA design, refer to the training materials packaged with the tool.

#### Stage 1: Design Entry and Simulation

For this first stage of the flow, use the Simulink software and the Synphony Model Compiler blockset to compose the design. You can use other Simulink blocksets for simulation and debugging, but the software only generates RTL code for blocks from the Synphony blockset. Simulate and verify the design at least once with Simulink to ensure correct functionality. For additional details about the flow, see FPGA Design Flow Procedure, on page 25.

#### Stage 2: Design Optimization and RTL Generation

The strengths of the Synphony Model Compiler software are optimization and RTL generation. To do this, add the SHLSTool block to the design.

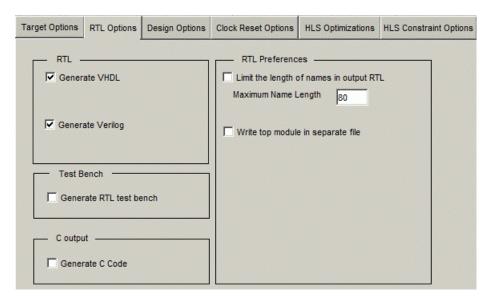

Set system-level optimization settings and the target technology with the SHLSTool block. Use the same block to generate RTL code. The optimizations are targeted towards the FPGA design. For details of the flow, see FPGA Design Flow Procedure, on page 25. The software generates RTL code and an optional test bench.

#### Stage 3: Logic Synthesis, Verification, and Place-and-Route

For this stage, you use synthesis, verification, and place-and-route tools. If you generated a test bench, run it in a VHDL simulator to verify the bit-exactness of the generated VHDL code with respect to the Simulink model. Use the RTL code for logic synthesis with the Synplify Pro software. After synthesis, verify the post-synthesis VHDL code generated by the synthesis software against the Synphony Model Compiler test bench. Then, use the synthesized netlist as input to the place-and-route tool of the FPGA vendor. For additional details about the flow, see FPGA Design Flow Procedure, on page 25.

#### **Design Requirements for RTL Generation**

To generate RTL, you must follow these rules:

- The design must be bound by the Synphony Model Compiler Port In and Port Out blocks. You must define your design boundaries with Synphony Model Compiler Port In and Port Out blocks. If you do not do this, the Synphony Model Compiler tool cannot determine the ports for the RTL description. The generated RTL will not be correct.

- All the blocks that need to be synthesized into RTL must be from the Synphony Model Compiler blockset.

- Do not use the following characters in port, block, subsystem, or signal names in the Simulink model. If you do, the tool might not generate RTL code successfully.

| & Ampersand            | ! Exclamation mark |

|------------------------|--------------------|

| ' Apostrophe           | `Grave accent      |

| * Asterisk             | - Minus            |

| \ Backslash            | # Number sign      |

| ^ Caret                | % Percent          |

| : Colon                | + Plus             |

| , Comma                | ? Question mark    |

| {Curly bracket, open   | ; Semicolon        |

| } Curly bracket, close | ~ Tilde            |

| \$ Dollar sign         |                    |

• Data types that are propagated through any of the Synphony blocks must have a word length that is greater than or equal to the fraction length.

#### **FPGA Design Flow Procedure**

The following procedure describes the steps required to follow the design flow (Synphony Model Compiler FPGA Design Flow, on page 22):

1. Start MATLAB and make sure you are in your design directory. Click the Simulink icon and open Simulink.

- 2. Set up the design.

- Open a model window. For details, see Starting a Synphony Model Compiler Design, on page 821.

- Configure the tool settings and specify the timing mode, as described in Configuring Synphony Model Compiler, on page 818.

- Build your circuit with Synphony Model Compiler blocks. For details, see Working with Synphony Model Compiler Blocks, on page 822.

- 3. Verify the design in Simulink.

- Set simulation parameters and simulate the design using the commands on the Simulate menu. For details, consult the Simulink documentation.

- Use a Simulink simulation with scaled double precision.

- Impose quantization on the design enabling fixed-point data type associations.

- Verify the bit-accurate design with a Simulink simulation.

- 4. Set up the implementation for RTL generation.

- Make sure your design follows the requirements described in Design Requirements for RTL Generation, on page 24.

- In the Simulink window, click Synphony Blockset, and add the SHLSTool block to the design. One instance of this block controls the whole design.

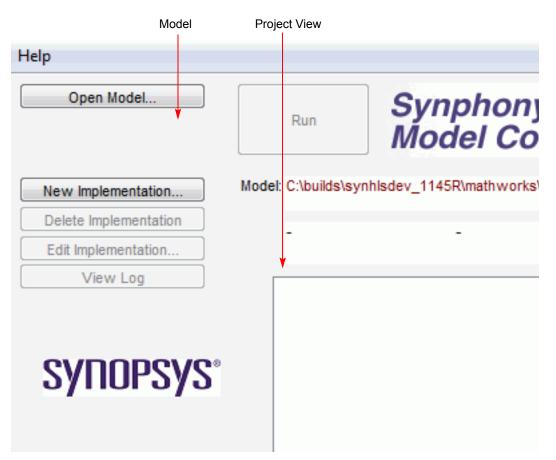

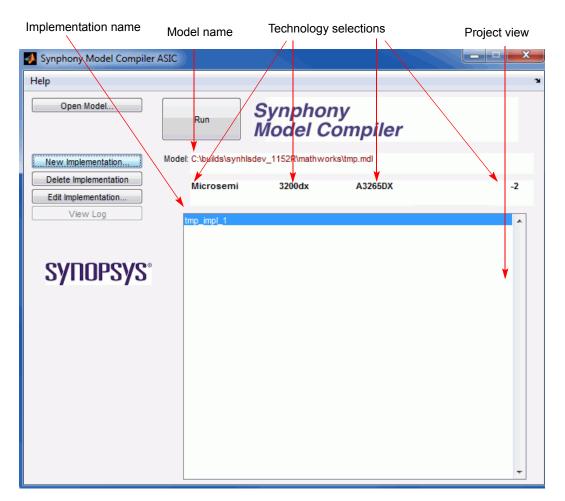

- Double-click the SHLSTool block in the model window to open the Synphony Model Compiler toolbox.

- Set up the implementation and the options for it, as described in Setting up Implementations, on page 824.

- Click OK in the Implementation Options dialog box.

- 5. Click Run in the Synphony Model Compiler window to generate RTL code and output files for the optimized design.

The software generates RTL code for the Synphony Model Compiler block components in the design. It does not generate RTL code for other blocks.

- 6. Run logic synthesis, verify, and place-and-route your design. For details about these tasks, consult the documentation for these tools.

- Start the Synplify Pro or Synplify Premier software and use the source code, constraint, and project files generated in the previous step as input to synthesize your design. If you want to target a different family or device, you can reset that in the synthesis tool when you run synthesis.

- Compare the test bench to post-synthesis gate-level simulation to verify results.

- Place and route the design, using the tool appropriate to your design and vendor.

## **Finding Information**

The following table shows you where to find information:

| For                                                          | See                                               |

|--------------------------------------------------------------|---------------------------------------------------|

| Procedures and tips on using the tool                        | Synthesizing the Design                           |

| Descriptions of individual Synphony Model<br>Compiler blocks | Blocks — By Library<br>Blocks — Alphabetical List |

| Descriptions of command line functions                       | SMC Functions                                     |

| Help                                                         | Getting Help                                      |

## Getting Help

The Synphony Model Compiler software includes documentation, which you can access in the following ways:

- For a printed copy, go to the MATLAB help (Help->Product Help) and select Synphony Model Compiler in the Contents tab of the Help system. Scroll down and open the PDF document (*Release Notes* or *User Guide*) you need. You can print out the PDF documents.

- For online help, open the Contents tab of the Help Navigator, scroll to Synphony Model Compiler, and select the topic you want.

- For context-sensitive online help about blocks in the Simulink library browser, click a block to see a one-line description displayed. Right-click on a block and select Help to display information about the block.

- For context-sensitive online help about blocks in the Simulink model window, right-click on the block and select Help. This displays information about the block.

- For context-sensitive online help on a dialog box, click the Help button.

#### CHAPTER 2

# SMC Blocks: A to Divider

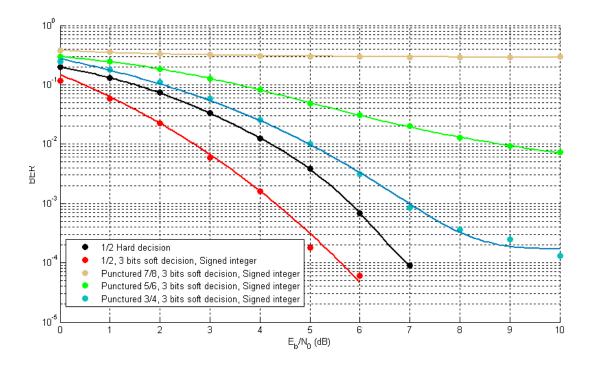

This chapter describes the Synphony Model Compiler blocks and the Synphony Model Compiler custom blocks, categorizing them by library and alphabetically. See the following:

- Blocks By Library, on page 30

- Blocks Alphabetical List, on page 45

Note the following:

- The Synphony Model Compiler library includes some top-level functionality like the SynCoSimTool, SHLSTool and SynFixPtTool toolboxes. They are documented along with the other blocks.

- Some Synphony Model Compiler blocks are classified as custom blocks. For details, and a list of the custom blocks, see Primitives and Custom Blocks, on page 984.

- Some blocks are specialized blocks, and the icons reflect the difference. For example, Black Box, M Control, and the port and subsystem blocks.

- The appendix Blockset Summary, on page 1129, contains a quick reference list of parameters like saturation and word length for different blocks.

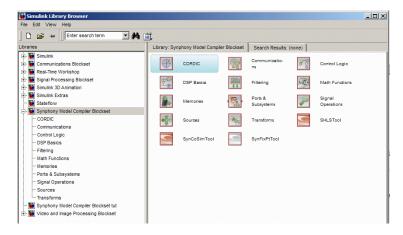

## Blocks — By Library

The Synphony Model Compiler blockset is organized into the block libraries described in the following table. You can access the libraries from the Simulink Library Browser. For an alphabetical list of individual blocks, see Blocks — Alphabetical List, on page 45).

| Communications           | Contains blocks specific to the communications industry.                                                                                                                                                                |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Logic            | Contains blocks that implement logic for controlling datapaths.                                                                                                                                                         |

| CORDIC                   | Contains blocks for specialized CORDIC math operations.                                                                                                                                                                 |

| DSP Basics               | Contains fundamental blocks used for most DSP functions.                                                                                                                                                                |

| Filtering                | Contains blocks for designing and implementing filters.                                                                                                                                                                 |

| Floating Point           | Contains blocks that perform various floating-point computations of math functions.                                                                                                                                     |

| Math Functions           | Contains blocks for specialized math operations.                                                                                                                                                                        |

| Memories                 | Contains blocks for memory structures like RAMs and FIFOs.                                                                                                                                                              |

| Ports &<br>Subsystems    | Contains port and black box blocks.                                                                                                                                                                                     |

| Signal Operations        | Contains blocks for the manipulation of signals.                                                                                                                                                                        |

| Sources                  | Contains blocks that generate constants and counters.                                                                                                                                                                   |

| Transforms               | Contains blocks for transforms that are important to DSP operations.                                                                                                                                                    |

| SMC Set Target<br>Device | Globally sets the target device so that target-specific optimizatons can be run for all the blocks in the design.                                                                                                       |

| SMC SHLSTool             | Specialized toolbox that controls the generation of RTL for<br>synthesis. The toolbox lets you set options in the<br>Implementation Options dialog box, described in<br>Implementation Options Dialog Box, on page 661. |

| SMC<br>SynCoSimTool      | Specialized toolbox that manages the cosimulation interface<br>between the smart black boxes in the design and ModelSim.                                                                                                |

| SMC<br>SynFixPtTool      | Specialized toolbox that opens the Simulink fixed-point interface.                                                                                                                                                      |

#### Communications

This library contains specialized blocks used for DSP designs in the communications industry.

| SMC Barker Code<br>Generator       | Generates Barker code of the specified length.                                                                           |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| SMC Block<br>Deinterleaver         | Reshuffles a fixed number of interleaved input symbols to obtain the original sequence.                                  |

| SMC Block Interleaver              | Shuffles a fixed number of input symbols to a new permutation.                                                           |

| SMC Convolutional<br>Deinterleaver | Reshuffles streaming input symbols according a to a predefined mapping scheme.                                           |

| SMC Convolutional<br>Encoder       | Corrects feed-forward errors using k/n convolutional codes.                                                              |

| SMC Convolutional<br>Interleaver   | Shuffles streaming input symbols to a new permutation, using a predefined mapping scheme.                                |

| SMC CRC Generator                  | Generates CRC bits and appends them to the input data frames.                                                            |

| SMC Depuncture                     | Removes user-specified symbols from the input data stream and replaces them with zeroes.                                 |

| SMC Gold Sequence<br>Generator     | Generates a Gold sequence, with specified polynomials $u$<br>and $v$ , of period $N = 2n - 1$ , called a preferred pair. |

| SMC Hadamard Code<br>Generator     | Generates Hadamard, Walsh, or OVSF codes with code lengths less than 512.                                                |

| SMC Interleaver2                   | Shuffles the incoming data according to a specified permutation vector.                                                  |

| SMC MPSK Baseband<br>Demodulator   | Implements M-ary phase shift keying demodulation.                                                                        |

| SMC MPSK Baseband<br>Modulator     | Implements M-ary phase shift keying modulation.                                                                          |

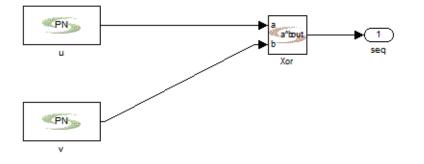

| SMC PN Sequence<br>Generator       | Generates a sequence of pseudorandom (PN) binary numbers using a linear-feedback shift register (LFSR).                  |

| SMC Puncture                                | Removes user-specified bits from the input data stream.                                                                        |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| SMC Rectangular QAM<br>Baseband Demodulator | Implements M-ary quadrature amplitude baseband hard decision demodulation of a complex sequence.                               |

| SMC Rectangular QAM<br>Baseband Modulator   | Implements M-ary quadrature amplitude baseband modulation on the binary input sequence of the vector length/word length log2M. |

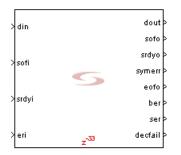

| SMC Reed-Solomon<br>Decoder                 | Decodes the encoded signal using Reed-Solomon error-correcting codes.                                                          |

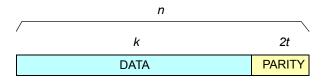

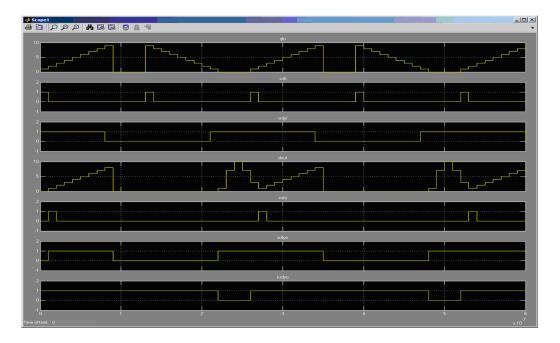

| SMC Reed-Solomon<br>Encoder                 | Generates an encoded signal, using Reed-Solomon codes.                                                                         |

| SMC Viterbi Decoder                         | Decodes convolutionally encoded input data.                                                                                    |

#### **Control Logic**

This library contains blocks that provide control logic for outputs.

| SMC M Control              | Uses an M file to define a function for complex control logic.                             |

|----------------------------|--------------------------------------------------------------------------------------------|

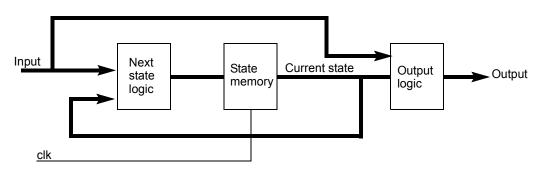

| SMC Mealy State<br>Machine | Provides control logic where the output depends on the input and an internal state vector. |

| SMC Moore State<br>Machine | Provides control logic where the output depends on the current state.                      |

### CORDIC

This library contains blocks for specialized CORDIC math operations.

| SMC CORDIC Exp     | Calculates the natural exponent of the input using the CORDIC algorithm.                                    |

|--------------------|-------------------------------------------------------------------------------------------------------------|

| SMC CORDIC Log     | Calculates the natural logarithm of the input using the CORDIC algorithm.                                   |

| SMC CORDIC Polar   | Calculates $\sqrt{(x^2+y^2)}$ and atan(y/x) where x and y are the inputs.                                   |

| SMC CORDIC Rotator | Implements a fully pipelined CORDIC rotator.                                                                |

| SMC CORDIC SinCos  | Implements a sine and/or cosine generator circuit using a fully parallel CORDIC algorithm in rotation mode. |

| SMC CORDIC Sqrt    | Calculates the square root of the input using the CORDIC algorithm.                                         |

| SMC CORDIC2        | Implements a circular CORDIC (Coordinate Digital Rotation Computer).                                        |

#### **DSP Basics**

This library contains blocks for basic DSP operations.

| SMC Add   | Implements a full-precision signed adder or subtractor.          |

|-----------|------------------------------------------------------------------|

| SMC Delay | Delays the input by the specified number of sample clock cycles. |

| SMC Gain  | Implements a constant gain to the input.                         |

### Filtering

This library contains blocks for designing and implementing filters.

| SMC CIC                         | Custom block that implements a CIC filter.                                                                                                           |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMC CIC2                        | Implements a CIC filter with additional enhancements compared to the CIC block.                                                                      |

| SMC Differentiator              | Custom block that performs a discrete time differentiation of the input signal.                                                                      |

| SMC Dynamic Farrow<br>Resampler | Implements a Farrow filter-based resampler with dynamic channel configuration.                                                                       |

| SMC FDATool                     | Opens the Simulink FDATool interface.                                                                                                                |

| SMC FIR                         | Implements a finite impulse response (FIR) filter.                                                                                                   |

| SMC FIR2                        | Implements fixed and reloadable coefficient FIR filters,<br>including polyphase filters, multichannel filters, and<br>symmetric coefficient filters. |

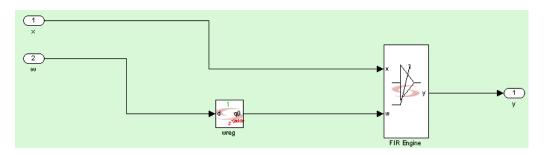

| SMC FIR Engine                  | Implements a finite impulse response (FIR) filter that uses the coefficients as vector input.                                                        |

| SMC FIR Rate<br>Converter       | Implements a polyphase FIR filter.                                                                                                                   |

| SMC FIR Resampler               | Implements a FIR filter based single-clock resampler.                                                                                                |

| SMC Frame FIR                   | Performs FIR filtering in frames. The beginning of a new frame is denoted by a start of frame input ( <b>Sofi</b> ).                                 |

| SMC IIR                         | Implements an infinite impulse response (IIR) filter.                                                                                                |

| SMC Integrator                  | Performs a discrete time integration of the input signal.                                                                                            |

| SMC Min Max Filter              | Computes the running window min/max or both min and max for the input.                                                                               |

| SMC Moving Average<br>Filter    | Implements a hardware efficient moving average filter.                                                                                               |

| SMC Parallel CIC2 | Performs CIC (cascaded integrator-comb) decimation filtering.                 |

|-------------------|-------------------------------------------------------------------------------|

| SMC Parallel FIR  | Implements a parallel input FIR filter.                                       |

| SMC RFIR          | Custom block that implements a reloadable finite impulse response FIR filter. |

#### **Floating Point**

This library contains blocks that perform various floating-point computations of math functions, or convert from fixed to floating-point precision or vice versa. Floating-point processing is needed for some applications that require a higher level of precision.

The SMC floating-point representation differs from the IEE floating-point representation, but you can use the functions described in Floating-Point Interface Functions, on page 881 to convert from one format to another.

| SMC Fixed to FP   | Converts a fixed-point input to the SMC floating-point format with the specified representation.                  |

|-------------------|-------------------------------------------------------------------------------------------------------------------|

| SMC FP Absolute   | Computes the absolute value for a floating-point input.                                                           |

| SMC FP Accumulate | Implements a floating-point accumulator.                                                                          |

| SMC FP Add        | Adds or subtracts two floating-point values.                                                                      |

| SMC FP Arc Tan    | Computes the floating-point arc tangent for a floating-point input phase.                                         |

| SMC FP Burst FFT  | Computes FFT using $N^{1}\log^{2}(N)$ clock cycles and floating-point notation.                                   |

| SMC FP Compare    | Compares two floating-point numbers and returns 1 if the selected condition holds true. Otherwise, 0 is returned. |

| SMC FP Constant   | Sets a constant value for a specified floating-point representation as the output.                                |

| SMC FP Div        | Performs floating-point inversion $(1/x)$ or division $(x/y)$ for the floating-point inputs.                      |

| SMC FP Format<br>Convert | Converts between SMC floating-point formats or between IEEE and SMC floating-point representations.                                                               |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMC FP Fused Mult<br>Add | Performs various multiply-add operations on three/four inputs.                                                                                                    |

| SMC FP IIR Section       | Generates a floating-point IIR filter section.                                                                                                                    |

| SMC FP Inv Sqrt          | Performs the inverse square root (1/sqrt(x)) of a floating-point input.                                                                                           |

| SMC FP Log               | Computes the floating-point logarithm of a floating-point input.                                                                                                  |

| SMC FP Port In           | Converts Simulink double to SMC floating-point format.<br>Can be used instead of SMC Port In to define the RTL<br>generation boundary of floating-point designs.  |

| SMC FP Port Out          | Converts SMC floating-point format to Simulink double.<br>Can be used instead of SMC Port Out to define the RTL<br>generation boundary of floating-point designs. |

| SMC FP Pow               | Computes the base <sup>x</sup> in floating-point, where x is a floating-point number and base is specified on the mask.                                           |

| SMC FP SinCos            | Computes the floating-point sine and cosine outputs for a floating-point phase input.                                                                             |

| SMC FP Sqrt              | Computes the floating-point sine and cosine outputs for a floating-point phase input.                                                                             |

| SMC FP Square            | Performs squaring of a floating-point input.                                                                                                                      |

| SMC FP Tan               | Computes the floating-point tangent of an input angle.                                                                                                            |

| SMC FP to Fixed          | Converts an input SMC floating-point format to a signed fixed-point format for the specified word length and fraction length.                                     |

| SMC FP Mult              | Multiplies two floating-point values.                                                                                                                             |

| SMC FP Vector Add        | Adds elements of the input vector to provide scalar output.                                                                                                       |

## **Math Functions**

This library contains blocks for specialized math operations.

| SMC Abs            | Calculates the absolute value of the scalar input.                                                                           |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| SMC Accumulator    | Implements an accumulator with optional reset and enable.                                                                    |  |

| SMC Add            | Implements a full-precision signed multi-input adder.<br>Selected inputs can be configured for addition or<br>subtraction.   |  |

| SMC ArcSinCos      | Computes asin and acos of the input x in radians.                                                                            |  |

| SMC Barrel Shifter | Implements a barrel shifter.                                                                                                 |  |

| SMC Binary Logic   | Calculates bitwise binary logic functions on the inputs.                                                                     |  |

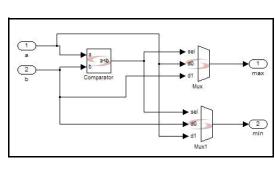

| SMC Comparator     | Implements a programmable comparator.                                                                                        |  |

| SMC Complex Abs    | Computes the magnitude of a complex number using a linear approximation.                                                     |  |

| SMC Complex Mult   | Multiplies two complex numbers.                                                                                              |  |

| SMC Divider        | Calculates the fixed-point fractional division of two inputs, A and B.                                                       |  |

| SMC Divider2       | Extends the functionality of the SMC Divider block by providing bit iterative and streaming multiplier-based division modes. |  |

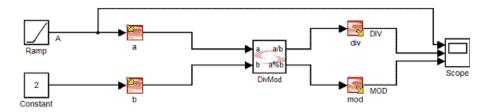

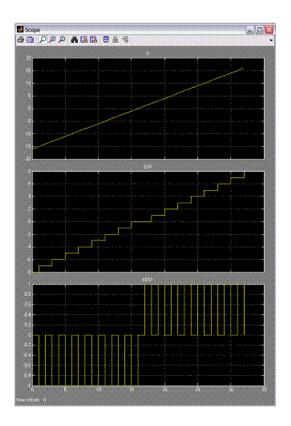

| SMC DivMod         | Calculates the integer division and/or modulo function of two inputs, A and B. $\!\!\!$                                      |  |

| SMC Frame Mean     | Computes arithmetic mean of inputs.                                                                                          |  |

| SMC Gain           | Implements a constant gain to the input.                                                                                     |  |

| SMC Inverter       | Calculates the inverse (one's complement) of the input.                                                                      |  |

| SMC Log            | Calculates the natural logarithm of the input.                                                                               |  |

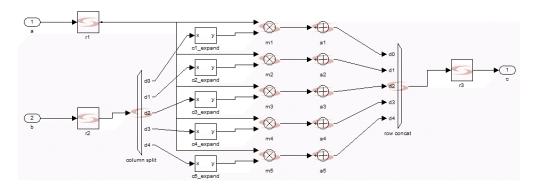

| SMC Matrix Mult    | Implements matrix multiplication of a two-input matrix signal.                                                               |  |

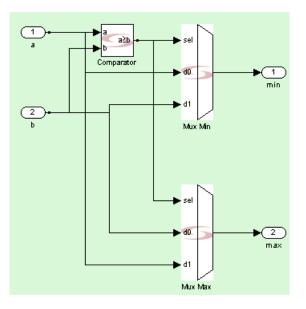

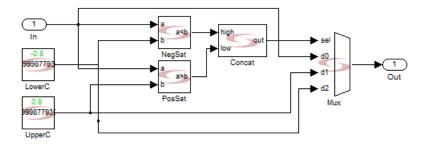

| SMC MinMax          | Custom block that calculates the minimum, maximum, or minimum and maximum of two inputs.                          |

|---------------------|-------------------------------------------------------------------------------------------------------------------|

| SMC Mult            | Implements a full-precision multiplier.                                                                           |

| SMC Negate          | Computes the two's complement (arithmetic negation) of a signed input.                                            |

| SMC Pow             | Raises a value to the power of another value.                                                                     |

| SMC Shifter         | Performs a variable left or right shift on the input signal.                                                      |

| SMC Sign            | Custom block that provides the 2-bit sign value (+1 or -1) for the input.                                         |

| SMC SinCos          | Calculates $sin(2\pi f)$ or $cos(2\pi f)$ for the input.                                                          |

| SMC SinCos2         | Creates sin and cos waveforms based on the input phase and amplitude values.                                      |

| SMC Sqrt            | Calculates the square root of the input.                                                                          |

| SMC Sum of Products | Multiplies inputs with gain values and calculates the sum<br>of the computed products to provide a scalar output. |

## **Memories**

This library contains blocks for memory structures like RAMs and FIFOs.

| SMC Delay                            | Delays the input by the specified number of sample clock cycles.                                                                                    |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| SMC Dynamic Access<br>Shift Register | Same as the SMC Shift Register. However, this block is implemented using RAM so that it can be mapped with good QoR on FPGA devices with Block RAM. |

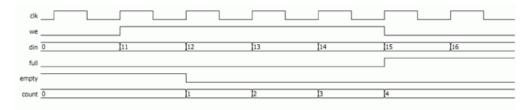

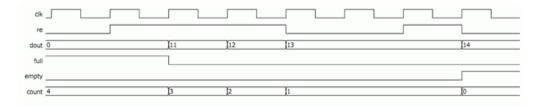

| SMC FIFO                             | Implements a synchronous FIFO (First in First Out) memory queue.                                                                                    |

| SMC Flow Control<br>Buffer           | Provides forward or backward flow control.                                                                                                          |

| SMC Loadable Shift<br>Register       | Implements the shift register with loadable reset and same cycle enable and reset functionality.                                                    |

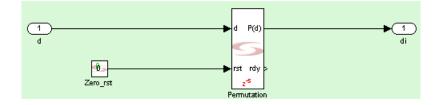

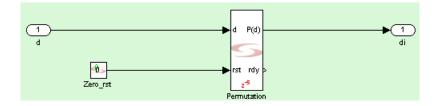

| SMC Permutation                      | Shuffles the incoming data according to a specified permutation vector.                                                                             |

| SMC RAM                              | Implements a memory function through a storage array that has read and write access through ports.                                                  |

| SMC RAM Based<br>Delay               | Implements delay using RAM and appropriate pipelines on the read and write address sides.                                                           |

| SMC Register                         | Inserts a delay.                                                                                                                                    |

| SMC ROM                              | Models a read-only memory (ROM) with a latency of one sample.                                                                                       |

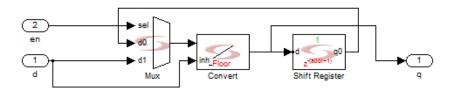

| SMC Shift Register                   | Implements a delay line with dynamic or static access to intermediate taps.                                                                         |

## Ports & Subsystems

This library contains port and black box blocks.

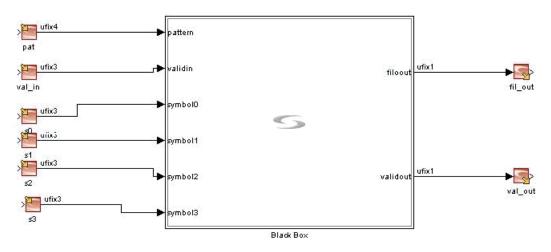

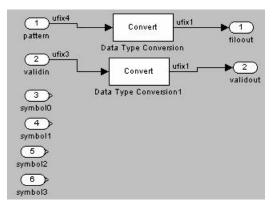

| SMC Black Box              | Provides a way to embed other blocks.                                                                                                                                     |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

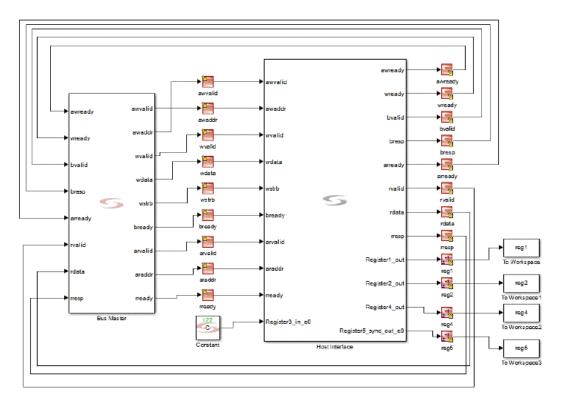

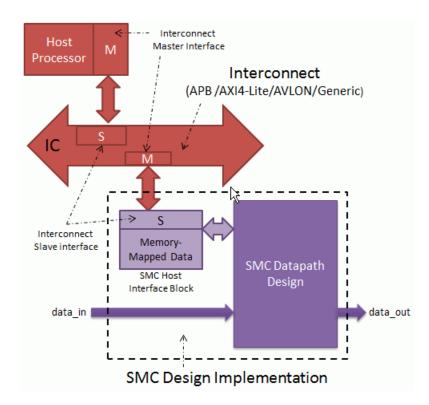

| SMC Bus Master             | This simulation-only block, verifies the functionality of the<br>Host Interface block and can send the memory map data<br>to the Host Interface block for the SMC design. |

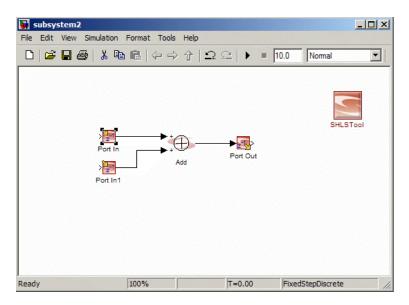

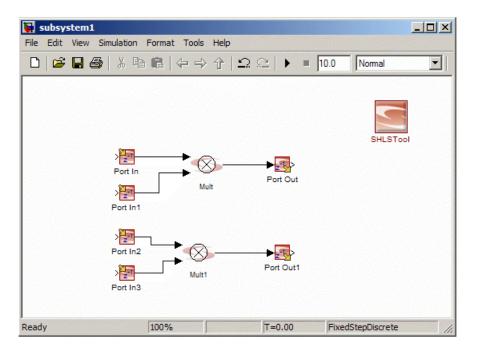

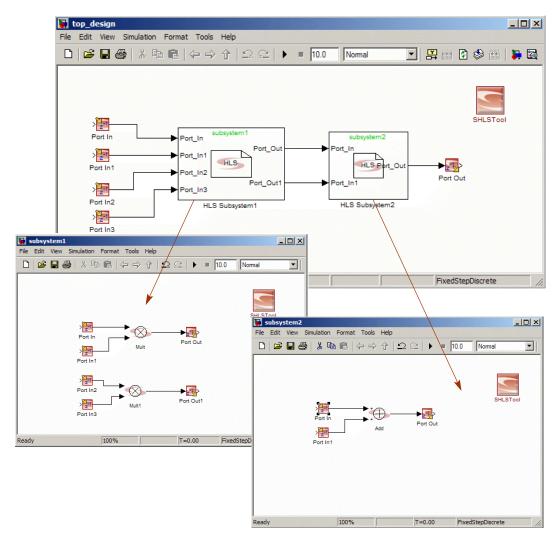

| SMC HLS Subsystem          | Lets you add a previously designed Synphony model to<br>the current design and set implementation settings for it.                                                        |

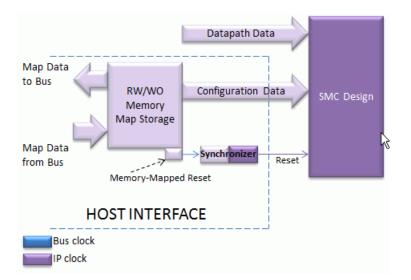

| SMC Host Interface         | Provides an interface to the host processor using a simpler bus protocol to configure the design.                                                                         |

| SMC In                     | Provides a way to add an in port to a subsystem                                                                                                                           |

| SMC Out                    | Provides a way to add an out port to a subsystem                                                                                                                          |

| SMC Port In                | Defines the input boundaries for the DSP design to be implemented in RTL.                                                                                                 |

| SMC Port Out               | Defines the output boundaries for the DSP design to be implemented in RTL.                                                                                                |

| SMC RTL<br>Encapsulation   | Embeds and simulates RTL blocks inside their Simulink<br>model without the need of external RTL simulators or<br>special Simulink features.                               |

| SMC Smart Black Box        | Lets you embed third-party IP in a Synphony Model<br>Compiler design.                                                                                                     |

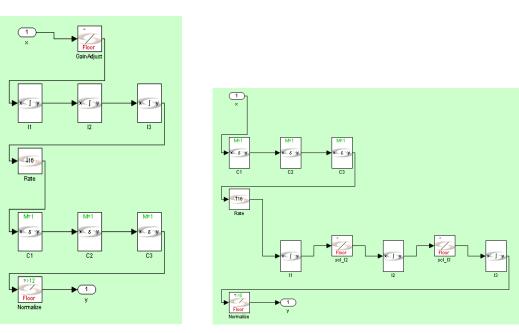

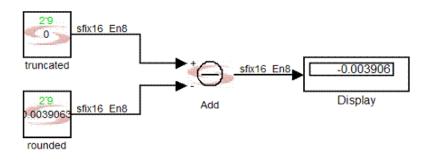

| SMC Subsystem              | Allows you to add a subsystem to a Synphony Model<br>Compiler design.                                                                                                     |