# Board Design Recommendations for ZL30260 – ZL30267, ZL40250 – ZL40253 and ZL30282 Devices

## Introduction

This document is intended to provide circuit design and PCB layout guidelines for the ZL30260 – ZL30267 series of any-to-any clock multiplier integrated circuits (ICs), the ZL40250 – ZL40253 series of SmartBuffer integrated circuits, and the ZL30282 Six-Output PCIe Clock Generator.

# **Power Supply**

Jitter levels on the clock output of a timing device may increase if the device is exposed to noise on its power supply pins. For optimal jitter performance, the device should be isolated from noise on power planes as recommended by the Microsemi application notes relevant for that particular device. The recommendations in these application notes should cover most of the real life situations. In extremely noisy environments the user should consider linear regulators to generate the supply voltage for the timing device.

The application note ZLAN-592 covers the power supply decoupling recommendations for the ZL30260 – ZL30267 and ZL30282 series.

The application note ZLAN-593 covers the power supply decoupling recommendations for the ZL40250 – ZL40253 series.

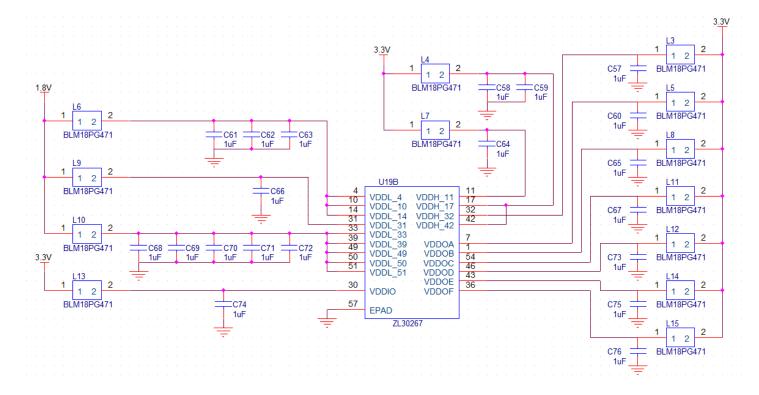

The following section shows the application of ZLAN-592 recommendations to a ZL30267 device which has all output clock signals configured to use a 3.3 V supply.

The PCB placement and routing presented below are intended for reference. Other valid implementations are possible as long as the main guidelines outlined below are followed.

A similar approach must be followed when the ZLAN-593 recommendations are implemented on a printed circuit board (PCB) design.

September 2017

Figure 1 · ZL30267 Power Supply Decoupling Scheme Example

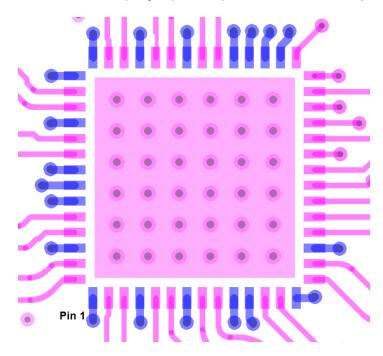

The ZL30267 device is located on the top layer (primary side) of the PCB. The breakout vias for the power supply pins (highlighted in the following picture) are placed as close as possible to the pins to minimize the length of the power supply routing to the internal power layers and to the decoupling capacitors placed on the bottom layer.

Figure 2 - ZL30267 Device Placed on the Top Layer of the PCB

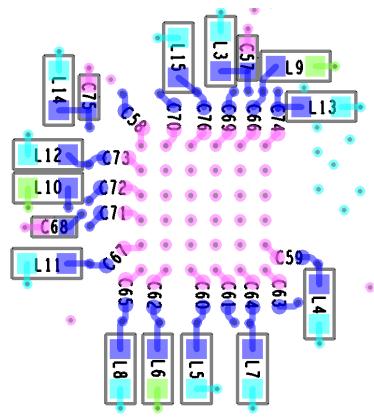

All of the decoupling capacitors are placed on the bottom layer of the PCB. Most of the  $1\mu F$  capacitors are placed between the ZL30267 power supply breakout vias and the GND vias located in the thermal pad, in order to minimize the distance to the timing device. The 0402 footprint used at these locations has round pads to facilitate this compact placement.

The GND vias in the thermal pad have solid connections to all the internal GND planes.

Figure 3 · Decoupling Placement on the Bottom Layer (through PCB view)

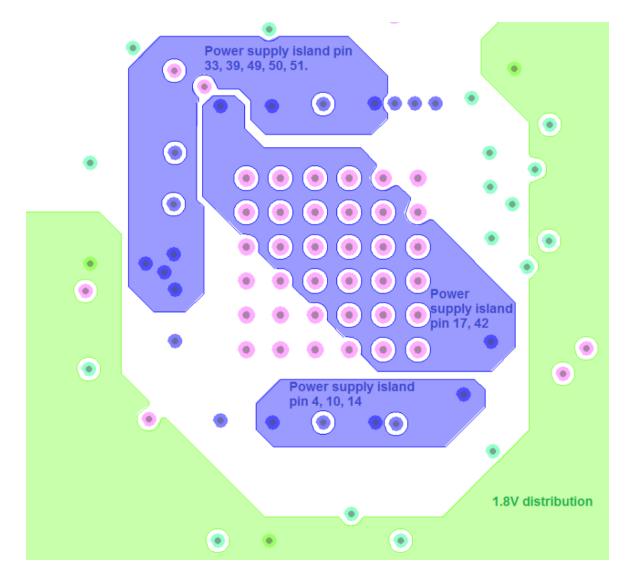

One internal layer is used to implement the distribution of the 1.8V power supply rail and the three power supply islands; see picture below. Another layer is used for the distribution of the 3.3V power supply rail.

Figure 4 · Internal Layer Implementation of Power Supply Islands and 1.8V distribution

## **Local Reference**

ZL30260 – ZL30267, ZL40250 – ZL40253, and ZL30282 series devices can use an oscillator or a crystal as a local reference clock. The jitter on the output of the timing device is directly impacted by the jitter of this local reference clock. For this reason it is important to provide a low jitter local reference clock.

#### **Local Oscillator**

Whenever possible, select the highest recommended oscillator frequency. The higher the oscillator frequency, the lower the jitter on the output of the timing device.

As a general rule, the oscillator must be placed on the PCB as close as possible to the timing device in order to minimize the length of the clock signal track and to reduce the possibility of noise coupling from adjacent circuits. The signal trace should be properly terminated to minimize reflections.

Noise on the oscillator's power supply can dramatically increase the jitter on its output clock. The oscillator must be supplied with a clean voltage in order to minimize the jitter caused by power supply noise.

LC filters are an effective way to filter noise with frequencies above 50-100KHz. For lower noise frequencies, the LC filtering becomes unfeasible due to the size of the LC components that have to be used. The alternative solution is to use a low dropout regulator.

In most situations, a power isolation filter consisting of a ferrite bead and several capacitors is enough to attenuate the voltage noise on the oscillator power supply to levels that are no longer impacting the output jitter.

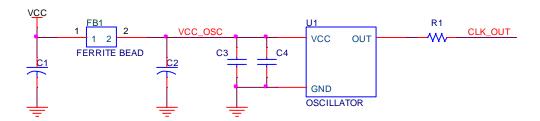

Figure 5 - Typical Power Supply Decoupling Circuit Recommended for Oscillators

C1 and C2 attenuate the low frequency noise on the VCC rail. Use a low ESR, 22-33 $\mu$ F, capacitor (usually tantalum /Polymer/Os\_Con type) in a package that allows migration to larger values up to 100 $\mu$ F (for example, a 1206 package).

C3 and C4 provide a low impedance path to GND for high frequency noise. Use 100nF and 10nF 0402, X7R or X5R, multilayer ceramic capacitors.

FB1 is used to increase the insertion loss of the filter. The ferrite bead should have a saturation current double the maximum supply current of the oscillator and an impedance of several hundred ohms at 100MHz. It should have also a low DC resistance in order to prevent a large voltage drop across the ferrite bead. Some examples of ferrite beads which can be used for this purpose are: BLM18PG121, BLM18PG221 or BLM18PG471 from Murata.

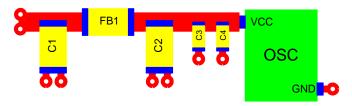

In layout, place C3, C4 as close as possible to the oscillator VCC pin and minimize the mounted inductance introduced by the layout that limits the effectiveness of the capacitors (via close to pads, multiple via).

Figure 6 · Recommended Layout Placement of the Power Supply Decoupling Circuit

### **Local Oscillator Buffering**

In order to reduce the cost, some designers are tempted to use a single local oscillator to feed several timing devices through a fan-out buffer. Microsemi does not recommend this approach; any buffer added on the local oscillator clock path will increase its jitter and will increase the jitter on the output of the timing circuit.

If a particular design can accommodate a higher output clock jitter, a buffer can be used. In this case it is important to select a clock fan-out buffer with very low additive jitter. The power supply of the buffer must be properly filtered using a circuit similar with the one suggested for the oscillator. The clock tracks should be properly terminated and routed as short as possible to minimize noise coupling from other circuits.

## **Crystal**

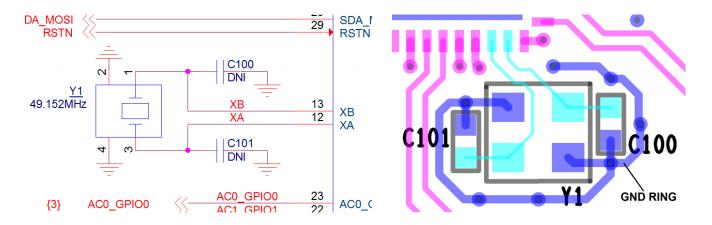

The on-chip crystal driver circuit is designed to work with fundamental mode AT-cut crystal resonators and includes configurable internal load capacitors. Based on the crystal's specification and PCB implementation, external capacitors may or may not be required. The datasheet provides the recommended crystal specifications required to properly select a crystal and also the methodology and an example of how to calculate and setup the load capacitors. In the example below, used to illustrate the PCB implementation of the crystal oscillator, external load capacitors are used.

When designing the PCB layout consider the following recommendations to reduce the crosstalk of other signals:

- Place the crystal as close as possible to the timing chip.

- Place the external load capacitors (if are required) close to the crystal pins.

- · Minimize the length of XA and XB signal tracks.

- Place a GND ring around the crystal circuits.

- Have a GND plane on the internal layer underneath the crystal circuits. If a GND plane is not available on the first layer underneath, avoid routing any signals in that area.

Figure 7 · Example of Crystal Circuit Implementation. Schematic and PCB View.

# Output Clock Distribution.

In cases where a clock is to be provided to several circuits, and there are not enough outputs available to achieve this, an external fan-out buffer can be used.

In order to minimize the jitter introduced by the fan-out buffer, consider the following recommendations:

- Use Microsemi low jitter fan-out buffers; visit www.microsemi.com/timing-and-synchronization for clock buffer selection.

- Properly decouple the power supply of the fan-out buffer as recommended by Microsemi datasheet for that specific device.

- Properly terminate the inputs and the outputs as recommended by Microsemi datasheet for that specific device.

- Use differential paired clocks where possible, especially for longer route lengths transitioning "noisy" areas of the PCB.

## Layout Recommendations.

One characteristic common to most of the modern electronic systems is the increased density of the circuits on the PCBs. The designer must pack together in a limited space noisy circuits like switch mode power supplies and big digital ICs with noise-sensitive clocking and analog circuits. While it is difficult to meet all the conflicting constraints generated by this situation, a bit of planning and following some simple rules can help to find an acceptable compromise solution. Here are some of the elements to consider at the layout design stage:

- Place the clocking circuits in "low noise" areas of the board away from switching mode power supplies, big/noisy digital circuits (FPGA/ASICs) and the high current path associated with them.

- Limit the length of the clock traces.

- Match the length of the p and n signals within a differential pair.

- Use controlled impedance routing and proper terminations for high speed signals/clocks as a way to preserve the signal integrity of the signal and reduce noise emission.

- Avoid routing the clock traces over discontinuities in the reference GND and power planes.

- Use extra clearance between clock tracks and adjacent signals (especially when they

are high speed / fast slew rate signals) to reduce the crosstalk.

- In the case of differential pairs, keep a minimum clearance of at least 2S between pairs; where S is the spacing between P and N tracks of a differential pair.

- Minimize the use of via in the clock traces. Avoid unnecessary bends; when necessary use 45° or round bend.

- When power decoupling implementation involves local power islands, minimize the

capacitive coupling between power islands and between the power islands and the

main power planes (try to not overlap them when are in adjacent layers not separated

by a GND plane layer). Avoid routing noisy digital signals in adjacent layers next to the

power islands.

- Make the connection between power supply pins (VCC and GND) and power planes as short as possible using a dedicated via and tracks wider than for regular signals (minimize the impedance of this connection). No via sharing between power supply pins.

- Place the decoupling capacitors as close as possible to the power pins of the IC. Place break out via as close as possible to the capacitor pins and connect them with tracks wider than for regular signal. No via sharing between decoupling. When possible use multiple via breakout to reduce further the impedance of this connection.

- On power distribution path, minimize the number of layer changes. Use multiple via at each layer change to limit the voltage drop especially on high current paths.

- Stack-up selection. It is preferable to route the clock traces on the signal layers placed between GND layers or GND and Power layers. If there are two signal layers adjacent in the stack-up, keep a 90deg angle between the routing directions of the two layers in order to minimize the crosstalk. For example route the signals East/West on one layer and North/South on the other.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.