# Timberwolf Digital Signal Processor family, powered by *AcuEdge*™ Technology

Designed for USB Audio Accessories

ZL38090

Product Brief

## **Description**

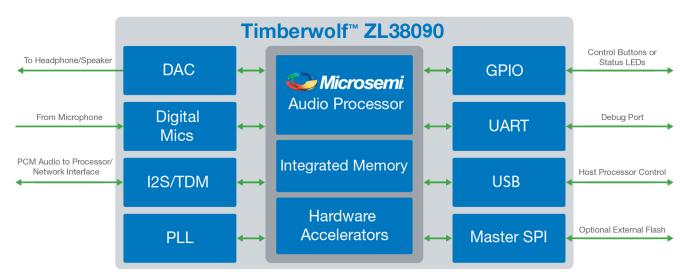

The ZL38090 is part of Microsemi's Timberwolf audio processor family of products that feature the company's innovative *AcuEdge* acoustic technology, which is a set of highly-complex and integrated algorithms. These algorithms are incorporated into a powerful DSP platform that allow the user to extract intelligible information from the audio environment.

The Microsemi *AcuEdge* Technology ZL38090 device is ideal for Universal Serial Bus (USB) Audio Accessories. The device is available in a 64 pin QFN or 56 ball WLCSP package. Its license-free, royalty-free intelligent audio Firmware (ZLS38090) provides Beamforming and a variety of other voice enhancements to improve both the intelligibility and subjective quality of audio.

Microsemi offers the  $MiTuner^{TM}$  ZLS38508LITE GUI software package allowing a user to interactively configure the ZL38090 device.

### **Applications**

- Unified Communication Devices

- USB Boom and Boomless Headsets

- · USB Beamforming Microphones

- USB Speakerphone

- · USB Speakers

**Typical USB Headset Application**

Document ID# 153166

Version 2

May 2016

#### **Ordering Information**

| Device OPN  | Package                                     | Packing         |

|-------------|---------------------------------------------|-----------------|

| ZL38090LDF1 | 64-pin QFN (9x9)                            | Tape & Reel     |

| ZL38090LDG1 | 64-pin QFN (9x9)<br>56-ball WLCSP(3.05x3.09 | _ T <u>r</u> ày |

| ZL38090UGB2 | 56-ball WLCSP(3.05x3.0                      | 5) Tape & Reel  |

|             |                                             |                 |

These packages meet RoHS 2 Directive 2011/65/EU of the European Council to minimize the environmental impact of electrical equipment.

## Microsemi *AcuEdge* Technology ZLS38090 Firmware Audio Features

- Supports 1 stereo headset pair with play and record or just playback functions

- Microphone Beamforming (2 microphones)

- · Standard Dynamic Range Compressor

- Limiter

- Expander

- Send and receive path 8-band parametric equalizers

- 8 kHz/16 kHz/48 kHz audio streaming

- 14 General Purpose Input/Outputs (11 in the WLCSP package) with fixed function capability for:

- Volume Up/Down, Mute Mic, and Hook-Switch On/Off

- · PWM outputs for LED control

#### **Common USB Features**

- USB Audio Class Device v1.0 compliant

- Adaptive mode for playback, Asynchronous mode for record

- USB Audio Class clock modes

- Remote wake-up via fixed function GPIO

- Common HID controls for volume, mute, equalizer, and audio source and destinations

- A USB port enumerates with:

- · EP0 (Control)

- 2 endpoints for Microphones and Speakers (both stereo)

- 1 interrupt endpoint (for Status Reporting)

- Skype/Lync Compatible

# Timberwolf Digital Signal Processor family, powered by *AcuEdge™* Technology

Designed for USB Boom and Boomless Headsets

ZL38090

Product Brief

Stand alone USB device (additional host processor not required for headphone applications)

#### **ZL38090 Common Hardware Features**

- · DSP with Voice Hardware Accelerators

- Dual  $\Delta\Sigma$  16-bit digital-to-analog converters (DAC)

- Sampling up to 48 kHz and internal output drivers

- Headphone amplifiers capable of 32 mW output drive power into 16 ohms

- · Impulse pop/click protection

- · 2 Digital Microphone inputs

- TDM port shared between PCM and Inter-IC Sound (I<sup>2</sup>S)

- General purpose UART port for debug

- · Boots from SPI or Flash

- · Master SPI port for serial Flash interface

- Can run unattended (controllerless), selfbooting into a configured operational state

For ease of mounting, the ZL38090 is available in two packages.

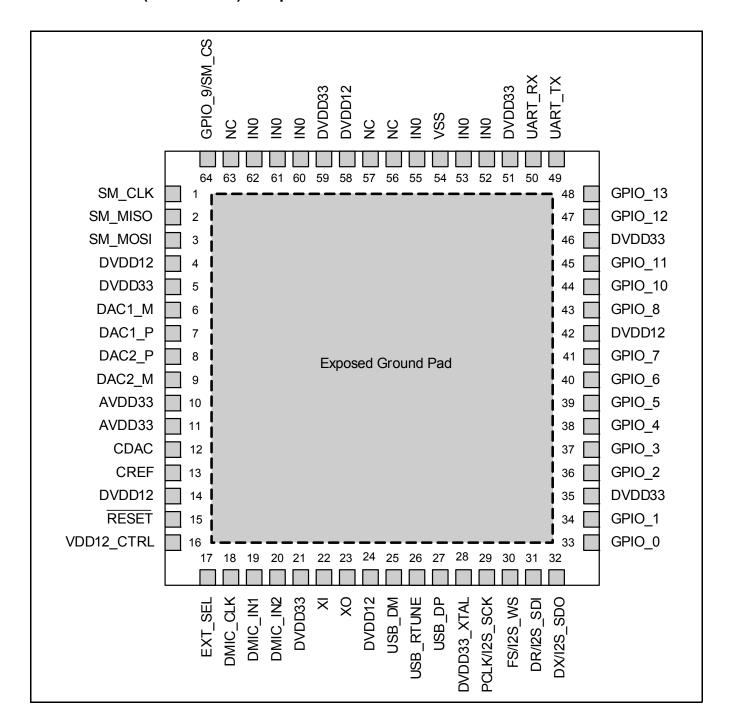

#### **QFN Hardware Features**

- 64-pin QFN

- 9 mm by 9 mm package size

- Headphone amplifiers can be configured as 2 differential or 4 single-ended outputs

- 4 Fixed Function PWM pins for Vol Up, Vol Down, Mute, and Hook Switch control and status

- 14 General Purpose Input/Output (GPIO) pins

- Internal +1.2 V voltage regulator

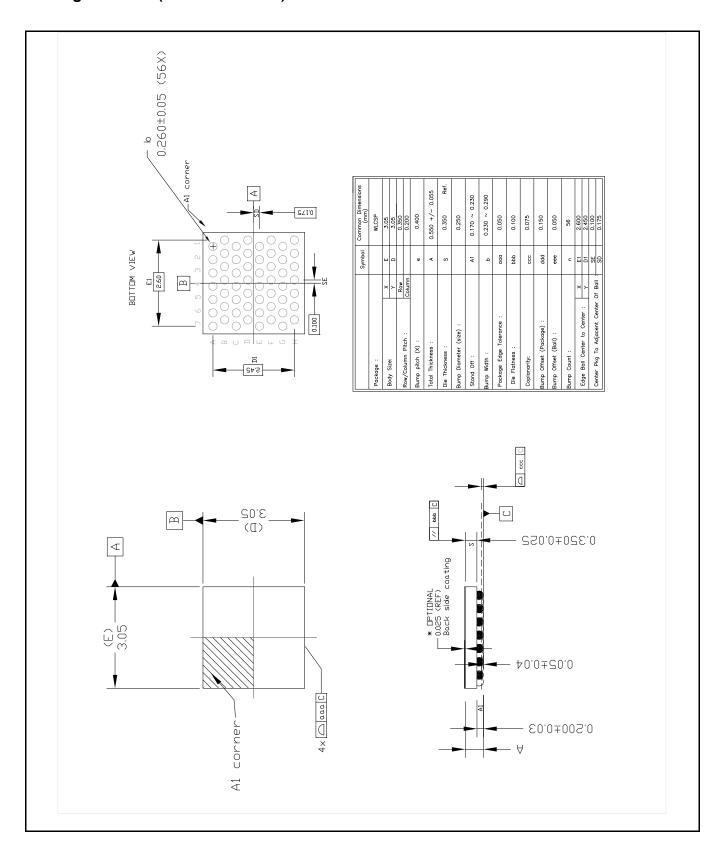

#### **WLCSP Hardware Features**

- 56-ball Wafer Level Chip Scale Package

- 3.05 mm by 3.05 mm package size

- Headphone amplifiers can be configured as 2 single-ended outputs

- 4 Fixed Function PWM pins for Vol Up, Vol Down, Mute, and Hook Switch control and status

- 11 General Purpose Input/Output (GPIO) pins

#### Tools

- ZLK38000 Evaluation Kit

- MiTuner™ ZLS38508LITE GUI software

ZL38090 Audio Processor for USB Headsets

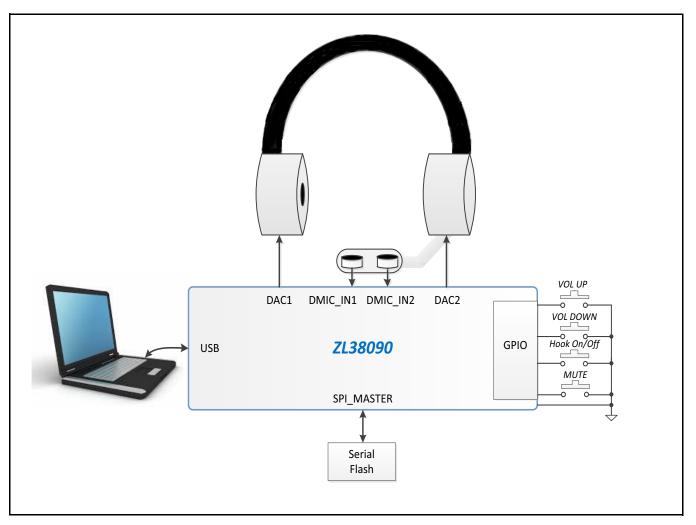

#### **Typical Headset Application**

The ZL38090 functions as a complete USB Audio device. The ZL38090 does not require a separate host processor to operate. It it is designed to meet the Skype Certification/Lync Logo specification for a headset. The USB port can be connected to any computer or gaming system. All device controls can be accessed through the USB port, including a subset of basic functions (preset modes) that can be wired to the GPIO pins to provide volume up/down, mute, or special programmable commands.

The ZL38090 has two internal differential headphone speaker amplifiers that can drive stereo signals directly into 16/32 ohm headphones.

Digital microphones can be connected to the ZL38090 DMIC interface, providing a low noise audio pick-up. The ZL38090 can perform beamforming when two microphones are used. Analog microphones can be used with the addition of an electret microphone pre-amplifier device.

The ZL38090 has a TDM port that can be used to route audio, or audio can be routed through the USB port.

**USB Headset Block Diagram**

Note: When using the WLCSP package option, the headphone speaker amplifiers (DAC1 and DAC2) have single-ended stereo drive.

## **ZLK38090 Evaluation Kit**

The ZLK38090 Evaluation Kit includes all the hardware necessary to operate the ZLE38090 Evaluation Board. The Evaluation Board provides a flexible platform to evaluate a ZL38090 Timberwolf Audio Processor device with  $AcuEdge^{TM}$  Technology Firmware. Firmware Code for the ZL38090 can be downloaded into the Evaluation Board using the ZLS38000 Firmware Loader software. The ZLE38090 Evaluation Board can then be controlled using the  $MiTuner^{TM}$  GUI Lite Software (ZLS38508LITE).

## Device Pinout (64-Pin QFN) - Top View

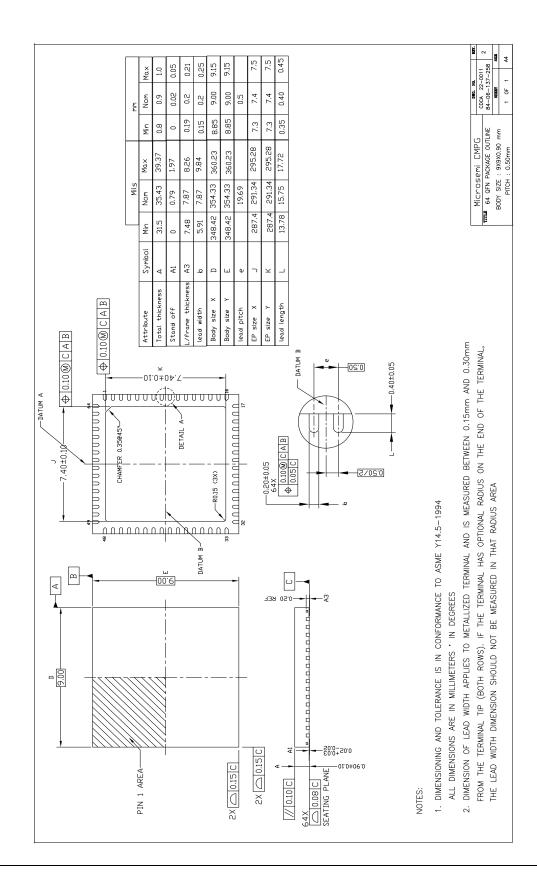

## Package Outline (64-Pin QFN)

## Device Pinout (56-Ball WLCSP) - Top View

| INO<br>(A1 | ·         |               |           | 9/SM_CS S | M_CLK       | SM_MISO      | SM_MOSI       |

|------------|-----------|---------------|-----------|-----------|-------------|--------------|---------------|

| INO<br>B1) | UART_RX   | DVDD33        | VSS<br>B4 | DVDD12    | VSS<br>B6   | DVD<br>(B    | $\overline{}$ |

| (C.        |           | $\overline{}$ |           | NO<br>C4  | INO<br>C5   | NC<br>(C6)   | DAC1_P        |

| DVDD12     | VSS<br>D2 | GPIO_8        | VSS D4    | INO D5    | RESE D6     | T DAC        | <u></u>       |

| PCLK/I2S   | $\bar{}$  | $\bar{}$      |           | IO_1 (6   | GPIO_6      | VSS<br>E6    | AVDD33        |

| FS/I2S_WS  | GPIO_3    | GPIO_2        | GPIO_0    | XO<br>F5  | GPIO_<br>F6 | _            | PAC           |

| DR/I2S     | $\bar{}$  | $\sim$        |           | NC [      | OVDD12      | DVDD12<br>G6 | CREF<br>G7    |

| DX/I2S_SDO | DMIC_IN2  | DMIC_IN1      | NC H4     | NC (H5)   | DMIC_C      |              | KI<br>17)     |

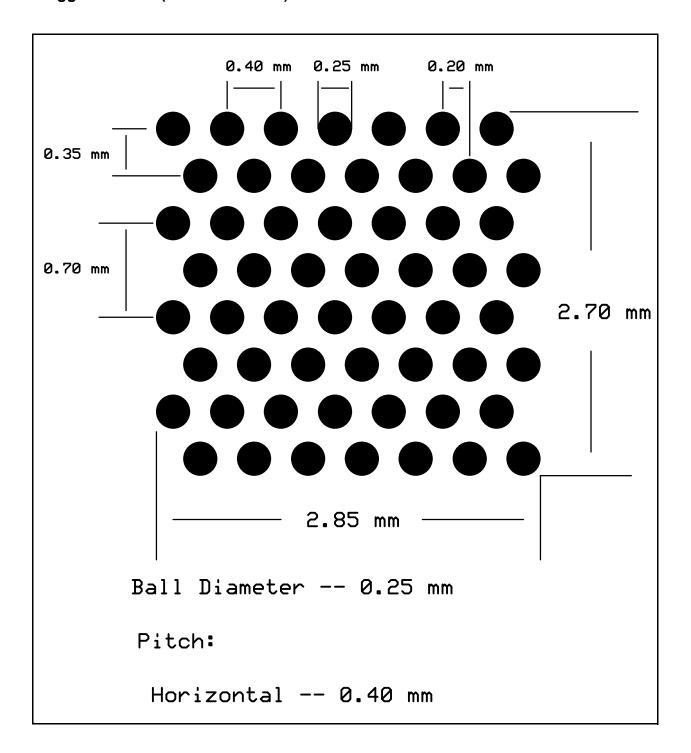

## Staggered Balls (56-Ball WLCSP) - Bottom View

## Package Outline (56-Ball WLCSP)

## **Device Pinout**

| QFN<br>Pin # | WLCSP<br>Ball | Name  | Type  | Description                                                                                                                                                                                                                                                                         |

|--------------|---------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15           | D6            | RESET | Input | <b>Reset.</b> When low the device is in its reset state and all tristate outputs will be in a high impedance state. This input must be high for normal device operation. A 10 $K\Omega$ pull-up resistor is required on this node to DVDD33 if this pin is not continuously driven. |

Table 1 - Reset Pin Description

| QFN<br>Pin # | WLCSP<br>Ball | Name   | Туре   | Description                                                                                                                                    |

|--------------|---------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 6            | -             | DAC1_M | Output | <b>DAC 1 Minus Output.</b> This is the negative output signal of the differential amplifier of the DAC 1.  Not available on the WLCSP package. |

| 7            | C7            | DAC1_P |        | <b>DAC 1 Plus Output.</b> This is the positive output signal of the differential amplifier of the DAC 1.                                       |

| 9            | -             | DAC2_M |        | DAC 2 Minus Output. This is the negative output signal of the differential amplifier of the DAC 2.  Not available on the WLCSP package.        |

| 8            | D7            | DAC2_P |        | DAC 2 Plus Output. This is the positive output signal of the differential amplifier of the DAC 2.                                              |

| 12           | F7            | CDAC   |        | DAC Reference. This node requires capacitive decoupling.                                                                                       |

| 13           | G7            | CREF   |        | Common Mode Reference. This node requires capacitive decoupling.                                                                               |

**Table 2 - DAC Pin Descriptions**

| QFN<br>Pin # | WLCSP<br>Ball | Name     | Туре   | Description                                                                                                                         |

|--------------|---------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 18           | H6            | DMIC_CLK | Output | <b>Digital Microphone Clock Output.</b> Clock output for digital microphones and digital electret microphone pre-amplifier devices. |

| 19           | НЗ            | DMIC_IN1 | Input  | Digital Microphone Input 1. Stereo or mono digital microphone input.  Tie to VSS if unused.                                         |

| 20           | H2            | DMIC_IN2 | Input  | Digital Microphone Input 2. Stereo or mono digital microphone input.  Tie to VSS if unused.                                         |

Table 3 - Microphone Pin Descriptions

| QFN<br>Pin # | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|---------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29           | E1            | PCLK/<br>I2S_SCK | Input/<br>Output | PCM Clock (Input/Tristate Output). PCLK is equal to the bit rate of signals DR/DX. In TDM master mode this clock is an output and in TDM slave mode this clock is an input.  I <sup>2</sup> S Serial Clock (Input/Tristate Output). This is the I <sup>2</sup> S bit clock. In                                                                                                             |

|              |               |                  |                  | I s serial clock (input instate output). This is the 1's bit clock. In I <sup>2</sup> S master mode this clock is an output and drives the bit clock input of the external slave device's peripheral converters. In I <sup>2</sup> S slave mode this clock is an input and is driven from a converter operating in master mode.                                                            |

|              |               |                  |                  | After power-up, this signal defaults to be an input in I <sup>2</sup> S slave mode.                                                                                                                                                                                                                                                                                                        |

|              |               |                  |                  | A 100 KΩ pull-down resistor is required on this pin to VSS. If this pin is unused, tie the pin to VSS.  When driving PCLK/I2S_SCK from a host, one of the following conditions must be satisfied:  1. Host drives PCLK low during reset, or                                                                                                                                                |

|              |               |                  |                  | 2. Host tri-states PCLK during reset (the 100 K $\Omega$ resistor will keep PCLK low), or                                                                                                                                                                                                                                                                                                  |

|              |               |                  |                  | 3. Host drives PCLK at its normal frequency                                                                                                                                                                                                                                                                                                                                                |

| 30           | F1            | FS/<br>I2S_WS    | Input/<br>Output | PCM Frame Pulse (Input/Tristate Output). This is the TDM frame alignment reference. This signal is an input for applications where the PCM bus is frame aligned to an external frame signal (slave mode). In master mode this signal is a frame pulse output.                                                                                                                              |

|              |               |                  |                  | I <sup>2</sup> S Word Select (Left/Right) (Input/Tristate Output). This is the I <sup>2</sup> S left or right word select. In I <sup>2</sup> S master mode word select is an output which drives the left/right input of the external slave device's peripheral converters. In I <sup>2</sup> S slave mode this pin is an input which is driven from a converter operating in master mode. |

|              |               |                  |                  | After power-up, this signal defaults to be an input in I <sup>2</sup> S slave mode. <i>Tie this pin to VSS if unused.</i>                                                                                                                                                                                                                                                                  |

| 31           | G1            | DR/<br>I2S_SDI   | Input            | PCM Serial Data Stream Input. This serial data stream operates at PCLK data rates.                                                                                                                                                                                                                                                                                                         |

|              |               |                  |                  | I <sup>2</sup> S Serial Data Input. This is the I <sup>2</sup> S port serial data input.                                                                                                                                                                                                                                                                                                   |

|              |               |                  |                  | Tie this pin to VSS if unused.                                                                                                                                                                                                                                                                                                                                                             |

| 32           | H1            | DX/<br>I2S_SDO   | Output           | PCM Serial Data Stream Output. This serial data stream operates at PCLK data rates.                                                                                                                                                                                                                                                                                                        |

|              |               |                  |                  | I <sup>2</sup> S Serial Data Output. This is the I <sup>2</sup> S port serial data output.                                                                                                                                                                                                                                                                                                 |

Table 4 - TDM and I2S Pin Description

| QFN<br>Pin # | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                                            |

|--------------|---------------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1            | A5            | SM_CLK           | Output           | Master SPI Port Clock (Tristate Output). Clock output for the Master SPI port. Maximum frequency = 8 MHz.                              |

| 2            | A6            | SM_MISO          | Input            | Master SPI Port Data Input. Data input signal for the Master SPI port.                                                                 |

| 3            | A7            | SM_MOSI          | Output           | Master SPI Port Data Output (Tristate Output). Data output signal for the Master SPI port.                                             |

| 64           | A4            | GPIO_9/<br>SM_CS | Input/<br>Output | Master SPI Port Chip Select (Input Internal Pull-Up/Tristate Output). Chip select output for the Master SPI port.  Shared with GPIO 9. |

**Table 5 - Master SPI Port Pin Descriptions**

| QFN<br>Pin # | WLCSP<br>Ball | Name    | Туре   | Description                                                                                                                                                                                               |

|--------------|---------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50           | B2            | UART_RX | Input  | <b>UART (Input).</b> Receive serial data in. This port functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device.             |

| 49           | C2            | UART_TX | Output | <b>UART (Tristate Output).</b> Transmit serial data out. This port functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device. |

**Table 6 - UART Pin Description**

| QFN<br>Pin #  | WLCSP<br>Ball | Name             | Туре             | Description                                                                                                                                                                                                     |

|---------------|---------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33, 34,<br>36 | F4, E4,<br>F3 | GPIO_[0:2]       | Input/<br>Output | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signalling.                                               |

| 37, 38,<br>39 | F2, -,<br>F6  | GPIO_[3:5]       |                  | General Purpose I/O (Input Internal Pull-Down/Tristate Output). These pins can be configured as an input or output and are intended for low-frequency signaling.  GPIO_4 is not available on the WLCSP package. |

| 64            | A4            | GPIO_9/<br>SM_CS |                  | General Purpose I/O (Input Internal Pull-Down/Tristate Output). This pin can be configured as an input or output and is intended for low-frequency signalling. Alternate functionality with SM_CS.              |

**Table 7 - GPIO Pin Descriptions**

| QFN<br>Pin# | WLCSP<br>Ball | Name    | Туре             | Description                                                                                                                                                |

|-------------|---------------|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41          | E2            | GPIO_7  | Input/<br>Output | <b>Hook Switch/Volume Down.</b> Fixed function used to control the hook state and volume down with GPIO[10:13].                                            |

| 43          | D3            | GPIO_8  |                  | Microphone/Volume Up. Fixed function used to control the hook state and volume down with GPIO[10:13].                                                      |

| 44          | E3            | GPIO_10 |                  | <b>Volume Control/Call State.</b> Fixed function used to control the volume and indicate the call state with GPIO[7:8].                                    |

| 45          | C3            | GPIO_11 |                  | Call Control/Volume State 1. Fixed function used to control the hook switch (on/off) and control multicolor LEDs for volume indication with GPIO[7:8].     |

| 47          | -             | GPIO_12 |                  | <b>Volume State 2.</b> Fixed function used to control multicolor LEDs for volume indication with GPIO[7:8]. GPIO_12 is not available on the WLCSP package. |

| 48          | -             | GPIO_13 |                  | Volume State 3. Fixed function used to control multicolor LEDs for volume indication with GPIO[7:8].  GPIO_13 is not available on the WLCSP package.       |

Table 8 - Headset Control/Indicator

| QFN<br>Pin # | WLCSP<br>Ball | Name | Туре   | Description                |

|--------------|---------------|------|--------|----------------------------|

| 22           | H7            | ΧI   | Input  | Crystal Oscillator Input.  |

| 23           | F5            | XO   | Output | Crystal Oscillator Output. |

**Table 9 - Oscillator Pin Description**

| QFN<br>Pin # | WLCSP<br>Ball | Name      | Type   | Description                                                                                                                                                                                                |

|--------------|---------------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25           | H5            | USB_DM    | Input/ | USB Data D- Signal. Carries USB data to/from USB 2.0.                                                                                                                                                      |

| 26           | G4            | USB_RTUNE | Output | Tx Resistor Tune. Connect to external 43.2 $\Omega$ resistor to VSS.                                                                                                                                       |

| 27           | H4            | USB_DP    |        | USB Data D+ Signal. Carries USB data to/from USB 2.0.                                                                                                                                                      |

| 40           | E5            | GPIO_6    |        | <b>USB Resume.</b> This pin is used to sense activity on USB Data D+ to resume from sleep or perform a USB reset. It can be configured as an input or output and are intended for low-frequency signaling. |

Table 10 - USB Pin Description

| QFN<br>Pin #                | WLCSP<br>Ball                | Name                  | Туре   | Description                                                                                                                                                                                                                                                                                                         |

|-----------------------------|------------------------------|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                          | _                            | EXT_SEL               | Input  | VDD +1.2 V Select. Select external +1.2 V supply. Tie to DVDD33 if the +1.2 V supply is to be provided externally. Tie to VSS (0 V) if the +1.2 V supply is to be generated internally. Not available on the WLCSP package.                                                                                         |

| 16                          | -                            | VDD12_CTRL            | Output | VDD +1.2 V Control. Analog control line for the voltage regulator external FET when EXT_SEL is tied to VSS. When EXT_SEL is tied to DVDD33, the VDD12_CTRL pin becomes a CMOS output which can drive the shutdown input of an external LDO. Not available on the WLCSP package.                                     |

| 4, 14,<br>24, 42,<br>58     | B5, D1,<br>G5, G6            | DVDD12                | Power  | Core Supply. Connect to a +1.2 V ±5% supply.  Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                                                                  |

| 5, 21,<br>35, 46,<br>51, 59 | B3, B7,<br>G3                | DVDD33                | Power  | <b>Digital Supply.</b> Connect to a +3.3 V ±5% supply.<br>Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                                                      |

| 28                          | -                            | DVDD33_<br>XTAL       | Power  | Crystal Digital Supply. For designs using a crystal or external oscillator, this pin must be connected to a +3.3 V supply source capable of delivering 10 mA. For designs that do not use a crystal or external oscillator this pin can be tied to VSS in order to save power.  Not available on the WLCSP package. |

| 10, 11                      | E7                           | AVDD33                | Power  | <b>Analog Supply.</b> Connect to a +3.3 V ±5% supply. Place a 100 nF, 20%, 10 V, ceramic capacitor on each pin decoupled to the VSS plane.                                                                                                                                                                          |

| 54                          | B4, B6,<br>D2, D4,<br>E6, G2 | VSS                   | Ground | Ground. Connect to digital ground plane.                                                                                                                                                                                                                                                                            |

|                             | _                            | Exposed<br>Ground Pad | Ground | <b>Exposed Pad Substrate Connection.</b> Connect to VSS. This pad is at ground potential and must be soldered to the printed circuit board and connected via multiple vias to a heatsink area on the bottom of the board and to the internal ground plane.  Not available on the WLCSP package.                     |

**Table 11 - Supply and Ground Pin Descriptions**

| QF<br>Pir |          | WLCSP<br>Ball | Name | Type | Description                                                                             |

|-----------|----------|---------------|------|------|-----------------------------------------------------------------------------------------|

| 56,<br>6  | 57,<br>3 | A3, C1,<br>C6 | NC   |      | <b>No Connection.</b> These pins are to be left unconnected, do not use as a tie point. |

**Table 12 - No Connect Pin Descriptions**

| QFN<br>Pin #                 | WLCSP<br>Ball | Name | Type  | Description                    |

|------------------------------|---------------|------|-------|--------------------------------|

| 52, 53,<br>55, 60,<br>61, 62 |               | IN0  | Input | IN0. Tie these pins to Ground. |

Table 13 - INO Pin Descriptions

Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively "Microsemi") is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.

This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi's conditions of sale which are available on request.

For more information about all Microsemi products visit our website at www.microsemi.com

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include mixed-signal ICs, SoCs, and ASICs; programmable logic solutions; power management products; timing and voice processing devices; RF solutions; discrete components; and systems. Microsemi is headquartered in Aliso Vieio, Calif. Learn more at www.microsemi.com.

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.