# IGLOO2 FPGA Low Standby Power - Libero SoC v11.5

DG0564 Demo Guide

February 2015

IGLOO2 FPGA Low Standby Power - Libero SoC v11.5

# **Revision History**

| Date             | Revision | Change         |

|------------------|----------|----------------|

| February 6, 2015 | 3        | Third release  |

| August 22, 2014  | 2        | Second release |

| October, 2013    | 1        | First release  |

# **Confidentiality Status**

This document is a non-confidential.

# **Table of Contents**

| Pr | eface                                            | 4   |

|----|--------------------------------------------------|-----|

|    | About this document                              | 4   |

|    | Intended Audience                                | 4   |

|    | References                                       | 4   |

|    | Microsemi Publications                           | 4   |

| 10 | LOO2 FPGA Low Standby Power - Libero SoC v11.5   | ,   |

| IG |                                                  |     |

|    | Introduction                                     |     |

|    | Design Requirements                              |     |

|    | Demo Design                                      |     |

|    | Introduction                                     |     |

|    | Extracting the Source Files                      |     |

|    | Creating the Design                              |     |

|    | Connecting Components in the Canvas              |     |

|    | Importing Physical Constraint files              |     |

|    | Synthesis and Layout                             |     |

|    | Programming                                      |     |

|    | Running the Demo Design                          |     |

|    | Power Measurement (Normal Operation and Standby) |     |

|    | Precise Standby Power Measurement                | 30  |

|    | Total Power (Dynamic and Static)                 |     |

|    | Standby Power                                    | 30  |

| Δr | ppendix A - Power Estimator                      | 3.  |

|    |                                                  |     |

| Δ  | List of Changes                                  | -34 |

|    |                                                  |     |

| В  | Product Support                                  | 35  |

|    | Customer Service                                 |     |

|    | Customer Technical Support Center                |     |

|    | Technical Support                                |     |

|    | Website                                          |     |

|    |                                                  |     |

|    | Contacting the Customer Technical Support Center |     |

|    | My Cases                                         |     |

|    | Outside the U.S.                                 |     |

|    | ITAR Technical Support                           | 36  |

# **Preface**

### **About this document**

This demo is for IGLOO<sup>®</sup>2 field programmable gate array (FPGA) devices. It provides instructions on how to use the corresponding reference design.

# **Intended Audience**

The following designers using the IGLOO2 devices:

- FPGA designers

- · System-level designers

#### References

#### **Microsemi Publications**

- IGLOO2 Power Calculator User Guide

- IGLOO2 FPGA Low Power Design User Guide

- IGLOO2 FPGA Fabric User Guide

# IGLOO2 FPGA Low Standby Power - Libero SoC v11.5

### Introduction

Microsemi<sup>®</sup> IGLOO2 FPGAs are designed to meet the demand of low power FPGAs. The IGLOO2 devices exhibit lower power consumption in static and dynamic modes. This demo guide describes how to implement standby power mode on the IGLOO2 devices using SmartDesign, and measure the standby power. The design drives the LEDs on the IGLOO2 Evaluation Kit with a pattern based on the state of the switches SW1 and SW3, as shown in Table 1.

Table 1 • LEDs Pattern

| LED E1, F4, F3, G7 Behavior | Standby Entry (SW1)    | Standby Exit (SW3) |

|-----------------------------|------------------------|--------------------|

| LEDs toggle                 | Released               | Released           |

| LEDs on                     | Depressed and Released | Released           |

| LEDs toggle                 | Depressed and Released | Depressed          |

This demo guide describes the following:

- Creating a Libero<sup>®</sup> System-on-Chip (SoC) project.

- Implementing standby power mode on IGLOO2 devices using SmartDesign.

- Importing a PDC file, running layout and programming the IGLOO2 silicon.

- Measuring standby power using a standard Digital Voltmeter (DVM)/Multimeter.

# **Design Requirements**

Table 2 shows the design requirements.

Table 2 • Design Requirements

| Design Requirements           | Description                     |

|-------------------------------|---------------------------------|

| Hardware Requirements         |                                 |

| IGLOO2 Evaluation Kit:        | Rev C or later                  |

| 12 V adapter                  |                                 |

| FlashPro4 programmer          |                                 |

| Desktop or Laptop             | Windows 64-bit Operating System |

| Software Requirements         |                                 |

| Libero SoC                    | 11.5                            |

| FlashPro Programming Software | 11.5                            |

## **Demo Design**

#### Introduction

The demo design files are available for download from the following path in the Microsemi website: http://soc.microsemi.com/download/rsc/?f=m2gl\_dg0564\_liberov11p5\_df

The demo design files include:

- Libero SoC project

- Constraint file

- · Programming file

- · Source files

- · Readme file

Refer to the Readme.txt file provided in the design files for the complete directory structure.

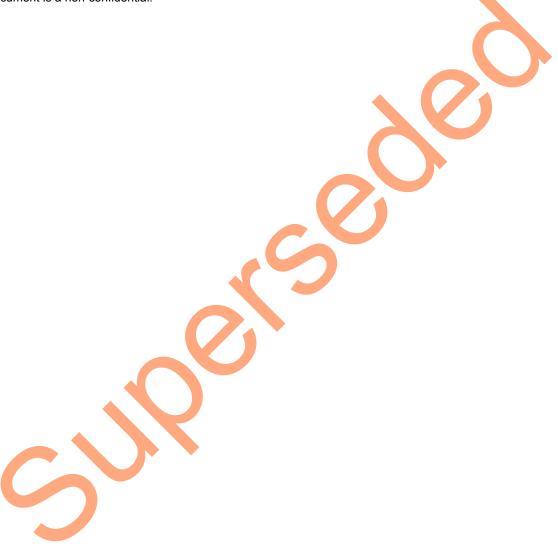

The design consists of a 32 kHz External Main Crystal Oscillator, Fabric CCC (FCCC), Standby power control logic and Fabric logic block. Figure 1 shows the block diagram of the design.

The FCCC is configured to provide 100 MHz clock to the Fabric logic. It is also configured with PLL power-down enabled. The 32 kHz External Main Crystal Oscillator is the reference clock source for the FCCC. The Lock signal is used as a reset signal to the Fabric logic. The standby power control logic consists of a clocked S-R latch which powers down the PLL of FCCC. The Fabric logic consists of 421 stages 18-bit loadable up-counters, 604 stages of shift registers, and 11 stages LSRAM and Math blocks. It also consists of a LED Driver block which is connected to a set of light-emitting diodes (LEDs) to monitor the state of the fabric while entering and exiting standby power mode.

Figure 1 • Design Block Diagram

#### **Extracting the Source Files**

Extract m2gl\_dg0564\_liberov11p5\_df.zip to extract the required lab files to the <C:\ or D:\>Microsemi\_prj folder on the HDD of the PC. Confirm that a folder named IGL2\_Standby\_tutorial containing sub-folders named Source\_files and Constraints are extracted.

## **Creating the Design**

This section describes how to create the standby power mode enabled design using SmartDesign. Some source files are provided in the *Source\_files* folder.

#### Launching Libero SoC

The following steps describe how to launch Libero SoC:

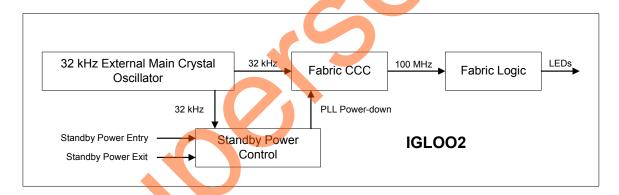

Click Start > Programs > Microsemi Libero SoC v11.5 > Libero SoC v11.5, or click on the shortcut icon on the PC. This opens Libero SoC Project Manager window as shown in Figure 2.

Figure 2 • Libero SoC Project Manager

- 2. Create a new project using one of the following options:

- Select New on the Start Page tab as shown in Figure 2.

- Click Project > New Project from the Libero SoC menu.

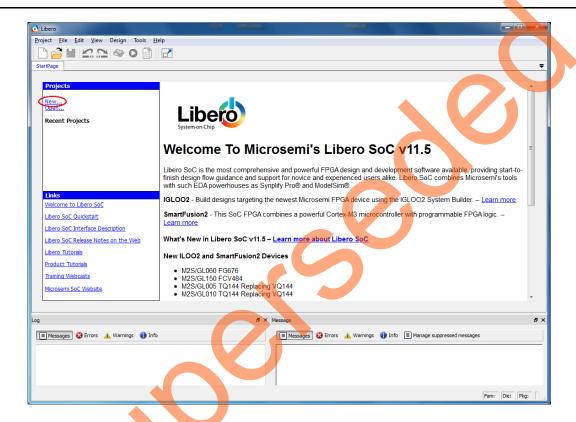

This opens **New Project** window as shown in Figure 3.

- 3. Enter the following information in the New Project Project Details page as shown in Figure 3:

- Project Name: IGL2 Standby

- Project Location: <C:\ or D:\>Microsemi\_prj\IGL2\_Standby\_tutorial

- Preferred HDL type: VHDL

- Enable Block Creation: Un-checked

Figure 3 • New Project - Project Details Page

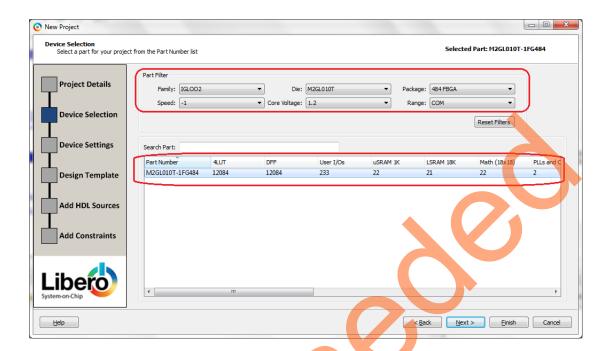

- 4. Click **Next**. This opens **New Project Device Selection** page as shown in Figure 4.

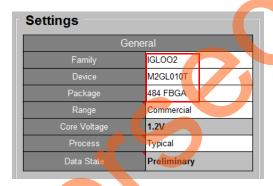

- 5. Select the following values from the drop-down list (highlighted in Figure 4):

- Family: IGLOO2

- **Die**: M2GL010T

- Package: 484 FBGA

- Speed: -1

- Core Voltage: 1.2

- Range: COM

6. Select the filtered device (M2GL010T-1FG484) as shown in Figure 4.

Figure 4 • New Project - Device Selection Page

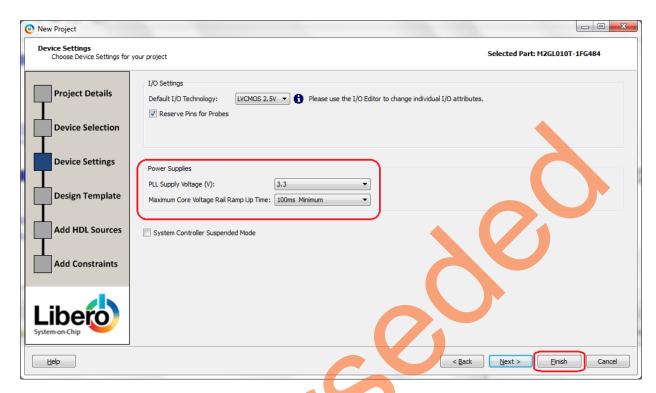

- 7. Click **Next**. This opens **New Project Device Settings** page as shown in Figure 5.

- 8. Select the following values in the Power Supplies section from the drop-down list (highlighted in Figure 5):

- PLL Supply Voltage (V): 3.3

- Maximum Core Voltage Rail Ramp Up Time: 100ms Minimum

The PLL Analog Supply voltage can be either 2.5 V or 3.3 V. The voltage setting in the **New Project - Device Settings** page must match with the PLL Analog supply voltage on the board to ensure that the PLL works properly. The PLL Analog Supply voltage is connected to 3.3 V on the IGLOO2 Evaluation Kit. Therefore, the setting must be changed.

9. Do not change the default selections. Click Finish.

Figure 5 • New Project - Device Settings Page

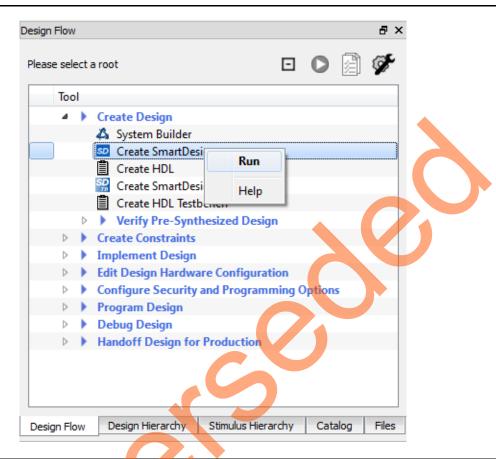

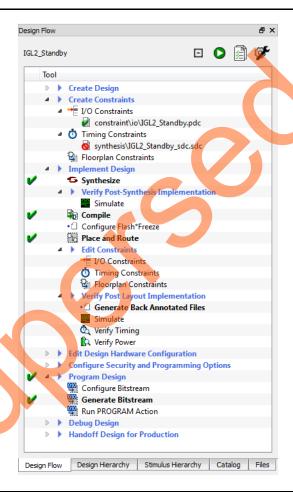

10. Expand **Create Design** in the **Design Flow** tab as shown in Figure 6. Right-click **Create SmartDesign** and select **Run**.

Figure 6 • Creating SmartDesign

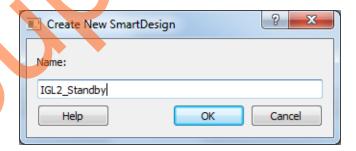

11. Enter IGL2\_Standby in the **Create New SmartDesign** dialog box and click **OK**. New SmartDesign canvas opens.

Figure 7 • Entering SmartDesign Name

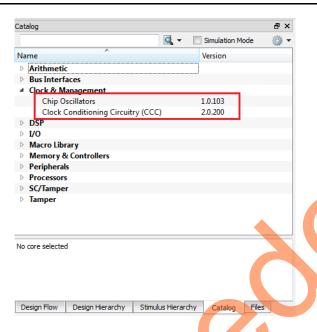

12. This design uses a Fabric CCC to generate 100 MHz internal clock. The CCC reference clock is the 32 kHz external main crystal oscillator. Expand **Clock & Management** in the IP catalog.

Figure 8 • Clock & Management Category of Libero SoC IP Catalog

- 13. Drag an instance of the Clock Conditioning Circuitry (CCC) v2.0.200 component into the SmartDesign canvas.

- 14. Double-click on the FCCC\_0 component in the SmartDesign canvas and open the FAB CCC Configurator window as shown in Figure 9.

- 15. Click **Basic** tab in the **FAB CCC Configurator** window (see Figure 9). Enter the following information:

- Reference Clock Frequency: 0.032 MHz

- Reference Clock: Select Oscillators > Crystal Oscillator from the pull-down menu

- GL0: Checked; Frequency: 100 MHz

- - X FAB CCC Configurator Basic Advanced PLL Options Basic-Options Reference Clock CCC 0.032 MHz Exact Value Frequency Actual ✓ GL0 Crystal Oscillator ▼ 100 GL1 100 GL2 100 GL3 Help ▼ OK Cancel

Figure 9 • Configuring Fabric CCC

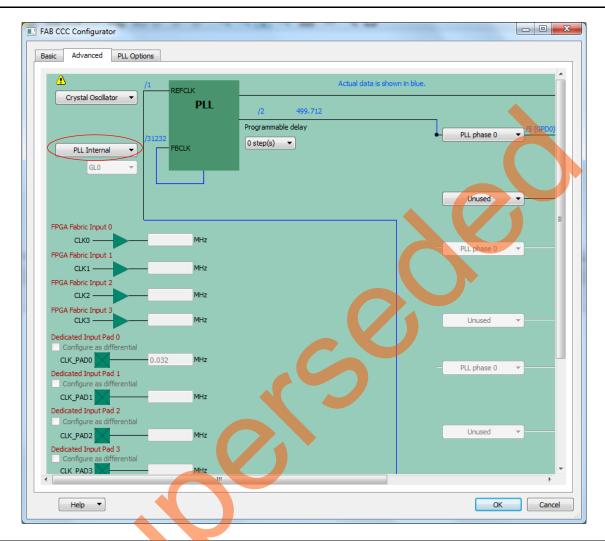

16. Click Advanced tab in the FAB CCC Configurator window and select Internal > PLL Internal from the pull-down menu as PLL feedback source, as shown in Figure 10.

Figure 10 · Configuring PLL Feedback Source

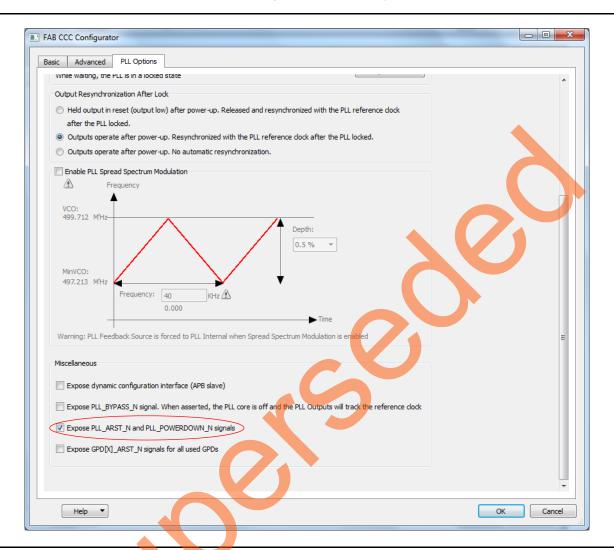

17. Click PLL Options tab in the FAB CCC Configurator window and check Expose PLL\_ARST\_N and PLL\_POWERDOWN\_N signals as shown in Figure 11.

Figure 11 • Configuring PLL Power-down Signal

- 18. Click OK and close the FAB CCC Configurator window.

- 19. Drag an instance of the Chip Oscillators v1.0.103 component from the IP catalog into the SmartDesign canvas.

- 20. Double-click on the OSC\_0 component in the SmartDesign canvas and open the Chip Oscillators Configurator window, as shown in Figure 12.

- 21. Configure the External Main Crystal Oscillator to drive FCCC and fabric logic. Enter the following information (see Figure 12):

- External Main Crystal Oscillator: Checked

- Source: Select Crystal (32 KHz 20 MHz) from the pull-down menu

- Frequency: 0.032 MHz

- Drives Fabric CCC(s): Checked

- Drives Fabric Logic: Checked

L Chip Oscillators Configurator External Main Crystal Oscillator HPMS\_CCC Crystal (32KHz-20MHz) • Source RCOSC\_50MHZ Drives Fabric CCC(s) Drives Fabric Logic 🔻 On-chip 25/50 MHz RC Oscillator Drives Fabric CCC(s) Drives Fabric Logic RCOSC\_1MHZ On-chip 1 MHz RC Oscillator Drives Fabric CCC(s) CCC Drives Fabric Logic CCC XTLOSC User Logic FPGA Fabric Help ▼ OK Cancel

Figure 12 • Configuring Chip Oscillators

22. Click **OK** and close the **Chip Oscillators Configurator** window.

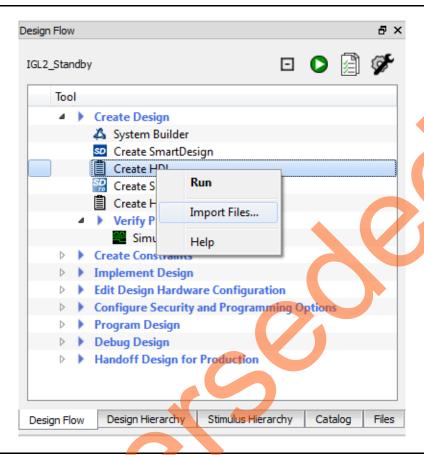

23. Import the VHDL source files into the project by selecting **Create HDL** under **Create Design** in the **Design Flow** tab. Right-click and select **Import Files...** (see Figure 13).

Figure 13 • Importing HDL Source Files

- 24. Enter the following information in Import Files dialog box and click Open:

- Look in: <C:\ or D:\>Microsemi\_prj\\IGL2\_Standby\_tutorial\\Source\_files

- Files of type: HDL Source Files (\*.vhd \*.v \*.h)

- File name: Select all files (click the first item and press Ctrl+A)

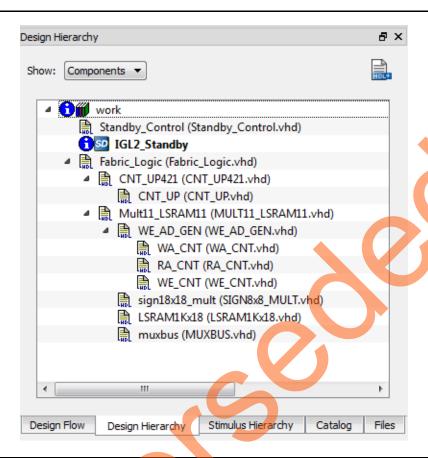

25. The files are visible on **Design Hierarchy** tab.

Figure 14 • Design Hierarchy Tab with Imported Files

- 26. Drag Standby Control and Fabric Logic components into the SmartDesign canvas.

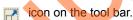

- 27. After adding the components, the SmartDesign resembles Figure 15. Drag the components to improve the appearance of the canvas.

Expand the canvas area by selecting View > Maximize Work Area, or click on

Reports S X StartPage S X STAR

Figure 15 • SmartDesign Canvas after Adding Components

#### **Connecting Components in the Canvas**

SmartDesign in Libero SoC has a connection mode that supports click, drag, and release to connect the components.

Connect the components in the SmartDesign canvas using the following procedure:

- 1. Select SmartDesign > Connection Mode from the Libero SoC menu.

- 2. Connect the XTLOSC\_CCC\_OUT port of OSC\_0 component to the XTLOSC\_CCC\_IN port of the FCCC\_0 component as follows:

- Click on the XTLOSC\_CCC\_OUT port of the OSC\_0 component and hold the left mouse button.

- Hold the left mouse button and drag the XTLOSC\_CCC\_IN port of FCCC\_0 component.

- Release the mouse button to connect.

Note: You can also connect the ports by selecting them using CTRL (Ctrl + click to select a port), rightclicking any of the selected ports, and selecting Connect.

3. Connect the other components in the SmartDesign canvas as per Table 3.

Table 3 • Connections in Canvas

| From                             | То                      |

|----------------------------------|-------------------------|

| OSC_0: XTLOSC_O2F                | Standby_Control_0: CLK  |

| Standby_Control_0: PLL_PowerDown | FCCC_0: PLL_ARST_N      |

|                                  | FCCC_0: PLL_POWERDOWN_N |

Table 3 • Connections in Canvas (continued)

| From         | То                  |

|--------------|---------------------|

| FCCC_0: GL0  | Fabric_Logic_0: CLK |

| FCCC_0: LOCK | Fabric_Logic_0: RST |

- 4. Select **SmartDesign > Connection Mode** from the Libero SoC menu to exit connection mode.

- 5. Promote the following ports to the top level (see Table 4). Click on the port, Right-click and select **Promote to Top Level**.

Table 4 • Promote to Top Level

| Ports                            |  |

|----------------------------------|--|

| Standby_Control_0: Standby_Entry |  |

| Standby_Control_0: Standby_Exit  |  |

| Fabric_Logic_0: LD               |  |

| Fabric_Logic_0: DIN[17:0]        |  |

| Fabric_Logic_0: DOUT[17:0]       |  |

| Fabric_Logic_0: LED_1            |  |

| Fabric_Logic_0: LED_2            |  |

| Fabric_Logic_0: LED_3            |  |

| Fabric_Logic_0: LED_4            |  |

The SmartDesign canvas appears as shown in Figure 16. Drag the components or use the SmartDesign Auto Arrange feature to improve the appearance of the canvas.

Figure 16 • SmartDesign Canvas after Connections

6. Save the design (File > Save IGL2\_Standby).

- 7. Generate the design by selecting **SmartDesign > Generate Component**, or by clicking the **Generate Component** icon on the SmartDesign toolbar (circled in Figure 16).

- 8. Restore the work area (View > Restore Work Area) if you expanded the work area earlier.

- 9. Confirm that the message IGL2\_Standby was generated appears in the Libero Log window.

- 10. Close the design (File > Close IGL2\_Standby).

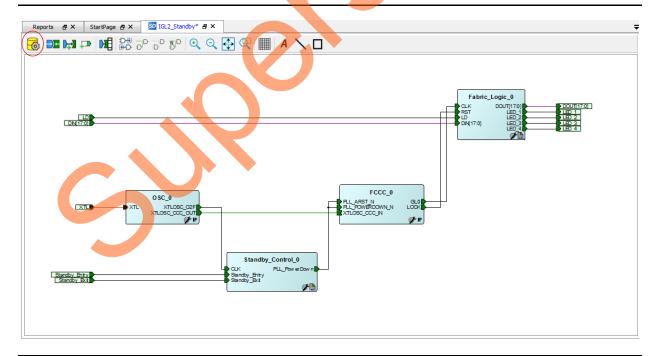

#### **Importing Physical Constraint files**

This section describes how to import a physical design constraint (PDC) file to make I/O attribute and pin assignments for the layout.

There are several ways to make I/O assignments:

Expand Create Constraints in the Design Flow tab. Right-click on I/O Constraints and select Import Files.....

Figure 17 • Importing I/O PDC Constraint File

- 2. Enter the following information in the **Import Files** dialog box and click **Open**:

- Look in: <C:\ or D:\>Microsemi\_prj\IGL2\_Standby\_tutorial\Constraints

- Files of type: I/O Constraint Files (\*.pdc)

- File name: IGL2\_Standby.pdc

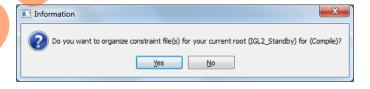

- Click No in the Information dialog box.

Figure 18 • Information Dialog Box after Importing PDC Constraint File

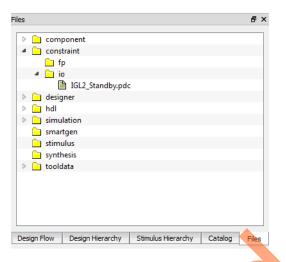

4. The file is visible on the Libero SoC Files tab under constraint > io.

Figure 19 • I/O PDC Constraint File in Libero SoC Project

A description of the Designer PDC constraints is available in the Libero Help (Go to Help > Help Topics > Implement Design > Constrain Place and Route > Assigning Design Constraints > Design Constraints Guide > Reference > Constraints by File Format > PDC Command Reference).

## **Synthesis and Layout**

Use the push-button flow to synthesize the design with Synplify Pro, run layout and generate the programming file as mentioned below:

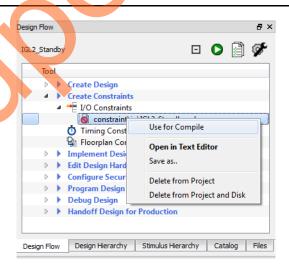

- 1. Expand Create Constraints > I/O Constraints in the Libero SoC Design Flow tab. Right-click IGL2 Standby.pdc under Constraints.

- 2. Right-click and select Use for Compile, as shown in Figure 20. A green check mark appears next to the constraint file indicating that the file will be used.

Figure 20 • Selecting I/O PDC Constraint File in Design Flow Tab

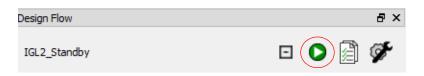

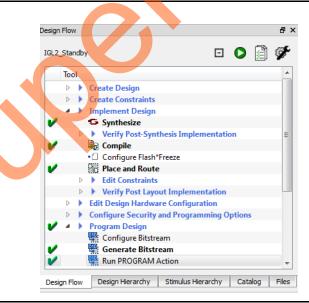

3. Click Generate Programming Data icon in the Design Flow tab (circled in Figure 21), or select Design > Generate Fabric Programming Data to synthesize the design, run layout using the I/O constraints that are created and generate the programming file.

Figure 21 • Generate Programming Data Icon

The design implementation tools run in batch mode. Successful completion of a design step is indicated by a green check mark next to Implement Design in the Design Flow tab (see Figure 22).

Figure 22 • Successful Design Implementation

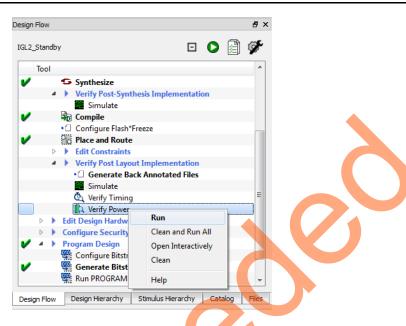

4. Generate a power report by right-clicking **Verify Power** under **Verify Post Layout Implementation** in the **Design Flow** tab and selecting **Run**.

Figure 23 • Generating Post Layout Power Report

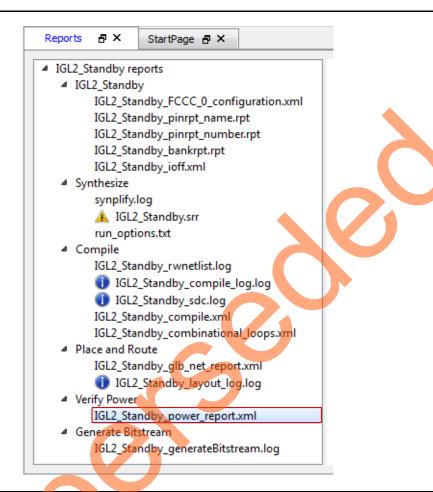

The Reports tab displays reports for the tools used to implement the design. Select IGL2\_Standby\_power\_report.xml under Verify Power in the Reports tab to view the power consumption.

Figure 24 • Reports Tab after Implementing Design

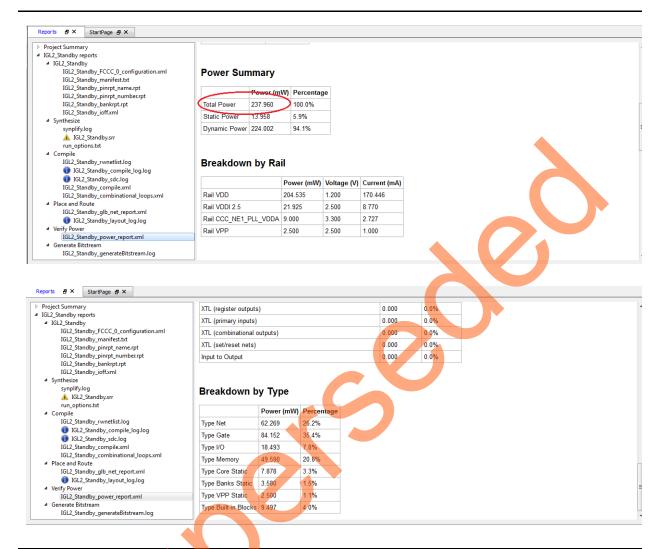

The **Reports** tab displays the power report as shown in Figure 25.

Figure 25 • Power Report

## **Programming**

The following steps describe how to run FlashPro in batch mode and program the IGLOO2 M2GL010T on the IGLOO2 Evaluation Kit board:

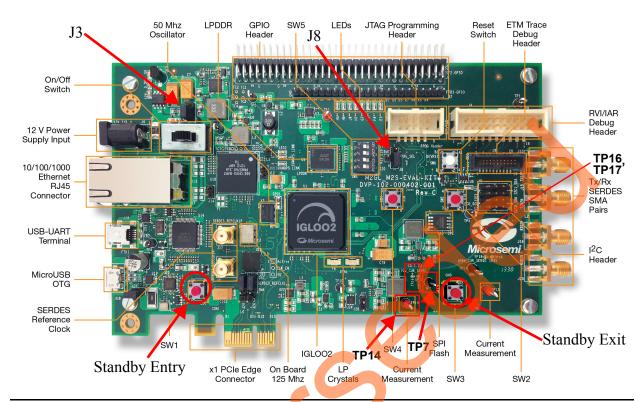

1. Prior to programming (and powering up) the IGLOO2 Evaluation Kit board, ensure that the jumpers are positioned as shown in Table 5.

Table 5 • Jumper Settings

| Jumper | Location                                            | Setting       |  |  |

|--------|-----------------------------------------------------|---------------|--|--|

| J3     | Above the On/Off Switch in Figure 26                | 1-2 installed |  |  |

| J8     | Below the JTAG Programming Header (J5) in Figure 26 | 1-2 installed |  |  |

Figure 26 • IGLOO2 Evaluation Kit

- 2. Plug the FlashPro4 ribbon cable into connector J5 (JTAG Programming Header) on the IGLOO2 Evaluation Kit board.

- 3. Connect the mini USB cable between the FlashPro4 and the USB port of the PC.

- 4. Install the FlashPro4 drivers if prompted. The drivers are located in *FlashPro Installation Directory*\Drivers folder.

- 5. Power on the board by plugging in the power cable and switching on the power switch. Three Green LEDs on top left of the board are powered on.

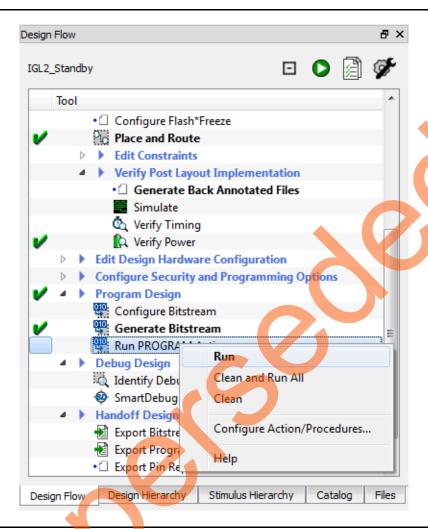

6. Expand **Program Design** in the **Design Flow** tab. Right-click **Run PROGRAM Action** and select **Run** to begin programming.

Figure 27 • Launching Programming Software from Design Flow Tab

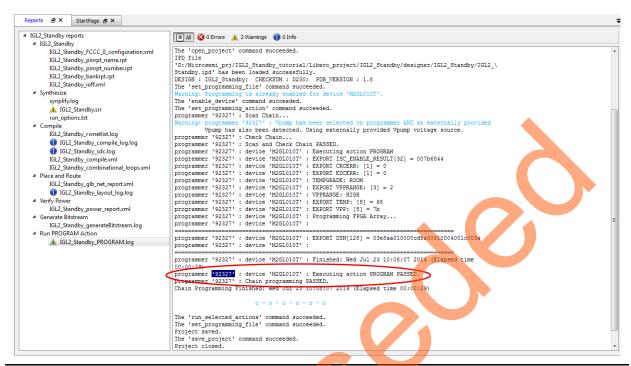

FlashPro runs in batch mode and programs the device. Programming messages are visible in the Libero SoC log window. Programmer number differs.

Note: Do not interrupt the programming sequence. It may damage the device or programmer.

The following message is displayed in the Reports view under Program Device when the device is programmed successfully (see Figure 27). Programmer number differs:

programmer '92327' : device 'M2GL010T' : Executing action PROGRAM PASSED.

Figure 28 • Programming Messages in Libero SoC Log Window

A green check mark appears next to Program Design and Program Device in the Design Flow tab indicating that programming has been completed successfully.

Figure 29 • Design Flow Tab after Programming

8. Close Libero SoC (Project > Exit). Select Yes if prompted about saving changes.

## **Running the Demo Design**

#### Power Measurement (Normal Operation and Standby)

IGLOO2 Evaluation Kit board has a voltage measuring circuit which measures the voltage across the VDD (1.2 V) current sense resistor.

The core power can be calculated using following equations:

- Core Current (mA) = Measured Voltage (mV) ÷ 5 (Scaling Factor)

- Core Power (mW) = 1.2 × Core Current

Connect the positive terminal of a standard digital voltmeter (DVM)/Multimeter to TP14 and negative terminal to TP7.

Note the digital voltmeter/Multimeter reading and calculate the power using above equations.

#### **Precise Standby Power Measurement**

Precise and accurate power measurements can be obtained by measuring voltage across the 1.2 V, 0.05  $\Omega$  sense resistor. Test points TP16 and TP17 can be used to directly measure voltage across the 1.2 V sense resistor. Since the current drawn by the device in standby mode is expected to be around or less than 10 mA, the voltage measured across the 0.05  $\Omega$  sense resistor is expected to be less than 0.5 mV. A precise digital voltmeter such as Fluke-287 that can measure sub-millivolt readings should be used to read voltage measured across the sense resistor.

Convert the voltage measured across sense resistor to power using the following equation:

Power (mW) = (Voltage (mV)/0.05)  $\times$  1.2

#### Total Power (Dynamic and Static)

The following steps describe how to calculate total power:

- 1. Reset the board by pressing and releasing the Reset button (SW6 DEVRST).

- 2. Observe the pattern of the LEDs E1, F4, F3, and G7 after resetting the board.

- 3. Measure the power

Note: If LEDs are not toggling after reset, the device is in Standby mode. Press and release Standby Exit push button (SW3) and observe the LEDs pattern. The LEDs start toggling. Then, Measure the power.

#### Standby Power

The following steps describe how to calculate standby power:

- Press and release Standby Entry push button (SW1) and observe the LEDs pattern. The LEDs stop toggling.

- 2. Measure the power

- 3. Press and release Standby Exit push button (SW3).

- 4. When finished, remove power from the board.

# **Appendix A - Power Estimator**

#### **Power Estimator**

The following steps describe how to use Power Estimator and calculate the total power:

- 1. Download the Power Estimator. SmartFusion2 and IGLOO2 Power Calculator

- 2. Double-click and invoke the power estimator spreadsheet.

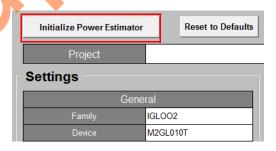

- 3. Click on the Summary worksheet. The Summary worksheet provides the device settings and the power summary.

- 4. Change the device settings. Enter the following information:

- Family: Select IGLOO2 from the pull-down menu

- Device: Select M2GL010T from the pull-down menu

- Package: Select 484 FBGA from the pull-down menu

Figure A-1 • Settings Section in the Device Settings and Summary Worksheet

The Summary worksheet has an integrated initialize power estimator wizard. This wizard provides an option to select design specific information. Upon running the wizard, it populates the power calculator spreadsheet with information about the design and performs power estimation for the design.

5. Click **Initialize Power Estimator** (see Figure A-2) and invoke the Initialize power estimator wizard. **Initialize Power Estimator** dialog box opens (see Figure A-3).

Figure A-2 • Initialize Power Estimator

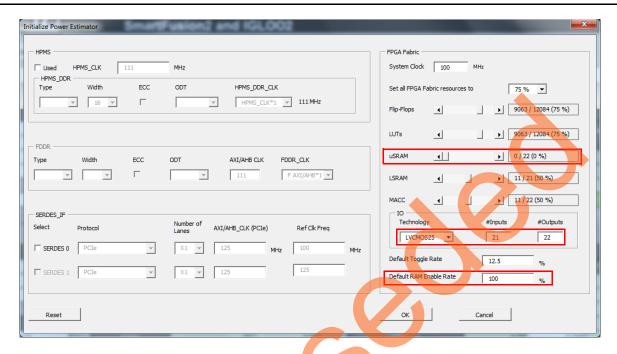

- 6. Enter the following information in the Initialize Power Estimator dialog box:

- uSRAM: Move the slider to zero, 0/22 (0%)

- IO:

- Technology: LVCMOS25

Appendix A - Power Estimator

#Inputs: 21#Outputs: 22

• Default RAM Enable Rate: 100%

Figure A-3 • Initialize Power Estimator Wizard

- 7. Click **OK** and close the **Initialize Power Estimator** dialog box. Click **Yes** in the **Set to Defaults** dialog box.

- 8. Click on the CCC & Oscillator worksheet and scroll down to FAB\_CCC Power section. Enter the following information in the FAB\_CCC Power table:

- Name: FCC\_0

- Reference clock frequency (MHz): 0.032

- PLL output frequency (MHz): 500 MHz

- Output1 frequency (MHz):100 MHz

| FAB_CCC Power |                                          |                                           |                               |                               |                               |                               |                      |                           |

|---------------|------------------------------------------|-------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|----------------------|---------------------------|

| Name          | Reference<br>Clock<br>Frequency<br>(MHz) | PLL Output<br>Clock<br>Frequency<br>(MHz) | Output1<br>Frequency<br>(MHz) | Output2<br>Frequency<br>(MHz) | Output3<br>Frequency<br>(MHz) | Output4<br>Frequency<br>(MHz) | VDD<br>Power<br>(mW) | PLL_VDDA<br>Power<br>(mW) |

| FCCC_0        | 0.032                                    | 500                                       | 100                           |                               |                               |                               | 2.59                 | 5.00                      |

|               |                                          |                                           |                               | _                             |                               |                               | 0.00                 | 0.00                      |

|               |                                          |                                           |                               |                               |                               |                               | 0.00                 | 0.00                      |

|               |                                          |                                           |                               |                               |                               |                               | 0.00                 | 0.00                      |

|               |                                          |                                           |                               |                               |                               |                               | 0.00                 | 0.00                      |

|               |                                          |                                           |                               |                               |                               |                               | 0.00                 | 0.00                      |

|               |                                          |                                           |                               |                               |                               |                               | 0.00                 | 0.00                      |

|               |                                          |                                           |                               |                               |                               |                               | 0.00                 | 0.00                      |

Figure A-4 • FAB\_CCC Section

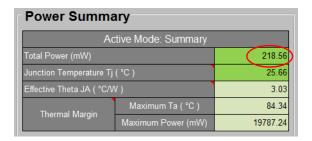

9. Click on the **Summary** worksheet to get the total power. The Power Summary section is populated with the Total Active mode power.

Figure A-5 • Power Summary

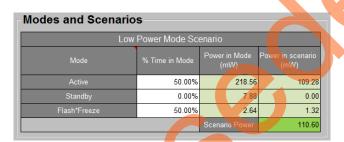

10. The Modes and Scenarios section is populated with the total power in the Active, Standby and Flash\*Freeze modes.

Figure A-6 • Modes and Scenarios

11. Close the Power Estimator.

# A – List of Changes

The following table lists critical changes that were made in each revision of the chapter in the demo guide.

| Date                          | Changes                                               | Page |

|-------------------------------|-------------------------------------------------------|------|

| Revision 3<br>(February 2015) | Updated the document for Libero SoC v11.5 (SAR 64364) | NA   |

| Revision 2<br>(August 2014)   | Updated the document for Libero SoC v11.4             | NA   |

| Revision 1<br>(October 2013)  | Initial release                                       | NA   |

# **B** - Product Support

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

#### **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 408.643.6913

## **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

For Microsemi SoC Products Support, visit

http://www.microsemi.com/products/fpga-soc/designsupport/fpga-soc-support

#### **Website**

You can browse a variety of technical and non-technical information on the SoC home page, at http://www.microsemi.com/soc.

## Contacting the Customer Technical Support Center

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.

#### **My Cases**

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

#### Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (soc\_tech@microsemi.com) or contact a local sales office. Sales office listings can be found at .microsemi.com/soc/company/contact/default.aspx.

# **ITAR Technical Support**

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via soc\_tech\_itar@microsemi.com. Alternatively, within My Cases, select **Yes** in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.