# 3.5A 12V E-Fuse with Hot-Swap and Voltage Surge Protection

#### Description

The LX8204 is a fast acting eFuse switch designed both to protect circuitry connected to its output (VOUT) from transient input voltage surges on its input (VCC), and to protect VCC from overload current events coming from the load on VOUT.

Voltage protection features include under-voltage lockout (UVLO), and over-voltage clamping. This clamp limits VOUT voltage allowing continued circuit operation during an input over-voltage transient condition, while UVLO ensures that VOUT remains off until VCC reaches its minimum operating threshold. On the current side, the LX8204 protects the input from a output short circuit and/or over current condition with a 3.5A current limit circuit. Additionaly, the LX8204 protects the subsequent systems from hot-swap condition.

Another protection feature is latching thermal shutdown of VOUT, with a fault flag output on the combined EN/FAULT pin. Once thermal shutdown threshold is reached and the eFuse switch opens, the tristate EN/FAULT pin will be pulled to about 1.6V signaling to the system and potentially other connected eFuse switches that a fault has occurred.

#### Features

- Protected from Hot-Swap Condition.

- 50mΩ(typ.) Rdson Internal eFuse FET Protected from 24V

- Up to 24V Transient Input Range

- < 15V Output Voltage Clamp including Dynamic Transient

- Continuous Operation During VCC Surge

- 3.5A Current Limit at Overloading

- Over-Temperature Protection

- 13mS and 1.4ms Softstart Rise Time

- Current Limit During Vout Softstart

- UVLO Detection

- 3mm x 3mm DFN Available

#### **Applications**

- Hard-Disk Drive

- Solid-State Drive

- Hot Swap

- PC Cards

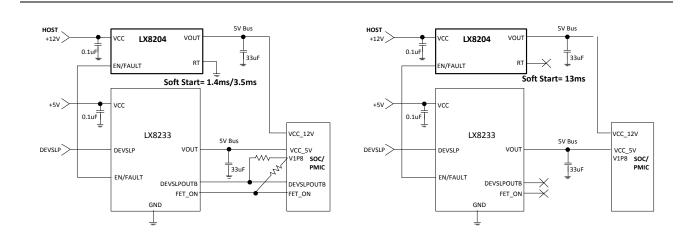

Figure 1 · Typical Application of LX8204

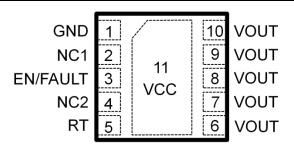

### **Pin Configuration and Pinout**

3mmx3mm WDFN

Figure 2 · Pinout Top View

### **Ordering Information**

| Ambient<br>Temperature | Туре                                   | Package      | Part Number                           | Packaging Type |

|------------------------|----------------------------------------|--------------|---------------------------------------|----------------|

| -40°C to 85°C          | RoHS Compliant,<br>Pb-free WDFN 3X3 10 | W/DEN 3X3 10 | LX8204-135ILD<br>LX8204-xyyILD*       | Bulk / Tube    |

| -40 0 10 00 0          |                                        | WDIN 3X3 TOE | LX8204-135ILD-TR<br>LX8204-xyyILD-TR* | Tape and Reel  |

Consult Factory for other options of "x" and "yy"

"x" is the soft start time with RT = GND (1 = 1.4ms, 3= 3.5ms)

"yy" is the current limit ( 20 is 2Amps, 25 = 2.5Amps, 30 = 3Amps, 35 = 3.5Amps)

## Pin Description

| Pin<br>Number           | Pin Designator | Input/<br>Output |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | De                                                                                                       | scription |             |                                 |  |

|-------------------------|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------|-------------|---------------------------------|--|

| 1                       | GND            | -                | Ground Pin                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                          |           |             |                                 |  |

| 2,4                     | NC1,2          | -                | Do Not (                                                                                                                                                                                                                                                                                                                                                                                                                                                | Do Not Connect.                                                                                          |           |             |                                 |  |

|                         |                |                  | The EN/FAULT pin is a tri-state, bidirectional interface. It can be used to disable the output of the device by pulling it to ground using an open drain or open collector device. If a thermal fault occurs, the voltage on this pin w go to an intermediate state to signal a monitoring circuit that the device is thermal shutdown. It can also be connected to another device in this fami to cause a simultaneous shutdown during thermal events. |                                                                                                          |           |             | drain<br>pin will<br>vice is in |  |

|                         |                |                  | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description                                                                                              | EN/FAULT  | eFuse State | Latching                        |  |

| 3                       | EN/FAULT       | Input/Output     | UVLO                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Under Voltage Lock Out. This<br>UVLO condition must be applied<br>even VCC is under Hi-Z or<br>grounded. | VL        | Off         | No                              |  |

|                         |                |                  | THsd                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Thermal Shutdown                                                                                         | VM        | Off         | Yes                             |  |

|                         |                |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Vcc>UVLO, No Fault                                                                                       | VH        | On          | n/a                             |  |

| 5                       | RT             | Input            | When RT is floating, the VOUT rise time will be 10ms.<br>When RT is grounded, the VOUT rise time will be longer than 1.4ms.<br>or 3.5ms.<br>LX8204-1yy: 1.4ms VOUT rise time.<br>LX8204-3yy: 3.5ms VOUT rise time.                                                                                                                                                                                                                                      |                                                                                                          |           |             |                                 |  |

| 6-10                    | VOUT           | Output           | Output of the device, connect to circuitry to be protected.                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |           |             |                                 |  |

| 11*<br>(exposed<br>pad) | VCC            | Input            | Input of the device. Positive input to the device (Bottom exposed pad)                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                          |           | 1)          |                                 |  |

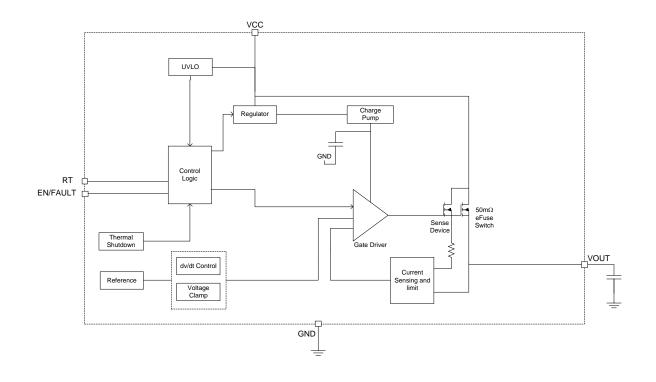

## **Block Diagram**

Figure 3 · Simplified Block Diagram of LX8204

### **Absolute Maximum Ratings**

| Parameter                    | Min                     | Max | Units |

|------------------------------|-------------------------|-----|-------|

| VCC to GND (Steady-State)    | -0.6                    | 18  | V     |

| VCC to GND (Transient 100ms) | -0.6                    | 25  | V     |

| EN/FAULT to GND              | -0.3                    | 6   | V     |

| ESD (Human Body Model)       | 2000 <sup>(Note2)</sup> |     | V     |

| ESD (Charged Device Model)   | 1000                    |     |       |

| Power Dissipation            |                         | 2.5 | W     |

| Storage Temperature          | -65                     | 150 | °C    |

Note: 1. Performance is not necessarily guaranteed over this entire range. These are maximum stress ratings only. Exceeding these ratings, even momentarily, can cause immediate damage, or negatively impact long-term operating reliability

2. All pins meet +2000/-2000V HBM ESD rating, except pin 4 which meets +2000/-1500V.

#### **Operating Ratings**

|                      | Min  | Тур | Max  | Units |

|----------------------|------|-----|------|-------|

| VCC                  | 10.8 | 12  | 13.2 | V     |

| I(VCC)               |      |     | 3.5  | А     |

| Junction Temperature | -40  |     | 125  | °C    |

Note: Performance is generally guaranteed over this range as further detailed below under Electrical Characteristics.

## **Thermal Properties**

| Thermal Resistance | Тур | Units |

|--------------------|-----|-------|

| θ <sub>JA</sub>    | 65  | °C/W  |

Note: The  $\theta_{JA}$  numbers assume no forced airflow. Junction Temperature is calculated using  $T_J = T_A + (PD \times \theta_{JA})$ . In particular,  $\theta_{JA}$  is a function of the PCB construction. The stated number above is for a four-layer board in accordance with JESD-51 (JEDEC).

### **Electrical Characteristics**

Unless otherwise specified, the following specifications apply over the operating ambient temperature of -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C except where otherwise noted with the following test conditions: VIN=12V. Typical parameter refers to T<sub>J</sub>=25°C

| Symbol                | Parameters                                 | Test Conditions/Comme                                                                                                                                                                                   | nts                      | Min  | Тур | Max  | Units |

|-----------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----|------|-------|

| eFuse FE              | т                                          |                                                                                                                                                                                                         |                          |      |     |      |       |

| TONDLY                | Turn-on Delay Time                         | Enable by EN/FAULT with 100mA and 50pF load                                                                                                                                                             | load current             |      | 100 |      | μs    |

| D                     | On Registeres                              | T <sub>A</sub> = 25°C, (Note 2)                                                                                                                                                                         |                          | 51   | 59  | 68   | mΩ    |

| R <sub>DSON</sub>     | On Resistance                              | T <sub>J</sub> = 80°C, (Note 1)                                                                                                                                                                         |                          |      | 75  | 90   | mΩ    |

| I <sub>OFF</sub>      | Off State Output<br>Leakage Current        | C = 12V <sub>DC</sub> , EN/FAULT = GND, VOUT = GND<br>Measure I(VOUT)                                                                                                                                   |                          |      |     | 1    | μA    |

| I <sub>DC</sub>       | Continuous Current                         | T <sub>A</sub> = 25°C                                                                                                                                                                                   | $\Gamma_A = 25^{\circ}C$ |      | 2   |      | Α     |

|                       |                                            | RT = Float                                                                                                                                                                                              |                          | 8    | 11  | 12   | ms    |

| T <sub>RISE</sub>     | VOUT Rise Time                             | RT = GND (LX8204-1yy)                                                                                                                                                                                   |                          |      | 1.4 | 2    | ms    |

|                       |                                            | RT = GND (LX8204-3yy)                                                                                                                                                                                   | RT = GND (LX8204-3yy)    |      | 3.5 |      | ms    |

| Thermal               | Shutdown                                   |                                                                                                                                                                                                         |                          |      |     |      |       |

| T <sub>SD</sub>       | Shutdown<br>Temperature                    | <ul> <li>VOUT is latched off once thermal shutdown is triggered. It can be reset two ways.</li> <li>1) EN/FAULT is pulled low then let float.</li> <li>2) VCC is recycled.</li> <li>(Note 1)</li> </ul> |                          | 140  | 150 | 160  | °C    |

| Under/Ov              | er Voltage Protection                      |                                                                                                                                                                                                         |                          |      |     |      |       |

| V <sub>CLAMP</sub>    | Output Clamping<br>Voltage                 | VCC = 18V                                                                                                                                                                                               |                          | 13.2 |     | 14.2 | V     |

|                       | Maximum<br>Overshoot During<br>Transient   | VCC transient from 12V to<br>24V at 40V/µs with I <sub>VOUT</sub> =                                                                                                                                     |                          |      |     | 15.7 | V     |

|                       | Minimum<br>Undershoot During<br>Transident | VCC transient from 12V to<br>24V at 40V/µs with I(VOU                                                                                                                                                   |                          | 7.35 |     |      | V     |

| V <sub>UVLO_TH</sub>  | Under-Voltage Lock-<br>Out Threshold       | Turn-on and voltage increases                                                                                                                                                                           |                          | 7.5  |     | 9.5  | V     |

| V <sub>UVLO_HYS</sub> | Under-Voltage Lock-<br>Out Hysteresis      |                                                                                                                                                                                                         |                          |      | 1.5 |      | V     |

| Current F             | rotection                                  |                                                                                                                                                                                                         |                          |      |     | •    | -     |

| I <sub>SC_LIM</sub>   | Short Circuit Current<br>Limit             | VOUT is <1V from GND.                                                                                                                                                                                   |                          |      | 1.6 |      | A     |

|                       |                                            |                                                                                                                                                                                                         | yy = 20                  |      | 24  |      | -     |

|                       | Overloading Current                        | VOUT is 0.5V lower than                                                                                                                                                                                 | yy = 25                  |      | 2.5 |      | 1     |

| AVG_LIM               | Limit                                      | the nominal VOUT.                                                                                                                                                                                       | yy = 30                  |      | 3   |      | 1     |

|                       |                                            |                                                                                                                                                                                                         | yy = 35                  | 3    | 3.5 |      | 1     |

| EN/FAUL               | T                                          |                                                                                                                                                                                                         |                          |      | •   |      |       |

| VENDISIL              | Disable Logic Input<br>Level Low           | Output disabled                                                                                                                                                                                         |                          |      |     | 0.4  | V     |

| VEN <sub>MIDIL</sub>  | Thermal Fault Input                        | EN/FAULT pin is driven by                                                                                                                                                                               | the other                |      | 1   | 1.0  | V     |

| Symbol                  | Parameters                                 | Test Conditions/Comments                                                   | Min | Тур  | Max | Units |

|-------------------------|--------------------------------------------|----------------------------------------------------------------------------|-----|------|-----|-------|

|                         | Logic Level Low                            | eFuse. Thermal Fault, Output Disabled.                                     |     |      |     |       |

| VEN <sub>MIDIH</sub>    | Thermal Fault Input<br>Logic Level Low     | EN/FAULT pin is driven by the other eFuse. Thermal Fault, Output Disabled. | 2.1 |      |     | V     |

| VEN <sub>ENIH</sub>     | Enable Logic Input<br>Level High           | Output Enabled                                                             | 3.3 |      |     | V     |

|                         | High State Max<br>Voltage                  | (Note 1)                                                                   |     |      | 5.4 | V     |

| VEN <sub>MIDOL</sub>    | Thermal Fault<br>Output Logic Level<br>Low | LX8233 drives EN/FAULT pin.<br>Thermal Fault, Output Disabled,             | 1.1 |      |     | v     |

| VEN <sub>MIDOH</sub>    | Thermal Fault<br>Output Logic Level<br>Low | LX8233 drives EN/FAULT pin.<br>Thermal Fault, Output Disabled              |     |      | 1.9 | v     |

| Logic L                 | Logic Low Input                            | $V_{EN}$ = GND at the normal operation                                     |     | 10   |     | μA    |

| IIL <sub>EN/FAULT</sub> | Sink Current                               | $V_{EN}$ = GND at the thermal shutdown                                     |     | 20   |     | μA    |

| IIH <sub>EN/FAULT</sub> | Logic High Leakage<br>Current              | $V_{EN} = 4.3V$                                                            |     |      | 3   | μA    |

| RT (Note 3              | 3)                                         |                                                                            |     |      |     |       |

|                         | Input leakage<br>current                   | FET_ON = GND                                                               |     |      | 1   | μA    |

| Total Dev               | ice                                        |                                                                            |     |      |     |       |

| I <sub>Q_OP</sub>       |                                            | Operational                                                                |     | 0.32 | 0.5 | mA    |

| IQ_DIS                  | Bias Current                               | Disable (EN/FAULT = GND)                                                   |     | 70   |     | μΑ    |

| I <sub>Q_FLT</sub>      |                                            | Thermal Fault Latch Off                                                    |     | 0.1  | 1   | mA    |

| V <sub>MIN</sub>        | Minimum Operating<br>Voltage               | (Note 4)                                                                   |     |      | 7.6 | V     |

| I <sub>INRUSH</sub>     | In-Rush Current                            | at the slew rate of 12V/10ns (Note 1)                                      |     | 1.5  |     | Α     |

Note: 1. Guaranteed by Design

Note: 2. Pulse test: Pulse width =  $300\mu$ s, Duty cycle = 2%.

Note: 3. Total pin capacitance must be  $\leq$ 50pf to be considered floating by the chip.

Note: 4. Device may shut down prior to reaching this level based on actual UVLO trip point.

## Theory of Operation / Application Information

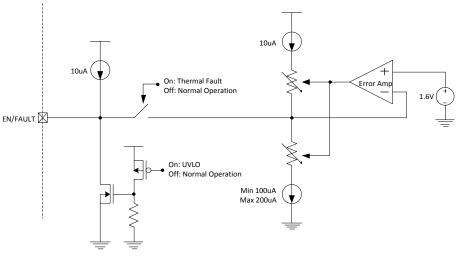

#### **EN/FAULT Operation**

EN/FAULT is typically floated and connected as common node between the parallel connected devices. There is an a weak (~430k $\Omega$ ) internal pull-up resistor, so the EN/FAULT pin goes to ~4.3V when VCC = 12V. However when parallel connected the actual voltage depends on the mismatch between the internal regulator supply voltages. To disable VOUT using the EN/FAULT pin you must use an external pull-down device, however the internal pull-up resistor will enable VOUT without any external signal.

If the IC's junction temperature passes the thermal shutdown threshold the LX8204 will pull down the EN/FAULTpin to the mid-level fault logic condition. As shown in the simplified schematic below an internal switch (thermal latch) engages at thermal shutdown driving the EN/FAULT pin to approximately 1.6V with pulldown capability to drive several parallel connected devices. Thus if LX8204 reaches thermal shutdown it will latch off all the parallel connected devices on the same node. It remains at 1.6V until either the Enable Pin is pulled low or there is a VCC power recycle.

Figure 4 · Simplified EN/FAULT circuitry

EN/FAULTnode is share with a secondary eFuse in order to shutdown the secondary eFuse for the case, thermal fault and UVLO condition. It will gurantee the secondary eFuse never turns on when LX8204 is under the specific condition like thermal fault and UVLO conditions. The EN/FAULT responses are listed in the following table. UVLO condition is applied even when VCC is in Hi-Z or grounded.

|               | eFuse                                                                                                               | EN/FAULT<br>as OUTPUT                                            | Effect on the secondary part |

|---------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------|

| UVLO          | eFuse is turned off.                                                                                                | Ground. Drive EN/FAULT is lower than 0.4V                        | Disable the secondary part.  |

| Thermal Fault | eFuse is turned off. The thermal<br>shutdown is latched off. It can<br>be reset by VIN recycle.<br>EN/FAULT toggle. | Mid point. Drive<br>EN/FAULT lower than<br>1.9V higher than 1.1V | Disable the secondary part.  |

#### **DV/DT (Rise time programming)**

The rise time is programmed by either connecting or grounding the RT pin. When the RT pin is floating, the rise time is 13mS (typ). When the RT pin is grounded, the soft start time depends on the order code. For example with order code LX8204-330, the soft start time will be 3.5mS (typ) when the RT pin is floating.

#### **Package Information**

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.