Power Matters.<sup>™</sup>

### Building High Reliability into Microsemi Designs with Synplify FPGA Tools

Microsemi Space Forum 2015, Synopsys

Microsemi

### Agenda

- FPGA SEU mitigation industry trends and best practices

- Market trends

- What's needed and when

- Current solutions

- Overview FPGA design tools

- Hardware debug and operation visibility

- DO-254 support

- SEU mitigation circuitry creation and error monitors

- New best practices  $\rightarrow$  What's next?

- Local TMR best practices

- Validating that TMR occurred and that it works

- Error monitoring and access

- Solutions for Microsemi RTG4

### **FPGA Military/Aerospace Solutions**

| Sal | And And |    |

|-----|---------|----|

| ~   |         |    |

| II. |         | 1/ |

- Mil/Aero market trends for FPGA systems

- Need highest datapath performance in smallest area

- High reliability and SEU error mitigation

- Strict processes for circuit creation and verification

- Reliable operation in harsh and high radiation environments

- Support for multiple FPGA vendor suppliers

- Synplify FPGA solutions provide

- DO-254 support and process compliance

- Debug operating design in RTL

- Automation of high reliability design techniques

- Highest system performance in smallest area

- Support for Verilog, VHDL, VHDL-2008 and System Verilog

Synplify enables high reliability, fast runtimes and deep debug

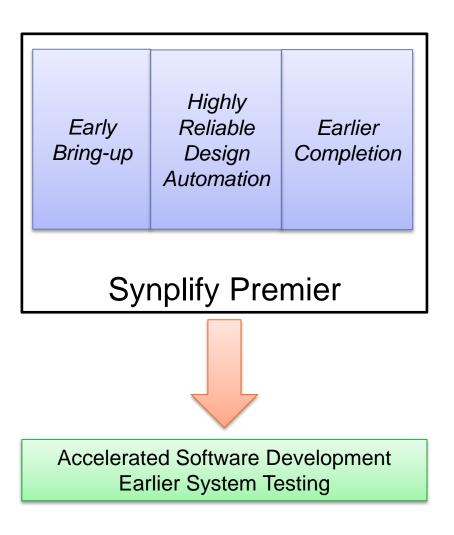

### Synplify Premier offers 10x Faster Hardware Bring-up for Microsemi FPGAs

- Single-pass design debug

- Upfront RTL and constraint checks

- Finds all errors in a single compile

- Diagnostic reporting

- Fast synthesis (low QoR) mode

- Highly Reliable Automation

- Hamming-3 error detection and correction design automation

- Quickly apply improvements

- Hierarchical & incremental flows

- Multi-machine synthesis

### Why is There a High Reliability Problem?

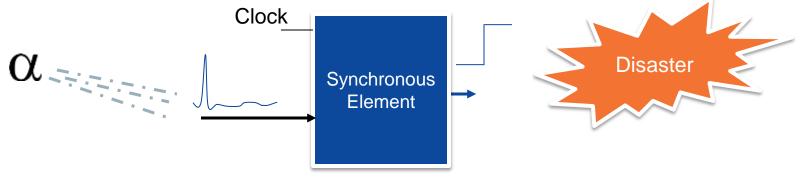

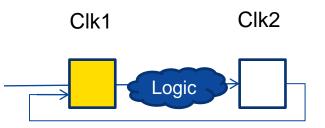

$\alpha$ Radiation-induced circuit glitches (SEUs, SETs) Power rail glitch Power supply glitch or brown-out Clk1 Clk2 Meta-stability due to design flaws Logic (failure to synchronize the circuit)

### **SETs and SEUs**

Glitches clocked into a synchronous element can cause operation errors and ultimately system failure

• Impacts memories, registers, state machines

#### **SET** (Single Event Transient)

A current spike or "glitch" in a signal that occurs due to ionization or electromagnetic radiation

### SEU (Single Event Upset)

Incorrect signal (SET) captured by a synchronous element that impacts its internal state and / or output

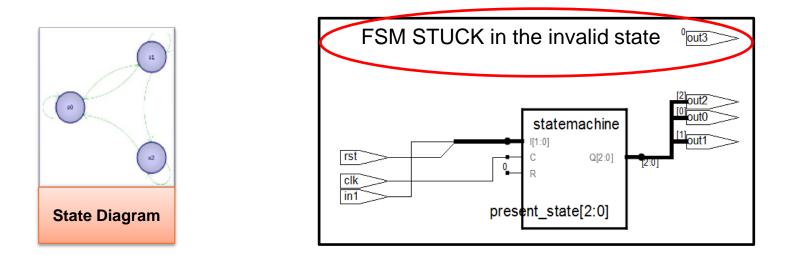

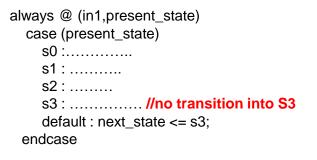

### SEUs Cause Incorrect Behavior or FSM Failure

A flip in a register bit within an FSM can cause what was assumed to be an "unreachable" or "invalid" state to be reached

RTL others clause that would handle state transition behavior out of an unreachable state is optimized away by default by the synthesis tool

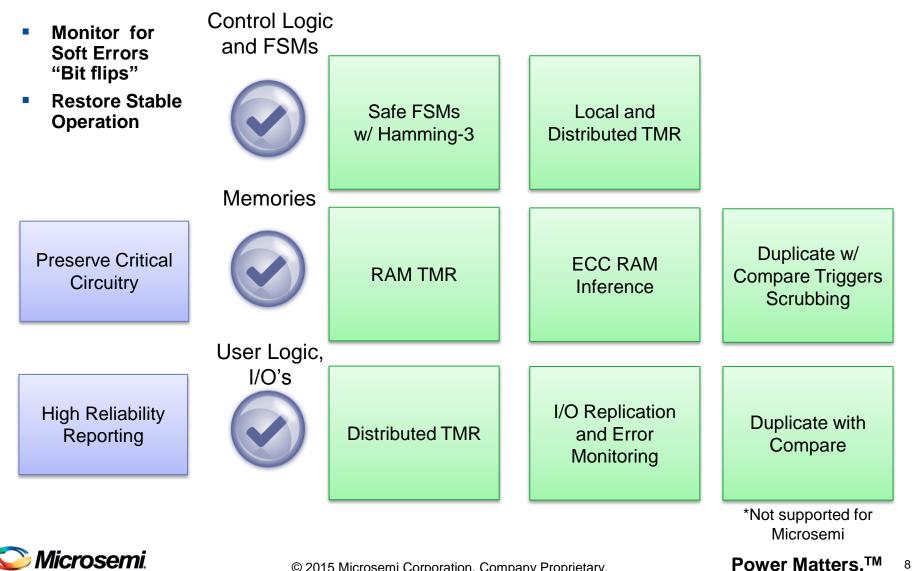

### **Synplify Premier Automates Design for High Reliability**

### **Radiation-Induced Error (SEU) Mitigation**

| Susceptibility to Particle Radiation Effects |                                                          |                                                          |           |  |

|----------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|-----------|--|

| Device Type                                  | RAD-HARD Anti-Fuse/<br>Flash                             |                                                          | SRAM      |  |

| Register                                     | Low Moderate                                             |                                                          | Low       |  |

| Block RAM                                    | Very High<br>unless Error Detection<br>& Correction used | Very High<br>unless Error Detection<br>& Correction used | Very High |  |

| Logic Cells                                  | None                                                     | None                                                     | High      |  |

| Routing Matrix                               | None                                                     | None                                                     | High      |  |

|                                              |                                                          |                                                          |           |  |

### **Current Solutions**

Overview FPGA design tools Hardware debug and operation visibility DO-254 support SEU mitigation circuitry creation and error monitors

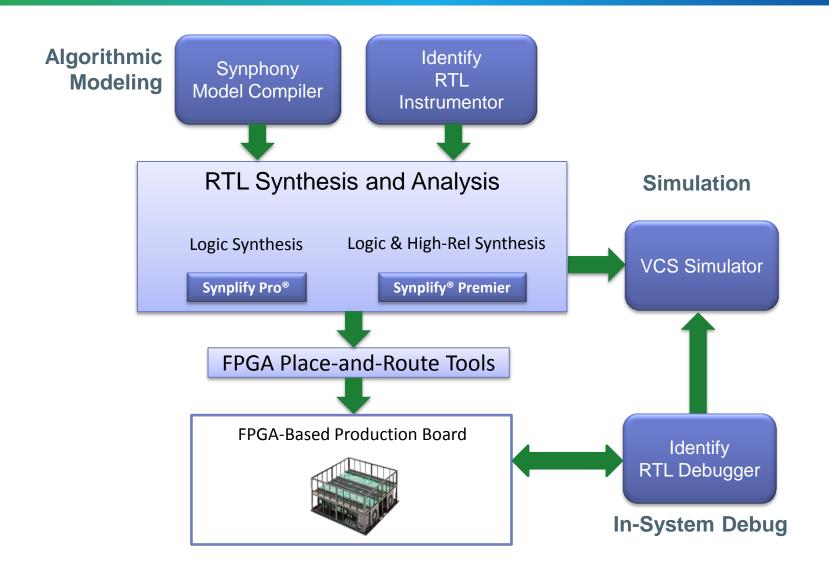

### **Synopsys FPGA Design Suite**

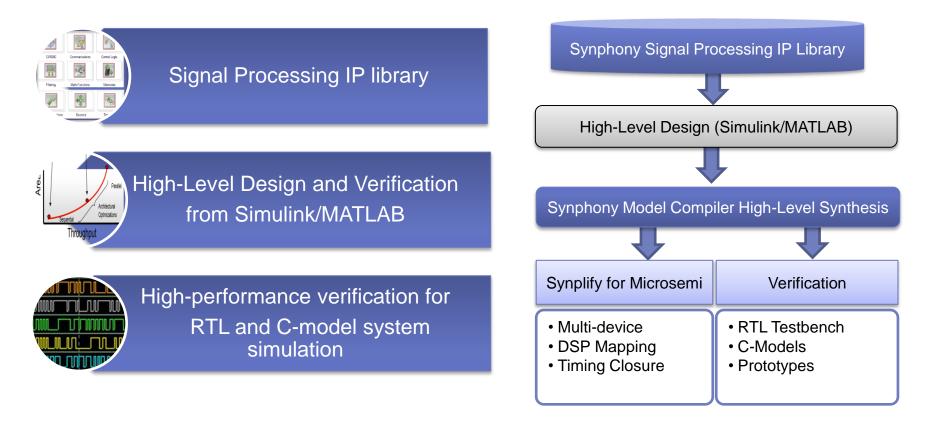

### **Synphony Model Compiler Overview**

Save Months in Design/Verification of Signal Processing Systems

Microsemi provides "Synphony Model Compiler" software distribution for Microsemi FPGA devices

Synopsys enables Synphony Model Compiler product enabling all FPGA devices

### Synplify Debug Provides Simulator-Like Visibility into FPGA Hardware Operation

| Tidentify Debugger<br>File Edit Debug Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | za z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Complex Counter Mode: events Value:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Error ROOT (bac, deno)<br>Error vord, star, tat (word, star)<br>Free tar year (star), tat (word, star), star<br>Free tar year (star), star, sta | 38       always@ ( #Gurr state <sup>2</sup> b01 or req1 or req2 )         39       begin         40       grant1 (= 1'b0;         41       grant 2 (= 1'b0;         42       case (#Gurr state <sup>2</sup> b02; //synopsys parallel_case         44       st_idle1: begin         45       if(( req1 += 1'b1;) 46 ( req2 == 1'b1 ))         46       #grant state <sup>2</sup> b01; (> st_grant2;)         47       else if ( req1 += 1'b1 )         48       #grant state <sup>2</sup> b01; (> st_grant1;)         49       else if ( req2 += 1'b1 )         50       #grant state <sup>2</sup> b01; (> st_grant2;)         51       else         52       #grant state <sup>2</sup> b01; (> st_grant2;)         53       end         64       et idle <sup>2</sup> ; bein                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INFO: OS<br>INFO: OS version<br>INFO: Using instrumen<br>b*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Image: Top [2560 rs         Marker: 1080 rs         Currer: 218 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs         Top [2560 rs           Wass         Top [2560 rs         Top [2560 rs |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | laty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

- Faster debug & higher design visibility

- Traditional debug takes too long

- Logic analyzers are insufficient

- Debug at speed in system required

- Debug were you design

- Instrument/debug directly in RTL

- Quickly select signals for sampling/triggering

- Capture signals at real-time speed

- Powerful triggering for pinpointing a fault

- Explore state spaces and conditions not easily reached by simulation

- Integrated with Synplify Premier

- Microsemi provides "Identify" software distribution for Microsemi FPGA devices

- Synopsys enables Synplify Premier and Identify products enabling all FPGA devices

7

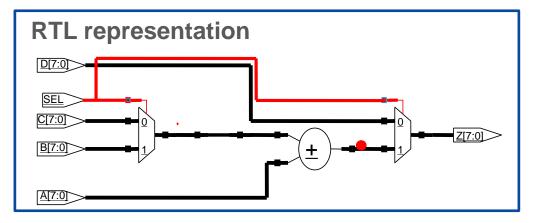

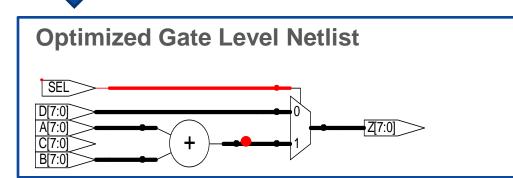

# Identify Enables Requirements Traceability after Synthesis Optimizations

- Synthesis

- RTL Enumerated TYPES appear as 1's and 0's in netlist

- RAM, DSP inferencing and sequential optimization optimize node in RED away

Synthesis performs optimizations

- Can cause debug node being absorbed or transformed

- No longer able to trace or probe these nodes

- Cannot relate their behavior in system back to your RTL

#### Instrument with Identify

- Nodes of interest preserved

- Relate behavior on board at nodes back to the RTL

### Synplify Enables DO-254 Compliant Process

|               |                                                                                                          | Extractivent SynDPSyS'<br>Particitative Reserves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Traceability  | Schematics for Documentation<br>Timing Reports and Log files<br>Safe FSM and TMR Reports                 | <section-header><section-header><section-header><list-item><list-item><list-item><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></list-item></section-header></section-header></list-item></list-item></list-item></section-header></section-header></section-header> |

|               |                                                                                                          | Synopsys:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Repeatability | Reproducible synthesis results<br>Lock down pre-verified blocks<br>Best Practices Safety-critical design | <section-header><section-header><section-header><text><text><text><text></text></text></text></text></section-header></section-header></section-header>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Equivalence   | Simulator Integration<br>Node preservation control for equivalence<br>assurance & requirements trace     | <text><section-header><text><text><text><text><text><text><text><text></text></text></text></text></text></text></text></text></section-header></text>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### **SEU Mitigation Practices – Synplify Pro & Premier**

- Clock Domain Synchronization Assurance

- Report alerts you to meta-stability problems due to design flaws such as failure to synchronize the circuit

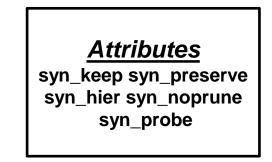

- Preservation of Debug Circuitry and of Custom Error Detection and Mitigation Circuitry

- Implementation during synthesis of RTL "others" clause that specifies your custom error mitigation circuitry

- Attributes to designate "preserve during synthesis nodes needed for probing and debug, or for equivalence proving purposes"

### **Single Event Upset Mitigation Practices**

- Antifuse/flash device registers can be moderately susceptible to SEUs

- FSMs contain registers

| Resource  | <b>Recommended solution</b>                                                                                                                        | Synplify<br>Version |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Registers | Local TMR                                                                                                                                          | Synplify Pro        |

| FSMs      | Hamming-3 Automatic Error<br>Correction<br>Specify how to return FSM from<br>"unreachable state" to safe state<br>by specifying and preserving the | Synplify Premier    |

TIP: Be sure to instruct the synthesis software to preserve error-mitigation circuitry

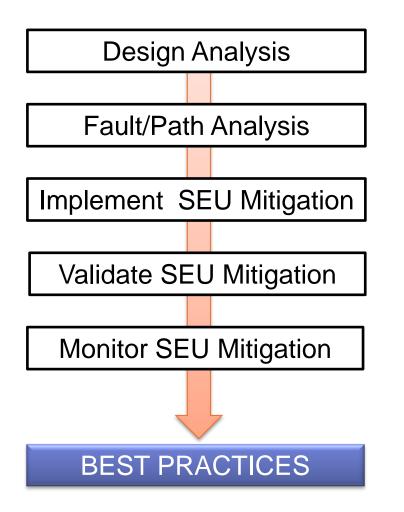

### **New Best Practices ... What's Next?**

Local TMR Best Practices Validating that TMR occurred and that it works Error monitoring and access Solutions for MicroSemi RTG4

### **New Industry Trends and Best Practices**

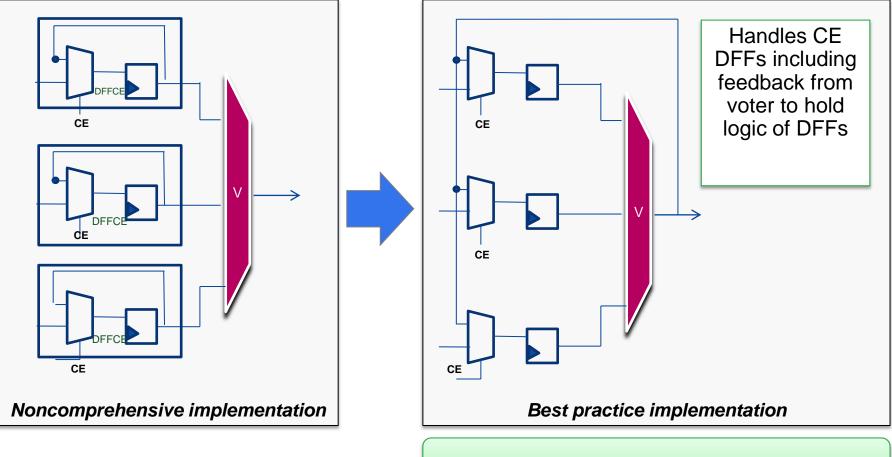

- TMR clock enable feedback loop in Local TMR & Distributed TMR circuitry

- Ways to determine "what best to TMR"

- Validation that TMR occurred

- Physical Separation of Triplicates

Synopsys is refining these solutions within Synplify Premier

### **Local TMR Best Practice**

Enhances Local TMR implementation to include feedback from voter

Available in Synplify Pro and Synplify Premier

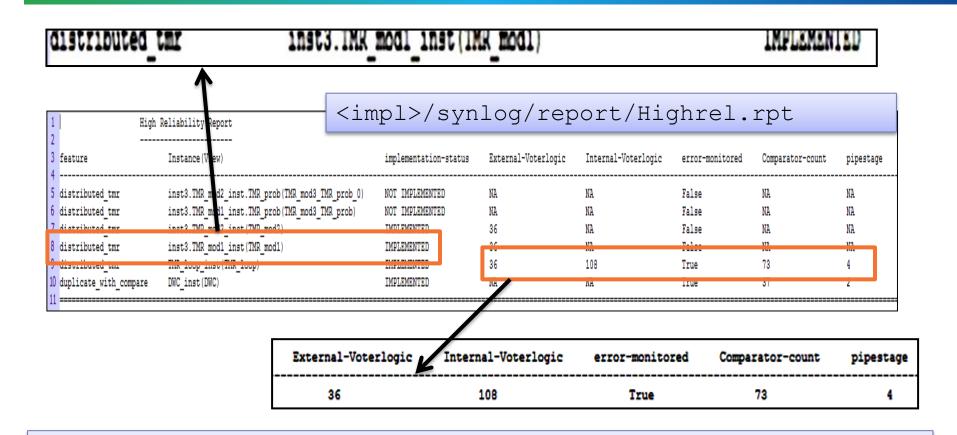

### Validating that TMR Occurred

Synplify Premier reports and confirms where SEU mitigation circuitry implemented

- For Local TMR and Distributed TMR, Safe FSM

- Voter logic, sequential loops, error monitoring, comparator gates, pipestage resources

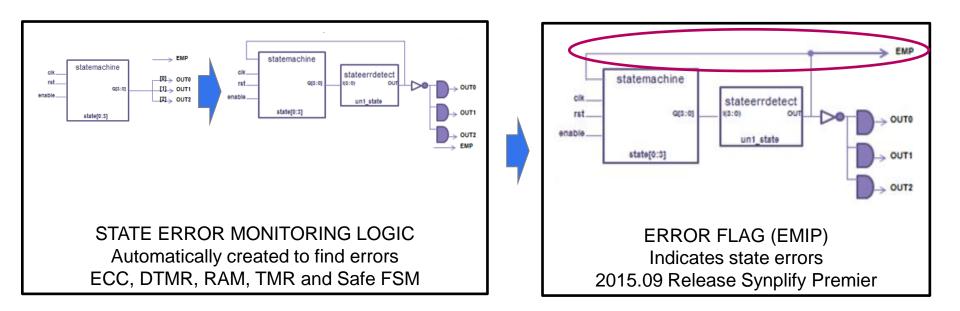

### **Error Monitoring & Access – FSM Example**

- Synthesis Attributes specify Error Nets to be monitored

- Synthesis creates error-monitoring logic and makes Error flag signal accessible

- set\_option –safe\_case 1

```

syn_create_err_net {-name {error_flag} -inst {i:state[1:3]}}

syn_connect -from {{n:error_flag} -to {t:EMIP.err_port}}

```

## **Synplify Premier MicroSemi RTG4 Solution**

- Safe FSM

- syn\_encoding = safe

- Using preserve & decode unreachable states logic

- Sequential logic and FSMs Hamming 3 error detection and correction (EDAC)

- Support for Block RAMs

- Inference of ECC block RAMs

- Access to error bits similar to duplicate and compare.

- Local TMR for registers not required

RTG4 design solution available in 2015.09 Synplify Premier release

### **More Information on Design for High Reliability**

http://www.synopsys.com/fpga

And visit us at our booth

### **Synplify Enables SEU Mitigation Methodologies**

- Enhanced Local TMR and Distributed TMR for CE DFF

- TMR Reporting Trade-off Analysis and Control

- TMR and Safe FSM reporting and/or visualization

- Fault injection for Safe FSM and TMR (future technology)

- Ease of validation of error recovery

- Error Flag implementation

### **Thank You**

Power Matters."

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com Microsemi Corporation (MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Power Matters.<sup>TM</sup>

26