Power Matters.<sup>™</sup>

#### **RTG4 Enabled by Microsemi Power Technology Portfolio**

Microsemi Space Forum 2015

Ken O'Neill, Director of Marketing, Space and Aviation

Brian Wilkinson, Sr Director Technical & Strategic Marketing & Applications

Microsemi Space forum

#### **RTG4 Overview and Power Requirements**

#### Agenda

- RTG4 product overview

- RTG4 power requirements

- Microsemi power components and systems

#### Introducing RTG4 High-Speed RT FPGAs

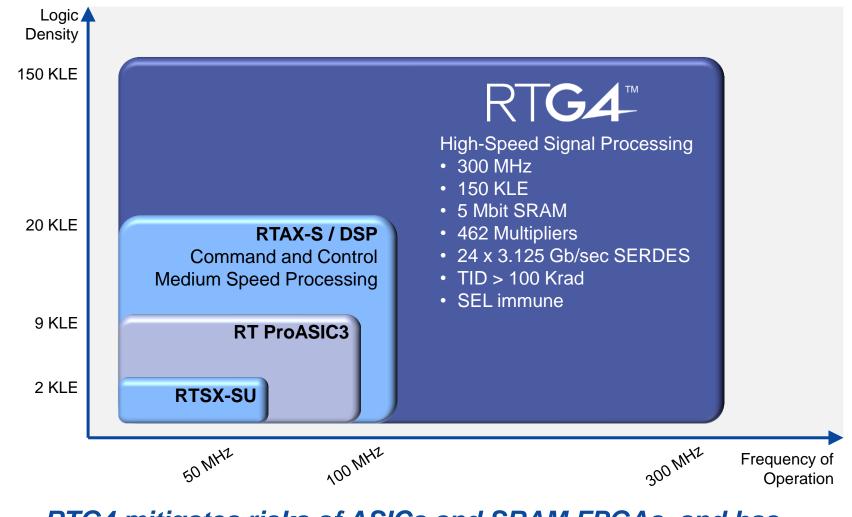

# RTG4 mitigates risks of ASICs and SRAM FPGAs, and has 20X improvement in signal processing throughput

😳 Microsemi.

## Why RTG4 is Compelling

- More flexible than an RH ASIC

- Reprogrammable, no NRE, no cost and schedule risk

- More signal-processing features than any other RT FPGA

- More registers, combinatorial logic, multiply blocks, and transceivers

- Lower power, live at power-up, no external boot memory needed

- Radiation enhanced for Geosynchronous Earth Orbit and deep space

- RTG4 65nm Flash has complete immunity to configuration upsets (SEU)

- Total ionizing dose (TID) and single event effects (SEE) hardened by design

#### **RTG4** offers groundbreaking features for satellite applications

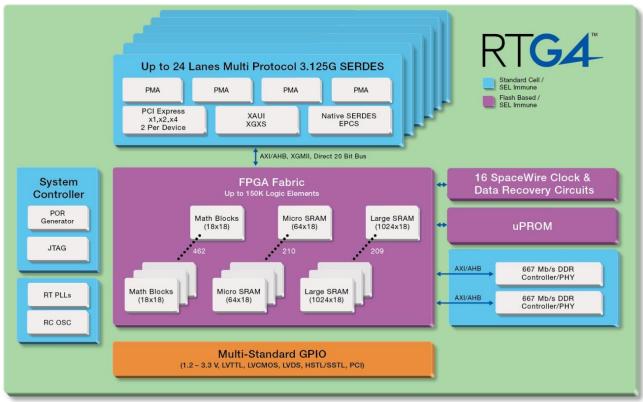

#### **RTG4 Radiation-Mitigated Architecture**

- Total-dose hardening of Flash cells

- Single-event hardening of registers, SRAM, multipliers, PLLs

#### Comprehensive radiation-mitigated architecture for signal processing applications

🏷 Microsemi.

#### **RTG4 Family Resources**

| Resources                                         | RT4G075      | RT4G150      |

|---------------------------------------------------|--------------|--------------|

| Logic Elements (TMR Register + 4-Input C Logic)   | 77,712       | 151,824      |

| 18x18 Multiply-Accumulate Blocks                  | 224          | 462          |

| RAM Mbits (1.5 Kbit and 24 Kbit Blocks, with ECC) | 2.8          | 5.2          |

| UPROM Kbits                                       | 254          | 381          |

| DDR2/3 SDRAM Controller (with ECC)                | 2x32         | 2x32         |

| PCI Express Endpoints                             | 2            | 2            |

| Globals                                           | 24           | 24           |

| PLLs (Rad Tolerant)                               | 8            | 8            |

| SpaceWire Clock & Data Recovery Circuits          | 16           | 16           |

| User IO (excluding SERDES)                        | 528          | 720          |

| SERDES lanes (3.125 Gbit/sec)                     | 16           | 24           |

| Hermetic, Ceramic Column-Grid Packages            |              |              |

| CG1432 (Six Sigma Columns)                        | $\checkmark$ |              |

| CG1657 (Six Sigma Columns)                        | $\checkmark$ | $\checkmark$ |

- RT4G150 is the first device, available now in Engineering Samples

- RT4G075 availability TBD

#### **Power Supplies**

|                         | [                                          | 2704                                                                             | 1                             | Supply                   | Voltage                                    | Description                                                                           |

|-------------------------|--------------------------------------------|----------------------------------------------------------------------------------|-------------------------------|--------------------------|--------------------------------------------|---------------------------------------------------------------------------------------|

| 2/ 1.5/ 1.8/ 2.5/ 3.3 V |                                            | RTG4                                                                             |                               | VDD                      | 1.2 V                                      | Core supply voltage                                                                   |

| 1.2/ 1.5/ 1.8/ 2.5      | VDDIx (MSIO banks)                         | SERDES_x_Lyz_VDDAIO<br>Tx/Rx Analog I/O Supply                                   | 1.2 V                         | VPP                      | 3.3 V                                      | Power supply for device<br>charge pumps                                               |

| 1.8/ 2.5/ 3.3 V<br>T    | Bank Supplies<br>VDDIx (MSIOD & DDRIO bank | s) SERDES_VDDI<br>Ref Clock recovery Supply<br>SERDES_x_Lyz_VDDAPLL              | 1.8/2.5/3.3 V                 | VDDPLL                   | 3.3 V                                      | Power for eight corner<br>PLLs, PLLs in SERDES<br>PCIe/PCS blocks, and<br>FDDR PLL    |

| 3.3 V                   | VDDI 3 (JTAG)<br>VPP Charge Pump           | Analog Supply for SERDES PLL of PCIe<br>SERDES_x_Lyz_REFRET<br>SERDES_x_Lyz_REXT | 0.1 μF<br>1.21 k ,1%          | VDDIx                    | 1.2 V, 1.5 V, 1.8<br>V,<br>2.5 V, or 3.3 V | Bank supplies                                                                         |

| 1.2 V                   |                                            |                                                                                  | SERDES VDDI                   | VREFx                    | 0.5 * VDDIx                                | FDDR reference voltage                                                                |

| VD <u>Dix</u>           | VDD Core supply                            | SERDES VREF                                                                      | \$1 k, 1%                     | SERDES_x_Lyz_VDDAI<br>O  | 1.2 V                                      | TX/RX analog I/O<br>voltage for SERDES<br>lanes.                                      |

| \$1k, 1%                | VREF x FDDR                                |                                                                                  | <b>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓</b>    | SERDES_x_Lyz_VDDAP<br>LL | 2.5 V                                      | Analog power for<br>SERDES TXPLL and<br>CDRPLL                                        |

| ₹1k, 1%                 |                                            | VDDPLL                                                                           | 3.3 V<br>5<br>22uF + + + 47uF | SERDES_VDDI              | 1.8 V, 2.5 V, or<br>3.3 V                  | Power for SERDES<br>reference clock receiver<br>supply.                               |

| Ţ                       | VSS                                        |                                                                                  | ļ                             | SERDES_VREF              | 0.5 *<br>SERDES_VDDI                       | External differential<br>receiver reference<br>voltage for SERDES<br>Reference Clocks |

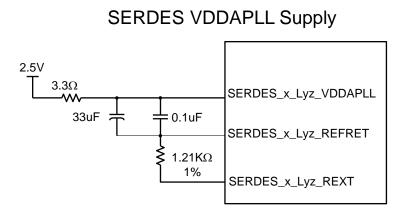

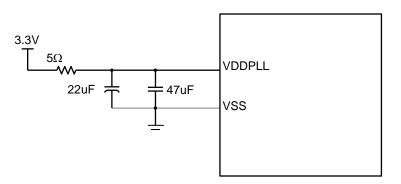

# **Analog Supplies**

FPGA PLL Supply

- External R-C filters provide filtering to sensitive analog PLL supplies.

- SERDES PLL = 2.5V

- SERDES TXPLL and CDRPLL supply

- SERDES Calibration resistor(REXT). 1.21KΩ

- impedance calibration (transmit, receive, and receiver equalization)

FPGA PLLs = 3.3V

Place all passive components as close to device as possible.

#### **Power Supply Specifications**

Key power supplies must comply to the specifications including operating range, POR trip points, and power supply ramp rates

| Symbol  | Description                                                                       | Min   | Тур | Max  | Units |

|---------|-----------------------------------------------------------------------------------|-------|-----|------|-------|

| VDD     | Core Supply Voltage                                                               | 1.14  | 1.2 | 1.26 | V     |

| VPP     | Flash operating voltage                                                           | 3     | 3.3 | 3.45 | V     |

| VDDt    | Power ON Reset Threshold for VDD supply                                           |       | 0.8 |      | V     |

| VPPt    | Power ON Reset Threshold for VPP supply                                           |       | 2.6 |      | V     |

| VDDr    | VDD Power supply ramp rates ( from GND/0V) for all power supplies                 |       |     | 24   | mV/μs |

| VPPr    | VPP Power supply ramp rates ( from GND/0V) for all power supplies                 | 0.016 |     | 66   | mV/μs |

|         | Monotonicity of VDD/VPP/VDDIx required through its rise time                      |       | Yes |      |       |

| Tvddpor | Power Up to Functional time (From VDD/VPP/VDDIx ramp to beginning of device ready |       | 60  |      | ms    |

## **Power Supply Decoupling Capacitors**

- Proper on-board power supply decoupling is required

- Keep decoupling caps close to pin (use 402's where possible on underside)

- Distribute overall decoupling capacitance around the device perimeter

- Use blind vias to remove crosstalk risk and cap surface mount area

- Use larger power vias to reduce inductance especially for high layer count boards

- PME (Precious Metal Electrode) decoupling caps within the FPGA package enhances overall PCB decoupling

| Pin Name | Internal PME capacitance available for CG1657 package |

|----------|-------------------------------------------------------|

| VDD      | 2.2uF/4V                                              |

| VDDI0    | 2.2uF/4V                                              |

| VDDI1    | 2.2uF/4V                                              |

| VDDI2    | 2.2uF/4V                                              |

| VDDI4    | 0.68uF/6.3V                                           |

| VDDI5    | 0.68uF/6.3V                                           |

| VDDI6    | 0.68uF/6.3V                                           |

| VDDI7    | 2.2uF/4V                                              |

| VDDI8    | 2.2uF/4V                                              |

| VDDI9    | 2.2uF/4V                                              |

| VDDPLL   | 2.2uF/4V                                              |

#### **Radiation Tolerant Power Supplies**

- Microsemi provides many Radiation-Tolerant components that can be used to supply power to RTG4 FPGAs

- Engineers should consider the following when selecting power supply components

- Calculate required power of the RTG4 device

- PowerCalc spreadsheet, SmartPower tool in Libero design software

- Select an appropriate Radiation-Tolerant regulator that can supply the required power and meet all power requirements of RTG4

- Radiation-Tolerant Linear-Regulator (Microsemi)

- Radiation-Tolerant Switching regulator (Microsemi)

#### **Current Requirements**

- Use RTG4 Power Calculator to estimate current required

- Available on Microsemi web site <u>RTG4 Power Calculator</u>

- Need to enter specific details for your design

- Example is for 99% utilized RT4G150 total 6.7W

- 4 fast clocks (150MHz to 250MHz), 2 slow clocks (25MHz and 50MHz)

- 496 I/O (400 LVCMOS, 66 PCI, 32 LVDS)

- 8 Lanes of transceivers (2.5Gb/sec)

| Current Summary             |              |             |            |  |  |

|-----------------------------|--------------|-------------|------------|--|--|

| Rail Breakdown              |              |             |            |  |  |

| Rail Name                   | Current (mA) | Voltage (V) | Power (mW) |  |  |

| VDD                         | 3928.71      | 1.200       | 4714.45    |  |  |

| VDDI 1.2                    | 33.96        | 1.200       | 40.75      |  |  |

| VDDI 1.5                    | 0.00         | 1.500       | 0.00       |  |  |

| VDDI 1.8                    | 0.00         | 1.800       | 0.00       |  |  |

| VDDI 2.5                    | 535.42       | 2.500       | 1338.56    |  |  |

| VDDI 3.3                    | 14.73        | 3.300       | 48.61      |  |  |

| SERDES_[01]_L[0123]_VDDAIO  | 287.38       | 1.200       | 344.86     |  |  |

| SERDES_[01]_L[0123]_VDDAPLL | 20.60        | 2.500       | 51.50      |  |  |

| PLL_VDDA                    | 60.00        | 2.500       | 150.00     |  |  |

#### **Microsemi Power Solutions for RTG4**

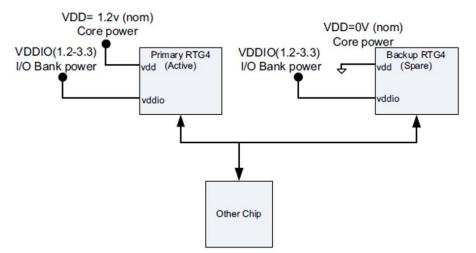

#### **Cold Sparing**

Advantages of cold sparing:

- Power-Up can be done in any sequence. (No Power supply sequencing requirements).

- No excess device leakage in spare device where implemented.

In cold sparing applications, voltage can be applied to device I/O's before and during power-up. RTG4 device is capable of cold sparing applications with the following strategies:

### **RTG4 Cold Sparing Strategies**

- Example of a system board integrating two parallel RTG4 devices on the board with shared or common I/C connections.

- Primary RTG4 device has its core powered and fully functional until a point where a swap of devices is determined as necessary.

- Backup RTG4 device has its I/O banks powered to prevent I/O leakage through the ESD diode and fabric core un-powered. This establishes a low power, protected state for the backup RTG4 device.

- At any point, you can swap by powering down the core of the primary RTG4 device and power up the core of the backup RTG4 device going through its configuration sequence.

- Primary and backup devices are identical parts.

- Only one of the two devices might be active at one time.

- Core VDD high activates the part and low de-activates the part.

- The de-activate part must tie the VDD to the ground and must not be floating.

#### SA 50 Series Concept, isolated DC-DC

#### SMT Construction in an Industry Standard Package

- •Features:

- +28V or 120V nominal Inputs

- Internal EMI Filter (120V version)

- •Triple, Dual and Single output versions

- Isolated Outputs

- •50W total combined power output

- Inhibit Feature

- •Isolated Sync Input, 500kHz

- •Output trim on Single & Dual Variants

- •>86% efficient Full load @5 +-15V out

- •Length Width Height

- •<u>3.055 x 2.055" x 0.50"</u>

- •Total Dose Rating of 200KRads

- •Threshold (LET) with no latch-up >80MeV-cm2/mg

### SB 30 Series 30 Watt Family, isolated DC-DC

- Triple Output for Digital Loads

- –5V @ 2A; 3.3V @ 3A; 2.5V @ 3A

- 30W total combined power output

- +28V or 100V nominal Inputs

- Internal EMI Filter (100 Vin only)

- •Outputs individually regulated

- Power Good Status

- •+/- 10% trim for each output

- Inhibit Feature

- Isolated Sync Input, 500kHz

- •75% efficiency

- •<u>3.055 x 2.055" x 0.60"</u>

- Total Dose Rating of 200KRads

- •Threshold (LET) with no latch-up >80MeV-cm2/mg

#### © 2015 Microsemi Corporation. Company Proprietary.

# SMT Construction in an Industry Standard Package

#### SB 30 Series 30 Watt Family, isolated DC-DC

- Designed to support multiple Low Voltage Digital loads

- Three independent outputs, each regulator with it's own PWM

- Multi Simultaneous Switching Outputs on one rail will not induce noise on an adjacent rail

- Excellent load step response

- Power up / power down sequencing built in

- Synchronize clock with other converters to reduce system noise

- For a nominal NRE, input / output voltages can be customized – consult PMG Microsemi

### **Isolated DC-DC converters in production**

- SA50-120-12S-B-P SA50-120-12S-B-T SA50-120-15S-A-H SA50-120-15S-A-P SA50-120-28S-B-H SA50-120-28S-B-P SA50-120-28S-B-T SA50-120-3R3-14T-B-P SA50-120-3R3-14T-B-TX1 SA50-120-5-12T-A-P SA50-120-5-12T-A-T SA50-120-5-15T-A-H SA50-120-5-15T-A-P SA50-120-5-15T-A-T SA50-28-5-15T-A-H SA50-28-5-15T-A-P SA50-28-5-15T-A-T SB30-100-2R5S-3R3-5T-A-H SB30-100-2R5S-3R3-5T-A-P SB30-100-2R5S-3R3-5T-A-T

- Input Voltages 28V, 100V & 120V Standard, others Custom

- Single Outputs: 3.3V, 5V, 12V, 15V, 28V Standard, others Custom

- Dual Outputs: Special Configurations of Triples

- Triple Outputs: 3.3V or 5V with 12V or 15V Standard, others can be available

- Case Style

- A = leads out the side

- B = leads out the top

- Performance Level

- P = Prototype

- T = SEE Tolerant, TID Hard

- H = SEE Hard, TID Hard

- Go To: <u>http://www.microsemi.com/product-</u> <u>directory/modules-a-hybrids/1450-dc-to-dc-converters</u>

#### Also Available:

- Semi and full Customized Versions

- Filter Solutions e.g. SF200-28

#### **RHH- Linear Regulators**

| Product   | Description                                                  | Critical<br>Parameters                                        | Vin Range      | Vout Range      |

|-----------|--------------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------|

| MHL8601   | Pos., Linear, 3A<br>Fixed or<br>Adjustable                   | VLDO = 0.300 V<br>(3A), Rad-Hard to<br>300Krad+               | +3V to +5.5V   | +1.26V to +4.5V |

| MHL8605   | Pos., Linear, 5A,<br>Fixed or<br>adjustable                  | VLDO = 0.300<br>(2A), 0.400 V (5A)<br>RadHard to 300<br>Krad+ | SV to +5.5V    | +1.26V to +4.5V |

| MHL8701/5 | Pos., Linear, 5A,<br>Fixed or<br>adjustable, SEE =<br>82 MeV | VLDO = 0.400 V<br>(2A) RadHard to<br>300 Krad+                | +3V to +5.5V   | +1.26V to +5.5V |

| MHL117    | Pos. Linear, Adj.,<br>1.25A, Vin = 40 V                      | RadHard to<br>300Krad                                         | +5V to +37V    | +1.21V to +4.5V |

| MHL127    | Dual, ±1A, Pos.<br>and Neg. Linear<br>regulator              | RadHard to 300<br>Krad                                        | ±5V to<br>±40V | ±6.5V to ±37V   |

#### **Linear Applications**

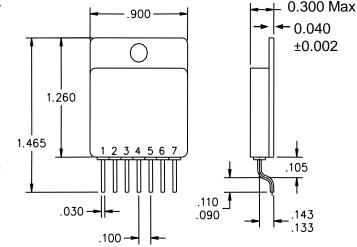

### **ULDO Linear Regulator MHL8701**

- The MHL 8701 series products are space qualified, ultra low dropout linear regulators designed for military and space flight applications. Assembled in a hermetic package, this series provides an ultra low drop out voltage of 400mV @ 2A. They are optimized for operation at +5V input or +3.3V input.

- Enhanced SEE performance, SET < 5% of Vout

- Thermal shutdown @ 150 °C

- Output Voltage: +1.26V to +4.5V

- Post Rad Output Voltage accuracy +-6%

- Rad-Tolerant to 300 Krad HDR TID

- Rad- Tolerant to 100 Krad Eldrs .01 rads(si)/sec

- LET= 85 MeV (Au ions) No Latch-up

- Fixed & Adjustable output voltages New Product

- 7 Pin Power SIP

- Available Now

#### **RHH-POL's**

| Product  | Description                               | Critical Parameters                  | Vin Range<br>(De-rated) | Vout Range         |

|----------|-------------------------------------------|--------------------------------------|-------------------------|--------------------|

| MHP8564A | Sw. Reg., 4.5A,<br>Adj./Fixed             | 300 Krad, lout= 4.0A                 | +4.5V to +8V            | +1.21V to<br>+4.5V |

| MHP8565A | Sw. Reg., 3.0A,<br>Adj                    | 300 Krad, Iout = 3.0A                | +4.5V to +8V            | +1.21V to<br>+4.5V |

| MHP8566A | Quad Sw. Reg.,<br>Adjustable Vout,<br>15A | 100 Krad TID, 15A<br>Efficiency, 15A | +4.5V to +8V            | +1.0V to<br>+4.5V  |

#### **RadHard Quad POL- MHP8566**

- Rad-Tolerant to 100 Krad <sup>1</sup>

- Quad adjustable output to +1.21 V.

- Up to 16A output current (total of all outputs)

- Vin Range: +4.5 V to +8 V (for +12 Vin consult factory)

Surface-mount package:

2.0 in. X 2.0 in. X 0.290 in.

Complete assembly – just add voltage set resistors.

Configurable as four independent 4A POLs or one 16A POL

```

*****FPGA Power Supply*****

```

42 pin flat pack = L 82.5 X W 82.5 X H 11.2 mm

Microsemi

SPACE FORUM

## **Thank You**

Power Matters."

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com Microsemi Corporation (MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Power Matters.<sup>TM</sup> 26