Power Matters.<sup>™</sup>

#### **RTG4 Board Level Considerations**

Microsemi Space Forum 2015

Bassam Youssef, Senior Staff Applications Engineer Jim Steward, Application Engineering

Microsemi

#### **Objectives**

- Provide an overview of PCB design considerations for RTG4 designs focusing on:

- Power Supplies

- Memory Controller Interfaces

- SERDES Interfaces

- Highlight information currently available in Microsemi documents

#### **Power Supplies**

|                           |                                                               |                                                                             | 1                    | Supply                       | Voltage                                    | Description                                                                           |

|---------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------|------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------|

| 1.2/ 1.5/ 1.8/ 2.5/ 3.3 V | l t                                                           | RTG4                                                                        |                      | VDD                          | 1.2 V                                      | Core supply voltage                                                                   |

| 1.2/ 1.5/ 1.8/ 2.5        | VDDIx (MSIO banks)                                            | SERDES_x_Lyz_VDDAIO<br>Tx/Rx Analog I/O Supply                              | 1.2 V                | VPP                          | 3.3 V                                      | Power supply for device charge pumps                                                  |

| 1.8/ 2.5/ 3.3 V           | Bank Supplies<br>VDDIx (MSIOD & DDRIO banks)<br>VDDI 3 (JTAG) | SERDES_VDDI<br>Ref Clock recovery Supply<br>SERDES_x_Lyz_VDDAPLL            | 1.8/ 2.5/ 3.3 V      | VDDPLL                       | 3.3 V                                      | Power for eight corner<br>PLLs, PLLs in SERDES<br>PCIe/PCS blocks, and<br>FDDR PLL    |

| 3.3 V                     | VDD 3 (JTAG) Analog VPP Charge Pump                           | g Supply for SERDES PLL of PCIe<br>SERDES_x_Lyz_REFRET<br>SERDES_x_Lyz_REXT | 0.1 μF<br>1.21 k ,1% | VDDIx                        | 1.2 V, 1.5 V,<br>1.8 V,<br>2.5 V, or 3.3 V | Bank supplies                                                                         |

| VDDix                     | VDD Core supply                                               | SERDES VREF                                                                 | SERDES VDDI          | VREFx<br>SERDES_x_Lyz_VDDAIO | 0.5 * VDDIx<br>1.2 V                       | FDDR reference<br>voltage<br>TX/RX analog I/O<br>voltage for SERDES                   |

| 1k, 1%                    | VREF x FDDR                                                   |                                                                             | ₹1 k , 1%            | SERDES_x_Lyz_VDDAPLL         | 2.5 V                                      | lanes.<br>Analog power for<br>SERDES TXPLL and<br>CDRPLL                              |

| <b>1 K</b> , 176          | vss                                                           | VDDPLL                                                                      | 22uF T T 47uF        | SERDES_VDDI                  | 1.8 V, 2.5 V, or<br>3.3 V                  | Power for SERDES reference clock receiver supply.                                     |

| Ţ                         |                                                               |                                                                             |                      | SERDES_VREF                  | 0.5 *<br>SERDES_VDDI                       | External differential<br>receiver reference<br>voltage for SERDES<br>Reference Clocks |

C Microsemi.

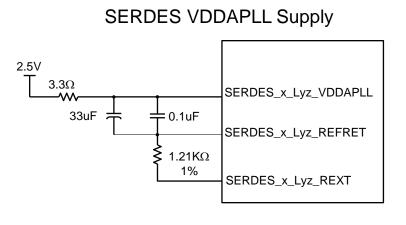

# **Analog Supplies**

FPGA PLL Supply

- External R-C filters provide filtering to sensitive analog PLL supplies.

- SERDES PLL = 2.5V

- SERDES TXPLL and CDRPLL supply

- SERDES Calibration resistor(REXT). 1.21KΩ

- Impedance calibration (transmit, receive, and receiver equalization)

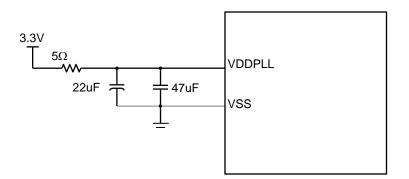

- FPGA PLLs = 3.3V

- Place all passive components as close to device as possible

#### **Power Supplies Specifications**

- Key power supplies must comply to the specifications including operating range, POR trip points, and power supply ramping

- Monotonicity of VDD/VPP/VDDIx is required through its rise time Preliminary Data

| Symbol  | Description                                                                       |       | Тур | Max  | Units |

|---------|-----------------------------------------------------------------------------------|-------|-----|------|-------|

| VDD     | Core Supply Voltage                                                               | 1.14  | 1.2 | 1.26 | V     |

| VPP     | Flash operating voltage                                                           | 3     | 3.3 | 3.45 | V     |

| VDDt    | Power ON Reset Threshold for VDD supply                                           |       | 0.8 |      | V     |

| VPPt    | Power ON Reset Threshold for VPP supply                                           |       | 2.6 |      | V     |

| VDDr    | VDD Power supply ramp rates ( from GND/0V) for all power supplies                 | 0.006 |     | 24   | mV/μs |

| Tvddpor | Power Up to Functional time (From VDD/VPP/VDDIx ramp to beginning of device ready |       | 60  |      | ms    |

#### **Power-up/down Sequence**

- There is no power-up/down sequence required for RTG4 if one of the following conditions is met:

- All PLLs are held in reset until VDDPLL supply reaches its minimum recommended Operating Conditions level (shown below)

| Symbol | Parameter                                                                     | Min  | Тур | Max  | Units |

|--------|-------------------------------------------------------------------------------|------|-----|------|-------|

| VDDPLL | Power for eight corner PLLs, PLLs in SERDES<br>PCIe/PCS blocks, and FDDR PLL. | 3.15 | 3.3 | 3.45 | v     |

- The device is held in reset by asserting DEVRST\_N until VDDPLL supply reaches its minimum recommended level as stated above

- If none of the above conditions is met, VDDPLL must start ramping up and reach its minimum recommend level (as stated above) before VDD, VPP, or VDDIx starts ramping up

- In other words, VDDPLL must not be the last supply to ramp up, and must reach its minimum recommended level before the last supply starts ramping up

- All I/O banks supplies must be powered for the RTG4 to power up

- You can bring up the I/O banks in any order and before or after the core voltage

# **Power Supply Decoupling Capacitors**

- To reduce any potential fluctuation on the power supply lines, proper onboard power supply decoupling caps is required

- Keep decoupling caps close to pin (use 402's where possible on underside of device BGA)

- Distribute overall decoupling capacitance around the device perimeter

- Use blind vias to remove crosstalk risk and cap surface mount area

- Use larger power vias to reduce inductance- especially for high layer count boards.

- PME (Precious Metal Electrode) decoupling caps within the package enhance overall PCB decoupling

| Pin<br>Name | Internal PME capacitance<br>available for LG/CG1657 |  |  |  |  |

|-------------|-----------------------------------------------------|--|--|--|--|

|             | package                                             |  |  |  |  |

| VDD         | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI0       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI1       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI2       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI4       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI5       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI6       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI7       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI8       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDI9       | 0.18uF/6.3V                                         |  |  |  |  |

| VDDPLL      | 0.8uF/6.3V                                          |  |  |  |  |

#### **Radiation Tolerant Power Supplies**

- Microsemi provides many Radiation-Tolerant components that can be used with RTG4 PCB designs

- Engineers should consider the following when selecting power supply components

- Calculate required power of the RTG4 device

- Power Calculator spreadsheet

- SmartPower tool in Libero SoC

- Select an appropriate Radiation-Tolerant regulator that can supply the required power and meet all the unique power requirements of the FPGA, using either of the below:

- Radiation-Tolerant Linear-Regulator (Microsemi)

- Radiation-Tolerant Switching regulator (Microsemi)

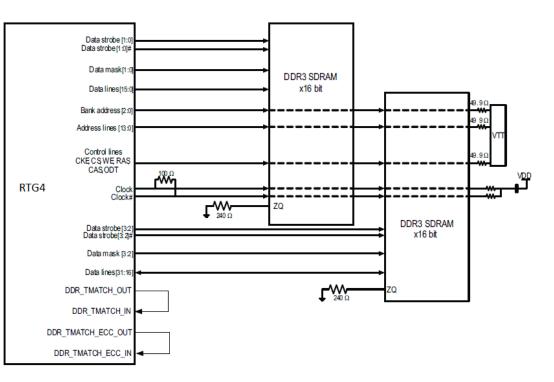

# **DDR3 Memory Interface**

#### DDR3 Characteristics

- SSTL15 interface

- RTG4 On-Die termination

- RTG4 IMP\_CALIB resistor

- **240**Ω

- CMD/ADDR require external termination to VTT(0.75V)

- CLK\_P/CLK\_N requires differential resistor at memory clk input

- Match ADDR/CMD/CTRL to CLK

- Tightly match DQ/DM/DQS delays

- TMATCH DQS compensation

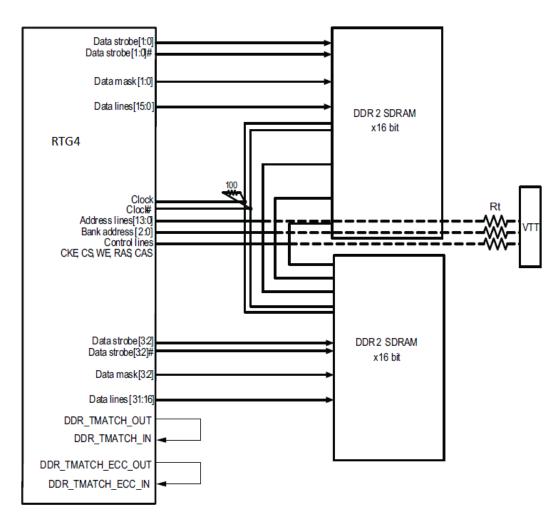

# **DDR2 Memory Interface**

- DDR2 Characteristics

- SSTL18

- RTG4 On-Die termination

- RTG4 IMP\_CALIB resistor

- 150Ω

- CMD/ADDR require external termination to VTT(0.9V)

- CLK\_P/CLK\_N requires differential resistor at memory clk input

- Match ADDR/CMD/CTRL to CLK

- Tightly matched DQ/DM/DQS delays

- Loosely match DQS to CLK

- TMATCH DQS compensation

\sub Microsemi.

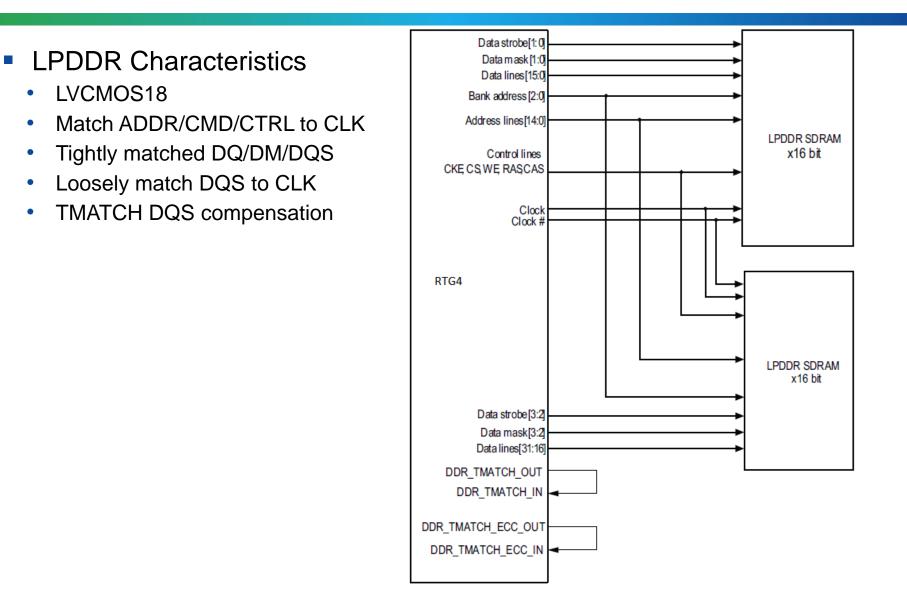

# **LPDDR Memory Interface**

😳 Microsemi.

# **SERDES Routing**

- Proper differential pair routing is needed for proper common-mode rejection and noise immunity

- Pair-to-pair spacing is 2X greater than trace-to-trace spacing

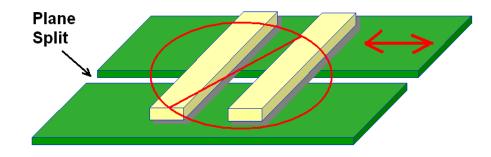

- Avoid Routing Discontinuities:

- No Plane Split Crossing

- Do not route High-Speed signals close to the edge of a plane

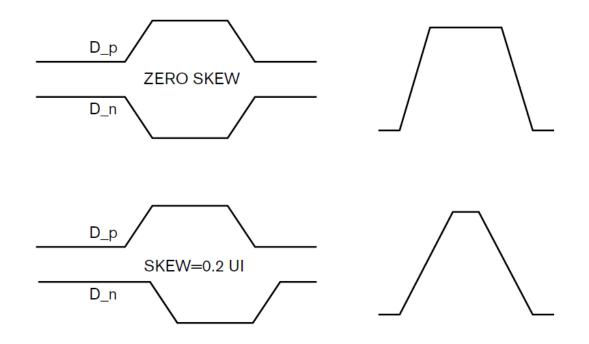

#### **SERDES Differential Skew**

- "Differential skew" refers to the time difference between the two singleended signals in a differential pair (LANE)

- Skew limits the bandwidth, adds data-dependent jitter, and limits the possibility of properly equalizing lanes

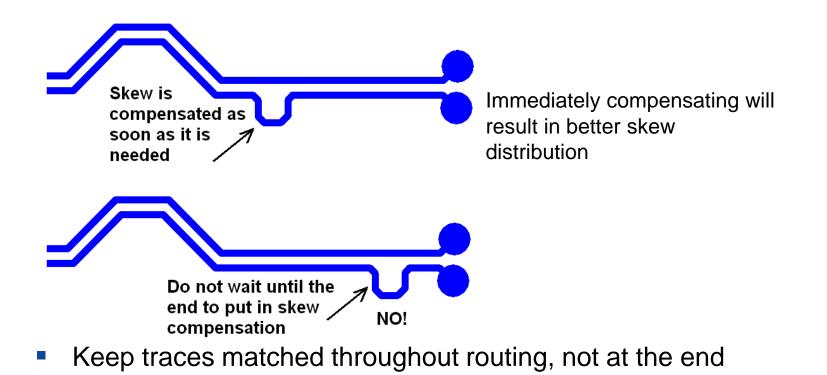

#### **SERDES Skew Matching**

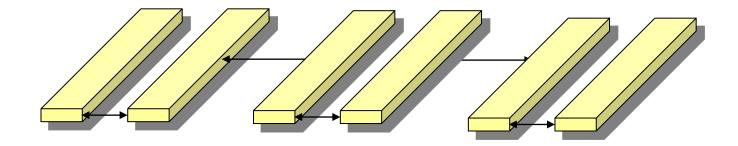

P & N trace skew matching "meandering" is used to balance the skew of the pair, it should be distributed throughout the trace length

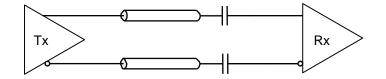

# **AC-Coupling**

- RTG4 requires AC-Coupling for all SERDES applications including PCI Express for link detection

- AC-coupling provides common-mode independence

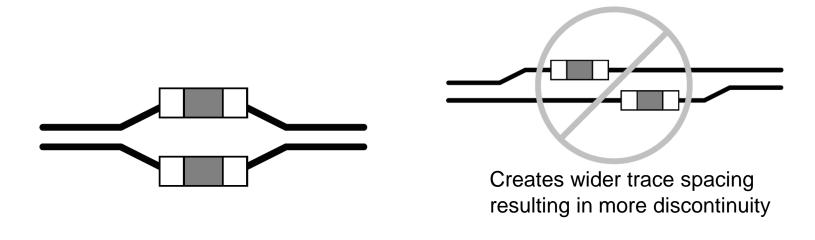

Use symmetrical routing and placement for best performance.

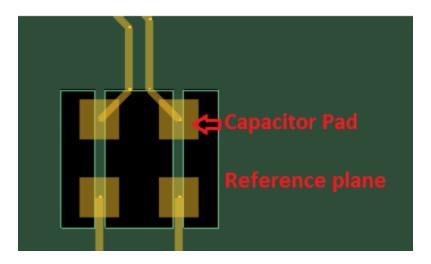

# **AC-Coupling**

- Minimize reflections from the mounting structures with cut-outs in the reference plane

- Clearing of the reference plane underneath the ac-coupling cap produces less discontinuities of the routing path

# SpaceWire: ES/MS to PROTO/Flight Silicon

- RTG4 ES device supports 12 SpaceWire ports

- RTG4 ES Dev board supports **12** SpaceWire ports

- The SpaceWire package pin assignment will be updated in the next silicon revision for PROTO and flight units to support 16 SpaceWire ports

- RTG4 Production Dev board will support 13 SpaceWire ports

- Going from the current silicon revision to the next silicon revision, refer to the pin mapping of the device on the Dev board

<u>SpaceWire Pin Mapping from RTG4 ES/MS Silicon to PROTO/Flight Silicon for RTG4</u> <u>Development Kit</u>

#### **CG1657 Package Pins**

- Two devices are available in Libero SoC Software

- RT4G150\_ES CG1657

- RT4G150 (production) CG1657

- Software generated package pins for RT4G150\_ES are not compatible with pins generated for RT4G150 device

- Due to SpaceWire enhancements

- The following pin mapping tables are provided to help you start designing your board

<u>SpaceWire Pin Mapping from RTG4 ES/MS Silicon to PROTO/Flight Silicon</u>

<u>SpaceWire Pin Mapping from RTG4 ES/MS Silicon to PROTO/Flight Silicon for RTG4</u>

<u>Development Kit</u>

#### **Take-Aways**

- Understand key points of the RTG4 power supplies and requirements

- Recognize the different PCB topologies and features for the memory controllers available with the RTG4

- Awareness of SERDES layout methods needed for PCB first-time success

# **Appendix**

| Name                                                                                                                                 | Operating Voltage                                | Description                                                                                                                                                                                                                                                                                                                           | Name                                                                                                         | Operating Voltage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                                                                                                                                  | 1.2 V                                            | DC core supply voltage. Must always power this pin.                                                                                                                                                                                                                                                                                   | SERDES x Lyz REXT                                                                                            | _                 | External reference resistor $(1.21 \text{ k}\Omega)$ connected to calibrate                                                                                                                                                                                                                                                                                                                                                                        |

| VPP<br>VDDIx<br>where x is the bank number                                                                                           | 3.3 V<br>1.2 V, 1.5 V, 1.8 V,<br>2.5 V, or 3.3 V | Power supply for charge pumps (for normal operation and programming). Must always power this pin.<br>I/O bank supplies for MSIO, MSIOD and DDRIO banks.<br>For MSIO banks: 1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.3 V                                                                                                                          | where,<br>• x refers to 1, 2, 3, 4,<br>PCIE_0 or PCIE_5<br>• yz refers to lanes 0 and<br>1, or lanes 2 and 3 |                   | TX/RX termination value. Each SERDES_x consists of two<br>REXT signals—one for Lane0 and Lane1, and another for<br>Lane2 and Lane3.<br>If the SERDES is not used, it must remain floating (DNC).                                                                                                                                                                                                                                                   |

|                                                                                                                                      |                                                  | For MSIOD banks: 1.2 V, 1.5 V, 1.8 V, 2.5 V<br>For DDRIO banks: 1.2 V, 1.5 V, 1.8 V, 2.5 V<br>For JTAG bank: 1.8 V, 2.5 V, or 3.3 V<br>To power-up the device, all I/O banks must be powered (to exit<br>from power-up-reset state).<br>There is no power-up sequence requirement between VDDI,<br>VPP, and VDD supplies.             | SERDES_VDDI                                                                                                  |                   | Power for SERDES reference clock receiver supply. The supply<br>voltage depends on SERDES reference clock source. Must<br>always power this pin.<br>External differential receiver reference voltage for SERDES<br>Reference Clocks.<br>Reference voltage must be powered with the SERDES_VDDI                                                                                                                                                     |

| VDDPLL                                                                                                                               | 3.3 V                                            | Power for Eight corner PLLs, PLLs in SERDES PCIe/PCS blocks, and FDDR PLL.<br>When in use, the supply must be connected to a common PLL supply (3.3 V) of the corresponding PLL return path (VSS) on-<br>board through an RC filter.<br>When not in use, the supply must be directly connected to 3.3 V (without the filter circuit). |                                                                                                              |                   | supply through voltage divider circuitry.<br>If SERDES reference clock uses an I/O reference standard<br>such as SSTL, HSTL on the board, SERDES_VREF must be<br>connected to SERDES_VDDI through a voltage divider circuit.<br>If SERDES is not used or SERDES reference clock uses a non<br>reference standard such as LVDS, LVCMOS, and LVTTL on the<br>board, SERDES_VREF must be connected to Ground through<br>a 1 k–10 k $\Omega$ resistor. |

| VREF0                                                                                                                                | 0.5 * VDDI                                       | Reference voltage for FDDR signals.                                                                                                                                                                                                                                                                                                   | VSS                                                                                                          | Ground            | Ground pad for core and I/Os. Always connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| VERF9                                                                                                                                |                                                  | Reference voltages must be powered with the appropriate bank<br>supplies through voltage divider circuitry. If I/O banks are used<br>as single-ended I/Os (and FDDR functionalities are not used),<br>VREF0, VREF9 can be left floating (DNC).                                                                                        |                                                                                                              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SERDES_x_Lyz_VDDAIO<br>where,<br>• x refers to 1, 2, 3, 4,<br>PCIE_0 or PCIE_5<br>• yz refers to lanes 0 and<br>1, or lanes 2 and 3  | 1.2 V                                            | TX/RX analog I/O voltage for SERDES lanes. Low voltage<br>power for Lane-y and Lane-z of SERDES_x.<br>If SERDES is not used, it must be connected to 1.2 V                                                                                                                                                                            |                                                                                                              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SERDES_x_Lyz_VDDAPLL<br>where,<br>• x refers to 1, 2, 3, 4,<br>PCIE_0 or PCIE_5<br>• yz refers to lanes 0 and<br>1, or lanes 2 and 3 |                                                  | Analog power for SERDES lanes.<br>If SERDES is used, all SERDES PLL pins must be connected to<br>the appropriate supply (2.5 V) of the corresponding return path<br>on-board (SERDES_x_Lyz_REFRET) through an RC filter.<br>If SERDES is not used, they must connect directly to 2.5 V<br>without the RC filter circuit.              |                                                                                                              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SERDES_x_Lyz_REFRET<br>where,<br>• x refers to 1, 2, 3, 4,<br>PCIE_0 or PCIE_5<br>• yz refers to lanes 0 and<br>1, or lanes 2 and 3  | _                                                | Local on-chip ground return path for SERDES lanes.<br>If SERDES is not used, it must be grounded (VSS).                                                                                                                                                                                                                               |                                                                                                              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Microsemi

SPACE FORUM

# **Thank You**

Power Matters."

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com Microsemi Corporation (MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Power Matters.<sup>TM</sup> 21