Power Matters.<sup>TM</sup>

#### **RTG4 Architecture Details**

Microsemi Space Forum 2015

Minh Nguyen Senior Marketing Manager, Space and Aviation

Microsemi

#### Agenda

- RTG4 Architecture Details

- FPGA Fabric

- Embedded Memories

- DSP Mathblock

- General Purpose IO

- Clock Conditioning Circuit (CCC) and PLL

- SpaceWire Clock Recovery

- SERDES

- FDDR Controller

- System Controller

- Summary of Radiation-Mitigated Features

- RTG4 Architecture, Performance and Power Comparison

- Conclusion

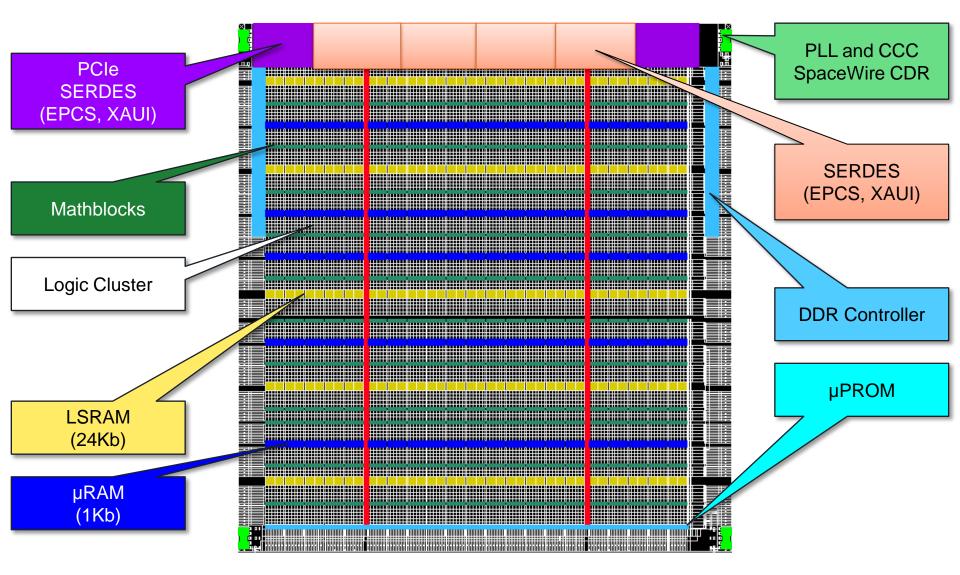

#### **RTG4 Layout Overview**

\sub Microsemi.

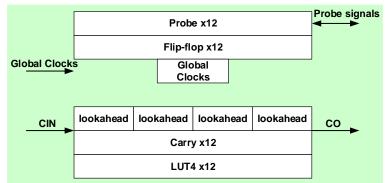

## **FPGA Fabric: Logic Cluster**

- Each Logic Cluster contains 12 Logic Elements

- 12 TMR Flip-flops with probe logic

- $\Rightarrow$  Built-in radiation mitigation

- $\Rightarrow$  Capture logic states for debugging purpose

- 12 LUT4 with fast carry arithmetic logic

- $\Rightarrow$  Efficient routing >95% module utilization

🏷 Microsemi.

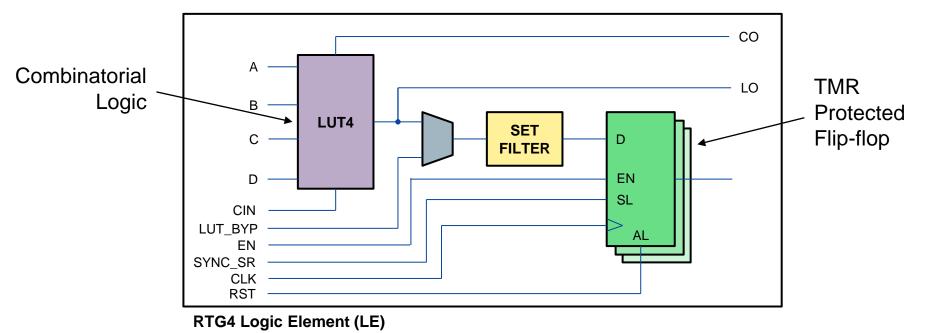

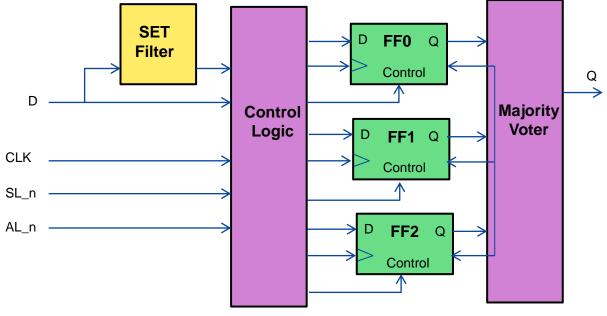

#### **FPGA Fabric: Flip-flops**

- Built-in SET filter can eliminate SET glitches up to 600 ps

- Delay added to data path in SmartTime has been seen to vary from 943 ps to 1.255 ns

- Radiation-hardened Control Logic for clock/reset (synchronous load) and reset/probe (asynchronous load)

- Radiation-hardened asynchronous Majority Voter ensures SEU immunity

- Proprietary triple-module redundancy (TMR) for maximum radiation mitigation while maintaining high performance

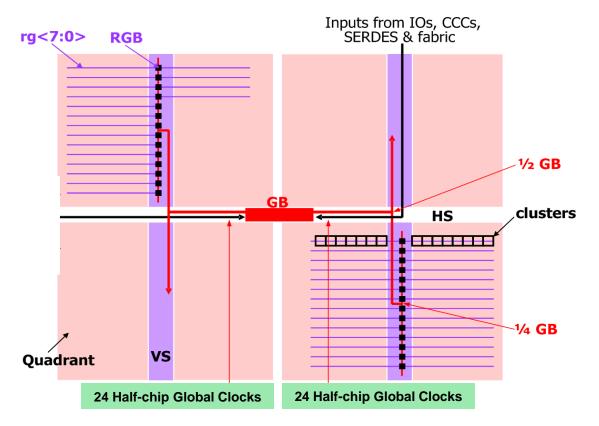

#### **Global Clock**

- 24 full-chip Global Clocks or 48 half-chip Global Clocks

- Complete radiation hardening by triple-redundant clock paths

- Global Clocks can come directly from:

- Output of CCC/PLL

- Global Buffer (GB)

- Dedicated Global I/Os

#### **Embedded Memories: SRAM**

- Radiation Tolerance:

- Resistant to multi-bit upset

- Built-in optional Error Detection and Correction (EDAC) without background scrubbing

- Shortened Hamming code with single error correct, double error detect (SECDED)

| Data Port                                   | Width (bits) |    |

|---------------------------------------------|--------------|----|

| User data width                             | 18           | 36 |

| User data width with shortened Hamming code | 24           | 48 |

- Large SRAM (LSRAM) Up to 24 Kbit

- Dual-port and two-port options

- Supported bit widths: x36, x18, x12 and x9

- Built-in EDAC available for x36 and x18

- Micro SRAM (uSRAM) Up to 1.5 Kbit

- Three-port SRAM

- Supported bit widths: x18, x12 and x9

- Built-in EDAC available for x18

- LSRAM and uSRAM contents can be pre-loaded from uPROM at power-on

😳 Microsemi.

#### **Embedded Memories: uPROM**

- Non-volatile memory based on FPGA configuration cell

- Configuration upset immune

- TID >= 100KRad

- Up to 374 Kbits storage for DSP coefficients

- Initialize RAMs and registers from uPROM

- Power-on initialization

- Modification of coefficients during normal operation

- RAM scrubbing

- Read performance of 50 MHz x 32-bits

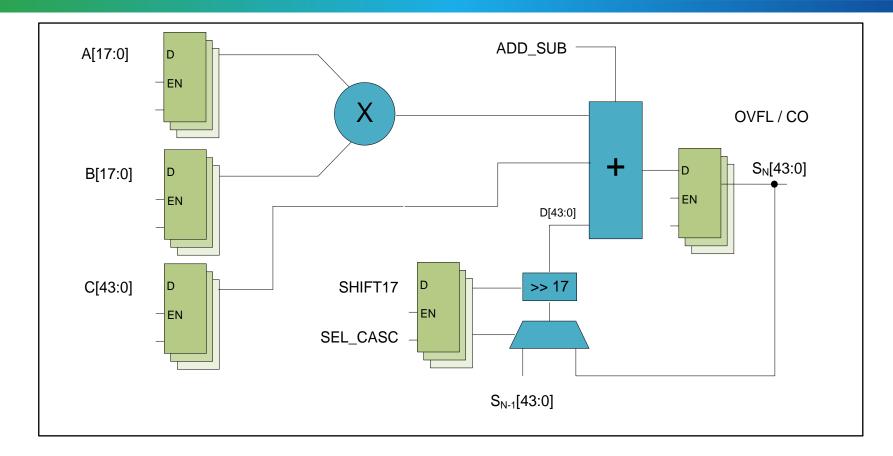

#### **DSP Mathblock**

- 18 x 18 multiplier with advanced accumulate

- High performance for signal processing throughput

- Optional SEU-protected registers on inputs and outputs (including C input)

#### \sub Microsemi.

#### **General Purpose IO**

- Three IO types: MSIO up to 3.3V, MSIOD and DDRIO up to 2.5V

- Programmable Input Delay available

- Cold Sparing supported with all IO supplies powered while the core supply is tied to ground

- Radiation Tolerance:

- IO Registers have the same built-in TMR structure as the fabric flip-flops

- MSIO and MSIOD input buffers are triplicated to be protected from SET

| IO Standards      |                          |                      | IO Types              |                       |  |  |  |

|-------------------|--------------------------|----------------------|-----------------------|-----------------------|--|--|--|

|                   |                          | MSIO<br>(Up to 3.3V) | MSIOD<br>(Up to 2.5V) | DDRIO<br>(Up to 2.5V) |  |  |  |

|                   | PCI (3.3V)               | Yes                  | No                    | No                    |  |  |  |

| Single-ended      | LVTTL / LVCMOS (3.3V)    | Yes                  | No                    | No                    |  |  |  |

|                   | LVCMOS (1.2V to 2.5V)    | Yes                  | Yes                   | Yes                   |  |  |  |

|                   | HSTL 1.5V (Class I)      | Yes                  | Yes                   | Yes                   |  |  |  |

|                   | HSTL 1.5V (Class II)     | No                   | No                    | Yes                   |  |  |  |

|                   | HSTL 1.8V                | Yes                  | Yes                   | Yes                   |  |  |  |

| Voltage Reference | SSTL 2.5V (Class I & II) | Yes                  | Yes                   | Yes                   |  |  |  |

|                   | SSTL 1.8V (Class I & II) | Yes                  | Yes                   | Yes                   |  |  |  |

|                   | SDRAM 3.3V               | Yes                  | No                    | No                    |  |  |  |

|                   | LVDS                     | Yes                  | Yes                   | No                    |  |  |  |

|                   | RSDS                     | Yes                  | Yes                   | No                    |  |  |  |

| True Differential | Mini LVDS                | Yes                  | Yes                   | No                    |  |  |  |

|                   | LVPECL (input only)      | Yes                  | No                    | No                    |  |  |  |

|                   | MLVDS                    | Yes                  | Yes                   | No                    |  |  |  |

|                   |                          |                      |                       |                       |  |  |  |

😳 Microsemi.

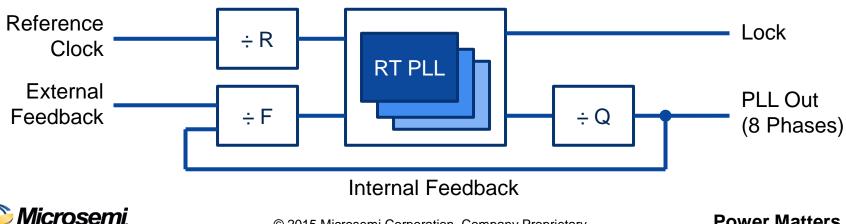

### **CCC** and **PLL**

- Radiation-Tolerant PLLs are used in CCC, SERDES and DDR blocks

- PLL output frequency up to 400 MHz

- Two CCC/PLL per corner. Two SpaceWire CDR circuits per CCC

- Triple module redundant (TMR) PLL in internal feedback mode

- Reference clock is fed back to all 3 sub-PLLs independently

- Sub-PLL is SEL immune

- Single PLL in external feedback mode

- PLL output travels through clock network and is fed back to PLL

- Common mode used for clock network delay compensation

- Only 1 sub-PLL is enabled in this mode

- Sub-PLL is SEL immune

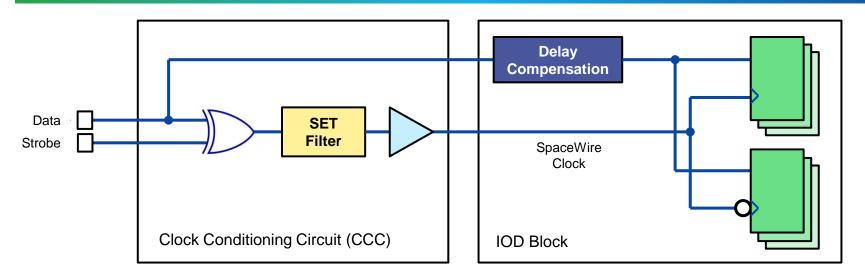

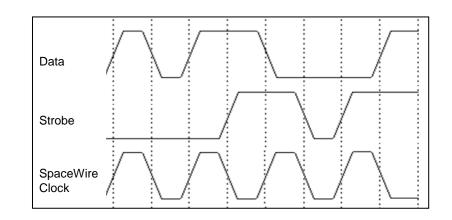

### **SpaceWire Clock Recovery**

- SpaceWire interface used for command-and-control and data

- Data and Strobe are XORed to recover SpaceWire clock

- Hardwired and SET protected

- Delay compensation available to align data and SpaceWire clock

- 16 SpaceWire Clock Recovery circuits on each RTG4

#### **Unique Microsemi RTG4 Feature**

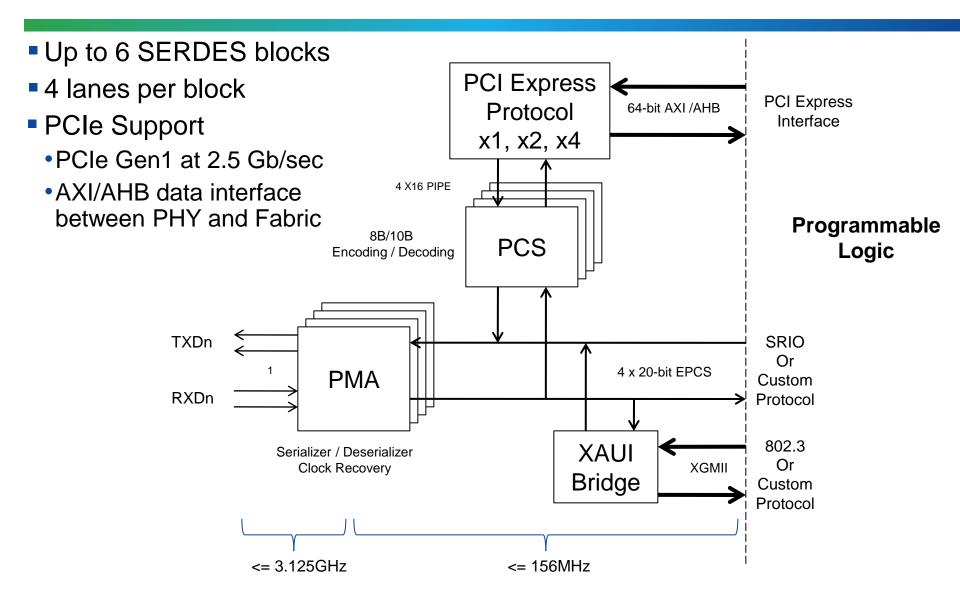

#### 3.125 Gb/sec SERDES

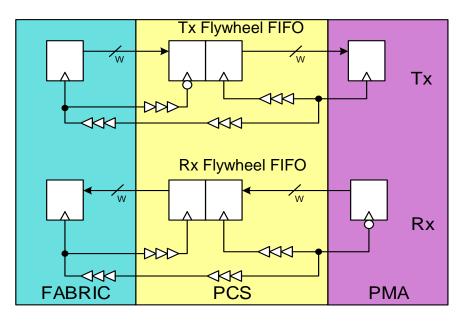

#### SERDES (Cont.): EPCS and XAUI

- EPCS and XAUI modes are improved from commercial SERDES (For example: SmartFusion2 and Igloo2)

- A flywheel FIFO improves read timing to the FPGA fabric and provides clock compensation to transfer Rx data to the Tx clock domain in the FPGA fabric

- Dedicated routing from SERDES clocks to the global clock network

- ⇒Efficient routing and high performance up to 3.125 Gb/sec

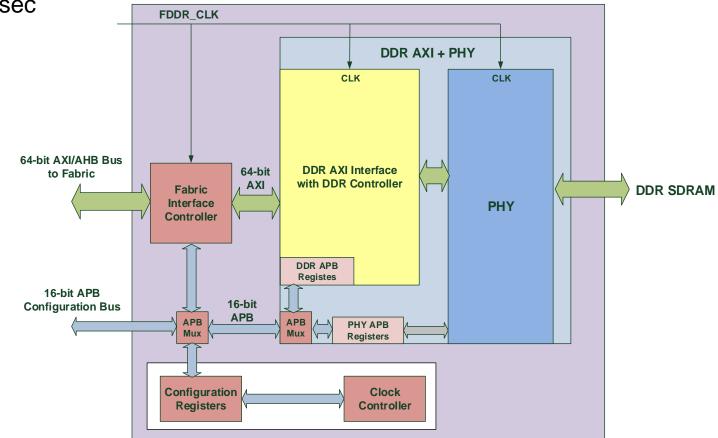

#### **FDDR Controller**

- 2 FDDR Controllers support:

- DDR2, DDR3 and LPDDR1

- 8/16/32 bit data bus. Built-in EDAC for x16 and x32

- Up to 667 Mb/sec

#### **System Controller**

- System Controller manage:

- Programming through JTAG and SPI Slave interface

- Power-On Reset (POR) Generator

- System Controller Suspend Mode protects device from unintended configuration due to radiation upsets

- JTAG\_TRSTB must be held Low and this mode must be set in Libero SoC software

- To exit this mode, hold JTAG\_TRSTB High and reprogram the device with System Controller Suspend Mode turned off in software

- System Controller Suspend Mode control bit is stored in a flash cell and immune from configuration upset

#### **Summary of Radiation-Mitigated Features**

|                                |            | Radiation Mitigation    |                                        |                         |                                              |  |  |  |

|--------------------------------|------------|-------------------------|----------------------------------------|-------------------------|----------------------------------------------|--|--|--|

| Features                       | SEL Immune | SEU Immune<br>By Design | SEU Mitigated<br>with Optional<br>EDAC | SET Immune<br>by Design | SET Mitigated<br>with Optional<br>SET Filter |  |  |  |

| Configuration Flash Memory     | YES        | YES                     |                                        |                         |                                              |  |  |  |

| FPGA Fabric                    |            |                         |                                        |                         |                                              |  |  |  |

| Combinatorial Logic            | YES        |                         |                                        |                         | YES                                          |  |  |  |

| Flip-flop                      | YES        | YES                     |                                        |                         |                                              |  |  |  |

| Global Clock and Reset         | YES        |                         |                                        | YES                     |                                              |  |  |  |

| LSRAM and uSRAM                |            |                         |                                        |                         |                                              |  |  |  |

| SRAM Data                      | YES        |                         | YES                                    |                         |                                              |  |  |  |

| SRAM Control                   | YES        |                         |                                        | YES                     |                                              |  |  |  |

| DSP Mathblock                  | YES        | YES                     |                                        |                         | YES                                          |  |  |  |

| MSIO/MSIOD Input Buffer        | YES        |                         |                                        | YES                     |                                              |  |  |  |

| PLL/CCC Internal Feedback      | YES        |                         |                                        | YES                     |                                              |  |  |  |

| PLL/CCC External Feedback      | YES        |                         |                                        |                         |                                              |  |  |  |

| SERDES                         |            |                         |                                        |                         |                                              |  |  |  |

| SERDES Control (Register Maps) | YES        | YES                     |                                        | YES                     |                                              |  |  |  |

| FDDR                           |            |                         |                                        |                         |                                              |  |  |  |

| FDDR Control (Register Maps)   | YES        | YES                     |                                        | YES                     |                                              |  |  |  |

| 50-MHz RC Oscillator           | YES        |                         |                                        | YES                     |                                              |  |  |  |

#### **RTG4 Architecture, Performance and Power Comparison**

© 2015 Microsemi Corporation. Company Proprietary.

Power Matters.<sup>TM</sup> 18

### **RTG4 vs. RT/RH SRAM FPGAs**

|                        | RT4G150         | Xilinx<br>XQR5VFX130<br>(SIRF) | Xilinx<br>XQR4VSX55     | Xilinx<br>XQR4VFX60     | Xilinx<br>XQR4VFX140     | Xilinx<br>XQR4VLX200     | Atmel<br>ATFS450 |

|------------------------|-----------------|--------------------------------|-------------------------|-------------------------|--------------------------|--------------------------|------------------|

| Non-TMR FF<br>TMR FF   | 151,824         | 81,920                         | 55,296<br><i>18,432</i> | 56,880<br><i>18,960</i> | 142,128<br><i>47,476</i> | 200,448<br><i>66,816</i> | 23,104           |

| LUT4<br>LUT6           | 151,824         | <i>106,496</i><br>81,920       | 55,296                  | 56,880                  | 142,128                  | 200,448                  | 46,208           |

| 18x18 MAC<br>24x18 MAC | 462             | <i>448</i><br>320              | 512                     | 128                     | 192                      | 96                       | None             |

| SRAM (Mbits)           | 5.2             | 10.7                           | 5.7                     | 4.1                     | 9.9                      | 6                        | 0.18             |

| SERDES Lanes           | 24              | 18                             | None                    | None                    | None                     | None                     | None             |

| In-orbit<br>Reconfig   | To be<br>tested | Unlimited                      | Unlimited               | Unlimited               | Unlimited                | Unlimited                | Unlimited        |

- Note that *italic data* were converted to compare with RTG4

- Assumptions:

- 1 SIRF LUT6 = 1.3 x RTG4 LUT4

- 1 SIRF Mathblocks = 1.4 x RTG4 Mathblocks

## ⇒ RTG4 is the largest RT FPGA with the most TMR flip-flops, combinatorial logic and SERDES

#### **RTG4 vs. SIRF**

| Resources                  | Microsemi<br>RT4G150 | Xilinx<br>V5QV SIRF |

|----------------------------|----------------------|---------------------|

| LUT4 + TMR FF              | 151,824              |                     |

| LUT6 + TMR FF              | -                    | 81,920              |

| User IO (non-SERDES)       | 720                  | 836                 |

| RAM Mbits                  | 5.2                  | 10.7                |

| UPROM Kbits                | 374                  | -                   |

| 18x18 MAC Blocks           | 462                  | -                   |

| 25x18 MAC Blocks           | -                    | 320                 |

| SERDES lanes               | 24                   | 18                  |

| DDR2/3 SDRAM<br>Controller | 2x32                 | -                   |

| Globals                    | 24                   | 32                  |

| PLLs (Rad Tolerant)        | 8                    | 6                   |

| SpaceWire CDR Circuits     | 16                   | -                   |

| PCI Express Endpoints      | 2                    | 3                   |

| CG1657                     | $\checkmark$         |                     |

| CG1752                     |                      | $\checkmark$        |

| • 46% More | Flip-Flops |

|------------|------------|

|------------|------------|

- 30% More Combinatorial Logic

- 6 More SERDES Lanes

- 16 SpaceWire CDR Circuits

#### **RTG4 vs. SIRF Performance Comparison**

- Performance benchmark was done to understand RTG4 performance with respect to SIRF using a wide range of benchmark designs

- Benchmark designs:

- 106 internal benchmark designs:

- Standard designs typically used for performance benchmarking, including customer designs, IP cores, and basic functions

- Advanced designs with high demand on long routing tracks and more complex functions

- DSP designs optimized for our technology

- 1 real world design:

- Channelized application (up to 24 channels) consuming a significant amount of DSP, logic and RAM

#### **Internal Designs: Performance Result**

| SW Settings      |            | SIRF               |  | RTG        | 64        |       |  |

|------------------|------------|--------------------|--|------------|-----------|-------|--|

| Design Tool      | ISE 13.2   |                    |  | Libero SoC |           |       |  |

| Synthesis Tool   | Synplify   |                    |  | Synplify   |           |       |  |

| Operating Cond.  | MIL, Wors  | t voltage          |  | MIL, Worst | voltage   |       |  |

| Device & Speed   | Only 1 dev | vice               |  | RT4G150    |           |       |  |

| Speed Grade      | Only 1 spe | Only 1 speed grade |  |            | -1        |       |  |

| TID (Krad)       | 0          | 0                  |  |            | 0         |       |  |

| SET Filter Value | ~ 2.1 ns   | ~ 2.1 ns           |  |            |           |       |  |

| Geomean          | RTG4       | RTG4 SIRF RTG4     |  |            | SIRF wit  | n SET |  |

| All Designs      | 1.00 1.02  |                    |  | 0.87 0.7   |           | ļ     |  |

| Adv. Designs     | 1.00       | 1.00 0.56          |  |            | 0.93 0.49 |       |  |

| DSP Designs      | 1.00       | 0.75               |  | 0.85 0.59  |           | )     |  |

$\Rightarrow$ RTG4 is 15% faster than SIRF with SET filter  $\Rightarrow$ RTG4 is significantly faster than SIRF in Advanced and DSP designs

🏷 Microsemi.

#### **Real World Design: Performance Result**

- Resource utilization:

- RTG4 could integrate up to 22 channels

- SIRF only integrated 16 channels and already 99% full

- The 22-channel design had 22.4% more logic than 16-channel design

- The 24-channel design did not fit in either part

#### Performance:

| Clock Domain                | RTG4  | SIRF  | Notes                          |

|-----------------------------|-------|-------|--------------------------------|

| External Clock (MHz)        | 150.6 | 115.2 | Long critical net delay 7.6 ns |

| External System Clock (MHz) | 37.1  | 42.4  |                                |

| Half Sample Clock (MHz)     | 168.9 | 103.5 | Long critical net delay 8.2 ns |

| Global Clock Bus (Mhz)      | 50.6  | 52.4  |                                |

# ⇒For large design, RTG4 maintains comparable performance while having more resources

#### **RTG4 vs. SIRF Power Comparison**

- Goal to compare RTG4 and SIRF power consumption in a highly utilized design switching at 175 MHz using:

- RTG4 Power Calculator v2c, available on RTG4 website

- SIRF Power Calculator v14.3.2, available on Xilinx website

- Use Model in RTG4

- 70% LUT4, 53% flip-flops

- 96% LSRAM blocks

- 100% DSP Mathblocks

- 18 SERDES lanes, 1 PCle

| Condition | Static 25C | Static 85C | Static 125C | Total 25C | Total 85C | Total 125C |

|-----------|------------|------------|-------------|-----------|-----------|------------|

| Process   | Typical    | Typical    | Typical     | Typical   | Typical   | Typical    |

| RTG4 (W)  | 0.14       | 0.49       | 1.26        | 11.416    | 11.766    | 12.536     |

| SIRF (W)  | 1.89       | 3.932      | 7.173       | 12.671    | 14.712    | 17.954     |

⇒RTG4 has lower total power. RTG4 has significant advantage in Static power, while SIRF has lower Dynamic due to 1V core.

#### Conclusion

- RTG4 comprehensive and robust architecture offers a complete solution for high-speed signal processing applications

- True Radiation-tolerant FPGAs with built-in mitigation throughout the device

- Significant improvement in performance while maintaining low power

Microsemi

SPACE FORUM

## **Thank You**

Power Matters."

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com Microsemi Corporation (MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Power Matters.<sup>TM</sup> 26