# PD70211 Datasheet PD Controller with Switching Regulator for AF/AT/UPOE /HDBaseT/4-pair PoE Applications

September 2019

## **Contents**

| 1 | Revis   | sion History                                 | 1    |

|---|---------|----------------------------------------------|------|

|   | 1.1     | Revision 2.0                                 | 1    |

|   | 1.2     | Revision 1.4                                 | 1    |

|   | 1.3     | Revision 1.31                                | 1    |

|   | 1.4     | Revision 1.3                                 | 1    |

|   | 1.5     | Revision 1.2                                 | 1    |

|   | 1.6     | Revision 1.1                                 | 1    |

|   | 1.7     | Revision 1.0                                 | 1    |

|   | 1.8     | Revision 0.6                                 | 1    |

|   | 1.9     | Revision 0.3                                 | 1    |

|   | 1.10    | Revision 0.2                                 | 2    |

|   | 1.11    | Revision 0.1                                 | 2    |

| _ | Du a al | out Overview                                 | 2    |

| 2 |         | uct OverviewFeatures                         |      |

|   |         | Applications                                 |      |

|   |         |                                              |      |

| 3 | Func    | tional Descriptions                          | 5    |

| 4 | Elect   | rical Specifications                         | 7    |

|   |         | Absolute Maximum Ratings                     |      |

|   | 4.2     | Operating Ratings                            | 8    |

|   | 4.3     | Thermal Properties                           | 8    |

|   | 4.4     | Electrical Characteristics                   | 9    |

|   | 4       | .4.1 Thermal Protection                      | . 14 |

|   | 4       | .4.2 Wall Adapter Mode                       | . 14 |

| 5 | Pin C   | onfiguration                                 | 16   |

| _ | Da al.  |                                              | 24   |

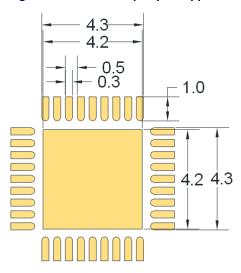

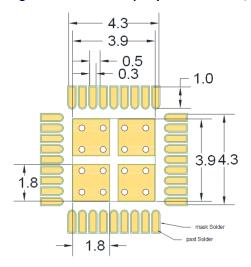

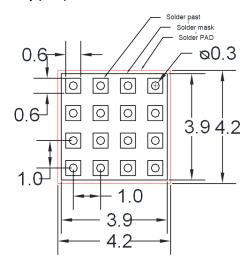

| 6 |         | age Specifications                           |      |

|   | 0.1     | Neconinenced FCB Layout                      |      |

| 7 |         | cations Information                          |      |

|   | 7.1     | Peripheral Devices                           |      |

|   | 7.2     | Setting Switching Frequency                  | 24   |

|   | 7.3     | Setting Soft-Start                           | 25   |

|   | 7.4     | Setting Pulse-skip Mode Threshold            | 25   |

|   | 7.5     | Setting UVLO/Hysteresis Thresholds           | 26   |

|   | 7.6     | Setting the Voltage Divider for Output Rails | 26   |

|   | 7.7     | Selecting the Sense Resistor                 | . 27 |

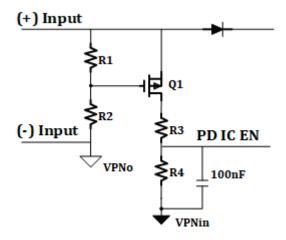

|   | 7.8     | Operation with an External DC Source         | 28   |

## 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

#### 1.1 **Revision 2.0**

Revision 2.0 was published in September 2019. The following is the summary of changes.

- QFN package diagram was re-drawn.

- A typo in pin name was corrected in Applications Information section.

- The column 'note' was removed from Ordering Information table.

- The document was converted to Microsemi formatting standards.

#### 1.2 **Revision 1.4**

Revision 1.4 was published in July 2017. In this revision, marking and MSL3 information were updated.

#### 1.3 Revision 1.31

Revision 1.31 was published in July 2016. In this revision, removed 'PD' in IC marking description, removed the name of the front-end die (PD70210A) in functional block diagram, and updated revision number and date in the footer.

#### 1.4 **Revision 1.3**

Revision 1.3 was published in October 2015. In this revision, fixed Vaux pin description, added UVLO\_ON missing information and PD70224 was changed to PD70211 in figures 9, 10, and 11.

#### 1.5 Revision 1.2

Revision 1.2 was published in June 2015. Updated typo in part marking definition.

#### 1.6 **Revision 1.1**

Revision 1.1 was published in January 2015. In revision 1.5 of this document, PCB footprint recommendation were added.

#### 1.7 **Revision 1.0**

Revision 1.0 was published in August 2014. In revision 1.0 of this document, frequency setting information was added.

#### 1.8 **Revision 0.6**

Revision 0.6 was published in July 2014. In revision 0.6 of this document, flags maximum voltage was reduced and WA\_EN information was added.

#### 1.9 Revision 0.3

Revision 0.3 was published in March 2013. In revision 0.3 of this document, general updates were made.

## 1.10 Revision 0.2

Revision 0.2 was published in March 2012. In revision 1.1 of this document, minor edits were made to Class Values.

## 1.11 **Revision 0.1**

Revision 0.1 was published in February 2012. It was the first publication of this document.

## 2 Product Overview

Microsemi's PD70211 is an advanced PD Interface IC with integrated switching (PWM) regulator control for Powered Devices in PoE applications. It supports IEEE802.3af, IEEE802at, HDBaseT, and general 2/4-pair configurations.

The PD70211 front-end includes an advanced classification block that supports 2, 3, 4, and 6 event classification. Using the SUPP\_Sx pins, it also identifies which of the four pairs of the cable actually receives power and generates appropriate flags.

The IC features an internal bleeder for discharging the input capacitor of the DC/DC converter rapidly to ensure fast re-detection and port power-up, in case of sudden removal and re-insertion of the Ethernet cable into the RJ-45. The advanced PWM current-mode section supports synchronous Flyback and Active Clamp Forward topologies, as well as Buck, Boost, and so on.

#### 2.1 Features

The PD70211 device has the following key features.

- Supports IEEE802.3af/at, HDBaseT, and other 2-pair/4-pair configurations

- Wall adapter support (Rear Aux method)

- PD detection and programmable classification

- 2,3,4, and 6 event classification

- Integrated 0.3 Ω isolating (series-pass) FET

- Inrush current limiting

- Less than 10 μA offset current during detection

- Advanced PWM section

- Lead-free MLPQ-36 (6 mm × 6 mm) package

## 2.2 Applications

The following are the applications of the PD70211 device.

- HDBaseT up to 95 Watts

- IEEE802.3af and IEEE802at

- Power forwarding

- Indoor and outdoor PoE

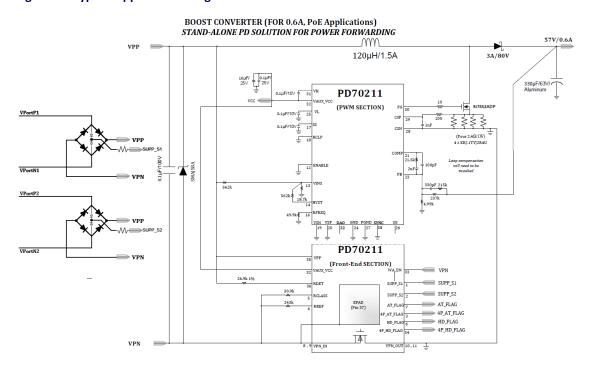

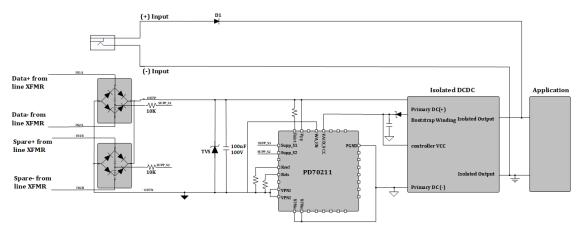

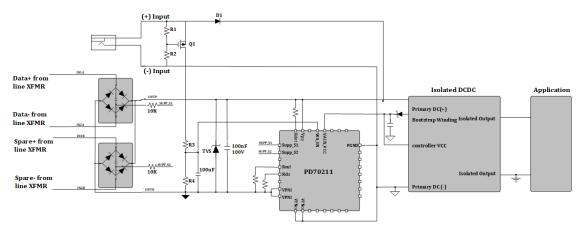

Figure 1 • Typical Applications Diagram

**Note:** Please consult Microchip Technology for the latest reference design.

# **3** Functional Descriptions

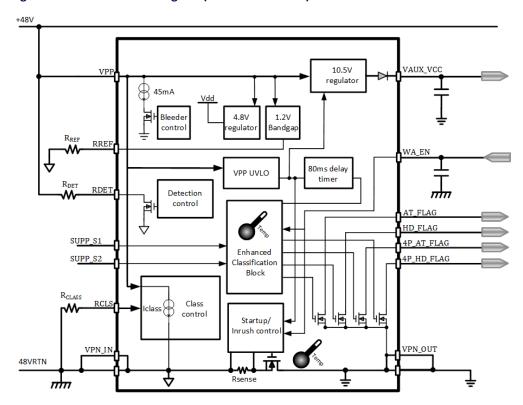

The following figure shows the functional blocks of the PD70211 device.

Figure 2 • PD70211 Block Diagram (Front-end Section)

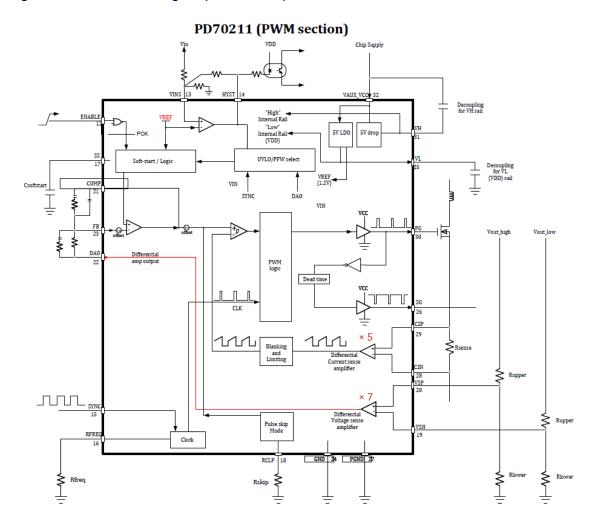

Figure 3 • PD70211 Block Diagram (PWM Section)

# 4 Electrical Specifications

The following section describes the electrical specifications of the PD70211 device.

## 4.1 Absolute Maximum Ratings

Performance is not necessarily guaranteed over this entire range. These are maximum stress ratings only. Exceeding these ratings, even momentarily, can cause immediate damage, or negatively impact long-term operating reliability. Voltages are with respect to IC ground (VPN\_IN).

**Table 1 • Absolute Maximum Ratings**

|                            |                  | Min  | Max                    | Units |

|----------------------------|------------------|------|------------------------|-------|

| VPP, VPN_OUT, RDET         |                  | -0.3 | 74                     | V     |

| AT_FLAG, HD_FLAG, 4P_AT_   | FLAG, 4P_HD_FLAG | -0.3 | 20                     | V     |

| SUPP_S1, SUPP_S2           |                  | 0    | V <sub>VPP</sub> + 1.5 | V     |

| RREF, RCLS, WA_EN          |                  | -0.3 | 5                      | V     |

| VAUX_VCC                   |                  | -0.3 | 20                     | V     |

| PG, SG                     |                  | -0.3 | 20                     | V     |

| VL                         |                  | -0.3 | 6                      | V     |

| VH (with respect to VAUX_V | CC)              | 0.3  | -6                     | V     |

| ENABLE                     |                  |      |                        |       |

| All other pins             |                  | -0.3 | VL+0.3                 | V     |

| Junction temperature       |                  | -40  | 150                    | °C    |

| Lead soldering temperature | (40 s, reflow)   |      | 260                    | °C    |

| Storage temperature, MSL3  |                  | -65  | 150                    | °C    |

| ESD rating                 | нвм              |      | ±1.5*                  | kV    |

|                            | ММ               |      | ±50                    | V     |

|                            | CDM              |      | ±500                   | V     |

<sup>\*</sup>Note: Pins VPP, VAUX/VCC, and RREF pass ±1 kV HBM only.

## 4.2 Operating Ratings

Performance is generally guaranteed over this range as detailed in the following front-end section Electrical Characteristics. Voltages are with respect to IC ground (VPN\_IN).

**Table 2 • Operating Ratings (Front-end Section)**

| Parameter            | Min  | Max  | Units |

|----------------------|------|------|-------|

| VPP                  | 0    | 57   | V     |

| Ambient temperature* | -40  | 85   | °C    |

| Detection range      | 1.1  | 10.1 | V     |

| Mark event range     | 4.9  | 10.1 | V     |

| Class event range    | 13.7 | 20.9 | V     |

<sup>\*</sup>The corresponding maximum operating junction temperature is 125 °C.

Performance is generally guaranteed over this range as detailed in the following PWM section Electrical Characteristics. Voltages are with respect to IC ground.

**Table 3 • Operating Ratings (PWM Section)**

| Parameter                                               | Min | Max  | Units |

|---------------------------------------------------------|-----|------|-------|

| VCC                                                     | 7.8 | 20   | V     |

| Fsw (adjustable frequency range)                        | 100 | 500  | kHz   |

| Maximum duty cycle                                      |     | 44.5 | %     |

| f <sub>sw_synch</sub> (synchronization frequency range) | 200 | 1000 | kHz   |

## 4.3 Thermal Properties

The following table lists the thermal specifications for the PD70211 device.

**Table 4 • Thermal Properties**

| Thermal Resistance | Min | Тур  | Max | Units |

|--------------------|-----|------|-----|-------|

| θја                |     | 22.3 |     | °C/W  |

| Өль                |     | 3    |     | °C/W  |

| θις                |     | 4    |     | °C/W  |

**Note:** The  $\theta_{Jx}$  numbers assume no forced airflow. Junction temperature is calculated using  $T_J = T_A + (P_D \times q_{JA})$ . In particular,  $\theta_{JA}$  is a function of the PCB construction. The stated number above is for a four-layer board in accordance with JESD-51 (JEDEC).

## 4.4 Electrical Characteristics

This section describes the electrical characteristics of the front-end and PWM sections, thermal protection mechanism against excessive internal temperature, and wall adapter mode functionality.

#### **Electrical Characteristics of Front-end Section**

Unless otherwise specified under conditions, the Min and Max ratings stated in the following table apply over the entire specified operating ratings of the PD70211 device. Typical values are determined either by design or by production testing at 25 °C ambient temperature. Voltages are with respect to IC ground (VPN\_IN).

**Table 5 • Typical Electrical Performance**

| Symbol                | Parameter                                      | Conditions                                   | Min  | Тур  | Max  | Units |

|-----------------------|------------------------------------------------|----------------------------------------------|------|------|------|-------|

| Input voltage         | 2                                              |                                              |      |      |      |       |

| lin                   | IC input current with Iclass off               | VPP = 55 V                                   |      | 1    | 3    | mA    |

| Detection ph          | nase                                           |                                              |      |      |      |       |

| VDET                  | Detection range                                |                                              | 1.1  |      | 10.1 | V     |

| R <sub>DET_ТН</sub>   | R <sub>DET</sub> disconnect<br>threshold       |                                              | 10.1 |      | 12.8 | V     |

| Rds_det_on            | On-resistance of internal FET during detection |                                              |      |      | 50   | Ω     |

| Rds_det_off           | Off-resistance of internal FET after detection |                                              | 2    |      |      | МΩ    |

| OFFSET_DET            | Input offset current                           | 1.1 V ≤ VPP ≤ 10.1 V, T <sub>J</sub> ≤ 85 °C |      |      | 5    | μΑ    |

| V <sub>R_DET_ON</sub> | Threshold when VPP goes low                    |                                              | 2.8  | 3.0  | 4.85 | V     |

| Classification        | n phase                                        |                                              |      |      |      |       |

| Vcls_on               | Classification sink turn-<br>on threshold      |                                              | 11.4 |      | 13.7 | V     |

| Vcls_off              | Classification sink turn-<br>off threshold     |                                              | 20.9 |      | 23.9 | V     |

| VHYS_CLS_ON           | Hysteresis of V <sub>CLS_ON</sub> threshold    |                                              |      | 1    |      | V     |

| Vmark_th              | Mark detection threshold (VPP falling)         |                                              | 10.1 |      | 11.4 | V     |

| <b>I</b> MARK         | Current sink in the mark event region          |                                              | 0.25 |      | 4    | mA    |

| Iclass_clim           | Current limit of class current                 |                                              | 50   | 68   | 80   | mA    |

| Iclass                | Classification current                         | R <sub>CLASS</sub> = not present (Class 0)   |      |      | 3    | mA    |

|                       | sink                                           | R <sub>CLASS</sub> = 133 $\Omega$ (Class 1)  | 9.5  | 10.5 | 11.5 | _     |

|                       |                                                | R <sub>CLASS</sub> = $69.8 \Omega$ (Class 2) | 17.5 | 18.5 | 19.5 | _     |

| Symbol               | Parameter                                                    | Conditions                                                                       | Min  | Тур  | Max  | Units        |

|----------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|--------------|

|                      |                                                              | R <sub>CLASS</sub> = $45.3 \Omega$ (Class 3)                                     | 26.5 | 28.0 | 29.5 |              |

|                      |                                                              | R <sub>CLASS</sub> = $30.9 \Omega$ (Class 4)                                     | 38.0 | 40.0 | 42.0 | <del>_</del> |

| Isolation FET        | •                                                            |                                                                                  |      |      |      |              |

| Roson                | On resistence                                                | Total resistance between VPN_IN to VPN_OUT;  ILDAD < 600 mA, -40 °C < TA < 85 °C |      |      | 0.3  | Ω            |

| Iclim_inrush         | Inrush current limit                                         |                                                                                  | 105  | 240  | 325  | mA           |

| ОСР                  | Overcurrent protection                                       |                                                                                  | 2.2  |      |      | Α            |

| ILOAD                | Continuous operation load                                    |                                                                                  |      |      | 2    | A            |

| Undervoltage         | e lockout                                                    |                                                                                  |      |      |      |              |

| UVLOon               | Threshold that marks start of inrush phase                   |                                                                                  | 36   |      | 42   | V            |

| UVLOOFF              | Threshold where pass-<br>FET turns off as VPP<br>collapses   |                                                                                  | 30.5 |      | 34.5 | V            |

| DC-DC input          | cap discharger                                               |                                                                                  |      |      |      |              |

| ICAP_DIS             | Discharge current                                            | 7 V ≤ VPP ≤ 30 V                                                                 | 22.8 |      | 60   | mA           |

| tdis                 | Discharge time                                               | $C_{DC_DC} \le 264 \mu F$ (by design, not tested)                                |      |      | 500  | ms           |

| timer <sub>dis</sub> | Discharge timer                                              | Time for which discharge circuit is activated                                    | 430  |      |      | ms           |

| References,          | rails, and logic                                             |                                                                                  |      |      |      |              |

| Vaux                 | Auxiliary voltage                                            | 0 mA < I <sub>AUX</sub> < 4 mA                                                   | 9.8  | 10.5 | 12.0 | V            |

| laux                 | Maximum continuous current from V <sub>AUX</sub>             |                                                                                  | 4    |      |      | mA           |

| laux_clim            | Auxiliary current limit                                      |                                                                                  | 10   |      | 32   | mA           |

| VREF                 | Bandgap reference voltage                                    |                                                                                  | 1.17 | 1.2  | 1.23 | V            |

| tflag_lo             | Low level flag                                               | For AT_FLAG, HD_FLAG,  4P_AT_FLAG, 4P_HD_FLAG,  IFLAG = 3 mA                     |      |      | 0.4  | V            |

| IFLAG                | Flag current driving capability                              | For AT_FLAG, HD_FLAG,<br>4P_AT_FLAG, 4P_HD_FLAG                                  | 5    |      |      | mA           |

| <b>T</b> FLAG        | Delay timer between<br>start of inrush and flags<br>declared | For AT_FLAG, HD_FLAG,<br>4P_AT_FLAG, 4P_HD_FLAG                                  | 80   |      |      | ms           |

| Vsupp_hi             | SUPP_Sx high voltage threshold                               | For SUPP_S1 and SUPP_S2                                                          | 25   |      | 35   | V            |

| Wall adapter         | ·                                                            |                                                                                  |      |      |      |              |

| Vін                  | Input high logic                                             |                                                                                  | 2.4  |      |      | V            |

|                      |                                                              |                                                                                  |      |      |      |              |

Table 6 • Truth Table for Status of Flags

| Number of Fingers "N" (N-Event classification) | SUPP_S1  | SUPP_S2    | AT_FLAG | HD_FLAG | 4P_AT_FLAG | 4P_HD_FLAG |

|------------------------------------------------|----------|------------|---------|---------|------------|------------|

| 1                                              | Х        | X          | Hi Z    | Hi Z    | Hi Z       | Hi Z       |

| 2                                              | Н        | L          | 0 V     | Hi Z    | Hi Z       | Hi Z       |

| 2                                              | L        | Н          | 0 V     | Hi Z    | Hi Z       | Hi Z       |

| 2                                              | Н        | Н          | 0 V     | Hi Z    | 0 V        | Hi Z       |

| 3                                              | L        | Н          | 0 V     | 0 V     | Hi Z       | Hi Z       |

| 3                                              | Н        | L          | 0 V     | 0 V     | Hi Z       | Hi Z       |

| 3                                              | Н        | Н          | 0 V     | 0 V     | 0 V        | Hi Z       |

| 4                                              | Х        | Х          | 0 V     | 0 V     | 0 V        | Hi Z       |

| 5                                              | RESERVED | FOR FUTURE |         |         |            |            |

| 6                                              | Х        | Х          | 0 V     | 0 V     | 0 V        | 0 V        |

#### **Electrical Characteristics of PWM Section**

Unless otherwise specified under conditions, the Min and Max ratings stated below apply over the entire specified operating ratings of the PD70211 device. Typical values stated, are determined either by design or by production testing at 25 °C ambient. Voltages are with respect to IC ground (VPN\_IN).

**Table 7 • Typical Electrical Performance**

| Symbol                 | Parameter                | Conditions                               | Min   | Тур        | Max                  | Units  |

|------------------------|--------------------------|------------------------------------------|-------|------------|----------------------|--------|

| Input voltage          | current                  |                                          |       |            |                      |        |

| Vcc_uvlo_up            | UVLO threshold with      | Vcc rise time -≥ 0.5 ms                  | 8.85  | 9.15       | 9.5                  | V      |

|                        | input rising             |                                          |       |            |                      |        |

| Vcc_uvlo_dn            | UVLO threshold with      | Vcc rise time -≥ 0.5 ms                  | 7     | 7.3        | 7.6                  | V      |

|                        | input falling            |                                          |       |            |                      |        |

| Ivcc_sd                | IC input current (no     | Venable = Low,                           |       | 1          | 2000                 | μΑ     |

|                        | switching)               | or Vvcc < Vcc_uvlo_up                    |       |            |                      |        |

| Ivcc_α                 | IC input current         | Venable = High, and                      |       |            | 3                    | mA     |

|                        | (switching, no load on   | $V_{VCC} > V_{CC\_UVLO\_UP}$             |       |            |                      |        |

|                        | SG, PG, VDD)             | fsw = 500 kHz                            |       |            |                      |        |

| Input UVLO/            | PFW                      |                                          |       |            |                      |        |

| VINS_TH                | Threshold on VINS pin    | Rising or falling                        | 1.171 | 1.200      | 1.229                | V      |

| V <sub>HYST_HIGH</sub> | Hysteresis pin high      | IHYST_SOURCING = 1 mA                    | 2.8   |            |                      | V      |

|                        | voltage                  |                                          |       |            |                      |        |

| V <sub>HYST_LOW</sub>  | Hysteresis pin low       | IHYST_SINKING = 3 mA                     |       |            | 0.4                  | V      |

|                        | voltage                  |                                          |       |            |                      |        |

| LDOs                   |                          |                                          |       |            |                      |        |

| VL                     |                          | I <sub>VDD_EXT</sub> < 5 mA (current out | 4.75  | 5          | 5.25                 | V      |

|                        |                          | of pin)                                  |       |            |                      |        |

| VH                     | VH rail (with respect to |                                          |       | <b>-</b> 5 |                      | V      |

|                        | VCC)                     |                                          |       |            |                      |        |

| Soft start             |                          |                                          |       |            |                      |        |

| Iss_ch                 | Current out of SS pin    | RFREQ = 33.3k, Vss = 0.5 V               | 32    | 36         | 40                   | μΑ     |

|                        | during charging phase    |                                          |       |            |                      |        |

| Iss_disch              | Current into SS pin      | RFREQ = 33.3k, Vss = 0.5 V               |       | 10         |                      | % of   |

|                        | during discharging       |                                          |       |            |                      | SS_CH  |

|                        | phase                    |                                          |       |            | 1.229<br>0.4<br>5.25 |        |

| Vss_ch                 | Soft start charge        | By design only                           | 90    |            | 95                   | % of   |

|                        | completed threshold      |                                          |       |            |                      | VREF   |

| Vss_disch              | Soft start discharge     |                                          |       | 50         |                      | mV     |

|                        | completed threshold      |                                          |       |            |                      |        |

| Rss_disch              | Soft-start pin discharge |                                          |       | 50         |                      | Ω      |

|                        | FET resistance           |                                          |       |            |                      |        |

| tыscн                  | Soft-start discharge FET |                                          |       | 32         |                      | Switc  |

|                        | on-time                  |                                          |       |            |                      | cycles |

| Symbol                 | Parameter                                                                        | Conditions                                           | Min   | Тур   | Max   | Units |

|------------------------|----------------------------------------------------------------------------------|------------------------------------------------------|-------|-------|-------|-------|

| f <sub>sw_range</sub>  | Switching frequency accuracy                                                     | RFREQ = 33.2k                                        | 285   | 315   | 345   | kHz   |

| f <sub>sync_max</sub>  | Maximum<br>synchronization<br>frequency                                          |                                                      | 1     |       |       | MHz   |

| Vsync_hi               | SYNC pin high threshold                                                          |                                                      | 2.4   |       |       | V     |

| Vsync_lo               | SYNC pin low threshold                                                           |                                                      |       |       | 0.8   | V     |

| tsync                  | Minimum pulse width of SYNC pulse                                                |                                                      | 100   |       |       | ns    |

| Dsync_max              | Maximum SYNC pulse duty cycle                                                    |                                                      |       |       | 90    | %     |

| Error amplifie         | er                                                                               |                                                      |       |       |       |       |

| VREF                   | Reference voltage                                                                |                                                      | 1.171 | 1.200 | 1.229 | V     |

| Gain <sub>DC_OPL</sub> | DC open-loop gain                                                                | Rload = 100k                                         | 70    | 100   |       | dB    |

| AVugbw                 | Unity gain bandwidth                                                             | Cload = 10 pF (By design only)                       | 2     | 5     |       | MHz   |

| Ісомр_оит              | Output sourcing current                                                          | 0.2 V ≤ V <sub>COMP</sub> ≤ 1.3 V                    | 110   |       | 620   | μΑ    |

| ICOMP_IN               | Output sinking current                                                           | 0.2 V ≤ V <sub>COMP</sub> ≤ 1.3 V                    | 145   |       | 495   | μΑ    |

| VEA_CMR_MAX            | Maximum of input common-mode range                                               |                                                      | 2     |       |       | V     |

| VCLAMP                 | COMP pin high clamp                                                              |                                                      | 1.8   | 2.1   | 2.6   | V     |

| PWM compar             | rator                                                                            |                                                      |       |       |       |       |

| Voffset                | Inserted offset in inverted input                                                |                                                      | 200   |       | 300   | mV    |

| VRCLP                  | Voltage set on RCLP pin<br>by external resistor to<br>GND                        |                                                      | 0     |       | 1     | V     |

| Current sense          | e amplifier                                                                      |                                                      |       |       |       |       |

| Gaincsa                | DC Gain                                                                          | 0 mA < I <sub>AUX</sub> < 4 mA                       | 4.75  | 5     | 5.25  | V     |

| laux                   | Maximum continuous current from V <sub>AUX</sub>                                 |                                                      | 4     |       |       | mA    |

| Vcsa_cmr_max           | Maximum input common-mode range                                                  |                                                      | 2     |       |       | V     |

| <b>t</b> blank         | Blanking time                                                                    |                                                      | 50    |       | 100   | ns    |

| VILIM                  | Current limit threshold<br>on output of current<br>sense amplifier               | Where PWM pulses start to get truncated              | 1.1   | 1.2   | 1.3   | V     |

| VILIMHICCUP            | Current limit threshold<br>on output of current<br>sense amplifier<br>capability | Where PWM pulses start to get omotted in hiccup mode | 1.7   | 1.8   | 1.9   | V     |

| Differential v         | oltage amplifier                                                                 |                                                      |       |       |       |       |

| Gain <sub>DA</sub>     | DC gain of differential voltage amplifier                                        |                                                      | 6.68  | 7.0   | 7.14  | V     |

| Symbol             | Parameter               | Conditions | Min  | Тур | Max | Unit |

|--------------------|-------------------------|------------|------|-----|-----|------|

| AVugbw_da          | Unity gain bandwidth of |            |      | 5   |     | MHz  |

|                    | differential voltage    |            |      |     |     |      |

|                    | amplifier               |            |      |     |     |      |

| VDA_CMR_MAX        | Maximum of input        |            | 3.5  |     |     | V    |

|                    | common-mode range       |            |      |     |     |      |

| Drivers            |                         |            |      |     |     |      |

| <b>R</b> рд_ні     | Drive resistance when   |            |      | 10  |     | Ω    |

|                    | PG is high              |            |      |     |     |      |

| R <sub>PG_LO</sub> | Drive resistance when   |            |      | 5   |     | Ω    |

|                    | PG is low               |            |      |     |     |      |

| tpg_min            | Minimum on-time of PG   |            |      |     | 120 | ns   |

| DMAX               | PG maximum duty cycle   |            | 44.5 |     | 50  | %    |

| Rsg_HI             | Drive resistance when   |            |      | 10  |     |      |

|                    | SG is high              |            |      |     |     |      |

| Rsg_Lo             | Drive resistance when   |            |      | 10  |     |      |

|                    | SG is low               |            |      |     |     |      |

| <b>t</b> DEAD      | Deadtime                |            | 60   | 110 | 190 | ns   |

| Logic levels o     | n VINS and ENABLE       |            |      |     |     |      |

| Vнı                | Input high threshold    |            | 2    |     |     | ٧    |

| VLO                | Input low threshold     |            |      |     | 0.8 | V    |

| Thermal prot       | ection                  |            |      |     |     |      |

| Tsp                | Thermal shutdown        |            |      | 157 |     | °C   |

|                    | (rising)                |            |      |     |     |      |

| Тнуѕт              | Thermal shutdown        |            |      | 15  | 30  | °C   |

|                    | hysteresis              |            |      |     |     |      |

#### 4.4.1 Thermal Protection

PD70211 is protected from excessive internal temperatures that may occur during various operating procedures. Two temperature sensors are located on the chip, monitoring the temperatures of the following:

- Isolating Switch (pass-FET)

- Classification Current Sink

Each of the over temperature sensor activates a protection mechanism that will disconnect the Isolation (pass) FET or the classification circuit, respectively. This protects the device from being permanently damaged or even from long-term degradation.

#### 4.4.2 Wall Adapter Mode

PD70211 supports wall adapter functionality. That is, by setting WA\_EN pin high, it will give priority to the wall adapter jack to supply the load.

WA\_EN pin is used while connecting a wall adapter voltage between VPP and VPN\_OUT by means of an OR-ing diode.

While WA\_EN, wall adapter enable pin, is held low (referenced to VPN\_IN), the front-end works as a normal PD.

When WA\_EN is raised high (referenced to VPN\_IN), three internal operations are forced:

- The Isolation FET is turned OFF.

- All output flags AT\_FLAG, HD\_FLAG, 4P\_AT\_FLAG, and 4P\_HD\_FLAG are activated (low state).

- Vaux output voltage is turned ON.

While activating WA\_EN pin, the wall adapter will supply input voltage for the DC-DC converter.

Having WA\_EN at high state does not disable detection and classification modes.

# 5 Pin Configuration

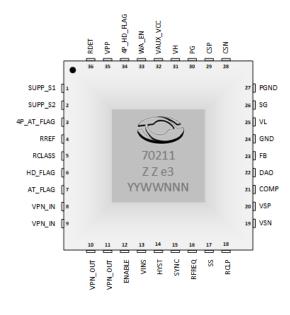

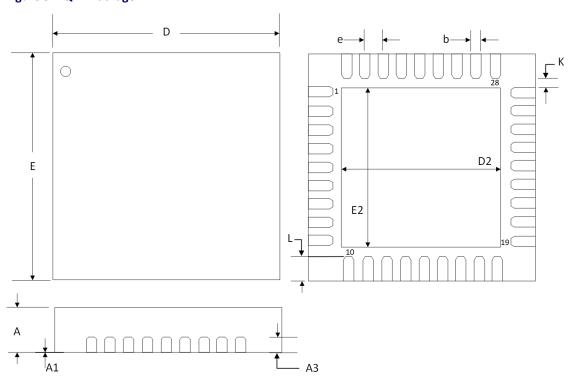

The following illustration shows the device pin diagram from the top view.

Figure 4 • PD70211 Pinout

(Top view)

The following table lists the pin descriptions of the PD70211 device.

**Table 8 • Pin Descriptions**

| Pin Number | Designator | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | SUPP_S1    | Input pin for sensing the voltage on the diode bridge connected to the data pairs. This pin along with the SUPP_S2 pin can be used to distinguish between 2-pair and 4-pair operation. (For PSEs that operate in 4 pairs but generates the classification procedure on only one pair and not on both pairs). Signal is referenced to VPN_IN. Place a 10k resistor in the input of this pin. |  |  |  |

| 2          | SUPP_S2    | Input pin for sensing the voltage on the diode bridge connected to the data pairs. This pin along with the SUPP_S1 pin can be used to distinguish between 2-pair and 4-pair operation. (For PSEs that operate in 4 pairs but generates the classification procedure on only one pair and not on both pairs). Signal is referenced to VPN_IN. Place a 10k resistor in the input of this pin. |  |  |  |

| 3          | 4P_AT_FLAG | Open Drain Output. The pin gets actively pulled low when a 4-pair version of a (non-standard) Type 2 PD-PSE mutually identify each other via classification. There is a minimum 80 ms delay from the moment when the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.                                                                             |  |  |  |

| 4          | RREF       | Bias current resistor. A 60.4k, $1\%$ resistor is connected between RREF and IC ground (VPN_IN).                                                                                                                                                                                                                                                                                            |  |  |  |

| Pin Number | Designator | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5 RCLASS   |            | Sets the Class of the PD. Connect RCLASS (programming resistor) between this pin and IC ground (VPN_IN). Allowed values are 133 $\Omega$ , 69.8 $\Omega$ , 45.3 $\Omega$ , and 30.9 $\Omega$ for Class 1, 2, 3, and 4 respectively. If RCLASS is not present, the PD will draw up to 3 mA during classification, thus indicating Class 0 (default Type 1) to the PSE. Signal is referenced to VPN_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 6          | HD_FLAG    | Open Drain Output. The pin gets actively pulled low when a 2-pair HDBaseT PD-PSE mutually identify each other via classification. There is a minimum 80 ms delay from the moment when the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 7          | AT_FLAG    | Open Drain Output. This pin gets actively pulled low when a Type 2 PD-PSE mutually identifies each other via classification. There is a minimum 80 ms delay from the moment when the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 8, 9       | VPN_IN     | Lower rail of the incoming PSE voltage rail – from the negative terminal of the two ORed bridge rectifiers (the corresponding upper PoE rail is VPP).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 10, 11     | VPN_OUT    | This is in effect, the switched ground for establishing continuity to the PWM section after successful detection, classification, and power-up. It is connected to the power ground and PWM controller IC's ground plane of the DC-DC converter section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 12         | ENABLE     | A logic-level input to enable the converter. We can pull it constantly up, say with a 100k resistor to VDD, to forcibly enable the converter, provided the input supply has exceeded any applicable UVLO thresholds as set on the VINS pin or on the VCC pin. Internally, the ENABLE pin goes to the input of an OR-gate, the other input terminal of which is tied to "POK" — a signal provided by the front-end. If the ENABLE pin is forced high, the output of the OR-gate goes high and the converter is allowed to start (provided all UVLO's are past). If the ENABLE pin is held low, the internal node "POK" goes active/high when the PD's front end conducts (power OK), so the OR-gate goes high once again. In this case, the switching converter turns ON as required by the PoE standard. However, for supporting wall adapters, injecting power after the front-end (at the input of the converter), we can forcefully turn the converter ON without the front-end signaling "PGOOD", by not tying the ENABLE pin low, but by tying it high (to VDD). That will turn ON the converter irrespective of the state of the front-end (conducting or not), and whether there is any incoming PoE power or not. |  |  |  |  |

| 13         | VINS       | The VINS pin is a programmable UVLO pin. The converter will turn ON provided the voltage on the VINS pin is above 1.2 V (and VCC is not in UVLO, and ENABLE pin is also high – connected to VDD, for example). The converter will stop switching (turns OFF) when the voltage on the VINS pin falls below 1.2 V (or if ENABLE is taken low, or if VCC falls outside its operating range). Thus, by connecting a voltage divider between input rail and IC ground, we can set the UVLO threshold to enable switching. However, to have a smooth startup, it is advisable to have some hysteresis too, by means of a resistor between VINS and HYST as explained below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Pin Number | Designator | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 14 HYST    |            | This is the output of the UVLO comparator as shown in the Block Diagram. We connect a "hysteresis resistor" from HYST pin to VINS pin to create positive feedback (and hysteresis). Initially, as the input voltage is rising, the VINS pin voltage is below 1.2 V and so the output of the UVLO comparator is low, leading the hysteresis resistor to fall in parallel to the lower resistor of the UVLO divider placed at the VINS pin, assisting it to pull down the VINS pin voltage further. As soon as the rising UVLO threshold is exceeded (VINS > 1.2 V), the output of the UVLO comparator suddenly goes high (up to VDD) and the hysteresis resistor, effectively comes partially across the upper resistor of the UVLO divider, assisting it in to pull up the voltage on the VINS pin. This feedback therefore increases the voltage on the VINS pin. Now, the input rail has to fall to a much lower level to allow the VINS pin voltage to fall below 1.2 V. That is how hysteresis is created by positive feedback action through the hysteresis resistor. The exact math is in the applications information of this datasheet. Note that HYST pin always toggles between high or low depending on whether the voltage on the VINS pin is above or below 1.2 V, respectively. This can always be used to simultaneously drive an opto, to indicate when the input rail is above the programmed rising |  |  |  |  |

| 15         | SYNC       | threshold and when it falls below the programmed falling threshold.  Used to synchronize the LX7309 to a frequency higher than its default value as set on RFREQ pin. The synchronizing clock must be 2x the desired sync frequency, with a maximum synchronizing clock frequency of 1 MHz (for 500 kHz PWM frequency). The PG pin's rising edge will occur at the same instant as the rising edge of the clock being applied on the SYNC pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 16         | RFREQ      | Connect a programming resistor from this pin to IC ground (pin GND) to set the switching frequency. A typical value of the programming resistor is 49.9k, and this value will provide a frequency of 215 kHz. Halving it will roughly double the frequency, whereas doubling it will halve the frequency. Note that the converter is designed to operate from 100 to 500 kHz based on this pin.  Switching Frequency Equation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|            |            | $Freq = \frac{1}{(90pF \times RFREQ) + 150ns}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|            |            | where Freq is [Hz] and $R_{\text{FREQ}}$ in [ $\Omega$ ]  For further information, see Setting Switching Frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 17         | SS         | This is the soft-start pin. Typically, a 0.1 μF capacitor, the "soft-start capacitor", is connected between this pin and IC ground (pin GND). The capacitor gets charged up 1.2 V by an internal resistor, and the voltage on the capacitor, in effect, forms the input voltage reference VREF of the error amplifier. But, note that this capacitor serves other functions too; for example, it controls the rate of hiccupping under overcurrent fault conditions. So, even if the internal reference is not being used (as ir isolated topologies with a TL431 on the secondary side), the soft-stat capacitor is recommended to be in place always. The actual capacitor used will be determined by the application. For further information, see Setting Soft-Start.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 18         | RCLP       | Low power clamp resistor. We can connect a resistor from this pin to IC groun GND) to set the exact level at which pulse-skipping mode is entered at light lo However, the usual default is to connect this pin directly to IC ground, in whic pulse-skipping mode is disabled. The method to select the threshold (and RCL resistor value) is described in the Applications Information section of this data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Pin Number | Designator | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 19 VSN     |            | The negative input of the internal differential-sense voltage amplifier. Note that the common-mode range of the differential voltage amplifier is 3.5 V and its gain is 7. We can use this differential amplifier for implementing topologies where the "system (output) ground" is different from the IC ground. We can then step-down both output rails (output rail and its return), by equal amounts, using identical voltage dividers, to bring the voltage below 3.5 V, then use differential sensing, and finally connect the output of the differential voltage amplifier (pin DAO) to FB pin.                                                                                                                                                                                                                                                                    |  |  |  |  |

| 20         | VSP        | The positive input of the internal differential-sense voltage amplifier. Note that it must always be connected in such a way that VSP is at a higher voltage than VSN. Also keep in mind that since the differential voltage amplifier has a gain of 7 and the output of that amplifier is connected to the feedback pin which compares that against a 1.2 V reference, in effect, the difference between VSP and VSN stabilizes to 1.2V/7 = 0.171 V in steady state. That is how the (identical) voltage dividers present on VSP and VSN are designed.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 21         | СОМР       | This is the output of the internal error amplifier, and the input of the PWM comparator. It is brought out to support isolated topologies because in such cases, there is an error amplifier already present on the secondary side (for example a TL431 or equivalent). Therefore, we want to bypass the error amplifier of the converter section. On the other hand, in non-isolated topologies, we want to use the error amplifier of the converter. We can do that directly or through the differential voltage amplifier stage.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 22         | DAO        | This is the output of the internal differential voltage amplifier (gain = 7). When amplifier is used, we connect DAO to the feedback pin (FB). We have part of the compensation network between the two pins, and this network is typical of any 3 error amplifier input, with or without a differential amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 23         | FB         | This is the feedback pin of the IC. It is internally compared to a 1.2 V reference. If the internal error amplifier is not used and the COMP pin is being used to inject the error signal (as in isolated topologies), the FB pin can be either tied high (to VDD), or connected to COMP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 24         | GND        | This is the IC ground or the analog (quiet) ground of the IC. Pin 20 is the Power ground (PGND). Typically, we can connect the analog ground and PGND together on a copper island on the component side, and then connect that through several vias very close to the chip on to a large ground plane which extends up to the lower side of the current sense resistor. All chip decoupling can then be very simple with respect to the copper island on the component side.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 25         | VL         | This is created by an internal LDO and basically provides a housekeeping rail for the IC itself, which is 5 V with respect to the IC ground. A 1 $\mu$ F ceramic cap placed close to this pin, connected to IC ground is recommended for proper decoupling. This pin can also provide up to 5 mA for external circuitry if required, thermal aspects (IC dissipation) being considered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 26         | SG         | Secondary Gate driver. We can use this to drive a synchronous FET or an active clamp FET. It is derived from VCC (~ 12 V), and has a 10 $\Omega$ limiting resistor. So, it can be used to drive a Gate-drive transformer directly. It is usually complementary to the Primary Gate driver pin (PG). But there is a typical 110 ns blanking time between the two to prevent cross-conduction. SG is held firmly low in pulse-skip mode (if allowed). It is also low during soft-start. It allows forced PWM (continuous conduction) mode by allowing negative inductor currents. It does not support diode-emulation mode (discontinuous conduction mode). However, in pulse-skip mode, since SG stays OFF, the converter automatically lapses into discontinuous conduction mode through the body-diode of the synchronous FET. We can leave this pin floating if unused. |  |  |  |  |

| Pin Number | Designator | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 27         | PGND       | Power ground (for internal SG and PG drivers). This is ideal for VCC decoupling and the Primary-side current sense resistor's lower terminal. We can also combine GND an PGND on to a single large ground plane. Note that Power ground plane is firmly connected to VPN_OUT, which is the drain side of the PD's low-side pass-FET (it stands for Negative Port Voltage Out).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 28         | CSN        | The negative input of the internal current-sense voltage amplifier. Note that the common-mode range of the differential current-sense amplifier is 2 V and its gain is 5. We can use this for high-side current sensing up to 2 V. It is then placed on the (steady) output side of a Buck inductor, and the maximum output voltage is 1.8 V for using this type of sensing. Ensure that CSN is at a lower voltage compared to the positive input of the current-sense amplifier (CSP). Current sensing can also be implemented in a more basic fashion for "low-side" sensing, with a resistor in the return (ground) of the Buck. In that case, CSN is shown connected to IC ground. However, to avoid noise from ground bounce, it is best to route this on the PCB in Kelvin manner to the lower end of the sense resistor. This is important because the peak operating voltage on the sense resistor is only 200 mV and PCB-related noise can cause jitter in the switching waveform in current-mode control. |  |  |  |  |

| 29         | CSP        | The positive input of the internal current-sense voltage amplifier. See description of Pin 28 (CSN) above. Note that the output of the current-sense amplifier is amplified 5 times. So a 0.2 V current-sense voltage translates to a 1 V swing at the input of the PWM comparator. Higher voltages lead to hiccup mode protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |