# UG0574 User Guide RTG4 FPGA Fabric

a **MICROCHIP** company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revis  | ion His        | story                                                  | 1  |

|---|--------|----------------|--------------------------------------------------------|----|

|   | 1.1    | Revisio        | n 6.0                                                  | 1  |

|   | 1.2    |                | n 5.0                                                  |    |

|   | 1.3    |                | n 4.0                                                  |    |

|   | 1.4    |                | n 3.0                                                  |    |

|   |        |                |                                                        |    |

|   | 1.5    |                | n 2.0                                                  |    |

|   | 1.6    | Revisio        | n 1.0                                                  | 2  |

| 2 | Fabrio | Over\          | view                                                   | 3  |

| 3 | Logic  | Elomo          | ents and Routing                                       | 5  |

| J | _      |                |                                                        |    |

|   | 3.1    | •              | ilement                                                |    |

|   |        | 3.1.1<br>3.1.2 | 4-Input LUT with Carry Chain                           |    |

|   |        | 3.1.2<br>3.1.3 | STMR-D Flip-Flop                                       |    |

|   |        | 3.1.3          | Interface Logic                                        |    |

|   | 2.0    | -              |                                                        |    |

|   | 3.2    | Ū              | Cluster                                                |    |

|   | 3.3    | _              | g Architecture                                         |    |

|   | 3.4    | Libero (       | Compile Report - Fabric Resources                      | 10 |

| 4 | Embe   | dded N         | Memory Blocks                                          | 11 |

|   | 4.1    | LSRAM          | 1                                                      | 12 |

|   |        | 4.1.1          | Dual-Port Mode                                         |    |

|   |        | 4.1.2          | Two-Port Mode                                          |    |

|   |        | 4.1.3          | LSRAM Read Operation                                   |    |

|   |        | 4.1.4          | LSRAM Write Operation                                  | 18 |

|   |        | 4.1.5          | Pipelined Read Synchronous Reset Operation             |    |

|   |        | 4.1.6          | Pipelined Read Asynchronous Reset Operation            |    |

|   |        | 4.1.7          | LSRAM ECC                                              |    |

|   |        | 4.1.8          | Using LSRAM in a Design                                |    |

|   |        | 4.1.9          | Use Model: LSRAM Write-Feed-Through using Fabric Logic |    |

|   |        | 4.1.10         | Debugging LSRAMs Using SmartDebug                      |    |

|   | 4.2    | •              | 1                                                      |    |

|   |        | 4.2.1          | μSRAM Read Operation                                   |    |

|   |        | 4.2.2          | µSRAM Write Operation                                  |    |

|   |        | 4.2.3          | µSRAM Synchronous Reset Operation                      |    |

|   |        | 4.2.4          | µSRAM Asynchronous Reset Operation                     |    |

|   |        | 4.2.5<br>4.2.6 | μSRAM ECC Using μSRAM in a Design                      |    |

|   |        | 4.2.7          | Collision Behavior                                     |    |

|   | 4.3    |                |                                                        |    |

|   | 4.3    | 4.3.1          | //µPROM Architecture and Address Space                 |    |

|   |        | 4.3.1          | µPROM Operation                                        |    |

|   |        | 4.3.3          | µPROM Configurator                                     |    |

| 5 | Math   |                | ······································                 |    |

| J |        |                |                                                        |    |

|   | 5.1    |                | ction                                                  |    |

|   | 5.2    | Feature        | es                                                     | 80 |

|   | 5.3    | Math Bl        | lock Resource Table                                    | 80 |

|   | 5.4    | Archited       | cture Description                                      | 81 |

|   | <b>Microsem</b>     |

|---|---------------------|

| Ī | a MICEOCHIE COMPANY |

|   | 5.5        | 5.4.1<br>5.4.2<br>5.4.3<br>Math BI<br>5.5.1<br>5.5.2<br>5.5.3                                                         | Multiplier       81         Adder or Subtractor       83         I/O and Control Registers       83         ocks Functional Examples       84         Designing with Math Blocks       84         Use Models       85         Coding Style Examples       89                                                                                                                                                                                                                                                   |

|---|------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | Apper      | ndix: Sı                                                                                                              | upported Memory File Formats98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7 | Apper      | ndix: M                                                                                                               | acro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 7.1        | LSRAM 7.1.1 7.1.2 7.1.3 7.1.4 7.1.5 7.1.6 7.1.7 7.1.8 7.1.9 7.1.10 7.1.11 7.1.12 7.1.13                               | Macro       101         A_WIDTH and B_WIDTH       101         A_WEN and B_WEN       102         A_ADDR and B_ADDR       102         A_DIN and B_DIN       102         A_DOUT and B_DOUT       103         A_BLK and B_BLK       103         A_WMODE and B_WMODE       103         A_CLK and B_CLK       103         A_REN and B_REN       105         ARST_N       105         ECC and ECC_DOUT_BYPASS       105         A_SB_CORRECT and B_SB_CORRECT       105         A_DB_DETECT and B_DB_DETECT       105 |

| 0 | 7.3        | μSRAM<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>Math Bl | Macro       105         A_WIDTH, B_WIDTH, and C_WIDTH       106         C_WEN       106         A_ADDR, B_ADDR, and C_ADDR       107         C_DIN       107         A_DOUT and B_DOUT       107         A_BLK, B_BLK, and C_BLK       108         C_CLK       108         ARST_N       108         ECC and ECC_DOUT_BYPASS       108         A_SB_CORRECT and B_SB_CORRECT       108         A_DB_DETECT and B_DB_DETECT       109         ock Macro       109                                                |

| 8 |            | -                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 8.1<br>8.2 | •                                                                                                                     | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 0.2        | remini                                                                                                                | лоуу                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# **Figures**

| Figure 1  | Functional Block Diagram of RTG4 Family Device                                              | . 3 |

|-----------|---------------------------------------------------------------------------------------------|-----|

| Figure 2  | Fabric Layout                                                                               |     |

| Figure 3  | Functional Block Diagram of Logic Element                                                   | . 5 |

| Figure 4  | Functional Block Diagram of STMR-D Flip-Flop                                                |     |

| Figure 5  | Functional Block Diagram of Interface Logic                                                 |     |

| Figure 6  | LSRAM/µSRAM/Math Block Interfacing with ILs in a Row                                        |     |

| Figure 7  | Functional Block Diagram of I/O Element                                                     |     |

| Figure 8  | Logic Cluster                                                                               |     |

| Figure 9  | Sample Compile Report for RT4G150                                                           |     |

| Figure 10 | Functional Block Diagram of LSRAM                                                           |     |

| Figure 11 | Block Select Inputs for Dual-Port Mode                                                      |     |

| Figure 12 | Two Port Mode x36 Data Flow                                                                 |     |

| Figure 13 | LSRAM Read Operation                                                                        |     |

| Figure 14 | LSRAM Write Operation— Followed by Earliest Read                                            |     |

| Figure 15 | LSRAM Synchronous Reset Operation                                                           |     |

| Figure 16 | LSRAM Asynchronous Reset Operation                                                          |     |

| Figure 17 | LSRAM Ports Configured as Dual-Port SRAM - DPSRAM Macro in Libero SoC                       |     |

| Figure 18 | Dual-Port Large SRAM Configurator                                                           |     |

| Figure 19 | LSRAM Ports Configured as Two-Port SRAM - TPSRAM Macro in Libero SoC                        | 28  |

| Figure 20 | Two-Port Large SRAM Configurator                                                            |     |

| Figure 21 | LSRAM Pipelined-ECC BLK Select De-assertion Hold Time Violation After Read                  |     |

| Figure 22 | LSRAM Configurator Fabric Wrapper Logic Mitigating BLK De-assertion Hold Time Issue on Dept |     |

| riguio 22 | Cascaded LSRAM Component 33                                                                 |     |

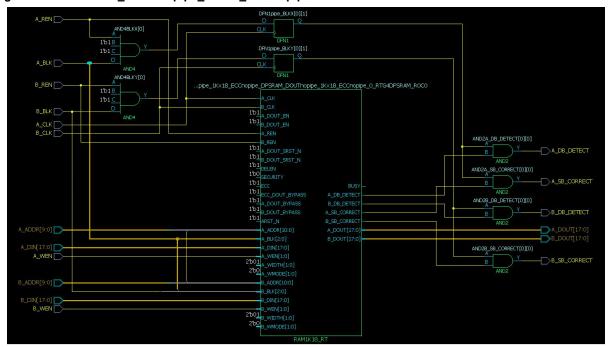

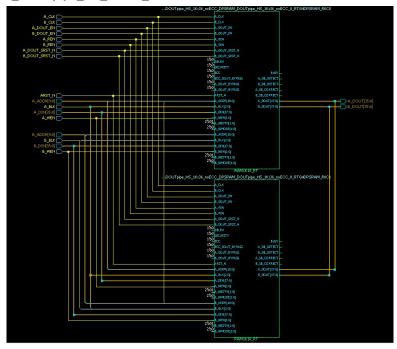

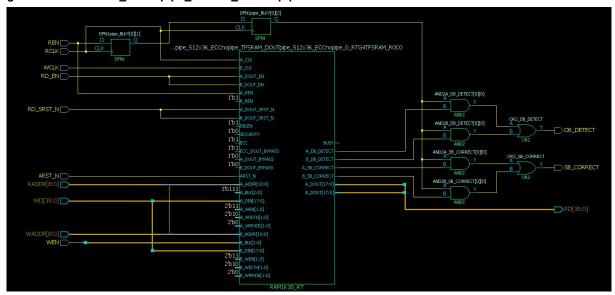

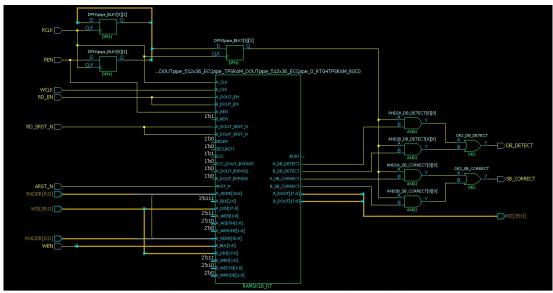

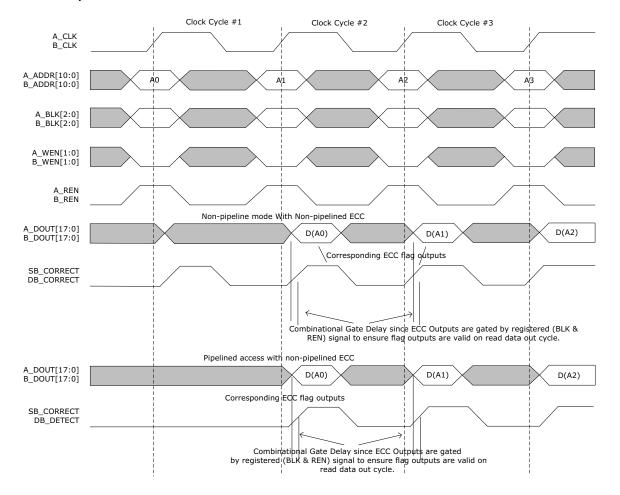

| Figure 23 | DPSRAM_DOUTnopipe_1Kx18_ECCnopipe                                                           | 36  |

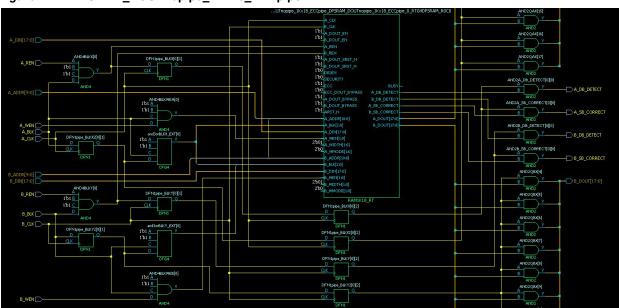

| Figure 24 | DPSRAM DOUTnopipe 1Kx18 ECCpipe                                                             |     |

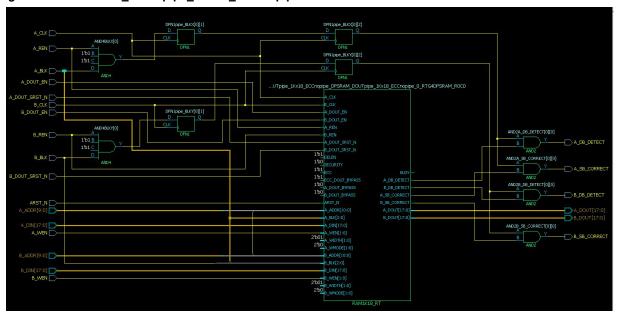

| Figure 25 | DPSRAM_DOUTpipe_1Kx18_ECCnopipe                                                             |     |

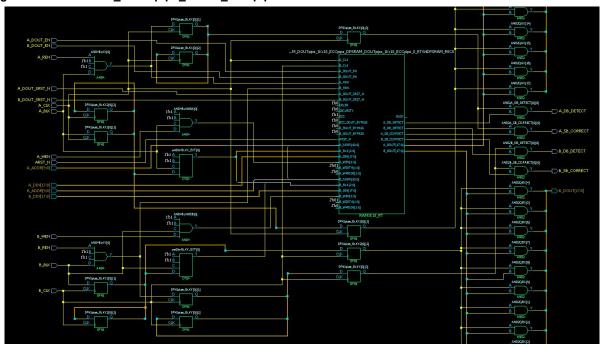

| Figure 26 | DPSRAM DOUTpipe 1Kx18 ECCpipe                                                               |     |

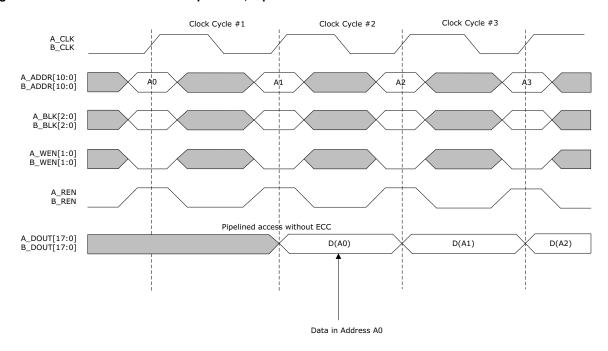

| Figure 27 | DPSRAM_DOUTpipe_HS_1Kx36_noECC                                                              |     |

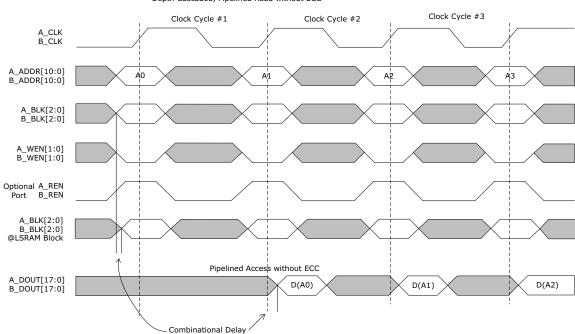

| Figure 28 | DPSRAM_DOUTpipe_LP_2Kx18_noECC                                                              |     |

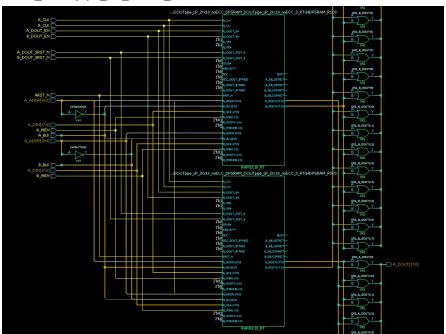

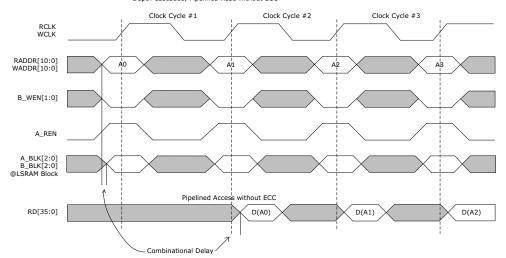

| Figure 29 | TPSRAM_DOUTnopipe_512x36_ECCnopipe                                                          |     |

| Figure 30 | TPSRAM_DOUTnopipe_512x36_ECCpipe                                                            |     |

| Figure 31 | TPSRAM_DOUTpipe_512x36_ECCnopipe                                                            |     |

| Figure 32 | TPSRAM_DOUTpipe_512x36_ECCpipe                                                              |     |

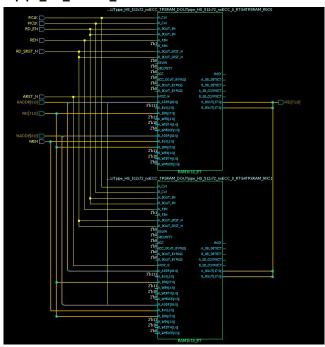

| Figure 33 | TPSRAM_DOUTpipe_HS_512x72_noECC                                                             |     |

| Figure 34 | TPSRAM_DOUTpipe_LP_1Kx36_noECC                                                              |     |

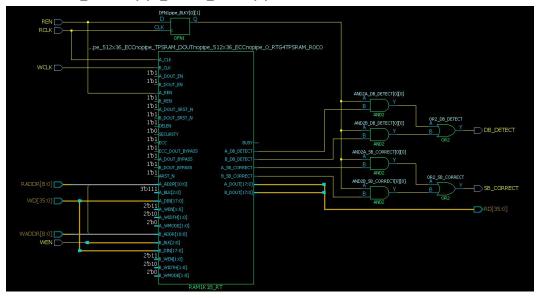

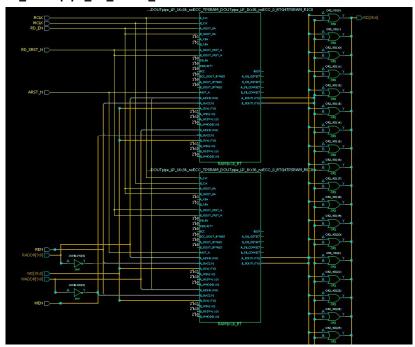

| Figure 35 | Case A: LSRAM Configurator Component with Comb Delay Gating ECC Flag Outputs, non-Pipeline  |     |

| 94 5 55   | ECC 43                                                                                      | -   |

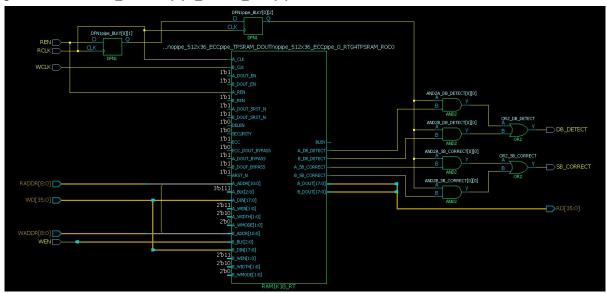

| Figure 36 | Case B: LSRAM Read Operation, Pipelined Read without ECC                                    | 44  |

| Figure 37 | Case C: Depth Cascaded Dual Port LSRAM Component, Pipelined Read without ECC                |     |

| Figure 38 | Case D: Depth Cascaded Two Port LSRAM Component, Pipelined Read without ECC                 |     |

| Figure 39 | Case E: Dual Port LSRAM with Pipelined ECC                                                  |     |

| Figure 40 | Case F: Two Port LSRAM with Pipelined ECC                                                   | 47  |

| Figure 41 | Libero Project Settings                                                                     |     |

| Figure 42 | TPSRAM: 0.5 Error Probability and 0.5 Correction Probability                                |     |

| Figure 43 | TPSRAM: 0.25 Error Probability and 0.85 Correction Probability                              |     |

| Figure 44 | TPSRAM: 0.15 Error Probability and 0.15 Correction Probability                              |     |

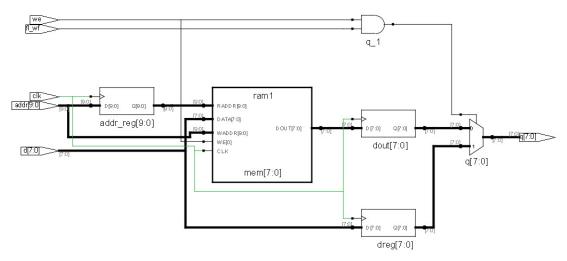

| Figure 45 | Sample Write-Feed-Thorough Fabric Logic                                                     |     |

| Figure 46 | Write-Feed-Through using Fabric Logic - RTL Schematic View                                  | 50  |

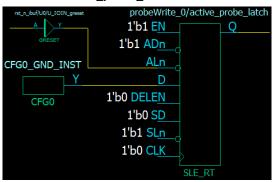

| Figure 47 | Post-Compile Netlist View of active_probe_latch                                             |     |

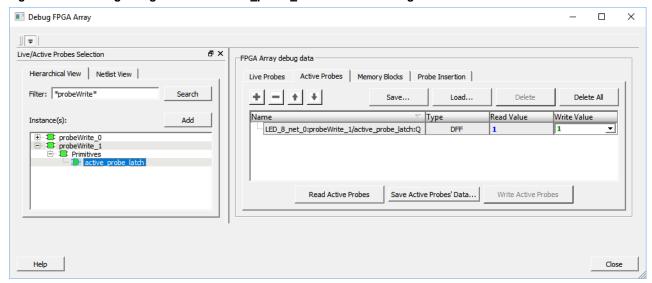

| Figure 48 | Instantiation of probeWrite_1 module with PRBWR_IN tied LOW                                 |     |

| Figure 49 | Writing a Logic-1 to the active_probe_latch Handshake Signal                                |     |

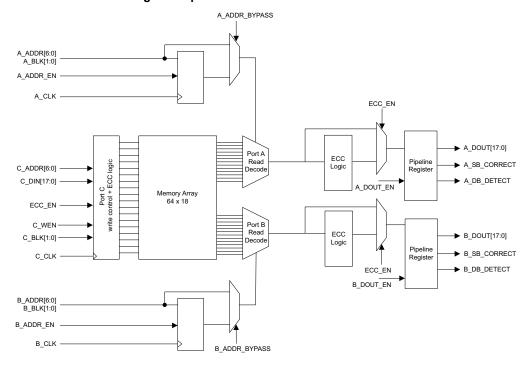

| Figure 50 | Functional Block Diagram of µSRAM                                                           |     |

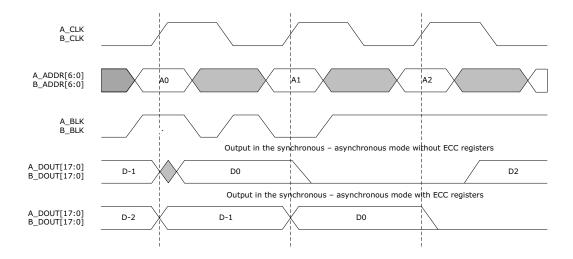

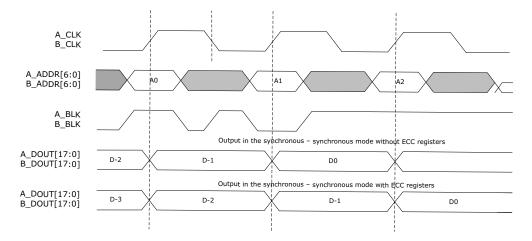

| Figure 51 | Synchronous-Asynchronous Read Operation without Pipeline Registers                          |     |

| Figure 52 | Synchronous-Synchronous Read Operation with Pipeline Registers                              |     |

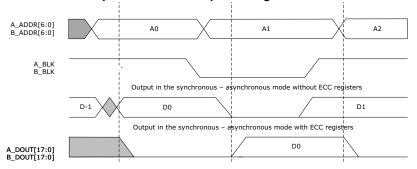

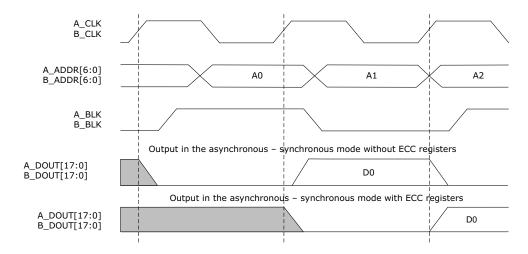

| Figure 53 | Asynchronous Read Operation without Pipeline Registers Waveform |     |

|-----------|-----------------------------------------------------------------|-----|

| Figure 54 | Asynchronous Read Operation with Pipeline Registers Waveform    |     |

| Figure 55 | μSRAM Write Operation                                           |     |

| Figure 56 | μSRAM Synchronous Reset Operation                               |     |

| Figure 57 | μSRAM Asynchronous Reset Operation                              | 62  |

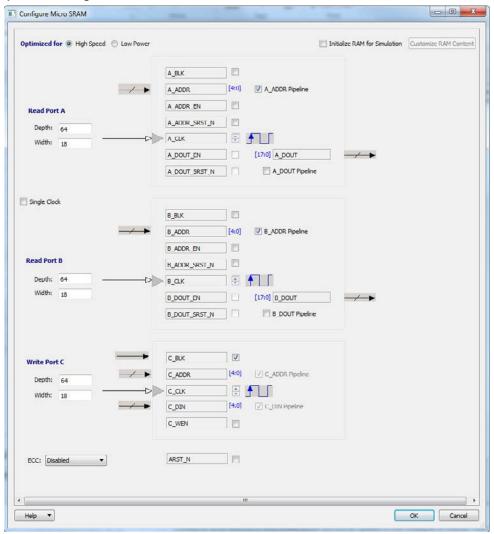

| Figure 58 | μSRAM Configurator in Libero SoC                                | 64  |

| Figure 59 | μSRAM Configurator                                              | 64  |

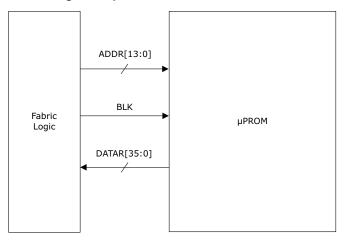

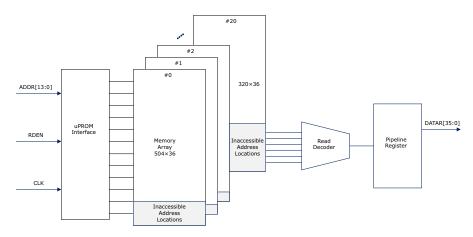

| Figure 60 | Functional Block Diagram of µPROM                               |     |

| Figure 61 | μPROM Memory Blocks                                             |     |

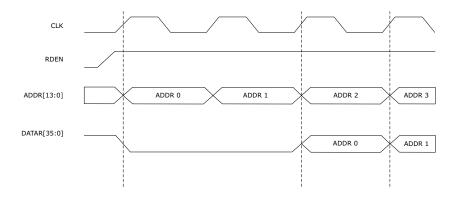

| Figure 62 | μPROM Read Operation                                            | 69  |

| Figure 63 | μPROM Configurator in Libero SoC                                | 70  |

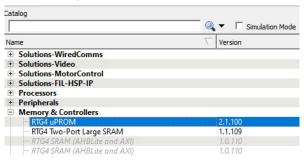

| Figure 64 | RTG4 µPROM Core in Catalog                                      | 70  |

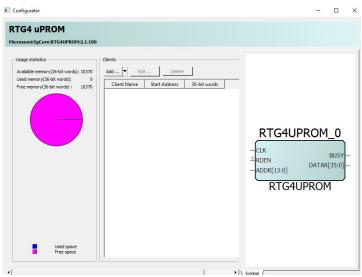

| Figure 65 | μPROM Configurator                                              | 70  |

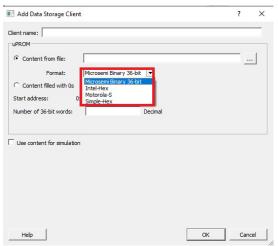

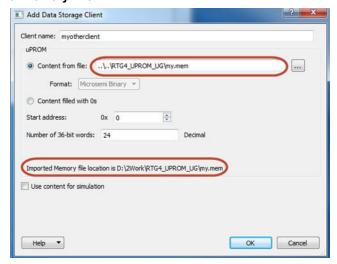

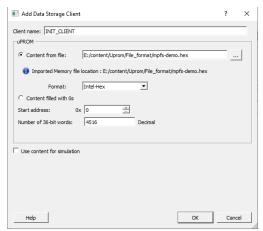

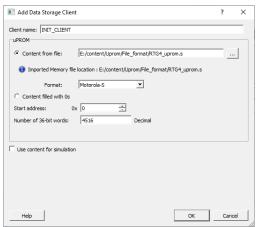

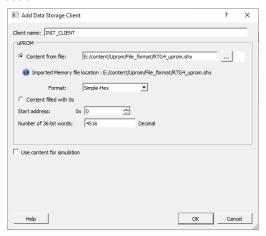

| Figure 66 | Add Data Storage Client Dialog Box                              | 71  |

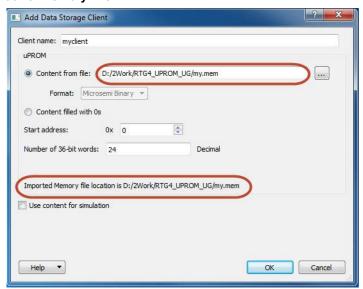

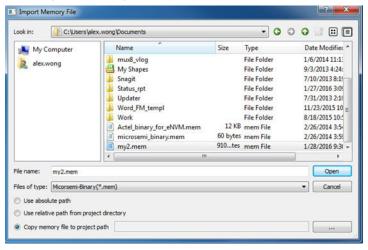

| Figure 67 | Import Memory File Dialog Box                                   | 72  |

| Figure 68 | Absolute Path of Memory File                                    | 72  |

| Figure 69 | Relative Path of Memory File                                    | 73  |

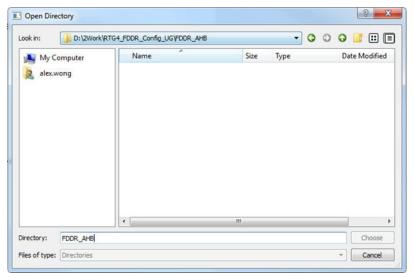

| Figure 70 | Location of Memory File to Copy From                            | 73  |

| Figure 71 | Project Sub-Folders Hidden from View                            | 74  |

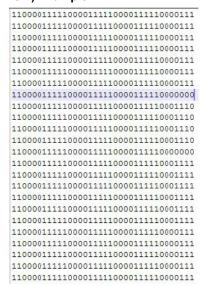

| Figure 72 | Microsemi Binary File (*.mem) Example                           | 74  |

| Figure 73 | Intel-Hex File Selection                                        | 75  |

| Figure 74 | Motorola-S File Selection                                       | 75  |

| Figure 75 | Simple-Hex File Selection                                       | 75  |

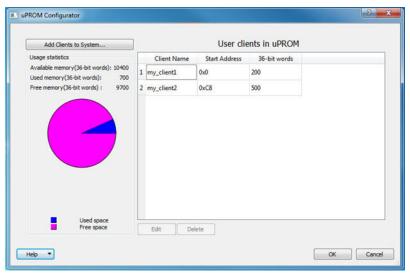

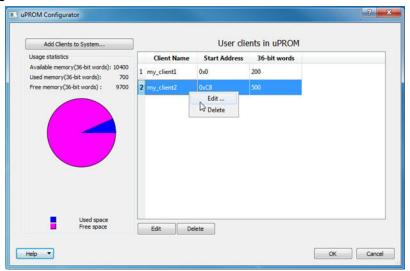

| Figure 76 | User Clients Added                                              | 76  |

| Figure 77 | Editing User Clients                                            | 77  |

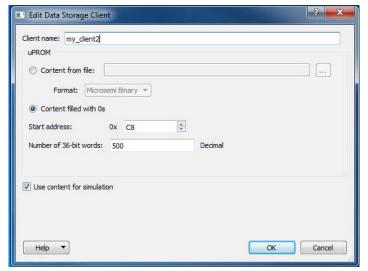

| Figure 78 | Edit Data Storage Client Dialog Box                             | 77  |

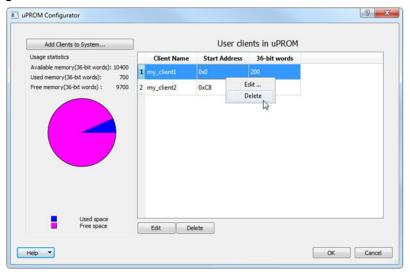

| Figure 79 | Deleting a Client                                               | 78  |

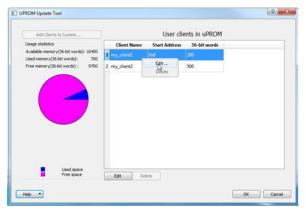

| Figure 80 | Update µPROM Memory Content                                     |     |

| Figure 81 | μPROM Update Tool                                               | 79  |

| Figure 82 | Edit Data Storage Client Dialog Box                             |     |

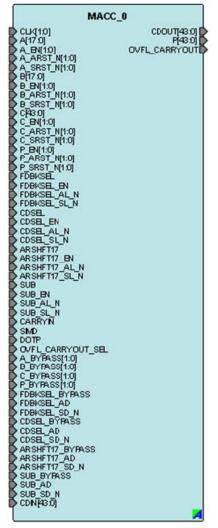

| Figure 83 | Functional Block Diagram of Math Block                          |     |

| Figure 84 | Functional Block Diagram of Math Block in Normal Mode           |     |

| Figure 85 | Functional Block Diagram of Math Block in DOTP Mode             |     |

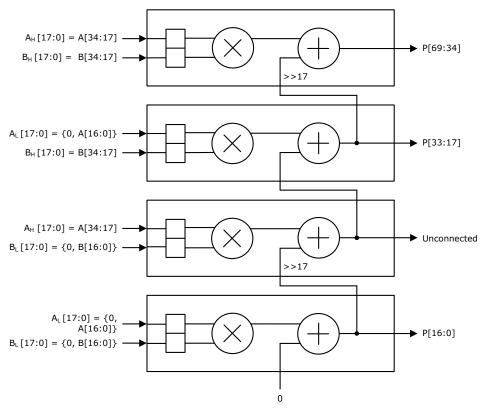

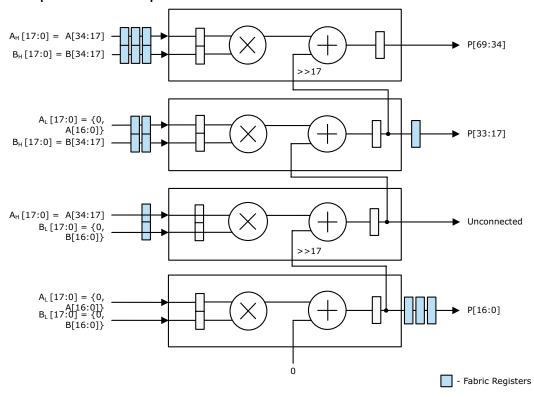

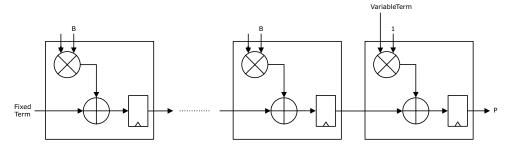

| Figure 86 | Non-Pipelined 35 × 35 Multiplier                                | 85  |

| Figure 87 | Pipeline 35 × 35 Multiplier                                     |     |

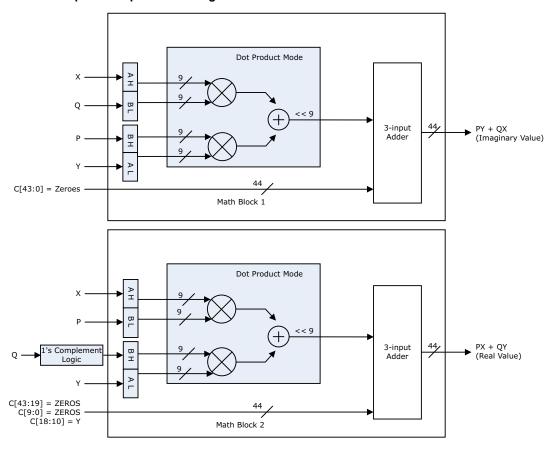

| Figure 88 | 9-Bit Complex Multiplication Using DOTP Mode                    |     |

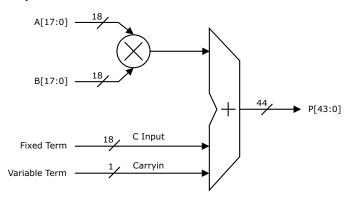

| Figure 89 | Rounding Using C-Input and CARRYIN                              |     |

| Figure 90 | Rounding and Trimming of the Final Sum                          |     |

| Figure 91 | Rounding and Trimming of the Final Sum                          |     |

| Figure 92 | LSRAM Configurator                                              | 101 |

| Figure 93 | μSRAM Configurator                                              | 106 |

| Figure 94 | Math Block Configurator                                         | 109 |

# **Tables**

| Table 1  | Fabric Resources for RTG4 FPGA Devices                              | 4     |

|----------|---------------------------------------------------------------------|-------|

| Table 2  | Number of Logic Elements                                            |       |

| Table 3  | ILs for Embedded Hard IP Blocks                                     | 7     |

| Table 4  | Fabric Array Coordinate Systems                                     | 9     |

| Table 5  | RTG4 LSRAM, µSRAM, and µPROM Features                               | 11    |

| Table 6  | RTG4 Embedded Memory Resources                                      | 12    |

| Table 7  | Port List for LSRAM                                                 | 13    |

| Table 8  | Data Width Configurations For Dual-port Mode                        | 14    |

| Table 9  | Block Select Operation                                              | 14    |

| Table 10 | Dual-Port Byte Write Enables Settings                               | 15    |

| Table 11 | Data Width Configurations for Two-Port Mode                         | 17    |

| Table 12 | Block Select Operation in Two-Port Mode                             | 17    |

| Table 13 | Two-Port Byte Write Enables For x36 Write Width                     | 17    |

| Table 14 | ECC Available Mode                                                  | 21    |

| Table 15 | LSRAM Error Flag Status                                             | 22    |

| Table 16 | Port List for the DPSRAM Configurator                               |       |

| Table 17 | Port List for the TPSRAM Configurator                               | 28    |

| Table 18 | LSRAM Configurator Component Timing and Ports                       |       |

| Table 19 | Functional Timing Waveforms                                         | 42    |

| Table 20 | ECC Errors Flag                                                     |       |

| Table 21 | Port List for µSRAM                                                 |       |

| Table 22 | μSRAM Error Flag Status                                             | 62    |

| Table 23 | Collision Scenarios                                                 |       |

| Table 24 | Port List for the μPROM Configurator                                |       |

| Table 25 | Resources for RTG4 Devices                                          | 80    |

| Table 26 | Truth Table for Propagating Operand D of the Adder or Accumulator   |       |

| Table 27 | Rounding Examples                                                   |       |

| Table 28 | Depth × Width Mode Selection                                        |       |

| Table 29 | Write/Read Operation Select                                         |       |

| Table 30 | Address Bus Used and Unused Bits                                    |       |

| Table 31 | Data Input Buses Used and Unused Bits                               |       |

| Table 32 | Data Output Buses Used and Unused Bits                              | . 103 |

| Table 33 | Block-Port Select                                                   |       |

| Table 34 | Width/Depth Mode Selection                                          |       |

| Table 35 | Address Buses Used and Unused Bits                                  |       |

| Table 36 | Data Input Bus Used and Unused Bits                                 | . 107 |

| Table 37 | Data Output Used and Unused Bits                                    |       |

| Table 38 | Block-Port Select                                                   |       |

| Table 39 | Truth Table for A_ADDR, B_ADDR, A_DOUT, and B_DOUT Registers        |       |

| Table 40 | Ports List of Math Block Configurator                               |       |

| Table 41 | Truth Table for Control Registers ARSHFT17, CDSEL, FDBKSEL, and SUB |       |

| Table 42 | Truth Table - Data Registers A, B, C, CARRYIN, P, and OVFL_CARRYOUT |       |

| Table 43 | Truth Table - Propagating Data to Operand D                         | . 115 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

### 1.1 Revision 6.0

The following is a summary of changes in this revision.

- Updated the information about the SB\_CORRECT and DB\_DETECT flags in LSRAM ECC, page 21.

- Removed the note about LSRAMs not being inferred in the ECC mode by the Synthesis tool (RTL Inference during Synthesis, page 63).

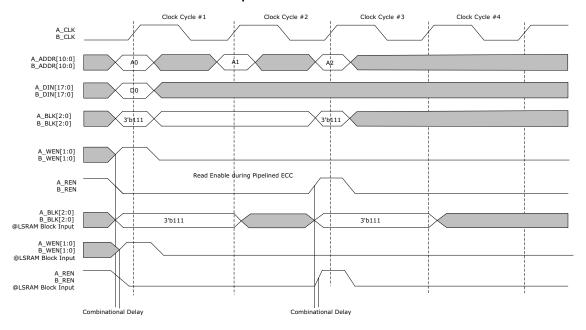

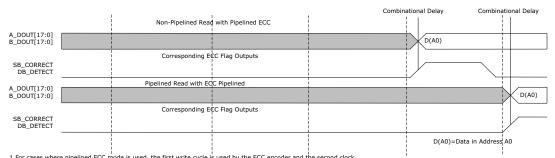

- Updated the LSRAM timing diagrams, see Figure 13, page 18 and Functional Timing Waveforms, page 42.

- LSRAM endianness information was added, see LSRAM, page 12.

- Added a note to describe the ECC behavior for uncorrectable errors, see LSRAM ECC, page 21.

- Updated Two-Port Data Width Configuration, page 17.

- Added all supported memory file formats for µPROM client, see Add Clients to System, page 71.

## 1.2 Revision 5.0

The following is a summary of changes in this revision.

- Added information about the LSRAM hold time violation after read during pipelined-ECC mode, see LSRAM Hold Time Violation, page 31.

- Updated the data widths supported by LSRAM in Two-Port Mode, see Table 11, page 17.

- Add Collision Behavior, page 67.

- Added the x36 data flow of the two port LSRAM, see Figure 12, page 16.

- Added Debugging LSRAMs Using SmartDebug, page 51.

- Added LSRAM Configurator Component Timing and Ports, page 34.

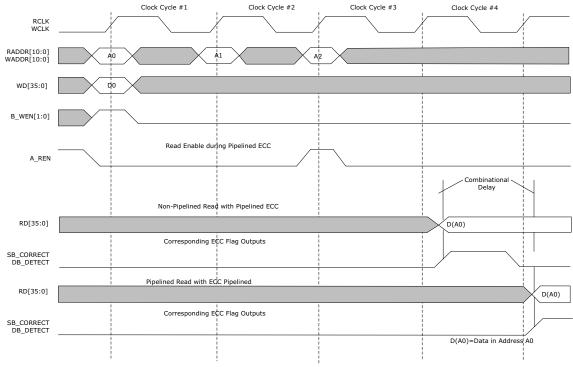

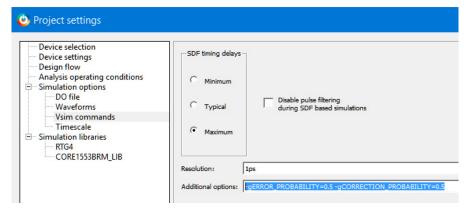

- Added Simulating ECC Errors in LSRAM, page 47.

- Removed x36 and x9 read port and write data width support respectively from Table 11, page 17 as it is not supported now. For more information, see *Customer Advisory Notice (CAN18002.3*).

- · Added Two-Port Block Select Operation, page 17.

## 1.3 **Revision 4.0**

The following is a summary of changes in this revision.

- When clock is at negative edge, the inversion will be absorb into the SLE with out effecting output polarity.

- During ECC pipeline mode, back to back read, write operations are not allowed.

- During accumulation, any error caused by a radiation-induced event (SEU/SET) stays in the accumulator until it is reset or purged.

- Read-before Write and Write-feed through modes are not supported.

- Updated Figure 14, page 19 and Table 14, page 21.

- The following register names are updated:

- A IN BYPASS changed to A ADD BYPASS

- B\_IN\_BYPASS changed to B\_ADD\_BYPASS

# 1.4 **Revision 3.0**

The following is a summary of changes in this revision.

- The I/O section is removed from this user guide and published as a separate user guide. See UG0741: RTG4 FPGA I/O User Guide.

- Removed BUSY signal reference from µPROM, page 68.

- Removed LSRAM write feed-through information.

- Updated Table 5, page 11 with μPROM data bus width details.

- Updated LSRAM ECC, page 21.

- Updated Figure 94, page 109.

- · Added Using LSRAM in a Design, page 22.

- Added Using µSRAM in a Design, page 63.

- Added µPROM Configurator, page 70.

- Updated LSRAM Read Operation, page 18.

- Added Use Model: LSRAM Write-Feed-Through using Fabric Logic, page 49.

- Updated Read Enable information in RTG4 Dual-Port LSRAM Configurator, page 23.

- Removed RT4G075 device reference from the document.

# 1.5 **Revision 2.0**

The following is a summary of changes in this revision.

- · Updated the document with FTC inputs.

- Updated Features section and Table 5-3.

- Updated µSRAM ECC, page 62.

- Updated Table 6-3.

- Updated Table 6-10.

- Updated Low Voltage CMOS (LVCMOS) section.

- Added Cold Sparing and Dedicated Global I/Os sections.

- Updated Programmable Slew Rate Control section.

- Added µPROM, page 68.

- Replaced GSR\_N signal with ARST\_N.

# 1.6 **Revision 1.0**

The first publication of this document.

# 2 Fabric Overview

RTG4™ FPGAs feature a fourth-generation FPGA fabric with radiation tolerance. Fabric is the programmable logic section of the RTG4 FPGA, which the user configures with VHDL or Verilog. The RTG4 FPGA fabric consists of the following resources:

- Logic element: These are basic building blocks in the RTG4 FPGA.

- Embedded memory blocks: These include large SRAM (LSRAM), microSRAM (μSRAM), and microPROM (μPROM).

- Math blocks: These have a built-in multiplier and adder.

The Libero® System-on-Chip (SoC) software (or third-party synthesis tools) automatically infers these logic elements, embedded memories, and math blocks from the user's register transfer level (RTL) code. For more information about the Libero SoC Classic and Enhanced Constraint design flow, see the *Libero SoC Classic Constraint Flow User Guide* and *Libero SoC for Enhanced Constraint Flow(ECF) User Guide*.

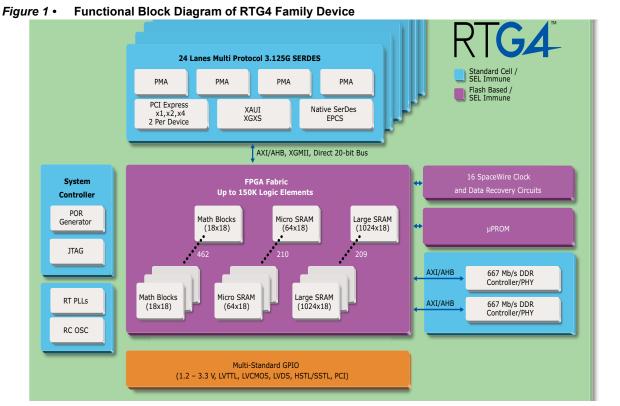

The following figure is a top-level functional block diagram of the RTG4 FPGA family. The highlighted fabric block is described in this document.

Microsemi Proprietary UG0574 Revision 6.0

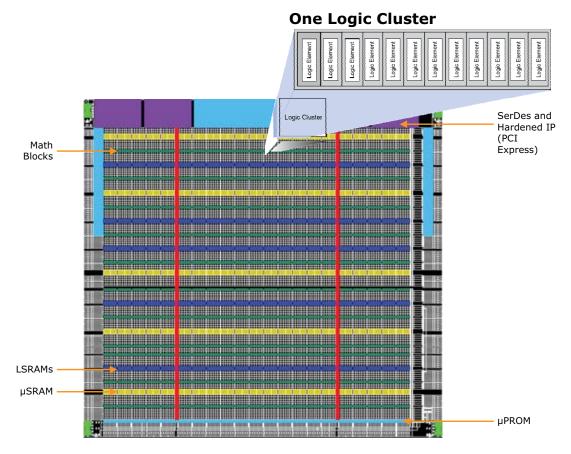

The following figure shows the fabric layout. The FPGA logic resources are displayed as logic clusters (LC). Each LC consists of 12 logic elements (LE). The embedded memory blocks and math blocks are arranged in rows.

Figure 2 • Fabric Layout

The following table lists the available fabric resources in the RTG4 family devices.

Table 1 • Fabric Resources for RTG4 FPGA Devices<sup>1</sup>

| Resources                   | RT4G150 |

|-----------------------------|---------|

| Logic elements              | 120,108 |

| Interface logic             | 31,716  |

| Total logic elements        | 151,824 |

| LSRAM blocks (24.5-Kb each) | 209     |

| Total LSRAM bits (Mb)       | 5       |

| μSRAM blocks (1.5-Kb each)  | 210     |

| Total µSRAM bits (Kb)       | 315     |

| Total RAM (Mb)              | 5.3     |

| Math blocks (18 × 18 MACC)  | 462     |

| μPROM (Bits)                | 374,400 |

<sup>1. 1</sup> Kb = 1024 bits, 1 Mb = 1024 Kb.

# 3 Logic Elements and Routing

The RTG4 FPGA fabric has an array of logic elements grouped in clusters connected via hierarchical routing structures. These clusters are arranged in rows and are used to implement sequential and combinational logic. The following table lists the available logic elements in RTG4 devices.

Table 2 • Number of Logic Elements

| Devices                      | RT4G150 |

|------------------------------|---------|

| Logic elements               | 120,108 |

| Interface logic <sup>1</sup> | 31,716  |

| Total logic elements         | 151,824 |

See Interface Logic, page 7 for more information.

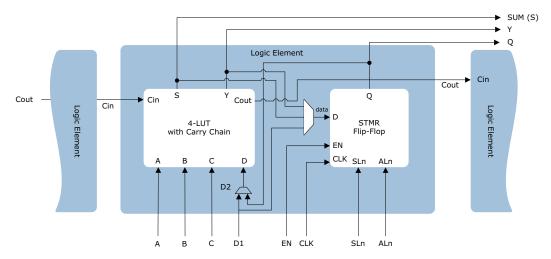

# 3.1 Logic Element

The logic element (LE) is the basic building block of the RTG4 FPGA. The logic element is fracturable – the LUT can be independently used without flip-flop or flip-flop can be used without LUT. The logic element consists of:

- 4-LUT with carry chain

- STMR-D flip-flop

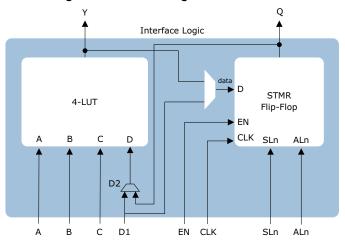

Figure 3 • Functional Block Diagram of Logic Element

# 3.1.1 4-Input LUT with Carry Chain

The 4-input LUT with carry chain can be configured to implement any 4-input combinational logical function or arithmetic function. The 4-input LUT generates the output (Y) depending on the four inputs—A, B, C, and D. The carry chain is implemented using a 3-bit carry-look-ahead circuit. This circuit is connected between various logic elements by carry chain input (Cin) signal and carry chain output (Cout) signal. When the LUT is used to implement arithmetic functions, the carry chain input (Cin) is used with LUT output to generate the sum (S) output. However, for non-arithmetic functions, the sum (S) output can still be used as an output along with the other output (Y).

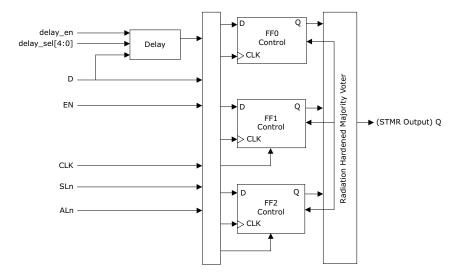

# 3.1.2 STMR-D Flip-Flop

Each logic element has a Single-event Transient (SET)-mitigated asynchronous Self-corrected Triple Module Redundancy (STMR)-D flip-flop, which can be used as a sequential logic element. The STMR-D flip-flop can be configured as a register. The following figure shows the functional block diagram of STMR-D flip-flop. Each STMR-D flip-flop has Asynchronous majority voter logic that ensures Single-event Upset (SEU) immunity within the timeline of an SET pulse width. Its TMR mitigates the SEU errors.

The STMR-D flip-flop has the following ports:

- Asynchronous load (ALn)

- Synchronous load (SLn)

- Data input (D)

- Enable (EN)

- Clock input (CLK)

- Data Output (Q)

- delay en

- delay sel[4:0]

Figure 4 • Functional Block Diagram of STMR-D Flip-Flop

ALn can be used as single global asynchronous set or reset signal of each fabric STMR-D flip-flops. It sets or resets the register depending on configuration. SLn can be used as synchronous set or reset signal of each fabric STMR-D flip-flop. It sets or resets the register depending on configuration. The data input (D) of the STMR-D flip-flop can be provided from the direct input or from the outputs of the 4-input LUT inside the logic element. When the design uses falling edge clocking, the Libero SoC Compile step optimizes the design netlist using a technique called "bubble pushing". As a result a discrete inverter instance can be removed from the netlist and the inversion property is pushed onto the CLK input pin of the SLE macro. D has a programmable delay circuit to derive a delayed data for SET mitigation. This delay circuit can be enabled or disabled using the delay\_en signal. The delay\_sel[4:0] signal decides the delay value for maximum SET glitch width, which can be filtered out. The radiation majority voter logic outputs the final output (Q) from the three flip-flops.

STMR-D flip-flops support Mitigated SET and Non-mitigated SET modes. These modes can be set by using the Libero SoC tool. For more information about how to set mitigation modes, see the *Libero SoC Classic Constraint Flow User Guide* and *Libero SoC for Enhanced Constraint Flow(ECF) User Guide*. Non-mitigated timing mode is significantly faster than the mitigated timing mode. Setting the fabric flip-flops in critical timing paths to Non-mitigated mode improves the application speed significantly and reduces the radiation tolerance nominally.

# 3.1.3 Interface Logic

The RTG4 embedded hard IP blocks (LSRAM,  $\mu$ SRAM, and math blocks) are connected to the fabric through interface logic (ILs). This interface logic element is structurally similar to a logic element with 4-input LUT, STMR-D flip-flop, and without a dedicated carry chain. Interface logic elements are also TMR-D and have same SET mitigation as Logic Elements. Each embedded hard IP block is associated with 36 interface logic elements. The following table lists the total number of ILs associated with each embedded hard IP block.

Table 3 • ILs for Embedded Hard IP Blocks

|                       | RT4G150          |               |  |

|-----------------------|------------------|---------------|--|

| Resources             | Number of Blocks | Number of LEs |  |

| LSRAM                 | 209              | 7,524         |  |

| μSRAM                 | 210              | 7,560         |  |

| Math block            | 462              | 16,632        |  |

| Total interface logic | 881              | 31,716        |  |

Figure 5 • Functional Block Diagram of Interface Logic

Figure 6 • LSRAM/µSRAM/Math Block Interfacing with ILs in a Row

If an embedded hard block is used by the target design, the interface logic element is used to connect the I/Os of the embedded hard IP block to the fabric routing. If an embedded hard IP block is not used by the design, the interface logic can be used as normal logic elements to implement combinational and sequential circuits. The preceding figure shows the interface logic connected to the embedded hard block.

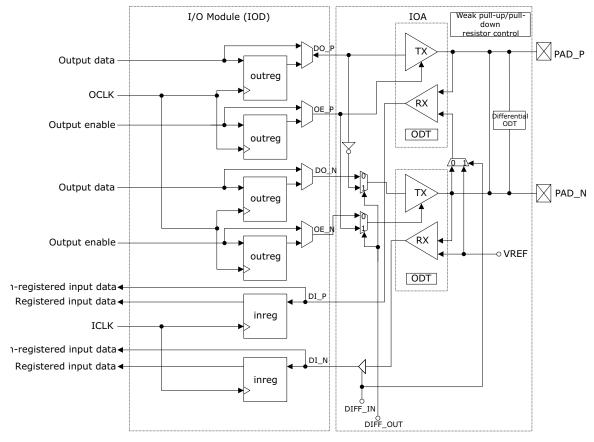

#### 3.1.4 I/O Element

The I/O element includes the I/O Digital (IOD) circuitry and the associated routing interface. Each user I/O pad is connected to its own dedicated I/O element. The I/O element interfaces the user I/Os with the fabric routing and enables the routing of external signals coming in through the I/Os to reach all the logic elements. The I/O element also enables the internal signals to reach the I/Os.

The following figure shows the functional diagram of the complete I/O element with the IOD and I/O Analog (IOA). The IOD circuitry consists of the following:

- **Input registers**: Used to register the inputs received from the I/Os. These registers allow capturing the input signals and synchronizing them to the design clock.

- Output registers: Used in the I/O element for registering the output signals at I/Os for better design

performance. These registers provide the registered version of the output signals to the I/Os.

- Output Enable registers: Act as a control signal for the output, if the I/O is configured as a tristate or bi-directional I/O.

- Routing multiplexers (MUXes): These routing MUXes are used to connect logic elements.

All these registers in the I/O modules are similar to the STMR-D-flip-flop available in the logic element. For a signal bus, these registers ensure that all the signal bus bits are synchronized to the clock signal when sent out through I/Os. For more information on IOA, see *UG0741: RTG4 FPGA I/Os User Guide*.

Figure 7 • Functional Block Diagram of I/O Element

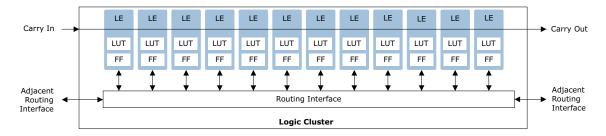

# 3.2 Logic Cluster

The logic elements in the RTG4 FPGA are organized in clusters. The logic cluster is a group of 12 LEs or 12 ILs. Each logic cluster is connected by a routing interface comprising MUXes and buffers. This routing interface connects to its associated LEs and the adjacent routing interfaces. Each routed signal is driven by a unique logic element output or by a routing MUX. All the logic elements are interconnected with feedback from outputs to inputs.

The following figure shows the logic cluster with routing interface.

Figure 8 • Logic Cluster

# 3.3 Routing Architecture

The RTG4 FPGA fabric routing architecture is a hierarchical grouping of fabric resources arranged in clusters. Each logic cluster has one routing interface that connects the LEs within a cluster and also to the routing interfaces of adjacent clusters.

The RTG4 device routing interface has two types of routings—intra cluster routing and inter cluster routing. The intra-cluster routing connects the LEs inside a cluster and inter-cluster routing connects multiple clusters. The intra-cluster routing has lower propagation delay compared to inter-cluster routing. When connecting the adjacent clusters, inter-cluster routing also has additional short routing connections for faster routing.

RTG4 FPGAs have vertical and horizontal routing stripes for global network. This global network is designed to route clocks and reset signals across the fabric with low skew, and is designed to support multiple clock domains. This global network can also be used for other high fan-out signals, such as enables and resets. See *UG0586: RTG4 FPGA Clocking Resources User Guide* for more information about global network.

Each 4-input LUT, D-type flip-flop, carry chain, LSRAM,  $\mu$ SRAM, and math block has individual X-Y coordinates. If the user design requires manual placement of these blocks, it is possible to set region constraints using these coordinates. The coordinates are measured from the lower left (0, 0) to the top right corner (X, Y), where X, Y values vary as per the device.

For more information about using coordinates for region/placement constraints, see the *Chip Planner User's Guide* or Libero SoC Online Help.

The array coordinates are measured from the bottom left corner to the top right corner of the FPGA fabric. The following table provides the array coordinates of logical blocks and embedded hard blocks of the RTG4 devices. For more information about how to use array coordinates for region or placement constraints, see *Libero SoC Classic Constraint Flow User Guide* and *Libero SoC for Enhanced Constraint Flow(ECF) User Guide* or online help (available in the software).

Table 4 • Fabric Array Coordinate Systems

|         | Logic Elements |                | μSRAM                                                | LSRAM  | Math Blocks                                                                                                          |  |

|---------|----------------|----------------|------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|--|

| Device  | Minimum (X, Y) | Maximum (X, Y) | (X, Y)                                               | (X, Y) | (X, Y)                                                                                                               |  |

| RT4G150 | 0, 0           | 1535, 311      | (0, 56), (0,125),<br>(0, 182), (0, 212),<br>(0, 266) | , ,    | (0, 17), (0, 41), (0, 71),<br>(0, 80), (0, 110),<br>(0, 140), (0, 167),<br>(0, 197), (0, 221),<br>(0, 251), (0, 281) |  |

# 3.4 Libero Compile Report - Fabric Resources

The compile report contains fabric resource utilization and the total number of resources available. See the following figure for a sample compile report for RT4G150. This report provides the number of 4LUTs, DFFs,  $\mu$ SRAMs, LSRAMs, math blocks, I/O, DLLs, PLLs, transceivers, and globals used in a design. It also contains the detail logic resource usage that contains the additional 4LUTs and DFFs required for RAMs and MACC interface logic.

Figure 9 • Sample Compile Report for RT4G150

# **Resource Usage**

| Туре                   | Used | Total  | Percentage |

|------------------------|------|--------|------------|

| 4LUT                   | 8100 | 151824 | 5.34       |

| DFF                    | 8267 | 151824 | 5.45       |

| I/O Register           | 0    | 2154   | 0.00       |

| User I/O               | 43   | 718    | 5.99       |

| Single-ended I/O       | 39   | 718    | 5.43       |

| Differential I/O Pairs | 2    | 359    | 0.56       |

| RAM64x18               | 4    | 210    | 1.90       |

| RAM1K18                | 3    | 209    | 1.44       |

| MACC                   | 32   | 462    | 6.93       |

| H-Chip Globals         | 9    | 48     | 18.75      |

| ccc                    | 1    | 8      | 12.50      |

| RCOSC_50MHZ            | 1    | 1      | 100.00     |

| SERDESIF Blocks        | 2    | 6      | 33.33      |

| FDDR                   | 0    | 2      | 0.00       |

| GRESET                 | 1    | 1      | 100.00     |

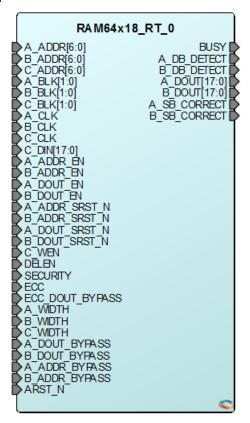

# 4 Embedded Memory Blocks

The RTG4 FPGA fabric has the following memory blocks:

- LSRAM: The embedded 24-Kb SRAM blocks are arranged in multiple rows within the fabric and can

be accessed through the fabric routing architecture. The LSRAMs can be operated in dual-port or

two-port modes. The following table lists the number of available LSRAM blocks depending on the

specific RTG4 device. LSRAM blocks are used for storing large data with Error-correcting Code

(ECC) and Single-event Transient (SET) mitigation options.

- μSRAM: The embedded 1.5-Kb SRAM blocks are arranged in multiple rows within the fabric and can be accessed through the fabric routing architecture. The following table lists the number of available μSRAM blocks depending on the specific RTG4 device. Embedded μSRAM blocks are used for storing small data with ECC and SET mitigation options.

- μPROM: The embedded non-volatile PROM is arranged in a single row at the bottom of the fabric and is read only through the fabric interface. The μPROM can be loaded only during device programming.

The following table lists the LSRAM, µSRAM, and µPROM features.

Table 5 • RTG4 LSRAM, µSRAM, and µPROM Features

| Feature         | LSRAM                                                                                          | μSRAM                                   | μPROM                            |

|-----------------|------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------|

| Memory size     | 24,576 bits/block                                                                              | 1,536 bits/block                        | 374,400 bits (total memory size) |

| Data bus width  | 512 × 36, 1K × 18, 2K × 12,<br>2K × 9 <sup>1</sup>                                             | 64 × 18, 128 × 12, 128 × 9 <sup>2</sup> | 16K × 36                         |

| Number of ports | 2 read/write ports in dual port mode                                                           | 2 read ports, 1 write port              | 1 read port                      |

| Memory modes    | True dual-port <sup>3</sup> and two-port                                                       | Three-port                              | Single-port                      |

| Read operation  | Synchronous                                                                                    | Synchronous/Asynchronous                | Synchronous                      |

| Write operation | Simple write                                                                                   | Simple write                            | Only during device programming   |

| ECC             | Available for ×18 data widths in dual-port mode and for ×18, ×36 data widths in two-port mode. | Available for ×18 data widths           |                                  |

Only the ×12 port width accesses the entire address space of the 24,576 bits. The ×9, ×18, and ×36 address space is limited to 18,432 bits.

**Note:** In specific configurations, x9 and x12 dual-port LSRAMs undergo compile transformations by Libero SoC. See, *Customer Advisory Notice (CAN) 18002.3*. Compile transformations occur when opening a design created by an older version of Libero or when compiling a design that contains manually instantiated LSRAM primitive macros.

<sup>2.</sup> Only the ×12 port width accesses the entire address space of the 1536 bits. The ×9 and ×18 address space is limited to 1152 bits.

<sup>3.</sup> True dual-port is not available for 2K x 12 and 2K x 9.

The following table lists the embedded memory resources available in RTG4 devices.

Table 6 • RTG4 Embedded Memory Resources

| Resources                   | RT4G150 |

|-----------------------------|---------|

| 24.5-Kb LSRAM blocks        | 209     |

| LSRAM (Mb) <sup>1</sup>     | 5       |

| μSRAM blocks (1.5-Kb each)  | 210     |

| μSRAM (Kb) <sup>1</sup>     | 315     |

| Total RAM (Mb) <sup>1</sup> | 5.3     |

| μPROM (Bits)                | 374,400 |

<sup>1. 1</sup> Kb = 1024 bits, 1 Mb = 1024 Kb.

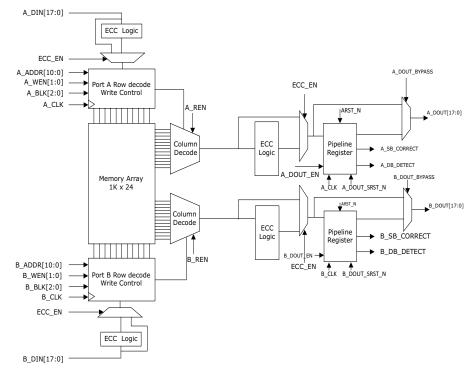

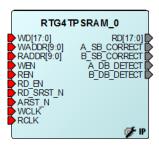

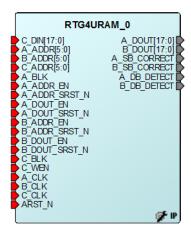

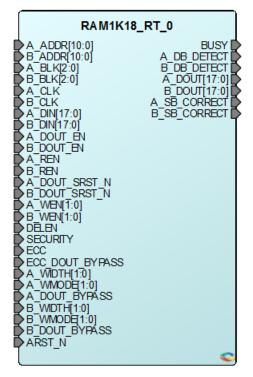

# 4.1 LSRAM

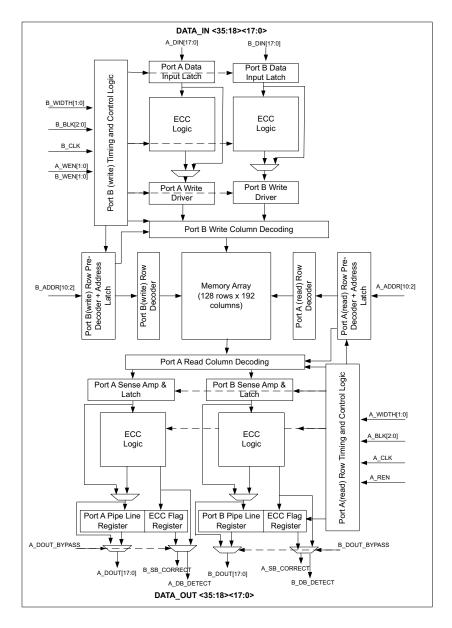

Each LSRAM has two independent ports—port A and port B, as shown in the following figure. Both these ports support write and read operations and can be configured in dual-port mode or two-port mode depending on the data width and access pattern requirement. LSRAMs follow the little-endian system.

Figure 10 • Functional Block Diagram of LSRAM

The following table lists the port list for LSRAM.

Table 7 • Port List for LSRAM

| Port Name               | Direction | Type <sup>1</sup> | Polarity    | Description                                                     |

|-------------------------|-----------|-------------------|-------------|-----------------------------------------------------------------|

| Port A                  |           |                   |             |                                                                 |

| A_ADDR[10:0]            | Input     | Dynamic           |             | Port A address                                                  |

| A_BLK[2:0]              | Input     | Dynamic           | Active high | Port A block selects                                            |

| A_CLK                   | Input     | Dynamic           | Rising edge | Port A clock                                                    |

| A_DIN[17:0]             | Input     | Dynamic           |             | Port A write-data                                               |

| A_DOUT[17:0]            | Output    | Dynamic           |             | Port A read-data                                                |

| A_WEN[1:0] <sup>2</sup> | Input     | Dynamic           | Active high | Port A write-enables (per byte)                                 |

| A_REN                   | Input     | Dynamic           | Active high | Port A read-enable                                              |

| A_WIDTH[1:0]            | Input     | Static            |             | Port A width/depth mode select                                  |

| A_WMODE[1:0]            | Input     | Static            | Active high | Port A write mode select. Must be 2'b00.                        |

| A_DOUT_BYPASS           | Input     | Static            | Active low  | Port A output pipeline bypass mode                              |

| A_DOUT_EN               | Input     | Dynamic           | Active high | Port A read pipeline register enable                            |

| A_DOUT_SRST_N           | Input     | Dynamic           | Active low  | Port A read pipeline synchronous-reset                          |

| A_SB_CORRECT            | Output    | Dynamic           | Active high | Port A 1-bit error correction flag                              |

| A_DB_DETECT             | Output    | Dynamic           | Active high | Port A 2-bit error detection flag                               |

| Port B                  |           |                   |             |                                                                 |

| B_ADDR[10:0]            | Input     | Dynamic           |             | Port B address                                                  |

| B_BLK[2:0]              | Input     | Dynamic           | Active high | Port B block selects                                            |

| B_CLK                   | Input     | Dynamic           | Rising edge | Port B clock                                                    |

| B_DIN[17:0]             | Input     | Dynamic           |             | Port B write-data                                               |

| B_DOUT[17:0]            | Output    | Dynamic           |             | Port B read-data                                                |

| B_WEN[1:0] <sup>2</sup> | Input     | Dynamic           | Active high | Port B write-enables (per byte)                                 |

| B_REN                   | Input     | Dynamic           | Active high | Port B read-enable                                              |

| B_WIDTH[1:0]            | Input     | Static            |             | Port B width/depth mode select                                  |

| B_WMODE[1:0]            | Input     | Static            | Active high | Port B write mode select. Must be 2'b00.                        |

| B_DOUT_BYPASS           | Input     | Static            | Active low  | Port B pipeline register select                                 |

| B_DOUT_EN               | Input     | Dynamic           | Active high | Port B pipeline register enable                                 |

| B_DOUT_SRST_N           | Input     | Dynamic           | Active low  | Port B pipeline synchronous-reset                               |

| B_SB_CORRECT            | Output    | Dynamic           | Active high | Port B 1-bit error correction flag                              |

| B_DB_DETECT             | Output    | Dynamic           | Active high | Port B 2-bit error detection flag                               |

| Common Signals          |           |                   |             |                                                                 |

| ARST_N                  | Input     | Global            | Active low  | Pipeline registers asynchronous-reset                           |

| ECC_EN                  | Input     | Static            | Active high | ECC enable, turns on the ECC encoders, decoders, and registers. |

| ECC_DOUT_BYPASS         | Input     | Static            | Active low  | ECC pipeline bypass                                             |

| DELEN                   | Input     | Static            | Active high | SET mitigation                                                  |

| SECURITY                | Input     | Static            | Active high | Lock access to system controller <sup>3</sup>                   |

| ·                       |           |                   |             |                                                                 |

Table 7 • Port List for LSRAM (continued)

| Port Name | Direction | Type <sup>1</sup> | Polarity    | Description                                                                                                |

|-----------|-----------|-------------------|-------------|------------------------------------------------------------------------------------------------------------|

| BUSY      | Output    | Dynamic           | Active high | Busy signal from the system controller. This is high while system controller accessing LSRAM. <sup>3</sup> |

<sup>1.</sup> Static inputs are defined during the design time and must be tied to logic 0 or 1.

### 4.1.1 Dual-Port Mode

The LSRAM block can be configured as a true dual-port SRAM with independent write and read ports. Write and read operations can be performed from both the ports (A and B) independently at any location as long as there is no write collision. The LSRAM block does not have built-in write collision detection circuit. Simultaneous read and write operations from both ports to the same address location results in correct data written into the memory, but does not guarantee correct read data. Each port has a unique address, data in, data out, clock, block select, write enable, pipeline registers.

### 4.1.1.1 Dual-Port Data Width Configuration

In dual-port mode, both ports A and B have maximum data width of ×18. Each port can be configured in multiple data widths. The configuration of one port has a corresponding configuration for the other port, as shown in the following table. A\_WIDTH indicates the read width and B\_WIDTH indicates the write width.

Table 8 • Data Width Configurations For Dual-port Mode

| A_WIDTH | B_WIDTH |

|---------|---------|

| ×9      | ×18     |

| ×18     | ×18     |

#### 4.1.1.2 **Dual-Port Block Select Operation**

In dual-port mode, to perform two independent write and read operations (on port A or port B or both) the block select signal is required. The following table lists the block select operation for port A and port B. When the pipeline registers are enabled, the effect of the block select at the outputs is delayed by one clock cycle, see Figure 11.

Table 9 • Block Select Operation

| A_BLK[2:0]      | B_BLK[2:0]      | Operation                                                                                       |

|-----------------|-----------------|-------------------------------------------------------------------------------------------------|

| Any one bit = 0 | Any one bit = 0 | No operation on port A or B. The data output A_DOUT[17:0] and B_DOUT[17:0] will be forced zero. |

| Any one bit = 0 | 111             | Read or write operation on port B. A_DOUT[17:0] will be forced zero.                            |

| 111             | Any one bit = 0 | Read or write operation on port A. B_DOUT[17:0] will be forced zero.                            |

| 111             | 111             | Read or write operation on both ports A and B.                                                  |

<sup>2.</sup> If the LSRAM block is configured for data width of x9 or ECC, both the bits of A\_WEN and B\_WEN must be tied to logic 1 and must not be dynamically changed.

<sup>3.</sup> For more information about BUSY signal from system controller, see UG0576: RTG4 FPGA System Controller User Guide.

Figure 11 • Block Select Inputs for Dual-Port Mode

### 4.1.1.3 Dual-Port Byte Write Enables

The byte write enables (A\_WEN[1:0] and B\_WEN[1:0]) enable writing individual bytes of data (9 MSB or 9 LSB) for the ×18 width. The byte write enables for port A (A\_WEN[1:0]) enable A\_DIN[17:9] and A\_DIN[8:0] respectively. The byte write enables for port B (B\_WEN[1:0]) enable B\_DIN[17:9] and B\_DIN[8:0] respectively. Writing one byte at a time to the LSRAM is not compatible with the built-in ECC logic, as per Table 14, page 21. The complete data word must be written by setting both WEN bits high when using the built-in LSRAM ECC.

If all byte write enables are low, then port A or port B is considered to be in read mode and any read operations are controlled by the read enables (A\_REN and B\_REN).

The following table lists the byte write enable settings for port A and port B.

Table 10 • Dual-Port Byte Write Enables Settings

| Depth x Width | A_WEN / B_WEN | Result                    |  |

|---------------|---------------|---------------------------|--|

| 2K×9, 1K×18   | 00            | Perform a read operation  |  |

| 2K×9          | 11            | Perform a write operation |  |

| 1K×18         | 01            | Write [8:0]               |  |

|               | 10            | Write [17:9]              |  |

|               | 11            | Write [17:0]              |  |

#### 4.1.1.4 Dual-Port Read Enable

The read enable signals, A\_REN and B\_REN, perform the read operation on port A and port B, unless any one bit of that port's block select is low which forces the data outputs to low. When read enable is low, the data outputs retain their previous state and no dynamic read power is consumed on that port. When read enable is high, LSRAM performs read operation and consumes read power.

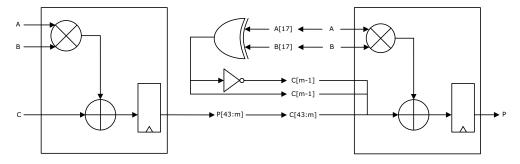

#### 4.1.2 Two-Port Mode

The LSRAM block can be configured as a two-port SRAM with port A dedicated to read operations and port B dedicated to write operations. For data widths greater than ×18, the read port borrows the port B data output signals, similarly write port borrows the port A data input signals.

Figure 12 illustrates the two-port LSRAM data-flow in the x36 data width configuration.

Figure 12 • Two Port Mode x36 Data Flow

### 4.1.2.1 Two-Port Data Width Configuration

In two-port mode, the maximum data width is ×36. Each port can be configured in multiple data widths. The configuration of read port has a corresponding configuration for the write port, as shown in the following table.

Table 11 • Data Width Configurations for Two-Port Mode

| Read Port | Write Port   |

|-----------|--------------|

| ×9        | ×9, ×18, ×36 |

| ×12       | ×12          |

| ×18       | ×9, ×18, ×36 |

| ×36       | ×18, ×36     |

Note: Libero SoC performs compile transformations on two-port LSRAMs configured for x9 and x12 write widths where the writes occur on port B. For more information, see *Customer Advisory Notice* (*CAN18002.3*). These configurations will have the read and write ports swapped so that writes occur on port A instead of port B.

### 4.1.2.2 Two-Port Block Select Operation

In the two-port mode Port A is the read port and Port B is the write port. Table 12, page 17 lists the Block select values required to enable the read and write operation on Port A and Port B respectively.

Table 12 • Block Select Operation in Two-Port Mode

| A_BLK[2:0] Setting         | Read Operation                                                                                    | B_BLK[2:0] Setting | Write Operation                   |

|----------------------------|---------------------------------------------------------------------------------------------------|--------------------|-----------------------------------|

| A_BLK[2:0]=111             | Read operation from Port A.                                                                       | B_BLK[2:0]=111     | Write operation at the Port B.    |

| Any bit of A_BLK[2:0] is 0 | No read operation from Port A. The data outputs A_DOUT[17:0] and B_DOUT[17:0] are forced to zero. | ,                  | No write operation at the Port B. |

#### 4.1.2.3 Two-Port Byte Write Enables

The byte write enables (A\_WEN and B\_WEN) enable writing individual bytes of data (9 MSB or 9 LSB) for ×9 width, ×18, and ×36 data widths. For ×36 write-width, the byte write enables for the corresponding data is used to enable each of the four bytes, that is, byte write enables for port A enable A\_DIN[17:9] and A\_DIN[8:0] and byte write enables for port B enable B\_DIN[17:9] and B\_DIN[8:0]. Writing one byte at a time to the LSRAM is not compatible with the built-in ECC logic, as per Table 14, page 21. The complete data word must be written by setting all WEN bits high when using the built-in LSRAM ECC.

The following table lists the byte write enable settings for port A and port B.

Table 13 • Two-Port Byte Write Enables For x36 Write Width

| Depth x Width | A_WEN/B_WEN  | Result            |

|---------------|--------------|-------------------|

|               | B_WEN[0] = 1 | Write B_DIN[8:0]  |

| 512×36 –      | B_WEN[1] = 1 | Write B_DIN[17:9] |

|               | A_WEN[0] = 1 | Write A_DIN[8:0]  |

| •             | A_WEN[1] = 1 | Write A_DIN[17:9] |

#### 4.1.2.4 Two-Port Read Enable

The read enable signals, A\_REN and B\_REN, perform the read operation on port A and port B, unless any one bit of A\_BLK is low which forces the data outputs to low. When read enable is low, the data outputs retain their previous state and no dynamic read power is consumed on that port. When read

enable is high, LSRAM performs read operation and consumes read power. When read width is x36, LSRAM port B read enable (B REN) is tied to port A read enable (A REN).

## 4.1.3 LSRAM Read Operation

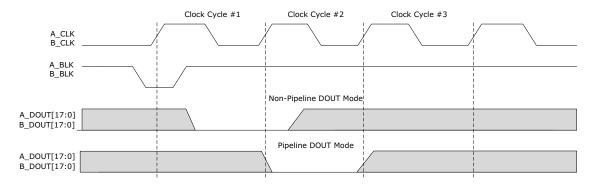

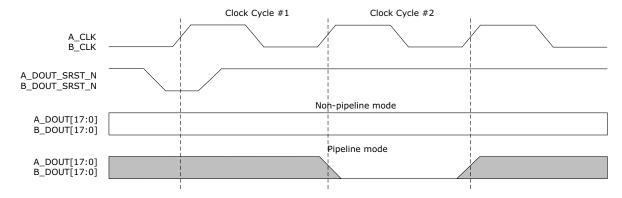

LSRAM supports both pipelined and non-pipelined read operations. In pipelined read operation, the output data is registered at the pipeline registers; hence, the data is available on the corresponding data output on the next clock cycle. Figure 13 shows the pipelined and non-pipelined read timing.

In non-pipelined read operation, the pipeline registers are bypassed with data available on the corresponding output in the same clock cycle. During this operation, LSRAM can generate glitches on the data output buses. Therefore, it is recommended to use LSRAM with pipeline registers to avoid glitches.

**Note:** Enable pipeline mode to achieve high performance. This will pipeline the output data bus before the data bus is delivered to the FPGA fabric.

**Note:** When using non-pipelined ECC mode, the SET filter must be enabled per the *Product Change Notification (PCN 18009.1)*. If this filter is not enabled by the user, Libero SoC (v11.9 and above) automatically turns on SET mitigation for non-pipelined ECC LSRAMs.

Figure 13 shows both pipelined and non-pipelined read operations.

Figure 13 • LSRAM Read Operation

1. For cases where pipelined ECC mode is used, the first write cycle is used by the ECC encoder and the second clock cycle is used when the LSRAM memory array is actually written. Therefore, it is not legal to perform a write immediately followed by a read to the same address on the next clock cycle, because the LSRAM is being written with the newly encoded data. When pipelined ECC mode is used, after issuing a write to a given LSRAM address, a subsequent read to that address must wait until two clock cycles later to ensure the correct data is being read. Once the read command is issued, pipelined ECC mode requires one clock cycle to decode the data from LSRAM before it is presented on the data output port.

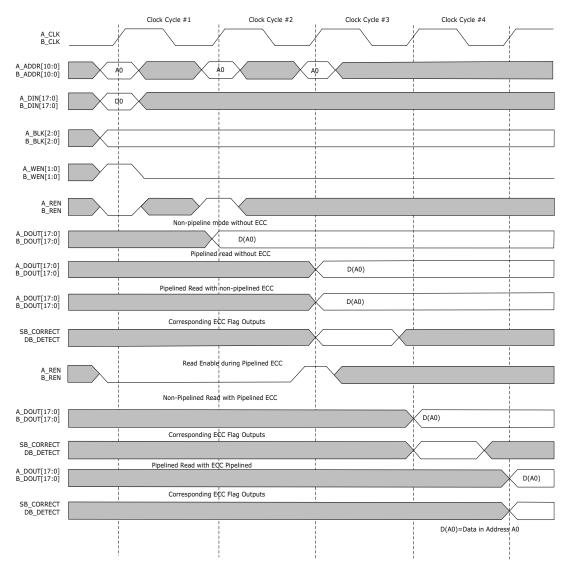

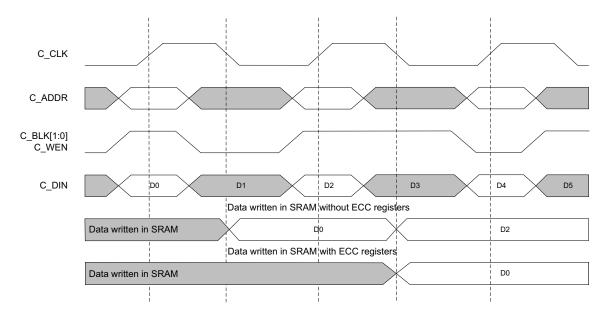

# 4.1.4 LSRAM Write Operation

LSRAM supports Simple write operations:

In a simple-write operation, data input A\_DIN and B\_DIN are written to the corresponding address locations A\_ADDR and B\_ADDR. The data written to the memory is available at the output only after performing a read operation.

**Note:** Simultaneous write operations from both ports to the same address location are not prevented. Since simultaneous write operations can result in data uncertainty, it is recommended to use external logic in the fabric to avoid collisions.

The following figure shows the timing for write operations followed by the corresponding read to the same address, at the earliest possible time.

Figure 14 • LSRAM Write Operation— Followed by Earliest Read

1.For cases where pipelined ECC mode is used, the first write cycle is used by the ECC encoder and the second clock cycle is used when the LSRAM memory array is actually written. Therefore, it is not legal to perform a write immediately followed by a read to the same address on the next clock cycle, because LSRAM is being written with the newly encoded data. When using pipelined ECC mode, after issuing a write to a given LSRAM address, a subsequent read to that address must wait until two clock cycles later to ensure the correct data is being read. Once the read command is issued, pipelined ECC mode requires one clock cycle to decode the data from LSRAM before it is presented on the data output port.

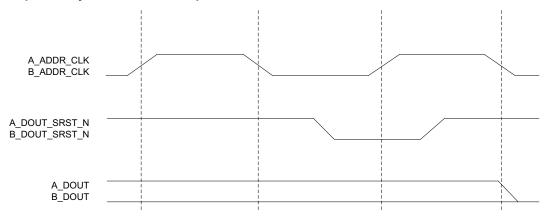

# 4.1.5 Pipelined Read Synchronous Reset Operation

Each port's pipeline registers have a synchronous reset. A\_DOUT\_SRST\_N and B\_DOUT\_SRST\_N drive the synchronous reset of the data output pipeline registers: A\_DOUT and B\_DOUT. If the synchronous reset is low, the pipeline data output registers are reset to zero on the next valid clock edge, as shown in the following figure.

Figure 15 • LSRAM Synchronous Reset Operation

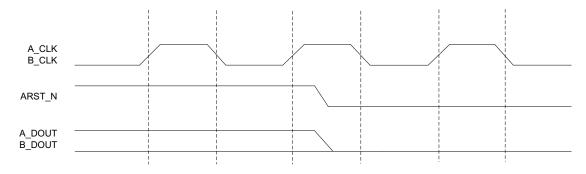

# 4.1.6 Pipelined Read Asynchronous Reset Operation

Each LSRAM has an asynchronous reset (ARST\_N), which connects the read-data pipeline registers to the global asynchronous-reset signal. If the asynchronous reset is driven low, the pipeline data registers are immediately reset to zero as shown in the following figure.

#### Figure 16 • LSRAM Asynchronous Reset Operation

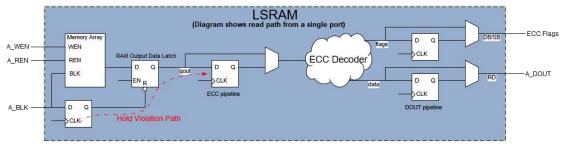

#### 4.1.7 LSRAM ECC

The LSRAM block has ECC logic circuitry (1-bit error correction, 2 bits error detection) for the ×18 and ×36 modes; but not for the ×9 and ×12 modes. The error correction code (ECC) encoder provides 24 bits of data for ×18 mode or 48 bits of data for ×36 mode. The ECC decoder reads the same amount of bits (24 or 48) from the array and provides the expected number of corrected bits (18 or 36) on the outputs. The ECC encoder contains an optional pipeline register which is enabled during pipelined ECC mode. The ECC encoder pipeline register delays the actual data write to the LSRAM by 1 clock cycle.

| T. I. I. 44 |     |           |      |

|-------------|-----|-----------|------|

| Table 14 •  | EUU | Available | wode |

| Port Widths | Write Enables |                 |                 |

|-------------|---------------|-----------------|-----------------|

| A/B         | (byte write)  | Output Pipeline | Pipeline Bypass |

| ×9/×9       | No ECC        | No ECC          | No ECC          |

| ×9/×18      | No ECC        | No ECC          | No ECC          |

| ×9/×36      | No ECC        | No ECC          | No ECC          |

| ×12/×12     | No ECC        | No ECC          | No ECC          |

| ×18/×9      | No ECC        | No ECC          | No ECC          |

| ×18/×18     | No ECC        | ECC available   | ECC available   |

| ×18/×36     | No ECC        | ECC available   | ECC available   |

| ×36/×9      | No ECC        | No ECC          | No ECC          |

Table 14 • ECC Available Mode (continued)

| Port Widths<br>A/B | Write Enables<br>(byte write) | Output Pipeline | Pipeline Bypass |

|--------------------|-------------------------------|-----------------|-----------------|

| ×36/×18            | No ECC                        | ECC available   | ECC available   |

| ×36/×36            | No ECC                        | ECC available   | ECC available   |

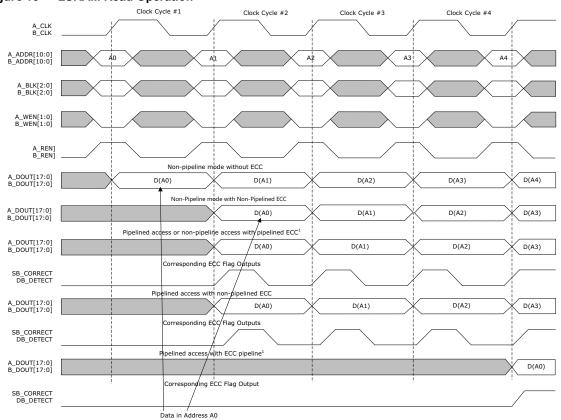

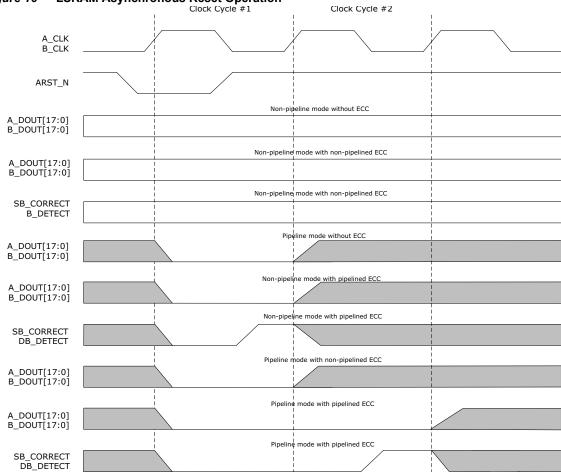

For cases where pipelined ECC mode is used, the ECC encoder, used during writes, and the ECC decoder, used during reads, will each add a clock cycle to the memory operations. During a write to a pipelined ECC LSRAM, the first write cycle is used by the ECC encoder and the second clock cycle is where the LSRAM memory array is actually written. Therefore, it is not legal to perform a write immediately followed by a read to the same address on the next clock cycle, because that is the same cycle where the LSRAM is being written with the newly encoded data. When using pipelined ECC mode, after issuing a write to a given LSRAM address, a subsequent read to that address must wait at least two clock cycles to ensure the correct data is being read. Once the read command is issued, pipelined ECC mode requires one clock cycle to decode the data from LSRAM before it is presented on the data output port. The following are the possible scenarios, since the output data can also be pipelined.

- Pipeline mode with non-pipelined ECC

- Pipeline mode with pipelined ECC

- Non-pipeline mode with non-pipelined ECC

- Non-pipeline mode with pipelined ECC

The timing diagrams for the above possible scenarios are shown in Figure 14.

The ECC logic generates two flags:

- SB\_CORRECT: Asserted when a single-bit error is detected. If SB\_CORRECT is set without the

dual-bit error flag being asserted, the corrupted bit is corrected in read data output. Even though the

corrupted bit is corrected in the read data output, the data in the RAM location is not corrected. The

user logic must correct the contents of the RAM.

- DB\_DETECT: Asserted when a dual-bit error is detected, but not corrected. Multi-bit errors (more than two bits) produce unknown results on the flags and data outputs. If DB\_DETECT is set, correction is not performed on read data output. Correction must be performed by user logic.

In pipeline mode, these flags are valid only in read data output clock cycle. In non-pipeline mode, the ECC flags are valid only in the same clock cycle as the corresponding read data output, because they are reset in the next clock cycle.

The following table lists the ECC errors and corresponding flag status.

Table 15 • LSRAM Error Flag Status

| ECC Errors       | SB_CORRECT | DB_DETECT |

|------------------|------------|-----------|

| No error         | 0          | 0         |

| Single-bit error | 1          | 0         |

| Double-bit error | 1          | 1         |

During an x36 read with LSRAM ECC enabled, all the A and B port ECC flags are used to represent the ECC status for the complete x36 read data out word.

Note: The ECC decoder generates two flags (DB\_DETECT and SB\_CORRECT). If a single-bit error occurs in a 24-bit word (18 data bits and 6 ECC bits), the error correction flag (SB\_CORRECT) is set high and the 18-bit data is corrected. If two or multiple-bit errors occur in the 24-bit word, DB\_DETECT and SB\_CORRECT flags are set high and the 18-bit data from the LSRAM is not corrected or modified. If multiple-bit errors occur in the 6 ECC bits, both ECC flags are asserted and no correction is performed on the 18-bit data.

# 4.1.8 Using LSRAM in a Design

An LSRAM block can be implemented in a design by the following methods:

- RTL Inference during Synthesis

- · Inserting an LSRAM Configurator Component

### 4.1.8.1 RTL Inference during Synthesis

Synplify Pro can infer an LSRAM and automatically set the configuration for various modes, if the RTL design contains an array of at least 12 bits. Synplify also supports inferring memories according to the user attribute syn\_ramstyle. Synthesis ensures that the signals of the LSRAM are properly connected to the rest of the design and sets the correct values for the static signals required to configure the appropriate operational mode. The tool ties unused dynamic input signals to low.

#### Note:

Synplify Pro can cascade multiple LSRAM blocks if the required memory size exceeds the limit of a single LSRAM block. It can also absorb any registers at the LSRAM interface if they are driven by the same clock. If the registers have different clocks, then the clock that drives the output register has priority, and all registers driven by that clock are absorbed into the LSRAM block. If the outputs are unregistered and the inputs are registered with different clocks, the input registers with the larger input have priority and are absorbed into the LSRAM block. For more information about LSRAM inference by Synplify Pro, see *Inferring Microsemi RTG4 RAM Blocks Application Note*.

### 4.1.8.2 Inserting an LSRAM Configurator Component

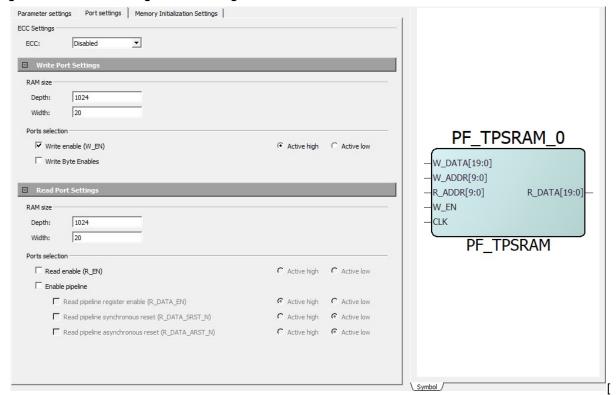

The Libero SoC software catalog provides separate configuration tools for dual-port and two-port modes. Using these configurators, the user can configure LSRAM in the required operating modes. These configuration tools generate the HDL wrapper files for LSRAM with the appropriate values assigned to the static signals. The generated HDL wrapper files can be used in the design hierarchy by connecting the ports to the rest of the design.

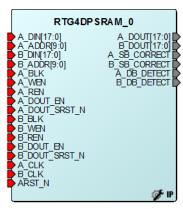

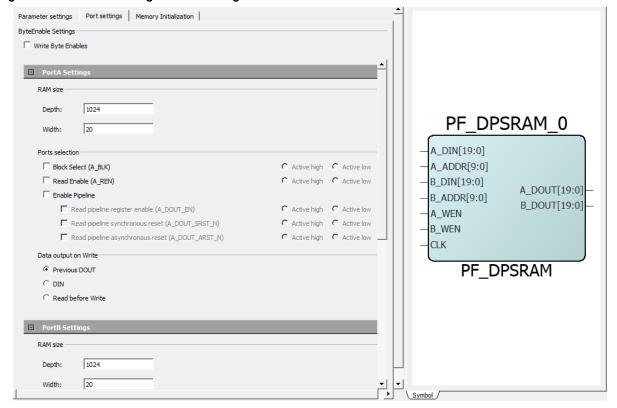

#### 4.1.8.2.1 RTG4 Dual-Port LSRAM Configurator

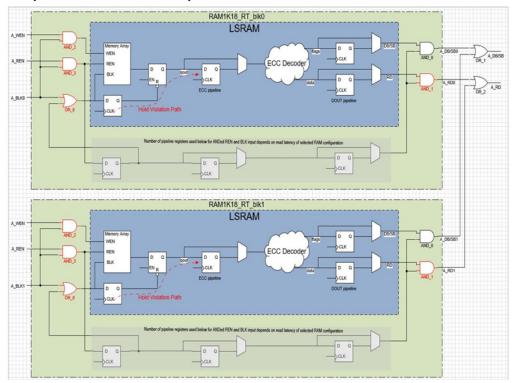

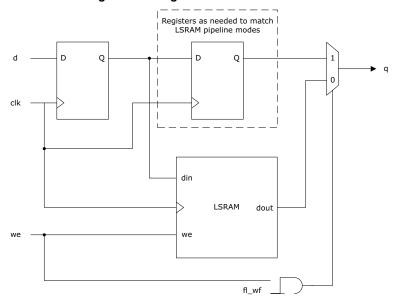

The RTG4 DPSRAM configurator is available in the Libero SoC IP catalog under **Memory & Controllers**, see Figure 17. The RTG4 DPSRAM IP configurator enables write and read access on both ports: port A and port B.

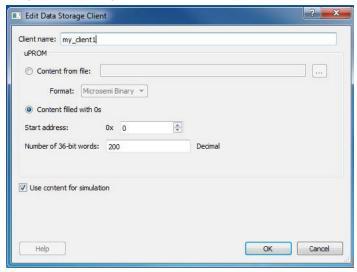

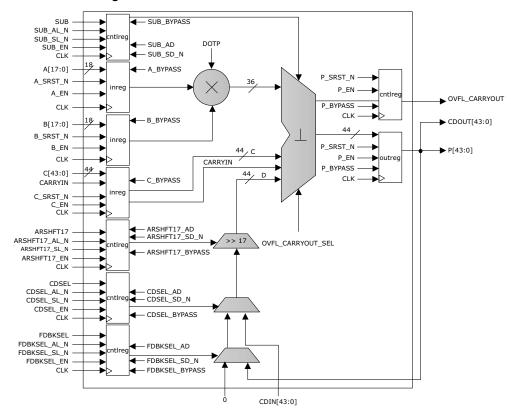

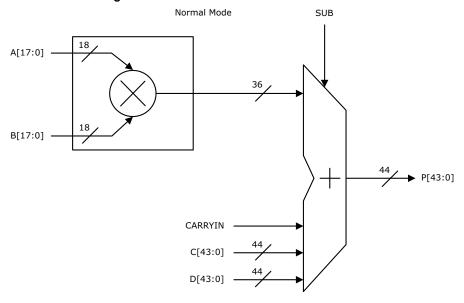

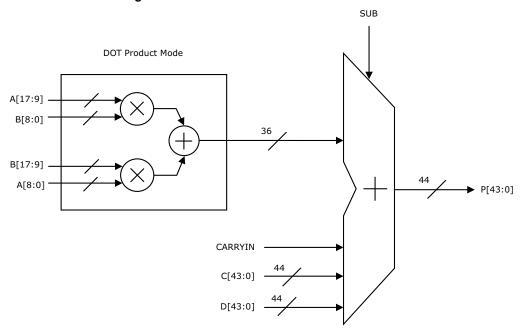

The DPSRAM configurator automatically cascades LSRAM blocks to create wider and deeper memories by selecting the most efficient aspect ratio. It also handles the grounding of unused bits. The core configurator supports the generation of memories that have different aspect ratios on each port. The configurator uses one or more memory blocks to generate a RAM component to match the configuration. The configurator also creates the external logic required for the cascading.