1

## ZLE40203\_XO Evaluation Board – using CTS oscillator VF901480

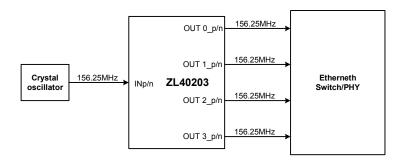

This document provides a brief description of the ZLE40203\_XO Evaluation Board. The board allows a quick and easy evaluation of the Microsemi ZL40203 buffer in a crystal oscillator fanout buffering application. ZL40203 is a precision 1:4 LVPECL fanout buffer with internal input terminations.

This circuit is part of a larger family of fanout buffers offered by Microsemi. This family of buffers supports clock rates of up to 750 MHz. It has a flexible I/O structure, the inputs are compatible with LVPECL, LVDS, CML, HCSL and LVCMOS and the outputs support LVPECL and LVDS signals. It offers six fanout combinations including 1:2, 1:4, 1:6, 1:8, 2:6 and 2:8 with internal and external terminations.

Figure 1: Top view of ZLE40203\_XO Evaluation Board

The main features of the evaluation board are:

- One ZL40203 1:4 precision LVPECL fanout buffer.

- SMA connectors providing, AC coupled, access to all 4 differential outputs.

- Dual crystal oscillator footprint to accommodate a 6 pin 5x7mm or a 6 pin 9x9.5mm LVPECL oscillator.

- Two power supply options: regulated 3.3V DC from an external power supply or 5 to 12V DC from an AC/DC adapter using the onboard 3.3V linear voltage regulator.

April 2014

© 2014 Microsemi Corporation

Option to provide a single ended output on J10 SMA connector by redirecting OUT3 signals through a balun transformer. In this case OUT3 signals are no longer available on J8/J7 SMA connectors.

Figure 2: Typical application example of an ultra low additive jitter fanout buffer

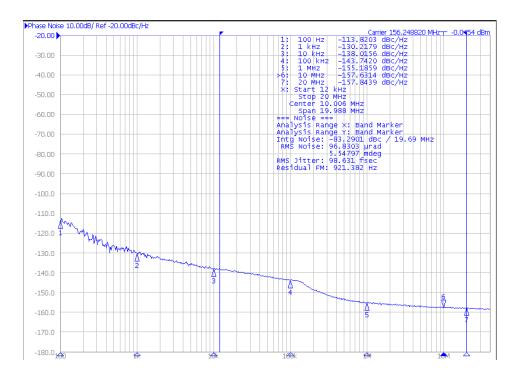

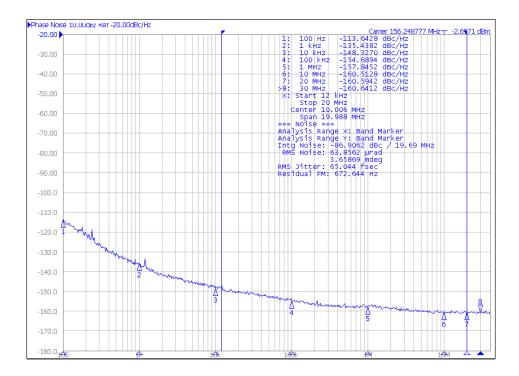

Below are two phase-noise plots showing a typical phase-noise plot at the output of the oscillator, and the phase noise plot captured at the fanout buffer output when using a CTS oscillator part number VF901480. The clock frequency is 156.25MHz. The output RMS jitter is 98fs (12kHz – 20MHz), only about 33fs higher than the input jitter.

Figure 3: Typical phase-noise plot captured at the fanout buffer output (Evaluation Board measurement)

Figure 4: Typical phase-noise plot at the output of a VF901480 oscillator

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1(949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi is the market leader in network synchronization and offers an industry-leading portfolio focused on timing solutions for packet networks (SyncE and IEEE1588) and optical transport network (OTN) systems. The company offers a complete portfolio of timing products for high-performance network synchronization including digital phase locked loop (DPLL) solutions to drive network clocks, as well as analog and mixed-signal timing ICs to meet performance requirements for up to 10G/40G interfaces. Microsemi's clock management solutions include clock generators and synthesizers, clock fanout buffers, and rate conversion jitter attenuators that allow product developers to simplify system and board design. Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.