# **CoreMP7 Subsystem**

User's Guide

### Actel Corporation, Mountain View, CA 94043

© 2005 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200058-1

Release: December 2005

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logo are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

|   | Introduction                                                                                                                                                                                                                                                                                                     |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | CoreMP7 and MP7Bridge     7       CoreMP7 and MP7Bridge Connections     7       Connecting CoreMP7 in CoreConsole     7       CoreMP7 Configuration in CoreConsole     10       MP7Bridge Connections in CoreConsole     10       MP7Bridge Configuration in CoreConsole     12       MP7Bridge Port List     13 |

| 2 | AHB Bus17AHB-Lite Overview17Connecting the AHB Bus in CoreConsole19AHB Bus Port List20                                                                                                                                                                                                                           |

| 3 | AMBA Bridge     23       Connecting the AMBA Bridge in CoreConsole     24                                                                                                                                                                                                                                        |

| 4 | APB Bus                                                                                                                                                                                                                                                                                                          |

| 5 | Memory Controller     27       Connecting the Memory Controller in CoreConsole     27       External Memory Interface     28       Memory Controller Configurable Options     31                                                                                                                                 |

| 6 | CoreUART-APB     33       Connecting CoreUART-APB in CoreConsole     34       CoreUART-APB Configurable Options     35       CoreUART-APB Programmer's Model     35                                                                                                                                              |

| 7 | Interrupt Controller     39       Connecting the Interrupt Controller in CoreConsole     40       Programmer's Model     41                                                                                                                                                                                      |

### Table of Contents

| 8  | Watchdog                         | 51                    |

|----|----------------------------------|-----------------------|

| 9  | Timers                           | 57<br>58<br>59<br>60  |

| 10 | System Control Block             | <mark>67</mark><br>67 |

| 11 | General Purpose I/O (GPIO) Block | 69                    |

| 12 | Flash ROM (FROM) Access Block    | 71                    |

| A  | Product Support                  | 75<br>75<br>75<br>75  |

|    | Index                            | 77                    |

## Introduction

This manual describes the subsystem components available within CoreConsole.

Chapter 1 – CoreMP7 and MP7Bridge describes the function of the MP7Bridge, its ports, and how to connect to it.

Chapter 2 – AHB Bus details the Advanced High-Performance Bus (AHB) fabric component, its ports, and the multiplexing of this fabric.

Chapter 3 – AMBA Bridge provides a module block diagram for the Advanced Microcontroller Bus Architecture (AMBA) Bridge and explains its function.

Chapter 4 – APB Bus describes and provides a diagram for the Advanced Peripheral Bus (APB) fabric.

Chapter 5 - Memory Controller describes the function of the memory controller.

Chapter 6 – CoreUART-APB details the communications, registers, and signals for the CoreUART-APB.

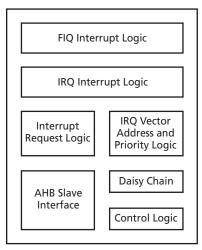

Chapter 7 - Interrupt Controller describes the function of the interrupt controller.

Chapter 8 – Watchdog describes the watchdog unit, which provides a way of recovering from software crashes.

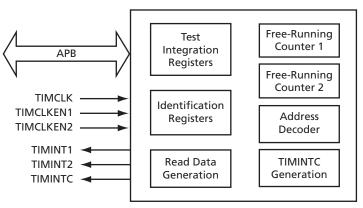

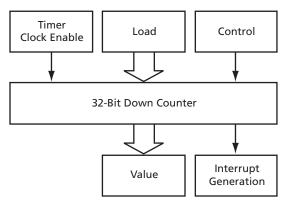

Chapter 9 – Timers provides a functional description of the timers and their operation.

Chapter 10 – System Control Block describes the System Control block.

Chapter 11 – General Purpose I/O (GPIO) Block describes the General Purpose I/O (GPIO) block.

Chapter 12 – Flash ROM (FROM) Access Block describes the Flash Read Only Memory (FROM) Access component.

# **CoreMP7 and MP7Bridge**

The CoreMP7 component is an ARM7TDMI-S processor optimized for implementation on Actel devices.

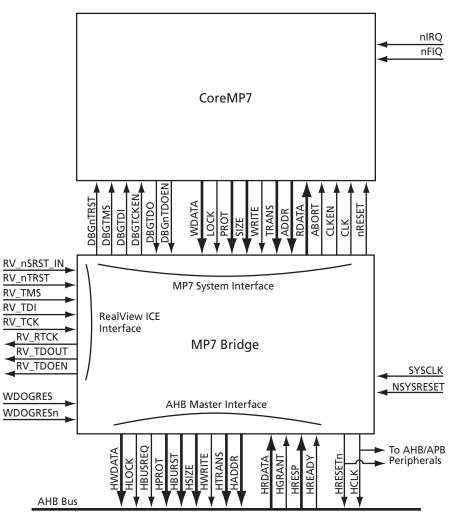

The MP7Bridge component has two functions. Firstly, it converts the native signals from the CoreMP7 processor into an AMBA AHB master interface suitable for connection to an AHB Bus. Secondly, the MP7Bridge includes circuitry which deals with clock signals, reset signals, and the signals which connect to the ARM RealView In-Circuit Emulation (ICE) JTAG port.

The MP7Bridge conditions the incoming raw system clock (SYSCLK) and generates two new clock signals, CLK and HCLK. CLK is tied to the CoreMP7 CLK input. HCLK is tied to the HCLK or PCLK inputs of all the other IP cores. This eliminates any clock skew between flip-flops internal to the CoreMP7 and flip-flops in the subsystem.

The incoming hardware reset signal (NSYSRESET) is synchronized to the system clock within the MP7Bridge and provision is made for handling a watchdog generated reset in the case where a watchdog component is included in the system.

Some circuitry to condition the RealView ICE signals is also included in the MP7Bridge.

## **CoreMP7 and MP7Bridge Connections**

Figure 1-1 on page 8 illustrates how the CoreMP7 and MP7Bridge components are typically connected in a subsystem design.

Note: When connecting the MP7Bridge within a design in CoreConsole, the user is not required to make individual connections to every port. Three groups of signals, or interfaces, are present on the MP7Bridge and these interfaces allow all of their constituent signals to be connected in a single step.

CoreMP7 and MP7Bridge

Figure 1-1. CoreMP7 and MP7Bridge Connections

## Connecting CoreMP7 in CoreConsole

When the CoreMP7 processor is instantiated in a design, most of its connections to the rest of the system (both inside and outside CoreConsole) are handled through the MP7Bridge.

Table 1-1 lists the ports present on the CoreMP7 component and describes how to connect these in CoreConsole.

| Connection                        | CoreConsole Label | Description                                                                                                                                                                                                             |

|-----------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |                   | Required Connections                                                                                                                                                                                                    |

| CoreMP7 System<br>Interface       | MP7_SysIf         | This interface groups together all of the signals which connect between<br>the CoreMP7 and the MP7Bridge as illustrated in Figure 1-1 on page 8.<br>Connect this interface to the MP7_SysIf interface of the MP7Bridge. |

|                                   |                   | Optional Connections                                                                                                                                                                                                    |

| Coprocessor                       | CoProcIf          | Groups together CoreMP7 coprocessor signals which provide a means to add coprocessor functionality.                                                                                                                     |

| Interface                         | Corroch           | This is normally left unconnected. Any inputs present in the interface will be tied to inactive levels.                                                                                                                 |

| Embedded Trace<br>Macrocell (ETM) | ETMIf             | This interface is used to connect to an ETM which facilitates real-time tracing of code running on the processor.                                                                                                       |

| Interface                         |                   | This is normally left unconnected. Any inputs present in the interface will be tied to inactive levels.                                                                                                                 |

| nIRQ                              | nIRQ              | Active low interrupt request input.                                                                                                                                                                                     |

|                                   |                   | This input is tied high if left unconnected.                                                                                                                                                                            |

| nFIO                              | nFIQ              | Active low fast interrupt request input.                                                                                                                                                                                |

|                                   |                   | This input is tied high if left unconnected.                                                                                                                                                                            |

| CECHICEND                         | CFGBIGEND         | When asserted (high) this input configures the CoreMP7 in big-<br>endian mode.                                                                                                                                          |

| CFGBIGEND                         |                   | If no connection is made to this input (normal case) it will be tied low to leave the processor in little-endian mode.                                                                                                  |

| DMORE                             | DMORE             | Output which is asserted (high) during LDM and STM instructions.<br>Normally left unconnected.                                                                                                                          |

#### Table 1-1. CoreMP7 Connections

CoreMP7 and MP7Bridge

## CoreMP7 Configuration in CoreConsole

Table 1-2 describes the configurable options for the CoreMP7 component.

| Configurable Option | Default setting | Description                                                                                                                         |

|---------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Die                 | M7A3P1000       | Selects target die. Family (ProAsic3 or ProAsic3E) is implied by die selection.                                                     |

| Debug               | Enabled         | Determines whether or not debug functionality is included in<br>CoreMP7 instance.<br>Possible settings are "Enabled" or "Disabled". |

| Speed grade         | -2              | Selects speed grade of the target Actel device                                                                                      |

#### Table 1-2. CoreMP7 Configuration

## MP7Bridge Connections in CoreConsole

Table 1-3 lists the ports present on the MP7Bridge and describes how to connect these in CoreConsole.

| Table | 1-3. | MP7Bridge | Connections |

|-------|------|-----------|-------------|

|-------|------|-----------|-------------|

| Connection CoreConsole Label |                      | Description                                                                                                                                                                                                                        |  |

|------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              | Required Connections |                                                                                                                                                                                                                                    |  |

| CoreMP7 System<br>Interface  | MP7_SysIf            | This interface groups together all of the signals which connect between<br>the CoreMP7 and the MP7Bridge as illustrated in Figure 1-1 on page 8.<br>Connect this interface to the MP7_SysIf interface of the CoreMP7<br>component. |  |

| AHB master<br>interface      | AHBmaster            | Groups together AHB master signals.<br>Connect to AHB mirrored master (AHBmmaster) interface of AHB<br>Bus.                                                                                                                        |  |

| SYSCLK                       | SYSCLK               | Raw system clock input.<br>Connect to susbsystem toplevel SYSCLK port.                                                                                                                                                             |  |

| NSYSRESET                    | NSYSRESET            | Active low hardware reset input.<br>Connect to subsystem toplevel NSYSRESET port.                                                                                                                                                  |  |

| Connection | CoreConsole Label | Description                                                                                                                                                                |

|------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK       | HCLK              | AMBA system clock.<br>Connect to HCLK/PCLK ports of AHB/APB peripherals.<br>May also be connected to subsystem toplevel if used outside the<br>subsystem.                  |

| HRESETn    | HRESETn           | Active low AMBA system reset.<br>Connect to HRESETn/PRESETn ports of AHB/APB peripherals.<br>May also be connected to subsystem toplevel if used outside the<br>subsystem. |

### Table 1-3. MP7Bridge Connections (Continued)

### CoreMP7 and MP7Bridge

| Connection CoreConsole Label        |          | Description                                                                                                                                                                                                             |  |

|-------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Optional Connections                |          |                                                                                                                                                                                                                         |  |

| RealView ICE<br>interface RV_ICE_If |          | Groups together RealView ICE JTAG interface signals.<br>If using debugging, connect this interface to the subsystem toplevel.                                                                                           |  |

| WDOGRES                             | WDOGRES  | Active high input which signals that watchdog has timed-out.<br>If your design includes a watchdog, connect this port to the<br>WDOGRES port of the watchdog.<br>This input is tied low if no connection is made to it. |  |

| WDOGRESn                            | WDOGRESn | Active low output signal used to reset watchdog component.<br>If your design includes a watchdog, connect this port to the<br>WDOGRESn port of the watchdog, otherwise leave unconnected.                               |  |

#### Table 1-3. MP7Bridge Connections (Continued)

## MP7Bridge Configuration in CoreConsole

Table 1-4 describes the configurable options for the MP7Bridge.

#### Table 1-4. MP7Bridge Configuration

| Configurable Option | Default setting | Description                                                                                 |

|---------------------|-----------------|---------------------------------------------------------------------------------------------|

| Device family       | ProASIC3        | Selects device family of target device.<br>Possible settings are "ProASIC3" or "ProASIC3E". |

## MP7Bridge Port List

Table 1-5 on page 13 provides a detailed list and description of the ports on the MP7Bridge.

| Port Name | Width              | Direction | Description                                                                                                                                                                            |  |  |  |

|-----------|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|           | System Connections |           |                                                                                                                                                                                        |  |  |  |

| SYSCLK    | 1                  | Input     | Incoming raw system clock                                                                                                                                                              |  |  |  |

| NSYSRESET | 1                  | Input     | Raw hardware system reset input from top level. Will typically be controlled by a push button switch.                                                                                  |  |  |  |

|           |                    | ·         | AHB Connections                                                                                                                                                                        |  |  |  |

| HCLK      | 1                  | Output    | AHB system clock. Reset and RealView ICE JTAG signals are synchronized to this clock. This also connects to the other cores.                                                           |  |  |  |

| HRESETn   | 1                  | Output    | AHB reset signal (active low). This reset may be asserted<br>asynchronously but will always be negated synchronous to HCLK.<br>HRESETn also connects to the other cores.               |  |  |  |

| HREADY    | 1                  | Input     | AHB ready signal                                                                                                                                                                       |  |  |  |

| HRESP     | 2                  | Input     | AHB response signal                                                                                                                                                                    |  |  |  |

| HGRANT    | 1                  | Input     | AHB grant signal                                                                                                                                                                       |  |  |  |

| HRDATA    | 32                 | Input     | AHB read data                                                                                                                                                                          |  |  |  |

| HADDR     | 32                 | Output    | AHB address signal                                                                                                                                                                     |  |  |  |

| HTRANS    | 2                  | Output    | AHB transfer type signal                                                                                                                                                               |  |  |  |

| HWRITE    | 1                  | Output    | AHB read/write indication                                                                                                                                                              |  |  |  |

| HSIZE     | 3                  | Output    | AHB size (byte, word etc.) of transfer indication                                                                                                                                      |  |  |  |

| HBURST    | 3                  | Output    | AHB burst signal                                                                                                                                                                       |  |  |  |

| HPROT     | 4                  | Output    | AHB protection signal                                                                                                                                                                  |  |  |  |

| HBUSREQ   | 1                  | Output    | AHB Bus request. In a single master system this port will typically be<br>unconnected. Where there are multiple masters it will be connected<br>to some form of arbitration component. |  |  |  |

### Table 1-5. MP7Bridge Port List

### CoreMP7 and MP7Bridge

| Port Name | Width | Direction | Description                                                               |

|-----------|-------|-----------|---------------------------------------------------------------------------|

| HLOCK     | 1     | Output    | AHB lock signal                                                           |

| HWDATA    | 32    | Output    | AHB write data                                                            |

|           |       | (         | CoreMP7 Connections                                                       |

| CLK       | 1     | Input     | Clock signal. Connects to CLK port of CoreMP7.                            |

| nRESET    | 1     | Input     | Reset signal. Connects to nRESET port of CoreMP7.                         |

| ADDR      | 32    | Input     | Address bus. Connects to ADDR port of CoreMP7.                            |

| LOCK      | 1     | Input     | Lock signal. Connects to LOCK port of CoreMP7.                            |

| SIZE      | 2     | Input     | Size signal. Connects to SIZE port of CoreMP7.                            |

| WRITE     | 1     | Input     | Write signal. Connects to WRITE port of CoreMP7.                          |

| PROT      | 2     | Input     | Protection signal. Connects to PROT port of CoreMP7.                      |

| TRANS     | 2     | Input     | Transfer signal. Connects to TRANS port of CoreMP7.                       |

| WDATA     | 32    | Input     | Write data. Connects to WRITE port of CoreMP7.                            |

| ABORT     | 1     | Output    | Abort signal. Connects to ABORT port of CoreMP7.                          |

| CLKEN     | 1     | Output    | Clock enable. Connects to CLKEN port of CoreMP7.                          |

| RDATA     | 32    | Output    | Read data. Connects to RDATA port of CoreMP7.                             |

| DBGnTRST  | 1     | Output    | Debug TAP reset signal. Connects to DBGnTRST port of CoreMP7.             |

| DBGTMS    | 1     | Output    | Debug test mode select signal. Connects to DBGTMS port of CoreMP7.        |

| DBGTDI    | 1     | Output    | Debug test data in signal. Connects to DBGTDI port of CoreMP7.            |

| DBGTCKEN  | 1     | Output    | Debug test clock signal. Connects to DBGTCKEN port of CoreMP7.            |

| DBGTDO    | 1     | Input     | Debug test data out signal. Connects to DBGTDO port of CoreMP7.           |

| DBGnTDOEN | 1     | Input     | Debug test data out enable signal. Connects to DBGnTDOEN port of CoreMP7. |

### Table 1-5. MP7Bridge Port List (Continued)

| Port Name   | Width                | Direction | Description                                                                                                                                                                                                                                                                      |  |  |

|-------------|----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | Watchdog Connections |           |                                                                                                                                                                                                                                                                                  |  |  |

| WDOGRES     | 1                    | Input     | Watchdog reset input. If a watchdog is present in the system, this<br>port should be connected to the 'bark' port of the watchdog; that is,<br>whichever signal the watchdog asserts when it initiates a reset.<br>This input is active high.                                    |  |  |

| WDOGRESn    | 1                    | Output    | Active low reset output to watchdog. Should be connected to the reset<br>port of the watchdog (if present).<br>This output is asserted when NSYSRESET is asserted but not when<br>WDOGRES is asserted. This allows the watchdog to reset the<br>system without resetting itself. |  |  |

|             |                      | RealV     | iew ICE JTAG Connections                                                                                                                                                                                                                                                         |  |  |

| RV_nSRST_IN | 1                    | Input     | RealView ICE system reset input.<br>Connect to top level if using RealView.                                                                                                                                                                                                      |  |  |

| RV_nTRST    | 1                    | Input     | RealView ICE Test Access Port (TAP) reset.<br>Connect to top level if using RealView.                                                                                                                                                                                            |  |  |

| RV_TMS      | 1                    | Input     | RealView ICE test mode select.<br>Connect to top level if using RealView.                                                                                                                                                                                                        |  |  |

| RV_TDI      | 1                    | Input     | RealView ICE test data in.<br>Connect to top level if using RealView.                                                                                                                                                                                                            |  |  |

| RV_TCK      | 1                    | Input     | RealView ICE test clock.<br>Connect to top level if using RealView.                                                                                                                                                                                                              |  |  |

| RV_RTCK     | 1                    | Output    | RealView ICE return test clock.<br>Connect to top level if using RealView.                                                                                                                                                                                                       |  |  |

| RV_TDOUT    | 1                    | Output    | RealView ICE test data out.<br>Connect to top level if using RealView.                                                                                                                                                                                                           |  |  |

| RV_nTDOEN   | 1                    | Output    | RealView ICE test data out enable.<br>Connect to top level if using RealView.                                                                                                                                                                                                    |  |  |

### Table 1-5. MP7Bridge Port List (Continued)

# **AHB Bus**

The AHB Bus component implements the AHB Bus fabric for a subsystem. Currently the AHB Bus essentially supports an AHB-Lite system in that it accommodates a single master. Up to 16 AHB slaves can be present on the bus. From a memory map point of view, all AHB slaves are allocated an equal amount (256 MB) of memory.

## **AHB-Lite Overview**

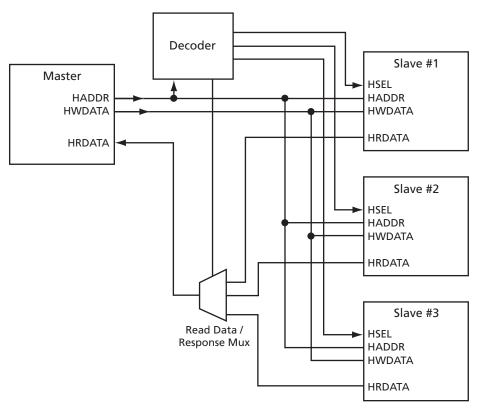

The AHB Bus component available in CoreConsole essentially implements an AHB-Lite Bus fabric. AHB-Lite is a subset of the full AHB specification and is intended for use in designs where there is only a single bus master.

AHB-Lite simplifies the AHB specification by removing the protocol required for multiple bus masters. This includes arbitration based on a request/grant type mechanism and split/retry responses from AHB slaves.

The basic structure of this fabric is shown in Figure 2-1 on page 18. The elements labeled "Decoder" and "Read Data/Response Mux" in the figure are contained within the AHB Bus component.

Figure 2-1. AHB-Lite Block Diagram

## Connecting the AHB Bus in CoreConsole

Table 2-1 lists the ports present on the AHB Bus and describes how to connect these in CoreConsole.

| Connection                       | CoreConsole Label    | Description                                                                                                                   |  |  |

|----------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                  | Required Connections |                                                                                                                               |  |  |

| AHB mirrored<br>master interface | AHBmmaster           | This interface connects to the AHB master.<br>Normally this will be connected to the AHBmaster interface of the<br>MP7Bridge. |  |  |

| HCLK                             | HCLK                 | AHB system clock input.<br>Connect this to the HCLK output of the MP7Bridge.                                                  |  |  |

| HRESETn                          | HRESETn              | Active low AHB system reset.<br>Connect this to the HRESETn output of the MP7Bridge.                                          |  |  |

|                                  | Optional Connections |                                                                                                                               |  |  |

|                                  | AHBmslave0           | AHB mirrored slave 0 interface.<br>Normally connected to AHBslave_base interface of Memory Controller.                        |  |  |

|                                  | AHBmslave1           | AHB mirrored slave 1 interface                                                                                                |  |  |

|                                  | AHBmslave2           | AHB mirrored slave 2 interface                                                                                                |  |  |

|                                  | AHBmslave3           | AHB mirrored slave 3 interface                                                                                                |  |  |

|                                  | AHBmslave4           | AHB mirrored slave 4 interface                                                                                                |  |  |

|                                  | AHBmslave5           | AHB mirrored slave 5 interface                                                                                                |  |  |

|                                  | AHBmslave6           | AHB mirrored slave 6 interface                                                                                                |  |  |

|                                  | AHBmslave7           | AHB mirrored slave 7 interface                                                                                                |  |  |

|                                  | AHBmslave8           | AHB mirrored slave 8 interface                                                                                                |  |  |

|                                  | AHBmslave9           | AHB mirrored slave 9 interface                                                                                                |  |  |

|                                  | AHBmslave10          | AHB mirrored slave 10 interface                                                                                               |  |  |

|                                  | AHBmslave11          | AHB mirrored slave 11 interface                                                                                               |  |  |

#### Table 2-1. AHB Bus Connections

#### AHB Bus

| Connection | CoreConsole Label | Description                     |

|------------|-------------------|---------------------------------|

|            | AHBmslave12       | AHB mirrored slave 12 interface |

|            | AHBmslave13       | AHB mirrored slave 13 interface |

|            | AHBmslave14       | AHB mirrored slave 14 interface |

|            | AHBmslave15       | AHB mirrored slave 15 interface |

#### Table 2-1. AHB Bus Connections (Continued)

### **AHB Bus Port List**

Table 2-2 lists the ports present on the AHB Bus component. Four groups of signals can be identified:

- 1. Common AHB system signals (clock and reset)

- 2. AHB mirrored master interface. This connects to the master on the AHB Bus. A mirrored master interface is made up of the same signals as a master interface but the direction of the signals is reversed.

- 3. Signals common to all 16 AHB mirrored slave interfaces. These are AHB master signals which connect to all slaves.

- 4. AHB mirrored slave (master) signals specific to each slave.

| Signal  | Direction                 | Description                                                                                                                    |  |

|---------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

|         | Common AHB System Signals |                                                                                                                                |  |

| HCLK    | Input                     | Bus clock. This clock times all bus transfers. All signal timings are related to the rising edge of HCLK.                      |  |

| HRESETn | Input                     | Reset. The bus reset signal is active low and is used to reset the system and the bus. This is the only active low AHB signal. |  |

#### Table 2-2. Ports on the AHB Bus Component

| Signal                            | Direction                     | Description                                                                                                                                                        |  |  |

|-----------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                   | Mirrored AHB Master Interface |                                                                                                                                                                    |  |  |

| HADDR[31:0]                       | Input                         | This is the 32-bit system address bus.                                                                                                                             |  |  |

|                                   |                               | Transfer type. Indicates the type of the current transfer:                                                                                                         |  |  |

|                                   |                               | 00 – Idle                                                                                                                                                          |  |  |

| HTRANS[1:0]                       | Input                         | 01 – Busy                                                                                                                                                          |  |  |

|                                   |                               | 10 – Non-Sequential                                                                                                                                                |  |  |

|                                   |                               | 11 - Sequential                                                                                                                                                    |  |  |

| HWRITE                            | Input                         | Transfer direction. When high this signal indicates a write transfer and when LOW a read transfer.                                                                 |  |  |

| HSIZE[2:0]                        | Input                         | Transfer size. Indicates the size of the transfer, which can be byte (8-bit), halfword (16-bit), or word (32-bit).                                                 |  |  |

| HBURST[2:0]                       | Input                         | Burst type. Indicates if the transfer forms part of a burst. The CoreMP7 performs incrementing bursts of type INCR.                                                |  |  |

| HPROT[3:0]                        | Input                         | Protection control. These signals indicate if the transfer is an opcode fetch or data access, and if the transfer is a Supervisor mode access or User mode access. |  |  |

| HWDATA[31:0]                      | Input                         | 32-bit data from the master.                                                                                                                                       |  |  |

| HRDATA[31:0]                      | Output                        | 32-bit date written back to the master.                                                                                                                            |  |  |

| HREADY                            | Output                        | Transfer done. When high the HREADY signal indicates that a transfer has finished on the bus. This signal can be driven low to extend a transfer.                  |  |  |

| HRESP[1:0]                        | Input                         | Transfer response. Indicates an Okay Error Retry, or Split response.                                                                                               |  |  |

| Common AHB Mirrored Slave Signals |                               |                                                                                                                                                                    |  |  |

| HADDRS[31:0]                      | Output                        | This is the 32-bit system address bus.                                                                                                                             |  |  |

|                                   |                               | Transfer type. Indicates the type of the current transfer:                                                                                                         |  |  |

|                                   |                               | 00 – Idle                                                                                                                                                          |  |  |

| HTRANSS[1:0]                      | Output                        | 01 – Busy                                                                                                                                                          |  |  |

|                                   |                               | 10 – Non-Sequential                                                                                                                                                |  |  |

|                                   |                               | 11 - Sequential                                                                                                                                                    |  |  |

### Table 2-2. Ports on the AHB Bus Component (Continued)

### AHB Bus

| Signal         | Direction | Description                                                                                                                                                                 |  |

|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HWRITES        | Output    | Transfer direction. A write transfer is indicated when this signal is high and a read transfer is indicated this signal is low during the address phase of an AHB transfer. |  |

| HSIZES[2:0]    | Output    | Transfer size. Indicates the size of the transfer, which can be:<br>00 - byte (8-bit)<br>01 - halfword (16-bit)<br>10 - word (32-bit).                                      |  |

| HBURSTS[2:0]   | Output    | Burst type. Indicates if the transfer forms part of a burst.                                                                                                                |  |

| HPROTS[3:0]    | Output    | Protection control. These signals indicate if the transfer is an opcode fetch or dat access, and if the transfer is a Supervisor mode access or User mode access.           |  |

| HWDATAS[31:0]  | Output    | 32-bit data to the slave                                                                                                                                                    |  |

| HREADYS        | Output    | Transfer done. Out to the slaves (alias of HREADY)                                                                                                                          |  |

|                | •         | Slave-Specific Mirrored Slave Signals                                                                                                                                       |  |

| HSELx          | Output    | Select of slave x (where x is a integer between 0 and 15)                                                                                                                   |  |

| HRDATASx[31:0] | Input     | 32-bit read data from slave x.                                                                                                                                              |  |

| HREADYSx       | Input     | Ready signal from slave x. When high indicates that slave has completed transfer and is ready for another transfer.                                                         |  |

| HRESPSx[1:0]   | Input     | Transfer response from slave x which can be:<br>00 – Okay<br>01 – Error<br>10 – Retry<br>11 – Split                                                                         |  |

### Table 2-2. Ports on the AHB Bus Component (Continued)

# **AMBA Bridge**

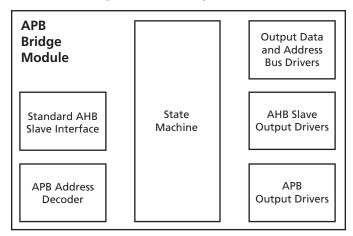

The AMBA Bridge is an AHB slave which links the AHB Bus to the APB Bus and acts as the master on the APB Bus. Address decoding for the APB Bus is carried out within the AMBA Bridge and this provides select signals for up to 16 APB slave slots.

Read and write transfers on the AHB are converted into corresponding transfers on the APB. High bandwidth peripherals such as a memory controller are typically connected to the AHB Bus whereas the APB Bus is used for less demanding peripherals such as a watchdog. Unlike the AHB Bus, transfers on the APB Bus are not pipelined.

Figure 3-1 shows the AMBA Bridge module block diagram.

Figure 3-1. AMBA Bridge

AMBA Bridge

## Connecting the AMBA Bridge in CoreConsole

Table 3-1 lists the ports present on the AMBA Bridge and describes how to connect these in CoreConsole.

| Connection           | CoreConsole Label | Description                                                                          |

|----------------------|-------------------|--------------------------------------------------------------------------------------|

|                      | F                 | Required Connections                                                                 |

| AHB slave interface  | AHBslave          | Connect this to the any of the 16 available slave slots on the AHB Bus.              |

| APB master interface | APBmaster         | Connect this to the APBmmaster interface of the APB Bus.                             |

| HCLK                 | HCLK              | AHB system clock input.<br>Connect this to the HCLK output of the MP7Bridge.         |

| HRESETn              | HRESETn           | Active low AHB system reset.<br>Connect this to the HRESETn output of the MP7Bridge. |

#### Table 3-1. AMBA Bridge Connections

## **APB Bus**

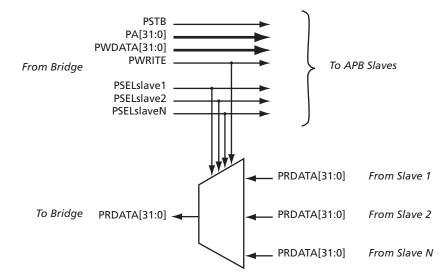

Along with the AMBA Bridge, the APB Bus component provides an AMBA APB fabric which supports up to 16 APB slaves. The AMBA Bridge provides APB address decoding in the form of select signals. The APB Bus is concerned with multiplexing the read data busses from all the APB slaves unto one single read data bus to send to the AMBA Bridge. Figure 4-1 gives an illustration of the APB fabric.

There is one APB master interface which is typically connected to the AMBA Bridge, and 16 equalsized (16 MB) APB slave interfaces.

Figure 4-1. APB Fabric

APB Bus

## Connecting the APB Bus in CoreConsole

Table 4-1 lists the ports present on the APB Bus and describes how to connect these in CoreConsole.

| Connection                       | CoreConsole Label                                                                 | Description                     |  |  |

|----------------------------------|-----------------------------------------------------------------------------------|---------------------------------|--|--|

|                                  | •                                                                                 | Required Connections            |  |  |

| APB mirrored<br>master interface | APBmmaster This interface connects to the APBmaster interface of the AMBA Bridge. |                                 |  |  |

|                                  |                                                                                   | Optional Connections            |  |  |

|                                  | APBmslave0                                                                        | APB mirrored slave 0 interface  |  |  |

|                                  | APBmslave1                                                                        | APB mirrored slave 1 interface  |  |  |

|                                  | APBmslave2                                                                        | APB mirrored slave 2 interface  |  |  |

|                                  | APBmslave3                                                                        | APB mirrored slave 3 interface  |  |  |

|                                  | APBmslave4                                                                        | APB mirrored slave 4 interface  |  |  |

|                                  | APBmslave5                                                                        | APB mirrored slave 5 interface  |  |  |

|                                  | APBmslave6                                                                        | APB mirrored slave 6 interface  |  |  |

|                                  | APBmslave7                                                                        | APB mirrored slave 7 interface  |  |  |

|                                  | APBmslave8                                                                        | APB mirrored slave 8 interface  |  |  |

|                                  | APBmslave9                                                                        | APB mirrored slave 9 interface  |  |  |

|                                  | APBmslave10                                                                       | APB mirrored slave 10 interface |  |  |

|                                  | APBmslave11                                                                       | APB mirrored slave 11 interface |  |  |

|                                  | APBmslave12                                                                       | APB mirrored slave 12 interface |  |  |

|                                  | APBmslave13                                                                       | APB mirrored slave 13 interface |  |  |

|                                  | APBmslave14                                                                       | APB mirrored slave 14 interface |  |  |

|                                  | APBmslave15                                                                       | APB mirrored slave 15 interface |  |  |

#### Table 4-1. APB Bus Connections

# **Memory Controller**

The Memory Controller is an AHB slave component which supports access to SRAM and Flash memory resources.

The Memory Controller uses 3 slave slots on the AHB Bus. A slot is allocated to the SRAM, another to the Flash and a third slot, designated as Base, can be used to access either the SRAM or Flash via a memory aliasing mechanism.

The memory controller has a 'Remap' input which is used to select whether SRAM or Flash appears at the Base slot. Typically the Base slave interface is connected to slot 0 on the AHB Bus, the Flash slave interface to slot 1, and the SRAM slave interface to slot 2.

The Remap signal may be driven by the System Control Block (see "System Control Block" on page 67) which provides a way for the processor to change the memory aliasing by writing to a particular location in its address space.

## Connecting the Memory Controller in CoreConsole

Table 5-1 lists the ports present on the Memory Controller and describes how to connect these in CoreConsole.

| Connection                   | CoreConsole Label    | Description                                                                                                                                                                        |  |  |

|------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                              | Required Connections |                                                                                                                                                                                    |  |  |

| Base AHB slave<br>interface  | AHBslave_base        | This interface groups together all of the signals used to connect<br>the base memory region to an AHB slot.<br>Normally connected to slave slot 0 (AHBmslave0) of the AHB<br>Bus.  |  |  |

| Flash AHB slave<br>interface | AHBslave_flash       | This interface groups together all of the signals used to connect<br>the flash memory region to an AHB slot.<br>Normally connected to slave slot 1 (AHBmslave1) of the AHB<br>Bus. |  |  |

| SRAM AHB slave<br>interface  | AHBslave_sram        | This interface groups together all of the signals used to connect<br>the SRAM memory region to an AHB slot.<br>Normally connected to slave slot 2 (AHBmslave2) of the AHB<br>Bus.  |  |  |

#### Table 5-1. Memory Controller Connections

#### Memory Controller

| Connection                   | CoreConsole Label       | Description                                                                                                                                                                                                                 |  |  |

|------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| External Memory<br>Interface | ExternalMemoryInterface | This interface contains the signals used to connect to the actual memory devices and should be routed to the toplevel of your subsystem. See "External Memory Interface" on page 28 for more information on this interface. |  |  |

| HCLK                         | HCLK                    | AHB system clock input.<br>Connect this to the HCLK output of the MP7Bridge.                                                                                                                                                |  |  |

| HRESETn                      | HRESETn                 | Active low AHB system reset.<br>Connect this to the HRESETn output of the MP7Bridge.                                                                                                                                        |  |  |

|                              | Optional Connections    |                                                                                                                                                                                                                             |  |  |

|                              |                         | This input is used to control aliasing of the Flash and SRAM<br>memory regions.<br>When Remap is low, Flash is aliased to the Base memory region.                                                                           |  |  |

| Remap                        | Remap                   | When Remap is high, SRAM is aliased to the Base memory region.                                                                                                                                                              |  |  |

|                              |                         | Remap is normally connected to the Remap output of the System<br>Control block (see "System Control Block" on page 67).                                                                                                     |  |  |

|                              |                         | If no connection is made, Remap will be tied low.                                                                                                                                                                           |  |  |

#### Table 5-1. Memory Controller Connections (Continued)

## **External Memory Interface**

The External Memory Interface of the Memory Controller should be routed to the subsystem toplevel to facilitate communication with Flash and SRAM resources.

The Memory Controller is designed to accommodate a variety of Flash and SRAM configurations as outlined in "Memory Controller Configurable Options" on page 31. For this reason, the External Memory Interface is somewhat generic in nature in order to enable connection to a range of different memory devices and memory systems.

Memory devices typically have a number of inputs that are fixed at static levels which are dependent on the particular memory architecture in place. If the memory devices in your system have such static inputs, it is intended that these are handled in the toplevel description for your FPGA device; that is, above the subsystem toplevel. Similarly, any tri-state buffers must be instantiated above the subsystem toplevel. The data bus connecting between the FPGA and the actual memory devices is normally a bi-directional bus which is driven by tri-state buffers.

Table 5-2 lists and describes the signals which make up the External Memory Interface. Apart from "MemDataIn", all of the signals are outputs from the Memory Controller. All of the 1-bit wide control signals are active low as indicated by the "N" at the end of the signal names.

| Signal               | Width                                                                                                                                                                    | Description                                                                                                                                              |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | •                                                                                                                                                                        | Flash control signals                                                                                                                                    |  |

| FlashCSN             | 1     Flash chip select.       1     In some systems the chip select pin of the Flash will be fixed at an active level in whic case this signal may be left unconnected. |                                                                                                                                                          |  |

| FlashOEnN            | 1                                                                                                                                                                        | Flash output enable                                                                                                                                      |  |

| FlashWEnN            | 1                                                                                                                                                                        | Flash write enable                                                                                                                                       |  |

| SRAM control signals |                                                                                                                                                                          |                                                                                                                                                          |  |

| SramCSN              | 1                                                                                                                                                                        | SRAM chip select.<br>In some systems the chip select pin of the SRAM will be fixed at an active level in which case this signal may be left unconnected. |  |

| SramOEnN             | 1                                                                                                                                                                        | SRAM output enable                                                                                                                                       |  |

| SramWEnN             | 1                                                                                                                                                                        | SRAM write enable                                                                                                                                        |  |

| SramByte0N           | 1                                                                                                                                                                        | SRAM byte 0 enable                                                                                                                                       |  |

| SramByte1N           | 1                                                                                                                                                                        | SRAM byte 1 enable                                                                                                                                       |  |

| SramByte2N           | 1                                                                                                                                                                        | SRAM byte 2 enable                                                                                                                                       |  |

| SramByte3N           | 1                                                                                                                                                                        | SRAM byte 3 enable                                                                                                                                       |  |

#### Table 5-2. Memory Controller External Memory Interface

### Memory Controller

### Table 5-2. Memory Controller External Memory Interface (Continued)

| Signal      | Width | idth Description                                                                                                                                                                                     |  |  |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |       | Shared memory signals                                                                                                                                                                                |  |  |

|             |       | Combined Flash/SRAM read enable.                                                                                                                                                                     |  |  |

| MemReadN    | 1     | This signal is asserted (low) when either FlashOEnN or SramOEnN is low and is intended for use in a memory system which does not have separate connections to the Flash and SRAM output enable pins. |  |  |

|             | 1     | Combined Flash/SRAM write enable.                                                                                                                                                                    |  |  |

| MemWriteN   |       | This signal is asserted (low) when either FlashWEnN or SramWEnN is low and is intended for use in a memory system which does not have separate connections to the Flash and SRAM write enable pins.  |  |  |

| MemAddr     | 28    | Flash/SRAM address bus                                                                                                                                                                               |  |  |

|             |       | Flash/SRAM data out enable.                                                                                                                                                                          |  |  |

| MemDataOEnN | 1     | Control signal for data bus tri-states. Active low; that is, low when data is driven on MemDataOut.                                                                                                  |  |  |

| MemDataOut  | 32    | Flash/SRAM data out                                                                                                                                                                                  |  |  |

| MemDataIn   | 32    | Flash/SRAM data in                                                                                                                                                                                   |  |  |

## Memory Controller Configurable Options

There are a number of configurable options which apply to the Memory Controller; these are detailed in Table 5-3 on page 31. If a configuration different to the default is required, the user should use the configuration dialog in CoreConsole to select appropriate values for the configurable options.

| Configurable Option                      | Default setting | Description                                                                                                                                                         |

|------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRAM mode                                | Asynchronous    | Selects either asynchronous or synchronous SRAM.<br>Possible settings are "Asynchronous" or "Synchronous".                                                          |

| Flash data bus width                     | 32 bit          | Selects the data bus width for the Flash memory interface.<br>Possible settings are "32 bit" or "16 bit".                                                           |

| Number of wait states for<br>Flash read  | 1               | Selects the number of wait states inserted during a Flash read access.<br>Possible range is 0 to 3.                                                                 |

| Number of wait states for<br>Flash write | 1               | Selects the number of wait states inserted during a Flash write access.<br>Possible range is 1 to 3.                                                                |

| Number of wait states for<br>SRAM read   | 1               | Only applicable when SRAM mode is set to "Asynchronous".<br>Selects the number of wait states inserted during an SRAM read<br>access.<br>Possible range is 0 to 3.  |

| Number of wait states for<br>SRAM write  | 1               | Only applicable when SRAM mode is set to "Asynchronous".<br>Selects the number of wait states inserted during an SRAM write<br>access.<br>Possible range is 1 to 3. |

# **CoreUART-APB**

The CoreUART-APB component available in CoreConsole is an APB-wrapped version of the Actel DirectCores CoreUART. The serial communication interface is identical to that described in the DirectCores CoreUART datasheet which is available on the Actel website:

http://www.actel.com/ipdocs/CoreUART\_DS.pdf

The CoreConsole CoreUART-APB adds an APB interface which gives access to transmit and receive data registers as well as two control registers and a status register. The CoreUART registers are described in "CoreUART-APB Programmer's Model" on page 35.

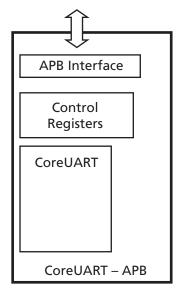

Figure 6-1 shows a block diagram of the CoreUART-APB.

Figure 6-1. CoreUART-APB Block Diagram

CoreUART-APB

## Connecting CoreUART-APB in CoreConsole

Table 6-1 lists the ports present on the CoreUART-APB component and describes how to connect these in CoreConsole.

| Connection                   | CoreConsole Label                                                                          | Description                                                                                                                                                                                                              |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                              | Required Connections                                                                       |                                                                                                                                                                                                                          |  |  |  |

| APB slave interface APBslave |                                                                                            | Connect this interface to any available slave slot on the APB Bus.                                                                                                                                                       |  |  |  |

| PCLK                         | PCLK                                                                                       | APB clock signal.<br>Normally connected to the HCLK output of the MP7Bridge.                                                                                                                                             |  |  |  |

| PRESETn                      | PRESETn Active low APB reset input.<br>Normally connected to the HRESETn output of the MP7 |                                                                                                                                                                                                                          |  |  |  |

| rx                           | rx                                                                                         | Serial receive data input.<br>Normally connected to subsystem toplevel for subsequent connection<br>to a pin of the FPGA.                                                                                                |  |  |  |

| tx                           | tx                                                                                         | Serial transmit data output.<br>Normally connected to subsystem toplevel for subsequent connection<br>to a pin of the FPGA.                                                                                              |  |  |  |

| Optional Connections         |                                                                                            |                                                                                                                                                                                                                          |  |  |  |

| txrdy                        | txrdy                                                                                      | Status output.<br>When low, the transmit data buffer/FIFO is not available for<br>additional transmit data.<br>The level of this signal is also available in the Status Register. (See<br>"Status Register" on page 37.) |  |  |  |

| receive_full receive_full    |                                                                                            | Status output.<br>When high, data is available in the receive data buffer/FIFO.<br>The level of this signal is also available in the Status Register. (See<br>"Status Register" on page 37.)                             |  |  |  |

#### Table 6-1. CoreUART-APB Connections

## **CoreUART-APB Configurable Options**

There are a number of configurable options which apply to the CoreUART-APB; these are detailed in Table 6-2. If a configuration different to the default is required, the user should use the configuration dialog in CoreConsole to select appropriate values for the configurable options.

| Configurable Option    | Default setting | Description                                                                                      |

|------------------------|-----------------|--------------------------------------------------------------------------------------------------|

| Transmit FIFO          | Disabled        | Enables or disables transmit FIFO                                                                |

| Receive FIFO           | Disabled        | Enables or disables receive FIFO                                                                 |

| Mode of operation      | Asynchronous    | Selects mode of operation of CoreUART.<br>Possible settings are "Asynchronous" or "Synchronous". |

| Device family ProASIC3 |                 | Selects target family.<br>Possible settings are "ProASIC3" or "ProASIC3E".                       |

## **CoreUART-APB Programmer's Model**

Table 6-3 lists the registers for CoreUART-APB.

| Table 6-3. CoreUART-APB Reg | isters |

|-----------------------------|--------|

|-----------------------------|--------|

| Address      | Туре       | Width | Reset value | Name   | Description            |

|--------------|------------|-------|-------------|--------|------------------------|

| base + 0x000 | Write      | 32    | 0           | TxData | Transmit Data Register |

| base + 0x004 | Read       | 32    | 0           | RxData | Receive Data Register  |

| base + 0x008 | Read/Write | 32    | 0           | Ctrl1  | Control Register 1     |

| base + 0x00C | Read/Write | 32    | 0           | Ctrl2  | Control Register 2     |

| base + 0x010 | Read       | 32    | 0           | Status | Status Register        |

### **Transmit Data Register**

The 7- or 8- bit transmit data

CoreUART-APB

### **Receive Data Register**

The 7- or 8- bit receive data.

### **Control Register 1**

Control Register 1 contains a single field, Baud value, which is used to set the baud rate for the CoreUART when in asynchronous mode. The Baud value should be set according to the following equation.

Baud value (decimal) = ( clock / ( (baud + 1) x 16) )

where clock is the APB system clock frequency in hertz.

The result of this calculation must be rounded to the nearest integer and converted to hexadecimal to obtain the value which should be written to Control Register 1 (Table 6-4).

For example, when the APB clock frequency is 10 MHz and a baud rate of 9600 is desired, 0x41 should be written to Control Register 1.

Table 6-4. Control Register 1

| Bits | Name                  | Туре | Function                          |

|------|-----------------------|------|-----------------------------------|

| 7:0  | Baud value Read/Write |      | 8 bit value setting the baud rate |

### **Control Register 2**

Control Register 2 (Table 6-5) is used to assign values to the configuration inputs available on the CoreUART.

| Table | 6-5. | Control | Register | 2 |

|-------|------|---------|----------|---|

|       |      |         |          |   |

| Bits | Name       | Туре                                                                                           | Function                                                               |

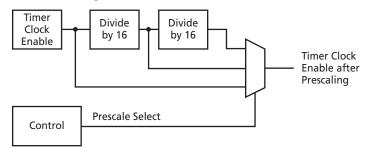

|------|------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|