# **Design Constraints User's Guide**

for Software v9.1

#### Actel Corporation, Mountain View, CA 94043

© 2010 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 5-02-00046-15

Release: November 2010

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

Mentor Graphics, Precision RTL, Exemplar Spectrum, and LeonardoSpectrum are registered trademarks of Mentor Graphics, Inc.

WaveFormer Lite is a registered trademark of SynaptiCAD, Inc.

Synplify is a registered trademark of Synplicity, Inc.

Sun and Sun Workstation, SunOS, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc

Synopsys is a registered trademark of Synopsys, Inc.

Verilog is a registered trademark of Open Verilog International.

Viewlogic, ViewSim, ViewDraw and SpeedWave are trademarks or registered trademarks of Viewlogic Systems, Inc.

Windows is a registered trademark and Windows NT is a trademark of Microsoft Corporation in the U.S. and other countries.

UNIX is a registered trademark of X/Open Company Limited.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

| Design Constraints                                | 9  |

|---------------------------------------------------|----|

| Families Supported                                |    |

| Constraint Support by Family                      |    |

| Constraint Entry                                  |    |

| Constraint File Format by Family                  |    |

| Basic Concepts                                    |    |

| Region                                            |    |

| Location                                          |    |

| I/O Attributes                                    |    |

| Assigning pins in Package Pins View               |    |

| Editing I/O Attributes                            |    |

| Editing Multiple Rows                             |    |

| Sorting Attributes                                |    |

| Formatting Rows and Columns                       |    |

| Manually Assigning Technologies to I/O Banks      | 51 |

| Automatically Assigning Technologies to I/O Banks |    |

| Reserving Pins for Device Migration               |    |

| Specifying an I/O Standard                        |    |

| I/O Attributes                                    | 59 |

| O Attributes by Family or Device                  | 60 |

| Bank Name                                         |    |

| Hold State                                        | 65 |

| Hot Swappable                                     | 66 |

| Input Delay                                       |    |

| I/O Standard                                      | 69 |

| I/O Threshold (or Output Level)                   | 75 |

| Locked                                            | 76 |

| Macro Cell                                        | 77 |

| Output Drive                                      | 78 |

| Output Load or Loading (pf)                       | 79 |

| Output Level                                      |    |

| Pin Number                                        |    |

| Port Name                                         |    |

| Power-up State                                    |    |

| Resistor Pull                                     | 85 |

#### Table of Contents

| Schmitt Trigger                                        |     |

|--------------------------------------------------------|-----|

| Skew                                                   |     |

| Slew                                                   |     |

| Use Register                                           |     |

| Explicitly Reserved                                    |     |

| I/O Bank Settings Dialog Box (IGLOO and ProASIC3 only) |     |

| I/O Bank Settings Dialog Box                           |     |

| More I/O Bank Attributes Dialog Box                    |     |

| Entering Constraints                                   |     |

| Importing Constraint Files                             |     |

| Using GUI Tools                                        |     |

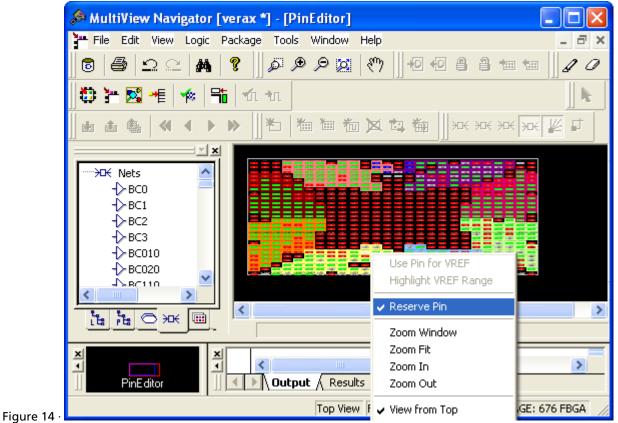

| MultiView Navigator (MVN)                              |     |

| Exporting Constraint Files                             |     |

| Constraints by Name: Timing                            |     |

| Create Clock                                           |     |

| Create Generated Clock                                 |     |

| Set Clock Latency                                      |     |

| Set False Path                                         |     |

| Set Input Delay                                        |     |

| Set Load on Output Port                                |     |

| Set Maximum Delay                                      |     |

| Set Minimum Delay                                      |     |

| Set Multicycle Path                                    |     |

| Set Output Delay                                       |     |

| Constraints by Name: Physical                          |     |

| Assign I/O to Pin                                      |     |

| Assign I/O Macro to Location                           |     |

| Assign Macro to Region                                 |     |

| Assign Net to Global Clock                             | 141 |

| Assign Net to Local Clock                              |     |

| Assign Net to Quadrant Clock                           |     |

| Assign Net to Region                                   |     |

| Configure I/O Bank                                     |     |

| Create Region                                          |     |

| Delete Regions                                         |     |

| Move Block                                             |     |

| Move Region                                            |     |

| Reserve Pins                                   | 159 |

|------------------------------------------------|-----|

| Reset Attributes on an I/O to Default Settings | 161 |

| Reset an I/O Bank to Default Settings          | 163 |

| Reset Net's Criticality to Default Level       | 165 |

| Set Block Options                              | 167 |

| Set Net's Criticality                          | 169 |

| Set Port Block                                 |     |

| Unassign I/O Macro from Location               | 173 |

| Unassign Macro from Region                     | 175 |

| Unassign Macro(s) Driven by Net from Region    | 177 |

| Unreserve Pins                                 | 179 |

# Constraints by Name: Netlist Optimization 181 Delete Buffer Tree 182 Demote Global Net to Regular Net 184 Promote Regular Net to Global Net. 186

| Promote Regular Net to Global Net | 186 |

|-----------------------------------|-----|

| Restore Buffer Tree               | 188 |

| Set Preserve                      | 190 |

#### Constraints by File Format - SDC Command Reference ...... 192

| About Synopsys Design Constraints (SDC) Files | 193 |

|-----------------------------------------------|-----|

| SDC Syntax Conventions                        | 194 |

| create_clock                                  | 196 |

| create_generated_clock                        | 198 |

| set_clock_latency                             |     |

| set_false_path                                |     |

| set_input_delay                               |     |

| set_load                                      | 211 |

| set_max_delay (SDC)                           |     |

| set_multicycle_path                           |     |

| set_output_delay                              |     |

# Design Object Access Commands220all\_inputs221all\_registers222all\_registers224get cells226get\_clocks227get\_pins228get\_nets229get\_ports230About Physical Design Constraint (PDC) Files231PDC Syntax Conventions234

Table of Contents

| GCF Syntax Conventions                                            |  |

|-------------------------------------------------------------------|--|

| About GCF Files                                                   |  |

| Constraints by File Format: GCF Command Reference                 |  |

| unreserve                                                         |  |

| undefine_region                                                   |  |

| unassign_quadrant_clock                                           |  |

| unassign_net_macros                                               |  |

| unassign_macro_from_region                                        |  |

| unassign_local_clock                                              |  |

| unassign_global_clock                                             |  |

| set_preserve                                                      |  |

| set_port_block                                                    |  |

| set_net_critical                                                  |  |

| set_multitile_location (IGLOO, Fusion, and ProASIC3)              |  |

| set_location                                                      |  |

| set_iobank (Axcelerator)                                          |  |

| set_iobank (IGLOO and ProASIC3)                                   |  |

| set_iobank (IGLOOe, IGLOO PLUS, Fusion, ProASIC3L, and ProASIC3E) |  |

| set_io (Axcelerator)                                              |  |

| set_io (IGLOO and ProASIC3)                                       |  |

| set_io (IGLOO PLUS)                                               |  |

| set_io (IGLOOe, Fusion, ProASIC3L, and ProASIC3E)                 |  |

| set_block_options                                                 |  |

| reset_net_critical                                                |  |

| reset_iobank                                                      |  |

| reset_io                                                          |  |

| reset_floorplan                                                   |  |

| reserve                                                           |  |

| move_region                                                       |  |

| move_block                                                        |  |

| dont_touch_buffer_tree                                            |  |

| delete_buffer_tree                                                |  |

| define_region                                                     |  |

| assign_region                                                     |  |

| assign_quadrant_clock                                             |  |

| assign_net_macros                                                 |  |

| assign_local_clock (Axcelerator)                                  |  |

| assign_local_clock (IGLOO, ProASIC3, SmartFusion and Fusion)      |  |

| assign_global_clock                                               |  |

| PDC Naming Conventions                                            |  |

| Placement Constraints                                                                  | .322   |

|----------------------------------------------------------------------------------------|--------|

| Macro                                                                                  | .323   |

| Package Pin and Pad Location                                                           | . 325  |

| net_critical_ports                                                                     | .326   |

| set_critical                                                                           | .327   |

| set_critical_port                                                                      | .328   |

| set_empty_io                                                                           | .329   |

| set_empty_location                                                                     | .330   |

| set_initial_io                                                                         | .331   |

| set_initial_location                                                                   | . 332  |

| set_io                                                                                 | .333   |

| set_io_region                                                                          | .334   |

| set_location                                                                           |        |

| set_memory_region                                                                      | .337   |

| set_net_region                                                                         | .338   |

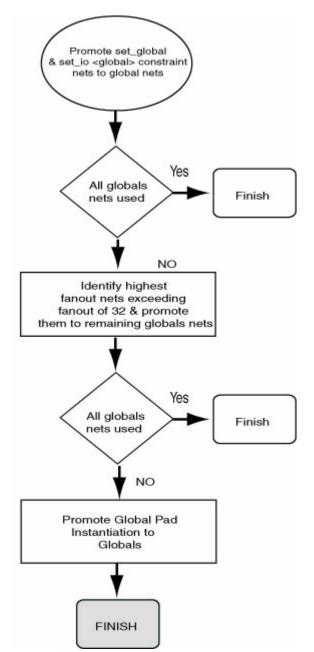

| About Global Resource Constraints                                                      | . 339  |

| Priority Order for Global Promotion                                                    | .340   |

| dont_fix_globals                                                                       | .342   |

| read                                                                                   | .343   |

| set_auto_global                                                                        |        |

| set_auto_global_fanout                                                                 | . 345  |

| set_global                                                                             | .346   |

| set_noglobal                                                                           | .347   |

| use_global                                                                             | .348   |

| Netlist Optimization Constraints                                                       | .351   |

| dont_optimize                                                                          |        |

| dont_touch                                                                             | .354   |

| Optimize                                                                               | .355   |

| set_max_fanout                                                                         | . 356  |

|                                                                                        |        |

| I/O Standards                                                                          |        |

| I/O Standards Table                                                                    |        |

| I/O Standards Compatibility Matrix                                                     | .367   |

| IGLOOe, ProASIC3L, ProASIC3E, SmartFusion and Fusion I/O Standards Compatibility Matri | rix368 |

| IGLOO, IGLOO PLUS, and ProASIC3 I/O Standards Compatibility Matrix                     | .370   |

| Axcelerator I/O Standards Compatibility Matrix                                         | .371   |

| I/O Standards and I/O Attributes Applicability                                         | .373   |

| IGLOOe, ProASIC3L, ProASIC3E, SmartFusion and Fusion I/O Standards and I/O Attributes  |        |

| Applicability                                                                          |        |

| IGLOO and ProASIC3 I/O Standards and Attributes Applicability                          |        |

| Axcelerator I/O Standards and I/O Attributes Applicability                             | .377   |

| Product Support                                                                        | 379    |

Table of Contents

# **Design Constraints**

Design constraints are usually either requirements or properties in your design. You use constraints to ensure that your design meets its performance goals and pin assignment requirements.

The Designer software supports both timing and physical constraints. In addition, it supports netlist optimization constraints. You can set constraints by either using Actel's interactive tools or by importing constraint files directly into your design session.

#### **Timing Constraints**

Timing constraints represent the performance goals for your designs. Designer software uses timing constraints to guide the timing-driven optimization tools in order to meet these goals.

You can set timing constraints either globally or to a specific set of paths in your design.

You can apply timing constraints to:

- Specify the required minimum speed of a clock domain

- Set the input and output port timing information

- Define the maximum delay for a specific path

- Identify paths that are considered false and excluded from the analysis

- Identify paths that require more than one clock cycle to propagate the data

- Provide the external load at a specific port

To get the most effective results from the Designer software, you need to set the timing constraints close to your design goals. Sometimes slightly tightening the timing constraint helps the optimization process to meet the original specifications.

#### **Physical Constraints**

Designer software enables you to specify the physical constraints to define the size, shape, utilization, and pin/pad placement of a design. You can specify these constraints based on the utilization, aspect ratio, and dimensions of the die. The pin/pad placement depends on the external physical environment of the design, such as the placement of the device on the board.

There are three types of physical constraints:

- I/O assignments

- Set location, attributes, and technologies for I/O ports

- Specify special assignments, such as VREF pins and I/O banks

- Location and region assignments

#### Design Constraints

- Set the location of Core, RAM, and FIFO macros

- Create Regions for I/O and Core macros as well as modify those regions

- Clock assignments

- Assign nets to clocks

- Assign global clock constraints to global, quadrant, and local clock resources

#### **Netlist Optimization Constraints**

The Designer software enables you to set some advanced design-specific netlist optimizing constraints.

You can apply netlist optimization constraints to:

- Delete or restore a buffer tree

- Manage the fan-outs of the nets

- Manage macro combinations (for example, IO-REG combining)

- Optimize a netlist by removing buffers and/or inverters, propagating constants, and so on

#### See Also

Constraint Support by Family

Constraint Entry Table

Constraint File Format by Family

Designer Naming Conventions

Designer Naming Conventions

# **Families Supported**

# **Constraint Support by Family**

Use the Constraint Family Support table to see which constraints you can use for your device family. Click the name of a constraint in the table for more information about it.

|                                                     | IGLOO | SmartFusion<br>and Fusion |   |   |     | Axcelerator                | r – | 1 | SX | MX | DX | ACT1 | ACt2/1200XL | ACT3 |

|-----------------------------------------------------|-------|---------------------------|---|---|-----|----------------------------|-----|---|----|----|----|------|-------------|------|

|                                                     |       |                           |   |   | Tim | ing                        |     |   |    |    |    |      |             |      |

| <u>Create a</u><br><u>clock</u>                     | Х     | Х                         | Х | Х | Х   | Х                          | Х   | Х | Х  | Х  | Х  | Х    | Х           | Х    |

| <u>Create a</u><br>generated<br>clock               | Х     | Х                         | Х | Х | Х   | Х                          | х   | Х |    |    |    |      |             |      |

| <u>Remove</u><br><u>clock</u><br><u>uncertainty</u> | Х     | Х                         | Х | Х | Х   | Х                          | х   | Х |    |    |    |      |             |      |

| <u>Set clock</u><br>latency                         | Х     | Х                         | Х | Х | Х   | Х                          | х   | Х |    |    |    |      |             |      |

| <u>Set clock</u><br>uncertainty                     | Х     | X                         | Х | Х | Х   | Х                          | Х   | Х |    |    |    |      |             |      |

| <u>Set disable</u><br><u>timing</u>                 | Х     | Х                         | Х |   |     | X<br>(including<br>RTAX-S) |     |   |    |    |    |      | Х           | Х    |

| <u>Set false</u><br><u>path</u>                     | Х     | Х                         | Х | Х | Х   | Х                          | х   | Х | Х  | Х  | Х  | Х    | Х           | Х    |

| <u>Set input</u><br><u>delay</u>                    | Х     | Х                         | Х | Х |     | Х                          |     |   |    |    |    |      |             |      |

| <u>Set load</u><br>on output<br>port                | Х     | Х                         | Х | Х | X   | Х                          | х   | Х |    |    |    |      |             |      |

Table 1 · Constraint Support by Family

#### Designer Naming Conventions

|                                                                   | IGLOO    | SmartFusion<br>and Fusion | ProASIC3 | ProASIC<br>Plus | ProASIC    | Axcelerator | eX       | SX-<br>A | SX | MX | DX       | ACT1     | ACt2/1200XL | ACT3     |

|-------------------------------------------------------------------|----------|---------------------------|----------|-----------------|------------|-------------|----------|----------|----|----|----------|----------|-------------|----------|

|                                                                   |          |                           |          |                 | Tim        | ing         | •        |          | •  |    |          |          |             |          |

| <u>Set</u><br><u>maximum</u><br><u>delay</u>                      | Х        | Х                         | Х        | Х               | Х          | Х           | Х        | Х        | Х  | Х  | Х        | Х        | Х           | Х        |

| <u>Set</u><br>minimum<br>delay                                    | Х        | Х                         | Х        | Х               | Х          | Х           | х        | Х        | Х  | Х  | Х        | Х        | Х           | Х        |

| <u>Set</u><br>multicycle<br>path                                  | Х        | Х                         | Х        | Х               |            | Х           |          |          |    |    |          |          |             |          |

| <u>Set output</u><br><u>delay</u>                                 | Х        | Х                         | Х        | Х               |            | Х           |          |          |    |    |          |          |             |          |

|                                                                   |          |                           |          |                 | Physical F | lacement    | •        |          |    |    |          |          |             | •        |

|                                                                   |          |                           |          |                 | -Clo       | ocks        |          |          |    |    |          |          |             |          |

| <u>Assign</u><br>Net to<br><u>Global</u><br><u>Clock</u>          | Х        | X                         | Х        | Х               | Х          |             |          |          |    |    |          |          |             |          |

| <u>Assign</u><br><u>Net to</u><br><u>Local</u><br><u>Clock</u>    | Х        | Х                         | X        | Х               | Х          | Х           |          |          |    |    |          |          |             |          |

| <u>Assign</u><br><u>Net to</u><br><u>Quadrant</u><br><u>Clock</u> | Х        | Х                         | X        |                 |            |             |          |          |    |    |          |          |             |          |

|                                                                   | <u> </u> | <u> </u>                  | <u> </u> | <u> </u>        | -Reg       | rions       | <u> </u> | <u> </u> | 1  |    | <u> </u> | <u> </u> | <u> </u>    | <u>I</u> |

#### Families Supported

|                                                                      | IGLOO | SmartFusion<br>and Fusion | ProASIC3 | ProASIC<br>Plus | ProASIC | Axcelerator | eX | SX-<br>A | SX | MX | DX | ACT1 | ACt2/1200XL | ACT3 |

|----------------------------------------------------------------------|-------|---------------------------|----------|-----------------|---------|-------------|----|----------|----|----|----|------|-------------|------|

|                                                                      |       |                           |          |                 | Tim     | ing         |    |          | •  |    |    |      |             |      |

| <u>Assign</u><br><u>Macro to</u><br><u>Region</u>                    | Х     | Х                         | Х        | Х               | Х       | Х           |    |          |    |    |    |      |             |      |

| <u>Assign</u><br><u>Net to</u><br><u>Region</u>                      | Х     | Х                         | Х        | Х               | Х       | Х           |    |          |    |    |    |      |             |      |

| <u>Create</u><br><u>Region</u>                                       | Х     | Х                         | Х        | Х               | Х       | Х           |    |          |    |    |    |      |             |      |

| <u>Delete</u><br><u>Regions</u>                                      | Х     | Х                         | Х        | Х               | Х       | Х           |    |          |    |    |    |      |             |      |

| <u>Move</u><br><u>Region</u>                                         | Х     | Х                         | Х        | Х               | Х       | Х           |    |          |    |    |    |      |             |      |

| <u>Unassign</u><br><u>macro(s)</u><br><u>driven by</u><br><u>net</u> | Х     | Х                         | Х        | Х               | Х       | X           |    |          |    |    |    |      |             |      |

| <u>Unassign</u><br><u>Macro</u><br>from<br>Region                    | Х     | Х                         | Х        | X               | X       | Х           |    |          |    |    |    |      |             |      |

|                                                                      |       |                           |          |                 | -I/     | Os          |    | 1        |    | 1  |    |      |             |      |

| <u>Assign</u><br>I/O to pin                                          | Х     | Х                         | Х        | Х               | Х       | Х           | X  | х        | X  | Х  | Х  | X    | Х           | Х    |

| <u>Assign</u><br><u>I/O Macro</u><br><u>to</u><br><u>Location</u>    | Х     | Х                         | Х        | Х               | Х       | X           |    |          |    |    |    |      |             |      |

|                                                                         | IGLOO | SmartFusion<br>and Fusion | ProASIC3 | ProASIC<br>Plus | ProASIC | Axcelerator | eX | SX-<br>A | SX | MX | DX | ACT1 | ACt2/1200XL | ACT3 |

|-------------------------------------------------------------------------|-------|---------------------------|----------|-----------------|---------|-------------|----|----------|----|----|----|------|-------------|------|

|                                                                         |       |                           |          |                 | Tim     | ing         |    |          |    |    |    |      |             |      |

| <u>Configure</u><br><u>I/O Bank</u>                                     | Х     | Х                         | Х        |                 |         | Х           |    |          |    |    |    |      |             |      |

| Reset<br>attributes<br>on I/O to<br>default<br>settings                 | X     | Х                         | Х        | Х               | Х       | Х           |    |          |    |    |    |      |             |      |

| <u>Reset I/O</u><br><u>bank to</u><br><u>default</u><br><u>settings</u> | Х     | Х                         | Х        |                 |         | Х           |    |          |    |    |    |      |             |      |

| <u>Reserve</u><br><u>pins</u>                                           | Х     | Х                         | Х        | Х               | Х       | Х           | Х  |          |    |    |    |      |             |      |

| <u>Unreserve</u><br><u>pins</u>                                         | Х     | Х                         | Х        | Х               | Х       | Х           | Х  |          |    |    |    |      |             |      |

| <u>Unassign</u><br><u>I/O macro</u><br><u>from</u><br><u>location</u>   | х     | X                         | Х        | Х               | Х       | Х           |    |          |    |    |    |      |             |      |

|                                                                         |       |                           |          |                 | -B1     | ock         | •  |          | •  |    |    |      |             |      |

| <u>Move</u><br><u>Block</u>                                             | Х     | Х                         | Х        |                 |         | Х           |    |          |    |    |    |      |             |      |

| <u>Set port</u><br><u>block</u>                                         | Х     | Х                         | Х        |                 |         | Х           |    |          |    |    |    |      |             |      |

| <u>Set Block</u><br>Options                                             | Х     | Х                         | Х        |                 |         | Х           |    |          |    |    |    |      |             |      |

#### Families Supported

|                                                                 |   |   |   |   | -N         | ets        |  | <br> |  |  |

|-----------------------------------------------------------------|---|---|---|---|------------|------------|--|------|--|--|

| <u>Assign</u><br><u>Net to</u><br><u>Global</u><br><u>Clock</u> | X | Х | Х | X | Х          |            |  |      |  |  |

| <u>Assign</u><br><u>Net to</u><br><u>Local</u><br><u>Clock</u>  | Х | X | Х | Х | Х          | Х          |  |      |  |  |

| Assign<br><u>Net to</u><br><u>Quadrant</u><br><u>Clock</u>      | х | Х | Х |   |            |            |  |      |  |  |

| <u>Assign</u><br><u>Net to</u><br><u>Region</u>                 | X | Х | Х | Х | Х          | Х          |  |      |  |  |

| Reset net's<br>criticality<br>to default<br>level               |   |   |   |   |            | Х          |  |      |  |  |

| <u>Set Net's</u><br><u>Criticality</u>                          |   |   |   |   |            | Х          |  |      |  |  |

| <u>Unassign</u><br>macro(s)<br>driven by<br><u>net</u>          | Х | Х | Х | Х |            | Х          |  |      |  |  |

|                                                                 |   |   | · |   | Netlist Op | timization |  |      |  |  |

| <u>Delete</u><br><u>buffer tree</u>                             | Х | Х | Х |   |            |            |  |      |  |  |

| Demote                                                          | Х | Х | Х | Х | Х          |            |  |      |  |  |

#### Designer Naming Conventions

|                                                                | IGLOO            | SmartFusion<br>and Fusion | ProASIC3 | ProASIC<br>Plus | ProASIC | Axcelerator | еX | SX-<br>A | SX | MX | DX | ACT1 | ACt2/1200XL | ACT3 |

|----------------------------------------------------------------|------------------|---------------------------|----------|-----------------|---------|-------------|----|----------|----|----|----|------|-------------|------|

|                                                                | Timing           |                           |          |                 |         |             |    |          |    |    |    |      |             |      |

| <u>Global</u><br><u>Net to</u><br><u>Regular</u><br><u>Net</u> | let to<br>egular |                           |          |                 |         |             |    |          |    |    |    |      |             |      |

| Promote<br>regular net<br>to global<br>net                     | Х                | Х                         | Х        | Х               | Х       |             |    |          |    |    |    |      |             |      |

| <u>Restore</u><br><u>buffer tree</u>                           | Х                | Х                         | Х        | Х               | Х       |             |    |          |    |    |    |      |             |      |

| <u>Set</u><br>preserve                                         | Х                | Х                         | Х        |                 |         | Х           |    |          |    |    |    |      |             |      |

#### See Also

Constraint Entry Table

Constraint File Format by Family

# **Constraint Entry**

Use the Constraint Entry table to see which tools and file formats you can use to enter constraints for your device family.

Click the name of a constraint, a constraint entry tool, file format type, editor, or checkmark in the table for more information about that item.

| Constraint                                          | SDC | GDC | PDC | PIN | DCF | ChipPlanner | I/O<br>Attribute<br>Editor | PinEditor | SmartTime,<br>Timer | Compile<br>Options |

|-----------------------------------------------------|-----|-----|-----|-----|-----|-------------|----------------------------|-----------|---------------------|--------------------|

|                                                     |     |     |     |     |     | Timing      |                            |           |                     |                    |

| <u>Create a</u><br><u>clock</u>                     | X   |     |     |     | X   |             |                            |           | X                   |                    |

| <u>Create a</u><br>generated<br>clock               | X   |     |     |     |     |             |                            |           | X                   |                    |

| <u>Remove</u><br><u>clock</u><br><u>uncertainty</u> | X   |     |     |     |     |             |                            |           | X                   |                    |

| <u>Set clock</u><br><u>latency</u>                  | X   |     |     |     |     |             |                            |           | X                   |                    |

| <u>Set clock</u><br><u>uncertainty</u>              | X   |     |     |     |     |             |                            |           | X                   |                    |

| <u>Set disable</u><br><u>timing</u>                 | X   |     |     |     |     |             |                            |           | X                   |                    |

| <u>Set false</u><br><u>path</u>                     | X   |     |     |     | X   |             |                            |           | X                   |                    |

| <u>Set input</u><br><u>delay</u>                    | X   |     |     |     |     |             |                            |           | X                   |                    |

| <u>Set load on</u><br>output port                   | X   |     |     |     | X   |             | X                          | X         | X                   |                    |

Table 2 · Constraint Entry by Tool and File Format

| Constraint                                                        | SDC | GDC | PDC | PIN | DCF | ChipPlanner    | I/O<br>Attribute<br>Editor | PinEditor | SmartTime,<br>Timer | Compile<br>Options |

|-------------------------------------------------------------------|-----|-----|-----|-----|-----|----------------|----------------------------|-----------|---------------------|--------------------|

|                                                                   |     |     |     |     |     | Timing         |                            |           |                     |                    |

| <u>Set</u><br><u>maximum</u><br><u>delay</u>                      | X   |     |     |     | X   |                |                            |           | X                   |                    |

| <u>Set</u><br>minimum<br>delay                                    | X   |     |     |     |     |                |                            |           | X                   |                    |

| <u>Set</u><br><u>multicycle</u><br><u>path</u>                    | X   |     |     |     |     |                |                            |           | X                   |                    |

| <u>Set output</u><br><u>delay</u>                                 | X   |     |     |     |     |                |                            |           | X                   |                    |

|                                                                   |     |     |     |     | Ph  | ysical Placeme | nt                         |           |                     |                    |

|                                                                   | r   | 1   | r   | r   | [   | -Clocks        | r                          |           |                     |                    |

| <u>Assign Net</u><br><u>to Global</u><br><u>Clock</u>             |     | X   | X   |     |     |                |                            |           |                     |                    |

| <u>Assign Net</u><br><u>to Local</u><br><u>Clock</u>              |     | X   | X   |     |     | X              |                            |           |                     |                    |

| <u>Assign Net</u><br><u>to</u><br><u>Quadrant</u><br><u>Clock</u> |     |     | X   |     |     | X              |                            |           |                     |                    |

|                                                                   |     |     |     |     |     | -Regions       |                            |           |                     |                    |

| <u>Assign</u><br><u>Macro to</u><br><u>Region</u>                 |     |     | X   |     |     | X              |                            |           |                     |                    |

#### Families Supported

| Constraint                                                           | SDC | GDC | PDC | PIN | DCF | ChipPlanner | I/O<br>Attribute<br>Editor | PinEditor | SmartTime,<br>Timer | Compile<br>Options |

|----------------------------------------------------------------------|-----|-----|-----|-----|-----|-------------|----------------------------|-----------|---------------------|--------------------|

|                                                                      |     |     |     |     |     | Timing      |                            |           |                     |                    |

| <u>Assign Net</u><br><u>to Region</u>                                |     | X   | X   |     |     | X           |                            |           |                     |                    |

| <u>Create</u><br><u>Region</u>                                       |     | X   | X   |     |     | X           |                            |           |                     |                    |

| <u>Delete</u><br><u>Regions</u>                                      |     |     | X   |     |     | X           |                            |           |                     |                    |

| <u>Move</u><br>region                                                |     |     | X   |     |     | X           |                            |           |                     |                    |

| <u>Unassign</u><br><u>macro(s)</u><br><u>driven by</u><br><u>net</u> |     |     | X   |     |     | X           |                            |           |                     |                    |

| <u>Unassign</u><br><u>macro</u><br><u>from</u><br><u>region</u>      |     |     | X   |     |     | X           |                            |           |                     |                    |

|                                                                      |     |     |     |     |     | -I/Os       |                            |           |                     |                    |

| <u>Assign I/O</u><br><u>to pin</u>                                   |     | X   | X   | X   |     | X           | X                          | X         |                     |                    |

| Assign I/O<br>Macro to<br>Location                                   |     | X   | X   |     |     | X           |                            |           |                     |                    |

| <u>Configure</u><br><u>I/O Bank</u>                                  |     |     | X   |     |     | Χ           |                            | X         |                     |                    |

| <u>Reset</u><br>attributes                                           |     |     | X   |     |     | X           | X                          |           |                     |                    |

Designer Naming Conventions

| Constraint                                                              | SDC | GDC | PDC | PIN | DCF | ChipPlanner | I/O<br>Attribute<br>Editor | PinEditor | SmartTime,<br>Timer | Compile<br>Options |

|-------------------------------------------------------------------------|-----|-----|-----|-----|-----|-------------|----------------------------|-----------|---------------------|--------------------|

|                                                                         |     |     |     |     |     | Timing      |                            |           |                     |                    |

| <u>on I/O to</u><br><u>default</u><br><u>settings</u>                   |     |     |     |     |     |             |                            |           |                     |                    |

| <u>Reset I/O</u><br><u>bank to</u><br><u>default</u><br><u>settings</u> |     |     | X   |     |     | Χ           | X                          |           |                     |                    |

| <u>Reserve</u><br><u>pins</u>                                           |     |     | X   |     |     |             | X                          | X         |                     |                    |

| <u>Unreserve</u><br><u>pins</u>                                         |     |     | X   |     |     |             | X                          | X         |                     |                    |

| <u>Unassign</u><br><u>I/O macro</u><br><u>from</u><br><u>location</u>   |     |     | X   |     |     | X           |                            |           |                     |                    |

|                                                                         |     |     |     |     |     | -Blocks     | I                          |           |                     | I                  |

| <u>Move</u><br><u>Block</u>                                             |     |     | X   |     |     |             |                            |           |                     |                    |

| <u>Set port</u><br><u>block</u>                                         |     |     | X   |     |     | X           |                            |           |                     |                    |

| <u>Set Block</u><br>Options                                             |     |     | X   |     |     |             |                            |           |                     | X                  |

|                                                                         |     |     |     |     |     | -Nets       |                            |           |                     |                    |

| <u>Assign Net</u><br><u>to Global</u><br><u>Clock</u>                   |     | X   | X   |     |     |             |                            |           |                     |                    |

#### Families Supported

| Constraint                                                            | SDC | GDC | PDC | PIN | DCF | ChipPlanner      | I/O<br>Attribute<br>Editor | PinEditor | SmartTime,<br>Timer | Compile<br>Options |

|-----------------------------------------------------------------------|-----|-----|-----|-----|-----|------------------|----------------------------|-----------|---------------------|--------------------|

|                                                                       |     | 1   | 1   |     | 1   | Timing           |                            |           |                     |                    |

| <u>Assign Net</u><br><u>to Local</u><br><u>Clock</u>                  |     | X   | X   |     |     | X                |                            |           |                     |                    |

| <u>Assign Net</u><br><u>to</u><br><u>Quadrant</u><br><u>Clock</u>     |     |     | X   |     |     | Χ                |                            |           |                     |                    |

| <u>Assign Net</u><br><u>to Region</u>                                 |     | X   | X   |     |     | X                |                            |           |                     |                    |

| <u>Reset net's</u><br>criticality<br>to default<br><u>level</u>       |     |     | X   |     |     |                  |                            |           |                     |                    |

| <u>Set Net's</u><br><u>Criticality</u>                                |     | X   | X   |     |     |                  |                            |           |                     |                    |

| <u>Unassign</u><br><u>macro(s)</u><br>driven by<br><u>net</u>         |     |     | X   |     |     | X                |                            |           |                     |                    |

|                                                                       |     |     |     |     | Ne  | tlist Optimizati | ion                        |           |                     |                    |

| <u>Delete</u><br><u>buffer tree</u>                                   |     | X   | X   |     |     |                  |                            |           |                     | X                  |

| <u>Demote</u><br><u>Global Net</u><br><u>to Regular</u><br><u>Net</u> |     | X   | X   |     |     |                  |                            |           |                     | X                  |

| Promote                                                               |     | X   | X   |     |     |                  |                            |           |                     | X                  |

#### Designer Naming Conventions

| Constraint                                           | SDC | GDC | PDC | PIN | DCF | ChipPlanner | I/O<br>Attribute<br>Editor | PinEditor | SmartTime,<br>Timer | Compile<br>Options |

|------------------------------------------------------|-----|-----|-----|-----|-----|-------------|----------------------------|-----------|---------------------|--------------------|

|                                                      |     |     |     |     |     | Timing      |                            |           |                     |                    |

| <u>regular net</u><br><u>to global</u><br><u>net</u> |     |     |     |     |     |             |                            |           |                     |                    |

| <u>Restore</u><br><u>buffer tree</u>                 |     | X   | X   |     |     |             |                            |           |                     |                    |

| <u>Set</u><br><u>preserve</u>                        |     |     | X   |     |     |             |                            |           |                     |                    |

#### See Also

Constraint Support by Family

Constraint File Format by Family

# **Constraint File Format by Family**

Use the File Format by Family table to see which file formats apply to each type of constraint and each device family.

| Family               | Tir | ning | Physi | cal Plac | ement | Netlist Op | otimiization |

|----------------------|-----|------|-------|----------|-------|------------|--------------|

|                      | SDC | DCF  | PDC   | PIN      | GCF   | PDC        | GCF          |

| IGLOO                | Х   |      | Х     |          |       |            |              |

| SmartFusion / Fusion | Х   |      | Х     |          |       | Х          |              |

| ProASIC3             | Х   |      | Х     |          |       |            |              |

| ProASIC PLUS         | Х   |      |       |          | Х     |            | Х            |

| ProASIC              | Х   |      |       |          | Х     |            | Х            |

| Axcelerator          | Х   |      | Х     |          |       | Х          |              |

| eX                   | Х   | х    |       | х        |       |            |              |

| SX-A                 | Х   | х    |       | х        |       |            |              |

| SX                   |     | Х    |       | х        |       |            |              |

| MX                   |     | х    |       | х        |       |            |              |

| DX                   |     | Х    |       | х        |       |            |              |

| АСТ3                 |     | Х    |       | Х        |       |            |              |

| ACT2/1200XL          |     | Х    |       | Х        |       |            |              |

| ACT1                 |     | Х    |       | Х        |       |            |              |

Table 3 · Constraint File Format by Family

SDC - Synopsys Design Constraints

PDC - Physical Design Constraints for IGLOO, ProASIC3, SmartFusion, Fusion, and Axcelerator

GCF – Design Constraints Format for  $\ensuremath{\text{ProASIC}}^{\ensuremath{\text{PLUS}}}$  and  $\ensuremath{\text{ProASIC}}$

DCF - Actel Design Constraints Format

PIN - Pin location constraints

#### See Also

Constraint Support by Family

Constraint Entry Table

# **Basic Concepts**

# **Designer Naming Conventions**

The names of ports, instances, and nets in an imported netlist are sometimes referred to as their original names. Port names appear exactly as they are defined in a netlist. For example, a port named A/B appears as A/B in ChipPlanner, PinEditor, and I/O Attribute Editor in MultiView Navigator. Instances and nets display the original names plus an escape character (\) before each backslash (/) and each slash (\) that is not a hierarchy separator. For example, the instance named A/B is displayed as A/\\B.

Following are Designer's naming conventions by device.

#### SmartFusion, Fusion, ProASIC3, and Axcelerator

The following components use the Tcl-compliant original names:

- PDC reader/writer

- SDC reader/writer

- Compile report

- SDF/Netlist writer for back annotation

- MultiView Navigator tools: NetlistViewer, PinEditor, ChipPlanner, and I/O Attribute Editor

- SmartTime

- SmartPower

#### **ProASIC**, **ProASIC**<sup>PLUS</sup>, **SX-A**, and **eX**

The following components use the Tcl-compliant original names:

- SDC reader/writer

- MultiView Navigator tools: NetlistViewer, PinEditor, ChipPlanner, and I/O Attribute Editor

- SmartTime

GCF follows the netlist original names; therefore, use the original names when referring to ports, instances, and nets in GCF files.

#### See Also

PDC Naming Conventions

# Clock

Specifying clock constraints is the most effective way of constraining and verifying the timing behavior of a sequential design. You must use clock constraints to meet your performance goals and to quickly reach timing closure.

Actel recommends that you specify and constrain all clocks used in the design.

To create a clock constraint, you must provide the following clock information:

Clock sourceSpecifies the pin or port where the clock signal is defined.

Clock period or frequency: Defines the smallest amount of time after which the signal repeats itself.

Duty cycle: Defines the percentage of time during which the clock period is high.

First edge: Indicates whether the first edge of the clock is rising or falling.

Offset: Indicates the shift of the first edge with respect to instant zero common to all clocks in the design.

#### **Example 1:**

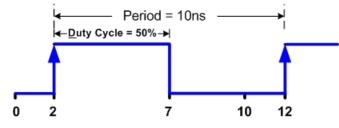

create\_clock -period 10 -waveform {2 7}

This example creates a clock with 10ns period, 2ns offset, and 50% duty cycle using the SDC command.

#### **Example 2:**

This example shows how to create a clock with 25MHz frequency, 4ns offset for its first rising edge, and 60% duty cycle using the SmartTime Constraints Editor. Using the Create New Clock Constraint dialog box is equivalent to using the SDC command: create\_clock -period 40 -waveform {4, 28}.

#### Basic Concepts

| Create New Clock Constraint                 |        |

|---------------------------------------------|--------|

| Source Pin: Clock_main                      |        |

| T(zero)                                     | 25 MHz |

| ← Duty Cycle: →<br>60 %<br>Comment:<br>4 ns |        |

| OK Cancel                                   | Help   |

#### See Also

Constraint support by family

Constraint entry table

create\_clock (SDC)

global\_clocks (DCF)

Specifying a clock constraint

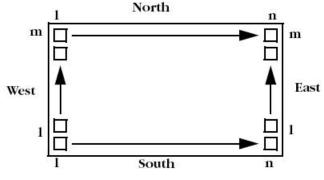

# Region

A region is a user-defined area on a chip into which you can constrain the physical placement of one or more macros. You can also constrain macros containing multiple tiles for cores, RAMs, and I/Os. The floorplanning process usually requires you to create several regions and assign logic to them. Logic can include core logic, memory, and I/O modules. When you run the place-and-route tool, it places the logic into their assigned regions.

Some regions are user-defined and others are automatically created by the tools to meet routing requirements (for example, Local clock regions).

You can use region constraints to:

- Create user-defined regions such as Inclusive, Exclusive, Empty, LocalClock, and QuadrantClock

- Assign and unassign macros to user-defined regions

- Constrain all the macros connected to a net by assigning them to a specific net region

- Move regions from one set of co-ordinates to another

#### See Also

Assign Macro to Region

Create Region

Delete Region

Move Region

Unassign macro from region

MultiView Navigator User's Guide: About Floorplanning, Creating Regions, Editing Regions

# Location

Each core, RAM, and I/O macro in the design is associated with a location on the device. When you run the placeand-route tool, it places all of your logic into their assigned locations.

You can use location constraints to:

- Overwrite the existing placements of macros

- Tell the place-and-route tool where to initially place the macros

- Assign I/O macros to specific pins to meet your board's requirements

#### See Also

Assign I/O to pin

Assign macro to location

Unassign macro from location

MultiView Navigator User's Guide: Assigning Logic to Locations, Moving Logic to Other Locations, Assigning Pins, Unassigning Pins

## I/O Attributes

I/O attributes are the characteristics of logic macros or nets in your design. They indicate placement, implementation, naming, directionality, and other characteristics. This information is used by the design implementation software during the place-and-route of a design.

Input and output attributes are described in the documentation for the I/O Attribute Editor. Attributes applicable to a specific tool are described in the documentation for that tool.

See the topics in <u>I/O Attributes Reference</u> for more detailed information about each attribute. See also , for a table of attributes for each device family, and <u>Welcome to I/O Attribute Editor</u>.

#### See Also

I/O Attributes by Family

I/O Standards and I/O Attributes Applicability

I/O Standards Compatibility Matrix

# About the I/O Attribute Editor

The I/O Attribute editor is available from the Libero IDE Project Manager, in the SmartDesign Microcontroller Subsystem configurator, and from MultiView Navigator.

#### **I/O Attribute Editor Features**

The I/O Attribute Editor is a graphical editor that enables you to:

- Create a new physical design I/O constraint

- Modify existing physical I/O constraints

- Import PDC I/O constraint files

- Automatically extract the ports at the top level of an HDL file

- Add, modify, or delete physical I/O constraints from SmartDesign

#### I/O Attribute Editor Advantages

- You can create and edit I/O constraints before compiling your design.

- It's efficient. You can re-use the same PDC file for two different modules.

- One module can use several different PDC files.

- You can add, modify, or delete a port from within the SmartDesign Canvas or Grid, and it is automatically updated in the I/O Attribute Editor. The PDC file is automatically passed from SmartDesign to Designer.

**Basic Concepts**

In Project Manager, you can edit constraints even before you have written any HDL code. You can edit I/O constraints using any text editor, as you did in previous versions, or you can use the graphical I/O Attribute Editor. You can create a new constraint file from the I/O Attribute Editor in Project Manager if you have a project open.

In Multiview Navigator, you can edit constraints only from a compiled netlist.

You cannot use all design constraints with all families; they are family and die specific.

#### **Supported families**

IGLOO, ProASIC3, SmartFusion, Fusion, Axcelerator, and RTAX-S

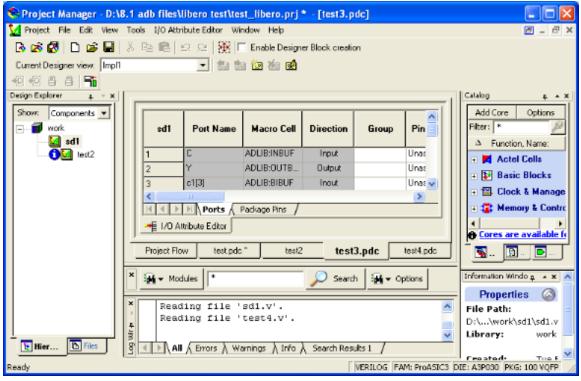

### I/O Attribute Editor in Libero IDE Project Manager

The I/O Attribute Editor from MultiView Navigator is now integrated in the Libero IDE Project Manager and in SmartDesign. SmartDesign automatically passes I/O constraints to Designer.

You can define physical I/O constraints using I/O Attribute Editor from within the Project Manager.

Figure 1 · I/O Attribute Editor in Project Manager

You can start I/O Attribute Editor either from SmartDesign or by opening a PDC file from the Design Explorer.

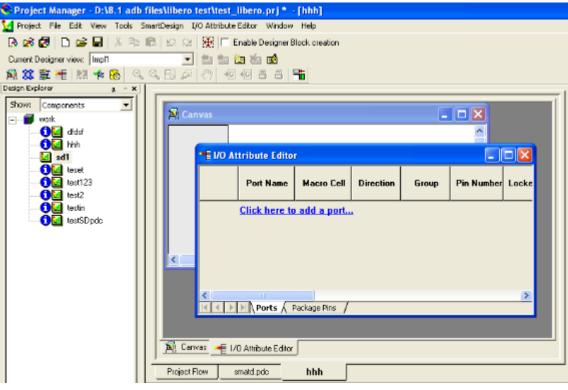

To start the I/O Attribute Editor from SmartDesign, from the **SmartDesign** menu, choose **Show I/O Attribute Editor View**. The I/O Attribute Editor opens in front of the SmartDesign Canvas as shown below.

#### I/O Attribute Editor in Libero IDE Project Manager

I/O Attribute Editor in SMartDesign

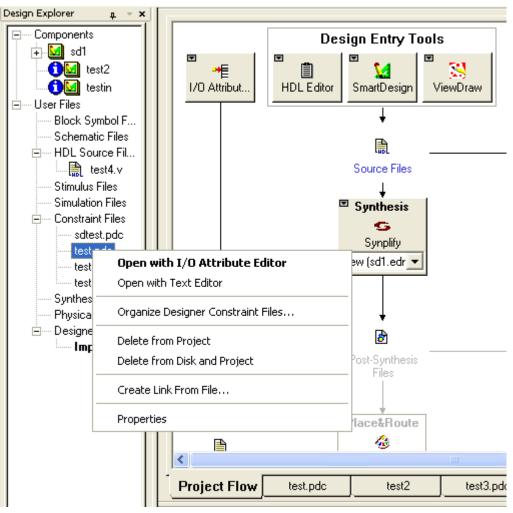

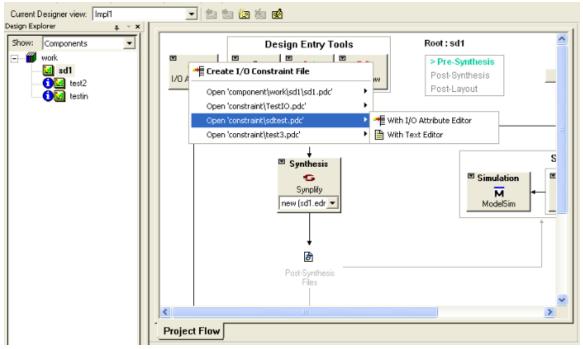

To open a PDC file from Design Explorer, right-click the file you want to open in the **Files** tab, and choose **Open with I/O Attribute Editor** as shown below.

#### **Basic Concepts**

Edit a PDC file in the I/O Attribute Editor

You can either load an existing PDC into the I/O Attribute Editor, or you can create a new PDC file using the I/O Attribute Editor. When you load an existing PDC file, only the I/O-related constraints are shown in the I/O Attribute Editor. The other constraints are preserved and inserted at the end of the new, saved file.

# I/O Attribute Editor Project Flow

I/O Attribute Editor enables you to view, create, and modify your physical design constraint (PDC) files. The **Files** tab lists your constraint files in alphabetical order.

You can create I/O physical design constraints using I/O Attribute Editor with the following steps:

Step One - Create a new PDC file.

Step Two - Add ports to your design.

Step Three - Modify the I/O attributes.

Step Four - Save the PDC file.

You can save your constraint file at any time.

# Creating a New PDC File

You can create a new constraint file from the I/O Attribute Editor in Project Manager if you have a project open and a module set as root.

#### To create a new PDC file with the I/O Attribute Editor:

From the File menu, choose New, or click the I/O Attribute Editor icon in the Project Flow window. The New dialog box appears.

| New                                                                                                                                                                                                                                            |                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Select a Type:<br>Schematic SmartDesign Component CoreConsole Component VHDL Source File Verilog Source File Verilog Source File Stimulus HDL File SDC File (sdc) Physical Design Constraint File (pdc) DO File VHDL Template Verilog Template | Physical Design Constraint File (pdc) |

| Help                                                                                                                                                                                                                                           | OK Cancel                             |

- 1. Select **Physical Design Constraint File (pdc)** for the file type

- 2. Type a name for the PDC file.

- 3. In the **Create with** drop-down list, choose **I/O Attribute Editor**.

- In the Initialize I/O Attribute Editor with drop-down list, choose Ports from current root (sd1), or choose No

Ports if you do not want to load the ports from the current root.

- 5. Click OK. The I/O Attribute Editor opens, displaying the attributes of the PDC file you just created.

- 6. From the File menu, choose Save <filename>.pdc. The saved file is added to your Libero IDE project.

- Note: Note: You can also use the right-click menu to create a new PDC file. Select and right-click the root module. Then choose Constraints > New I/O Constraint File from the right-click menu.

Suppose you just want to enter a constraint for a clock and reset the ports. In this case, you do not have to load all the ports before creating the new PDC file.

#### To create a new PDC file with the I/O Attribute Editor without loading all ports:

- 1. From the **File** menu, choose **New**, or click the I/O Attribute Editor icon in the Project Flow window. The New dialog box appears.

- 2. Select Physical Design Constraint File (pdc) for the file type.

- 3. Type a name for the PDC file.

- 4. In the Create with drop-down list, choose I/O Attribute Editor.

- 5. In the Initialize I/O Attribute Editor with drop-down list, choose No Ports if you do not want to load the ports.

- 6. Click OK. The I/O Attribute Editor opens, displaying the attributes of the PDC file you just created.

- 7. Save the PDC file.

- 8. Open the new PDC file in a text editor to confirm that only two constraints were exported for clock and reset.

- 9. Right-click the root module, and choose **Constraints>Organize Designer Constraint Files** to add the PDC file to Designer as shown below.

| Design Explorer      | a - x                                |         |                                        |                  |          |            |         |            |

|----------------------|--------------------------------------|---------|----------------------------------------|------------------|----------|------------|---------|------------|

| E Components         |                                      | ame     | Macro Cell                             | Direction        | Group    | Pin Number | Locked  | Bank Nam   |

|                      | Open Component                       |         |                                        |                  |          |            |         |            |

| E User Files         | Open HDL file                        | ere to  | add a port                             |                  |          |            |         |            |

| Block                | Check HDL file                       |         |                                        |                  |          |            |         |            |

| Scher                | Create Symbol                        |         |                                        |                  |          |            |         |            |

| ⊡HDL 9               | Constraints +                        | Ne      | w I/O Constraint                       | File             |          | ]          |         |            |

| Stimul<br>Simula     | Organize source files for simulation | Or      | ganize Designer (                      | Constraint File: | 5        |            |         |            |

| 🗐 Const              | Organize source files for synthesis  | Op      | en 'component'w                        | vorki,sd1\sd1.p  | dc' 🕨    |            |         |            |

| te St                | Synplify Synthesis                   | Op      | en 'constraint\Te                      | stIO.pdc         | •        |            |         |            |

| te te                | Create Stimulus                      |         | en 'constraint\so<br>en 'constraint\te | -                | •        |            |         |            |

| Synth                | Run Pre-Synthesis Simulation         | -       |                                        |                  |          |            |         |            |

| ⊡ Physic<br>⊡ Design | Run Post-Synthesis Simulation        |         |                                        |                  |          |            |         |            |

| i In                 | Run Post-Layout Simulation           | _       |                                        |                  |          |            |         | >          |

|                      | Delets from Project                  |         | Package Pins /                         |                  |          |            |         |            |

|                      | Delete from Disk and Project         | or      |                                        |                  |          |            |         |            |

|                      | Properties                           | nstrain | t test3.pdc                            | TestlO.          | pdc test | 4.pdc sdt  | est.pdc | Test11.pdc |

10. In the Organize Constraints for Designer dialog box, select the files to pass to Designer, and click Add.

11. Reopen the PDC file with the I/O Attribute Editor.

When you load ports from a module, the PDC file is automatically associated with that module. However, if no ports are loaded, you need to associate the PDC file using the **Organize Designer Constraint Files** command.

# **Opening an Existing PDC File**

You can open an existing PDC file after you have opened a project and selected a module that contains the PDC file.

### To open an existing PDC file do one of the following:

- In the Design Explorer, from the **Files** tab, expand the Constraint Files list, and double-click the PDC file you want to open. The main window displays the I/O Attribute Editor with the contents of the PDC fle.

- In the Design Explorer, click the **Hierarchy** tab, right-click the PDC file you want to open, and choose **Constraints>Open <pdc filename>**.

- Right-click the I/O Attribute Editor icon in the main window, choose the PDC file to open, and then choose whether to open it with the I/O Attribute Editor or with a text editor, as shown in the figure below.

Figure 2 · Right-click the I/O Attribute Editor Icon to Display Its Right-click Menu The I/O Attribute Editor opens with the I/O attributes of the selected file. When you open an existing PDC file, only the I/O-related constraints are displayed in the I/O Attribute Editor.

### Importing I/O Assignments

You can import I/O attributes from an existing PDC file into the I/O Attribute Editor. Constraints in the PDC file that are not I/O constraints are not read nor are they saved when you save the PDC file.

### To import a PDC file into the I/O Attribute Editor of your design:

- 1. From the I/O Attribute Editor menu, choose Import I/O Assignments. The Open dialog box appears.

- 2. In the **Open** dialog box, find and select the PDC file to import, and click **Open**.

### **Use Designer PDC Constraints**

You can enter pin constraints from Libero Project Manager by either using the text editor to add them to a PDC file or by using the I/O Attribute Editor.

Once you have imported I/O constraint files into Designer, you can modify the constraints with the MultiView Navigator. After modifying the constraints, you can import them back into Project Manager to use the most updated PDC file when performing an iterative design process.

When you use the Use Designer PDC feature, Libero Project Manager will do the following:

- 1. Open the ADB file.

- 2. Export all physical constraints.

- 3. In Libero IDE, from the **File** menu, choose **Import Files**, and select the PDC file to import into the Libero project.

- 4. Update the list of constraint files to be imported to Designer. The next time you start Designer, it will include this new PDC file instead of the other PDC files in the Libero project.

- Note: Note: After selecting the Use Designer PDC feature, you can make more modifications to the newly added PDC file in Libero Project Manager.

### To use the Use Designer PDC feature:

- Right-click an ADB file, and choose Use Designer PDC from the right-click menu.

- Right-click a Designer tool, and choose Use Designer PDC from the right-click menu.

- From the **Organize Constraint Files for Designer** dialog box, click **Use Designer PDC**. (The Use Designer PDC button does not appear until Layout is complete in Designer.)

An Information box appears asking you to confirm that you want to export the Designer PDC file.

| Informa | tion                                                       |                  |                    | $\mathbf{X}$             |

|---------|------------------------------------------------------------|------------------|--------------------|--------------------------|

| (į)     | This will export a Physical De<br>Do you want to continue? | esign Constraint | File file and pass | it directly to this ADB. |

|         | Yes                                                        | No               | Help               |                          |

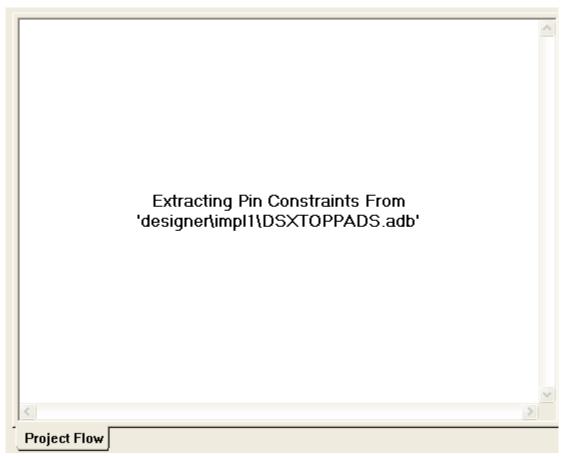

After you click **Yes**, a dialog box appears in which you enter a file name for this Designer PDC file. The default file name appears in the dialog. Click **Save** to replace the old PDC file with the newly modified one, or enter a new, unique name for the PDC which will be used for further design iterations. While converting the PDC file, a message appears, as shown below.

Figure 3 · Information Message Appears During PDC Conversion

After selecting the Use Designer PDC feature, the **Organize Constraints for Designer** dialog box will organize the PDC file as the constraint file to be used by Designer the next time you start it up.

### **Basic Concepts**

| Organize Constraints for Designer                                                                                                                                                       |                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Click to select a constraint file in the project, a<br>'designer\impl1\DSXTOPPADS.adb'.<br>Use the Remove button to remove constraint I<br>Use the Up/Down arrow buttons to specify the | files from Designer.                                                                 |

| Constraint files in the project: Origin<br>DSXTOPPADS.pdc User<br>DSXTOPPADS.sdc User                                                                                                   | Constraint files for Designer:<br>DSXTOPPADS_sdc.sdc<br>exported_from_DSXTOPPADS.pdc |

|                                                                                                                                                                                         | <u>A</u> dd →<br>← <u>R</u> emove                                                    |

| Designer only supports sdc and pdc as source<br>Show this dialog before creating a new AD<br>Help                                                                                       | Use Designer PDU                                                                     |

Figure 4 · Organize Constraints for Designer with Use Designer PDC Button

## Adding, Modifying, and Deleting Ports

You can add ports to, delete ports from, and modify ports in the I/O Attribute Editor.

### To add ports:

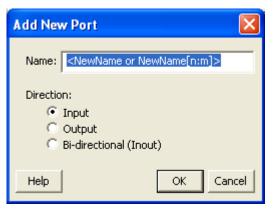

1. From the **I/O Attribute Editor** menu, choose **Add port**. The **Add New Port** dialog box appears (as shown below).

Figure 5 · Add New Port Dialog Box

2. Specify the name of the port you wish to add. You can specify a bus port by including the bus width as part of the name using brackets [], such as mybus[3:0].

3. Select the direction of the port.

You can also add a port using the right-click menu.

|   | Add Port      | Macro Cell | Function | Loc |

|---|---------------|------------|----------|-----|

| 1 | Manage Groups | <u>]</u>   | IO82RSB1 | ·   |

| 2 | Hide          |            | IO81RSB1 |     |

| 3 | Unhide        |            | IO80RSB1 |     |

|   | Freeze Pane   | is /       |          |     |

| Ŕ | Unfreeze Pane |            |          |     |

Figure 6 · I/O Attribute Editor Right-click Menu

### To modify a port in the I/O Attribute Editor:

1. Select the port in the Grid, right-click and choose **Modify Port**. The Modify Port dialog box appears, as shown in the figure below.

| Modify port1 |           |

|--------------|-----------|

| Name: port1  |           |

| Direction:   | Inout)    |

| Help         | OK Cancel |

Modify Port Dialog Box

2. Enter the new name for the port, change its direction, and click **OK**.

To remove a port from the I/O Attribute Editor, select the port in the Grid, right-click and choose Delete Port.

Note: If you opened a PDC file associated with a module and the ports are loaded from the module, you cannot add, modify, nor delete the ports because they are brought over from the module.

## Saving/Closing a PDC File

To save the current PDC file, from the **File** menu, choose **Save** <*PDC filename*>.pdc. The saved file is added to your Libero IDE project. The new constraints will override any existing constraints in this file. Any comments you added

are not saved with this file. Therefore, you may want to save your changes into another file using the Save As menu command.

To save the current PDC file with a different name, choose **Save** <*PDC filename*>.pdc As. The **Save** As dialog box appears. Enter a new name for the PDC file.

To close the current PDC file without saving, from the File menu, choose Close. Click No when prompted to save.

You can also close a PDC file by right-clicking the name of the tab in the I/O Attribute Editor and choosing **Close**, as shown in the figure below.

|   |                       | je Pins /                | > |

|---|-----------------------|--------------------------|---|

| ļ | Project Flow test.pdc | Restore                  |   |

| × | Modules *             | Close Search 🙀 🗸 Options |   |

Figure 7 · Close a PDC File

## Deleting a PDC File from a Libero IDE Project

### To delete a PDC file from a project:

- 1. In the Design Explorer, click the Files tab.