# **Creating Analog Testbenches**

for Fusion Designs

#### Actel Corporation, Mountain View, CA 94043

© 2007 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200092-0

Release: March 2007

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logo are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

| Introduction                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Setting Up the Example Files                                                                                                                                     |

| Configuring the Voltage/Temperature Monitor                                                                                                                      |

| Creating the Analog Testbench                                                                                                                                    |

| Simulating the Fusion Design                                                                                                                                     |

| Product Support21Customer Service21Actel Customer Technical Support Center21Actel Technical Support21Website21Contacting the Customer Technical Support Center21 |

|                                                                                                                                                                  |

## Introduction

This tutorial demonstrates how to create analog testbenches for Fusion FPGAs using Libero® IDE and WaveFormer Lite.™

To create an analog testbench, follow the steps below:

- 1. Chapter 1 Setting Up the Example Files

- 2. Chapter 2 Configuring the Voltage/Temperature Monitor

- 3. Chapter 3 Creating the Analog Testbench

- 4. Chapter 4 Simulating the Fusion Design

This tutorial assumes basic knowledge and experience with the Libero IDE design flow and WaveFormer Lite testbench generation tool. For more information about Libero, refer to the *Libero User's Guide*, available at the Actel web site (www.actel.com).

## **Setting Up the Example Files**

In this step, you will set up the project files for the Fusion design used in this tutorial.

- 1. Download the Creating an Analog Testbench tutorial supplemental files from the Actel website.

- 2. Create a new folder on your C drive named VT\_Mon (C:\Actelprj\VT\_Mon).

- 3. Unzip the supplemental files to the C:\Actelprj\VT\_Mon folder.

- 4. From the Start menu, choose Actel Libero IDE or double-click the Actel Libero IDE icon on the desktop.

- 5. From the File menu, choose Open Project.

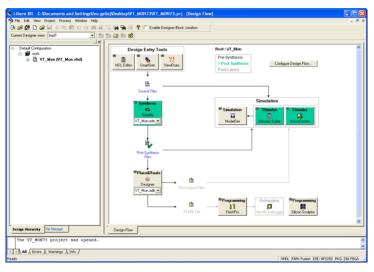

- 6. Browse to C:\Actelprj\VT\_Mon and click OK. This opens the VT\_Mon project in Libero IDE (see Figure 1-1).

Figure 1-1 · Libero IDE Design Flow Window with VT\_Mon Project

Note: If the Tool Profile Conflict dialog box appears, select Use the profile currently selected in Libero IDE and click OK.

# **Configuring the Voltage/Temperature Monitor**

This step uses SmartGen to configure the voltage and temperature monitor Fusion peripherals and implements them in the design HDL code. The intended function for this design is to monitor a supply voltage and a temperature, and send flags to the Fusion system when the voltage rises above 5.25 V or falls below 4.75 V, and when the monitored temperature exceeds 70° C.

In this step, you will configure a voltage monitor, a temperature monitor, and two gate drivers. The gate driver functions are responsible for sending flags to the Fusion system, which could then either control the input environment or sound alarms, or both.

1. Launch SmartGen by clicking the SmartGen button from the Libero IDE interface. This opens the SmartGen tool (Figure 2-1).

| ) 📽 🎥 🗊 🔋                                                     | Core Varieties for Fusion Family                   |                  |          |                           |                                     |  |

|---------------------------------------------------------------|----------------------------------------------------|------------------|----------|---------------------------|-------------------------------------|--|

| <ul> <li>Analog System Builder</li> </ul>                     | Variety                                            | Function         | Vendor   | Manine                    | Datali                              |  |

| <ul> <li>Analog System builder</li> <li>Arithmetic</li> </ul> | Analog System Builder                              | Analog System    |          | 1.2                       | Analog System Builder               |  |

| * Godi Conditioning / PU.                                     | Ricele                                             | Adder            | Actel    | 2.0                       | Area optimized, Low Speed           |  |

| <ul> <li>         · · · · · · · · · · · · · · ·</li></ul>     | Fact Brent Kung                                    | Adder            | Actel    | 20                        | Speed opinized.                     |  |

| * II Counters                                                 | Event Kung                                         | A-55m            | Actel    | 20                        | Area optimized, Medium Speed        |  |

| <ul> <li>Corrers</li> <li>Decoder</li> </ul>                  | Sklansky                                           | 6.65m            | Actel    | 20                        | Sceed optimized > 32. Fastest av    |  |

| * Cecoler                                                     | With Final Adder                                   | Anay Adder       | Actel    | 2.0                       | Array adder with final adder        |  |

| K 9 Flash Memory System Builder                               | With Final Adder Pipelined                         | Annay Adder      | Actel    | 2.0                       | Array Adder with pipelined final ad |  |

| R FishRom                                                     | Without Final Addee                                | Anay Adder       | Actel    | 20                        | Array adder with no final adder     |  |

| x % 10                                                        | Binnie                                             | Subtactor        | Actel 20 | Area optimized, Low Speed |                                     |  |

| * D Look                                                      | Fast Bient Kung                                    | Subjective       | Actel    | 2.0                       | Speed optimized                     |  |

| x / Maicres                                                   | Event Kung                                         | Subtractor       | Actel    | 2.0                       | Area optimized, Medium Speed        |  |

| N D Multiplexor                                               | Sklansky                                           | Subtractor       | Actel    | 20                        | Speed optimized > 32 Fastest av     |  |

| K S RAM                                                       | Riccle                                             | Adder / Subha    | Actel    | Actel 20                  | Area optimized, Low Speed           |  |

| * Register                                                    | Fast Bient Kung                                    | Adder / Subha    | Actel 21 | 2.0                       | Speed optimized                     |  |

| * TVoltage Regulator Power Supply Monitor                     | E Dent-Kung                                        | Adder / Subtra   | Actel    | 2.0                       | Area optimized Medium Speed         |  |

| Ha Categories A Robatetic Mar P Catalog                       | Sklansky                                           | Adder / Subha    | Actel    | 20                        | Speed optimized > 32. Fastest av    |  |

| California Antonia Mate California                            |                                                    | * **             |          |                           |                                     |  |

| Name Category Function                                        | Variety                                            | Vendor Version   | General  | . 40-                     |                                     |  |

| Name Category Function                                        | valety                                             | Aleudox Alection | General  | egun                      |                                     |  |

| rkspace C:\&ctelpri\sample\VTBon\s                            | martgen\smartgen.aws op<br>% a core wariety in the |                  | iev.     |                           |                                     |  |

Figure 2-1 · SmartGen Window

- 2. Under the Categories tab, click the Analog System Builder category.

- 3. In the Variety window, double-click Analog System Builder. The Analog System Builder (ASB) core configurator (Figure 2-2) allows you to select the required analog functions, the analog inputs that need to be configured, and the specific threshold values required to send event flags to the system logic.

|                                                                                                                                                |                             |         |         |                          |                         | _                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|---------|--------------------------|-------------------------|----------------------|

| Analog System Builder: Cre                                                                                                                     | ate core                    |         |         |                          |                         |                      |

| ADC Configuration                                                                                                                              | MHz ADC Clock:              | Resolut | ion: 10 | r bits                   | 2                       | idvanced Options     |

| Available peripherals:                                                                                                                         | Peripherals used in system: |         |         |                          |                         | $\mathcal{I} \times$ |

| Vokage Monitor<br>Current Monitor<br>Temperature Monitor                                                                                       | Peripheral                  | Signal  | Туре    | Acquisition<br>time (us) | Sampling Bate<br>(ksps) | Package Pin          |

| Colferential Volkoge Menitor<br>Clinet Digital Tiput<br>Gale Driver<br>Real Time Counter<br>Informal Yonge Menitor<br>Informal Volkoge Menitor |                             |         |         |                          |                         |                      |

|                                                                                                                                                | Modify Sampling Sequence    |         |         |                          |                         | Generate             |

| Help                                                                                                                                           |                             |         |         |                          |                         | Close                |

Figure 2-2 · Analog System Builder Configurator for Fusion

#### Configuring the Voltage/Temperature Monitor

- 4. In the ADC Configuration panel, enter 40.0 as the System Clock frequency and 10.0 as the Resolution.

- 5. From the Available peripherals list, select Voltage Monitor and click Add to System. This opens the Configure Voltage Monitor Peripheral window.

This input signal configuration will signal the system when the voltage on the AV5V input pin is 5.25 V or higher for one sample, or 4.75 V or lower for the other sample. The ASB will deassert (remove) the system flag after two consecutive samples when the signal falls under 5.25 V or rises above 4.75 V.

- 6. Enter the following information (as shown in Figure 2-3) :

- Signal name: AV5V

- Acquisition time: 1.0

- Maximum voltage: 5.5

- Enter the following information for Flag 1:

- Flag Name: over5p25

- · Flag Type: over

- Threshold (V): 5.25

- Assert Samples: 1

- Deassert Samples: 2

- Enter the following information for Flag 2:

- Flag Name: under4p75

- Flag Type: under

- Threshold (V): 4.75

- Assert Samples: 1

- Deassert Samples: 2

| Configure Vo     | ltage Mor                        | nitor Periph | eral                |                |                                |                   |                           |           |

|------------------|----------------------------------|--------------|---------------------|----------------|--------------------------------|-------------------|---------------------------|-----------|

|                  | AV pad                           | Signal name: |                     | Pr             | escaler                        | •)-               |                           |           |

|                  | iltering<br>ng factor:<br>value: | None         | ▼<br>∀<br>Compariso | n Flag Specifi | Acquisition ti<br>Maximum volt |                   | 1.000<br>5.5<br><b>()</b> | us 🕄<br>V |

|                  | Flag                             | g Name       | Flag                | Туре           | Threshold<br>(V)               | Assert<br>Samples | De-assert<br>Samples      |           |

| 1<br>2<br>3<br>4 | OVER5P2<br>UNDER4F               |              | OVER<br>UNDER       |                | 5.25                           | 1                 |                           | 2 2       |

| Help             |                                  |              |                     |                | [                              | ОК                | Car                       | ncel      |

#### Figure 2-3 · Configure Voltage Monitor Peripheral Window

- 7. Click OK. This adds the voltage monitor peripheral to the list of peripherals used in the system.

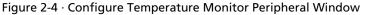

- 8. From the Available peripherals list, select Temperature Monitor and click Add to System. This opens the Configure Temperature Monitor Peripheral window.

This signal will send a flag to the system when one sampling of the input is  $70^{\circ}$  C or higher. Fusion will remove the system flag when the temperature is lower than  $70^{\circ}$  C for two samples.

- 9. Enter the following information (as shown in Figure 2-4) :

- Signal name: Temp

- Acquisition time: 10.0

Enter the following information for Flag 1:

- Flag Name: over70C

- Flag Type: over

- Threshold (C): 70

- Assert Samples: 1

- Deassert Samples: 2

| õignal nai | nperature Monitor | Peripheral      | Acquisition time:  | 10.0              |                      |

|------------|-------------------|-----------------|--------------------|-------------------|----------------------|

| -Digital f |                   |                 |                    | 1.010             | us                   |

|            | value: 0.000      | c               |                    |                   |                      |

|            |                   | Comparison Flag | Specification      |                   | <u>*</u> ×           |

|            | Flag Name         | Flag Type       | , Threshold<br>(C) | Assert<br>Samples | De-assert<br>Samples |

| 1          | over70C           | OVER            | 70                 | 1                 | 2                    |

| 2          |                   |                 |                    |                   |                      |

|            |                   |                 |                    |                   |                      |

| 4          |                   |                 |                    |                   |                      |

| 4<br>5     |                   |                 |                    |                   |                      |

| 5          |                   |                 |                    |                   | ×                    |

| 5          |                   |                 |                    |                   |                      |

- 10. Click OK. This adds the temperature monitor peripheral to the list of peripherals used in the system.

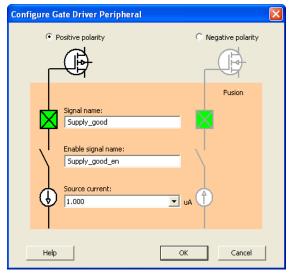

- 11. From the Available peripherals list, select Gate Driver and click Add to System. This opens the Configure Gate Driver Peripheral window.

You will configure the gate driver function for the voltage monitor. The gate driver enable in this case is designed to be the logical NOR of the over and under threshold flags.

- 12. Enter the following information (as shown in Figure 2-5 on page 12):

- Signal name: Supply\_good

- Enable signal name: Supply\_good\_en

- Source current: 1.000

Configuring the Voltage/Temperature Monitor

Figure 2-5 · Configure Gate Driver Peripheral Window

- 13. Click OK. This adds the gate driver peripheral to the list of peripherals used in the system.

- 14. From the Available peripherals list, select Gate Driver and click Add to System. This opens the Configure Gate Driver Peripheral window.

You will configure the gate driver function for the temperature system output flag when the temperature exceeds  $70^{\circ}$  C. In this design, the Over\_temp flag is used as the gate driver enable.

- 15. Enter the following information (as shown in Figure 2-6 on page 13):

- Signal name: Over\_temp

- Enable signal name: Over\_temp\_en

- Source current: 1.000

| Configure Gate Driver Peripheral                               |          |

|----------------------------------------------------------------|----------|

| Positive pularity     Negative pular                           | rilγ     |

| Fusion Signal name: Over_temp Enable signal name: Over_temp_en |          |

| Source current:                                                |          |

| Help OK Cance                                                  | <u>i</u> |

Figure 2-6 · Configure Gate Driver Peripheral Window

- 16. Click OK. This adds the gate driver peripheral to the list of peripherals used in the system.

- 17. Click Generate. This brings up the Generate Core dialog box (Figure 2-7).

| Generate Core    |           |

|------------------|-----------|

| Configured cores | a         |

|                  |           |

|                  |           |

|                  |           |

|                  |           |

|                  |           |

| 1                |           |

| Core name:       | newCore   |

|                  |           |

| Output format:   | VHDL      |

|                  |           |

|                  |           |

|                  |           |

|                  |           |

| Help             | OK Canrel |

Figure 2-7 · Generate Core Dialog Box

- 18. Enter *VT\_Mon* as the Core name and click OK.

- 19. Click Close to close the Analog System Builder window.

- 20. From the File menu, choose Exit to close SmartGen.

To complete this design you will need to configure and make proper connections to the Flash Memory System Builder. Doing so is beyond the scope of this tutorial.

## **Creating the Analog Testbench**

The next step in a Fusion design flow is to synthesize your design and create a testbench.

SynaptiCAD's WaveFormer Lite v11.11d provides the capability to create and generate a testbench with analog and digital signals. The input signals for the voltage and temperature inputs for the VT\_Mon design can easily be drawn using the WaveFormer Lite user interface.

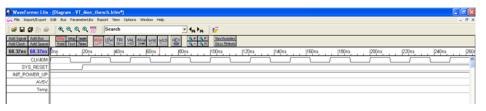

1. Click the **Stimulus WaveFormer** button in the Libero IDE design flow window to launch WaveFormer Lite. This opens the WaveFormer Lite user interface.

Libero IDE finds the clock and respective input/output signals of the VT\_Mon design. Clock and signal names are already identified in the waveform window. The SYS\_CLK, SYS\_RESET, and INIT\_POWER\_UP input signal names have already been entered in the GUI (Figure 3-1).

Figure 3-1 · Initial WaveFormer Lite Timing Diagram

The VT\_Mon testbench in WaveFormer Lite has already been configured with a 40 MHz clock, the Initial\_Power\_Up signal goes active high at 10 ns, and the System Reset signal goes active high at 40 ns. The analog inputs AV5V and Temp can now be configured in the WaveFormer window.

- 2. From the Options menu, choose Display Unit > 1µs.

- 3. Double-click the AV5V signal name to open the Signal Properties dialog box.

- 4. In the Signal Properties dialog box, set the following information:

- Direction: output (default)

- Size Ratio: Enter 3 to increase the vertical height of the waveform display row.

- Signal Type: actel\_voltage

- Radix: real

- Label Eqn (Equation): Use the arrow 🔟 to open a pop-up list of waveform types. For this testbench, select Ramp (StartV,EndV,Duration). This option enables you to easily insert a ramp of beginning and ending voltages over a specified duration. A ramp waveform equation is perfect for creating a long, slow voltage variation that might be experienced by a voltage monitor input signal in this particular design.

Note: When starting a new waveform, be sure the window is clear of any other equations.

#### Creating the Analog Testbench

| Signal Properties 5 W O R D ?                    | , (Concatenate)<br>Inc(start,increment,count)                                 |

|--------------------------------------------------|-------------------------------------------------------------------------------|

| orginal reportion                                | Dec(start, decrement, count)                                                  |

| Name: AV5V Control Active Low                    | IncString("string",start,increment,count)                                     |

|                                                  | Range(start,finish,count)                                                     |

| Simulate Once Analog Props Grid Lines            | RandInt(count, Range_to_zero)                                                 |

| O Drive     C Simulate     O Watch     O Compare | Hex(list)<br>Bin(list)                                                        |

| Equation Entry Verilog VHDL                      | Rep((list), count)                                                            |

|                                                  | Skip(count)                                                                   |

| Type: Boolean Eqn 💌 ex. (SIG1 and SIG2) delay 5  | File("filename.txt")                                                          |

|                                                  | Signal("signalname")                                                          |

|                                                  | map {operations} list                                                         |

| Clock: Unclocked 💌 Edge/Level: pos 💌             | PRBS7(length,seed)                                                            |

| Set: Not Used 🔻 Clear: Not Used 👻                | PRBS15(length,seed)                                                           |

|                                                  | Sin(amplitudeV, period, duration)                                             |

| Clock Enable: Not Used 💌 Advanced Register       | SinStart(amplitudeV, period, duration)                                        |

|                                                  | SinEnd(amplitudeV, period, duration)                                          |

|                                                  | CapCharge(amplitudeV, RC, duration)<br>CapDischarge(amplitudeV, RC, duration) |

| Wfm Eqn 8ns=Z (5=1 5=0)*5 9=H 9=L 5=V 5=X 💌      | Ramp(StartV,EndV,Duration)                                                    |

| Label Eqn Ramp(0,0,500)                          | Kanp(Starty)Endy(Baration)                                                    |

|                                                  |                                                                               |

| Export Signal Direction: output                  |                                                                               |

| Analog Display Size Ratio: 3                     |                                                                               |

| Signal Type: actel_voltage                       |                                                                               |

| Radix: real V Bus MSB: LSB:                      |                                                                               |

| Radix: real 💽 Bus MSB: LSB:                      |                                                                               |

| 🔲 Falling Edge Sensitive 📃 Rising Edge Sensitive |                                                                               |

| OK Cancel Apply Prev Next                        |                                                                               |

For the initial AV5V signal, edit the ramp equation to Ramp(0,0,500) and click Label Eqn (Figure 3-2). The AV5V data shows a steady state zero voltage for 500  $\mu$ s.

Figure 3-2 · WaveFormer Lite Signal Properties Dialog Box

You can add a subsequent value to the ramp equation that specifies the number of increments to be used in the duration. In the AV5V testbench example, to complete the waveform, each ramp and duration is required to be implemented in five or eight increments (see Step 5 below). More increments would have the effect of providing a smoother waveform.

- 5. With the **Signal Properties** dialog box still open, insert the following series of ramp equations, and click the **Label Eqn** button:

- Ramp(0,0,500) Zero voltage for 500 μs

- Ramp(1,5,200,8) Ramps from 1.0 V to 5.0 V in 200 µs, in 25 µs increments

- Ramp(5,5,100,5) Voltage stays steady at 5.0 V for 100 μs

- Ramp(5,5.5,200,8) Ramps from 5.0 V to 5.5 V in 200 µs, in 25 µs increments

- Ramp(5.5,5.5,100,5) Voltage stays steady at 5.5 V for 100 μs

- Ramp(5.5,5,200,8) Ramps from 5.5 V to 5.0 V in 200 µs, in 25 µs increments

- Ramp(5,5,100,5) Voltage stays steady at 5.0 V for 100 μs

- Ramp(5,4.6,200,8) Ramps from 5.0 V to 4.6 V in 200 µs, in 25 µs increments

- Ramp(4.6,4.6,100,5) Voltage stays steady at 4.6 V for 100  $\mu s$

- Ramp(4.6,5,200,8) Ramps from 4.6 V to 5.0 V in 200 µs, in 25 µs increments

- + Ramp(5,5,200,5) Voltage stays steady at 5 V for 200  $\mu s$

- Note: Clear the Label Eqn field prior to entering each equation to avoid duplicating the same equation for the next segment of the waveform.

The total signal duration is  $2100 \ \mu s$ .

WaveFormer easily concatenates the new data waveform to the preceding waveform so that a continuous waveform is created.

- 6. Click OK.

- 7. Right-click the Temp signal name to open the Signal Properties dialog box for the Temp signal.

- 8. In the Signal Properties dialog box, set the following information:

- Direction: output (default)

- Size Ratio: Enter 3 to increase the vertical height of the waveform display row.

- Signal Type: actel\_temperature

- Radix: real

- Label Eqn (Equation): Use the arrow 🔟 to open a pop-up list of waveform types, and select Ramp (StartV,EndV,Duration). In the case of temperature, use values in degrees Celsius, starting with 70° C.

- 9. Enter the following series of ramp equations, incorporating each by clicking the Label Eqn button:

- Ramp(50,50,500) Temperature stays steady at 50° C for 500 µs

- Ramp(50,70,400,16) Temperature increases from 50°C to 70°C in 400 µs in 25 µs increments

- Ramp(70,72,200,8) Temperature increases from 70° C to 72° C in 200 µs in 25 µs increments

- Ramp(72,72,200,10) Temperature stays steady at 72°C for 200 μs

- Ramp(72,70,200,8) Temperature drops from 72°C to 70°C in 200 µs in 25 µs increments

- Ramp(70,68,200,8) Temperature drops from 70°C to 68°C in 200 µs in 25 µs increments

- Ramp(68,72,200,8) Temperature ramps from 68°C to 72°C in 200 µs in 25 µs increments

- Ramp(72,71,200,8) Temperature drops from 72° C to 71° C in 200 µs in 25 µs increments The total signal duration is 2100 µs

The total signal duration is 2100  $\mu$ s.

10. Click **OK**. The resulting data for the AV5V and Temp signals is shown in the WaveFormer window as individual pulses or increments with the analog values for each increment (Figure 3-3).

Figure 3-3 · Resulting Waveform for AV5V Voltage Monitor Signal

#### Creating the Analog Testbench

| File Import/Export                         | Edit Bus Paran               | neterLibs Proje | t Report View | v Options Wind | fow Help |                    |                                |       |   |        |         | - 8      |

|--------------------------------------------|------------------------------|-----------------|---------------|----------------|----------|--------------------|--------------------------------|-------|---|--------|---------|----------|

| 🛎 🖬 🕼 🖨                                    | ର୍ ର୍ ଉ                      | Q HIDE          |               |                | •        | 4n 1n              | Verilog                        | •     | 6 | iff M# | ∜g ⊩g ≩ | ET<br>LL |

| Add Signal Add Bus<br>Add Clock Add Spacer | Delay Setup 5<br>Hold Text 1 | tanple HIGH     |               | INVal WHI W    |          | 9 + 9 F<br>9 - 9 R | ViewVariables<br>Class Hethods |       |   |        |         |          |

| 656m: 1.656m: Oue                          |                              | 500us           | 1.0ms         | 1.5ms          |          | ms .               | 2.5ms                          | 3.0ms |   | 3.5ms  | ł       | 4.0ms    |

| CLK40M                                     |                              |                 |               |                |          |                    |                                |       |   |        |         |          |

| SYS_RESET                                  |                              |                 |               |                |          |                    |                                | _     |   |        |         |          |

| IT_POWER_UP                                |                              |                 |               |                |          |                    |                                |       |   |        |         |          |

| ATRETURN01                                 |                              |                 |               |                |          |                    |                                | _     |   |        |         |          |

| AV5V                                       |                              |                 |               |                |          |                    |                                |       |   |        |         |          |

| Temp                                       |                              |                 |               |                |          |                    |                                |       |   |        |         |          |

| VAREF                                      |                              |                 |               |                |          |                    |                                |       |   |        |         |          |

| Supply_good                                |                              |                 |               |                |          |                    |                                |       |   |        |         |          |

| Over_temp                                  |                              |                 |               |                |          |                    |                                |       |   |        |         |          |

If you use SynaptiCAD WaveFormer Pro software, check Analog Display in the Signal Properties dialog box to provide a visual representation of the analog signal (Figure 3-4).

Figure 3-4 · Resulting WaveForm Pro Waveform for AV5V Voltage Monitor Signal

- 11. From the File menu, choose Save.

- 12. From the Import/Export menu, choose Export Timing Diagram As. In the Export dialog box, select VHDL w/Top Level Test Bench (.vhd) and click OK.

## **Simulating the Fusion Design**

In this step, you will simulate the design.

- 1. Right-click the **Stimulus Editor** button in the Libero IDE interface and choose **Organize Stimulus**. This opens the Organize Stimulus dialog box.

- 2. Select your testbench file and click Add. This adds your testbench to the Associated Files list (Figure 4-1).

| Organize Stimulus                                                                                                                                                                                       |                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Click to select a stimulus file in the project, and<br>Use the Remove button to remove associated f<br>Use the Up/Down arrow buttons to specify the<br>The top level module should appear last in the I | files.<br>compilation order for the simulator. |

| Stimulus files in the project:<br>VT_Mon_tbench_equ.vhd                                                                                                                                                 | Associated files:                              |

|                                                                                                                                                                                                         | <u>A</u> dd →<br>← <u>R</u> emove              |

| Help                                                                                                                                                                                                    | OK Cancel                                      |

Figure 4-1 · Organize Stimulus Dialog Box

- 3. Click OK.

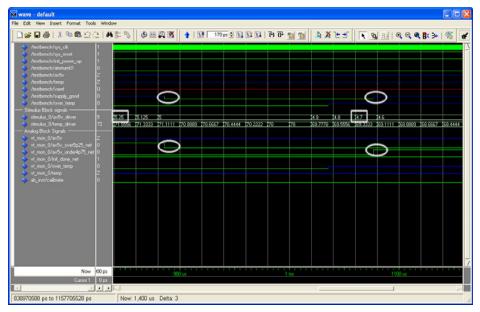

- 4. Click the **Simulation ModelSim** button. This opens the ModelSim user interface. The results of the simulation for the VT\_Mon design are shown in Figure 4-2 and Figure 4-3 on page 20.

#### Figure 4-2 · Effect of the AV5V Input Testbench after Simulation

Figure 4-2 demonstrates the effect of the varying voltage on the AV5V input. The stimulus\_0/av5v\_driver line shows that part of the waveform where the voltage is initially 5.25 V and ramps down below 4.75 V between 800 and 1100  $\mu$ s. As specified by the AV5V maximum voltage threshold flag, and visualized by the /testbench/supply\_good

#### Simulating the Fusion Design

output signal, the Fusion logic asserts the overvoltage flag where the voltage is exceeding 5.25 V and deasserts it as the voltage drops below 5.25 V. The threshold flag remains deasserted until the voltage drops below 4.75 V, where it reasserts, as indicated by the vt\_mon\_0/av5v\_under4.75v logic and /testbench/supply\_good output signal, at approximately 1080  $\mu$ s. Any delay between the input voltage signal and the respective flag threshold value is a function of the specified sampling rate, resolution of the analog to digital converter, and number of samples taken before assert/deassert flag is set. The AV5V testbench works as desired, clearly showing the assert/deassert of the flags based on the requested thresholds.

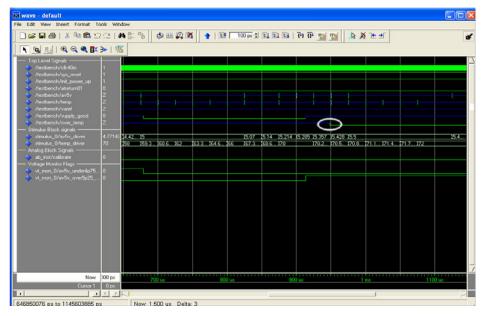

The temperature monitoring threshold flag in the Fusion ASB has been set to assert when the temperature exceeds  $70^{\circ}$  C and will deassert when the temperature is less than or equal to  $70^{\circ}$  C. Figure 4-3 demonstrates the effect of a varying temperature on the Temp input of the design, where the temperature is rising from  $50^{\circ}$  C and passes through  $70^{\circ}$  C. Note that the testbench/over\_temp signal, which has been deasserted, asserts as the temperature passes above  $70^{\circ}$  C, and the /testbench/over\_temp output simultaneously asserts as directed by the threshold detection logic. Any delay in the actual assertion or deassertion as compared to the input temperature is a function of the specified sampling rate and resolution of the analog to digital converter. The Temp testbench shows the over\_temp assertion/assertion as the temperature rises above the specified threshold of  $70^{\circ}$  C.

## **Product Support**

Actel backs its products with various support services including Customer Service, a Customer Technical Support Center, a web site, an FTP site, electronic mail, and worldwide sales offices. This appendix contains information about contacting Actel and using these support services.

### **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From Northeast and North Central U.S.A., call **650.318.4480** From Southeast and Southwest U.S.A., call **650.318.4480** From South Central U.S.A., call **650.318.4434** From Northwest U.S.A., call **650.318.4434** From Canada, call **650.318.4480** From Europe, call **650.318.4252** or +44 (0) **1276 609 300** From Japan, call **650.318.4743** From the rest of the world, call **650.318.4743** Fax, from anywhere in the world **650.318.8044**

### Actel Customer Technical Support Center

Actel staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions. The Customer Technical Support Center spends a great deal of time creating application notes and answers to FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

### **Actel Technical Support**

Visit the Actel Customer Support website (www.actel.com/custsup/search.html) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the Actel web site.

### Website

You can browse a variety of technical and non-technical information on Actel's home page, at www.actel.com.

Product Support

### Contacting the Customer Technical Support Center

Highly skilled engineers staff the Technical Support Center from 7:00 A.M. to 6:00 P.M., Pacific Time, Monday through Friday. Several ways of contacting the Center follow:

#### Email

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is tech@actel.com.

#### Phone

Our Technical Support Center answers all calls. The center retrieves information, such as your name, company name, phone number and your question, and then issues a case number. The Center then forwards the information to a queue where the first available application engineer receives the data and returns your call. The phone hours are from 7:00 A.M. to 6:00 P.M., Pacific Time, Monday through Friday. The Technical Support numbers are:

#### 650.318.4460 800.262.1060

Customers needing assistance outside the US time zones can either contact technical support via email (tech@actel.com) or contact a local sales office. Sales office listings can be found at www.actel.com/contact/offices/index.html.

# For more information about Actel's products, visit our website at http://www.actel.com

Actel Corporation • 2061 Stierlin Court • Mountain View, CA 94043 USA Customer Service: 650.318.1010 • Customer Applications Center: 800.262.1060 Actel Europe Ltd. • River Court, Meadows Business Park • Station Approach, Blackwater • Camberley Surrey GU17 9AB United Kingdom • Phone +44 (0) 1276 609 300 • Fax +44 (0) 1276 607 540

**Actel Japan** • EXOS Ebisu Bldg. 4F • 1-24-14 Ebisu Shibuya-ku • Tokyo 150 • Japan Phone +81.03.3445.7671 Fax +81.03.3445.7668 • http://jp.actel.com

**Actel Hong Kong** • Suite 2114, Two Pacific Place • 88 Queensway, Admiralty Hong Kong Phone +852 2185 6460 Fax +852 2185 6488 • www.actel.com.cn

50200092-0/3.07