# UG0065 User Guide Fusion Starter Kit

Power Matters.™

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

www.microsemi.com

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |  |  |  |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| 2 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |  |  |  |  |  |

| 3 | Installation and Settings  3.1 Software Installation  3.2 Hardware Installation  3.3 Testing the Evaluation Board  3.4 Programming the Test File                                                                                                                                                                                                                                                                                                                                      | . 3                             |  |  |  |  |  |

| 4 | Hardware Components  4.1 Fusion Evaluation Board  4.2 Board Description and Usage  4.3 Power Supplies  4.3.1 Daughter Card Power Supply Connections  4.3.2 Power Supplies and Chaining Boards Together  4.4 Programming the AFS-EVAL-BRD1 with a FlashPro3  4.4.1 Connecting the FlashPro3 Programmer to the Board  4.4.2 Programming or Re-Programming the Example Design  4.4.3 Jumpers for Isolating Switches and LEDs from the FPGA  4.4.4 Analog Circuitry Provided on the Board | . 4                             |  |  |  |  |  |

| 5 | Description of Test Design                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                              |  |  |  |  |  |

| 6 | Demo Design Tutorial  6.1 CoreABC Design Description 6.1.1 Functionality Description 6.1.2 Demonstration Instructions 6.1.3 CoreABC Design Implementation  6.2 SmartDesign Demonstration 6.2.1 Demonstration Instructions 6.2.2 Implementation                                                                                                                                                                                                                                        | 15<br>15<br>15<br>18<br>38<br>4 |  |  |  |  |  |

| 7 | Test Procedures for Board Testing  7.1 Equipment Required 7.1.1 Microsemi Equipment Provided by Microsemi to Testing Facility 7.1.2 Testing Facility Equipment to Be Available for Testing  7.2 Test Procedure for the AFS-EVAL-BRD1 7.2.1 Initial Power-Up Procedure 7.2.2 Testing Board Functionality with AFS600-FG256 Silicon                                                                                                                                                     | 64<br>64<br>64<br>64            |  |  |  |  |  |

| 8 | Appendix: FG256 Package Connections for AFS600 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |  |  |  |  |  |

| 9 | Appendix: Board Schematics  9.1 Top-Level View  9.2 Fusion Schematics                                                                                                                                                                                                                                                                                                                                                                                                                 | 78                              |  |  |  |  |  |

| 10 | Apper | ndix: Signal Layers           | 92  |

|----|-------|-------------------------------|-----|

|    | 10.1  | Errata                        | 92  |

| 11 | Apper | ndix: SmartDesign Connections | 98  |

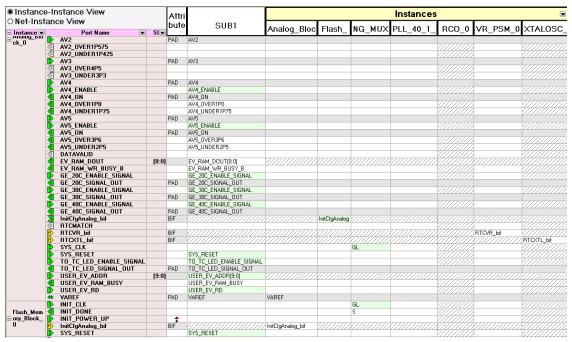

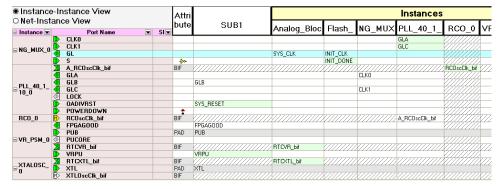

|    | 11.1  | SUB1 Connections              | 98  |

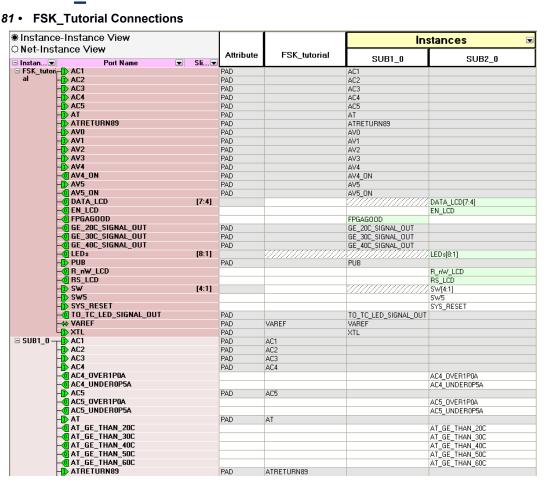

|    | 11 2  | ESK Tutorial Connections      | 100 |

# **Figures**

| Figure 1               | The Fusion Evaluation Board                                     | 2  |

|------------------------|-----------------------------------------------------------------|----|

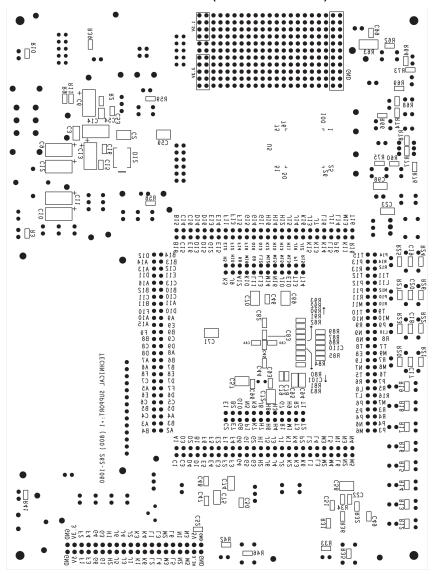

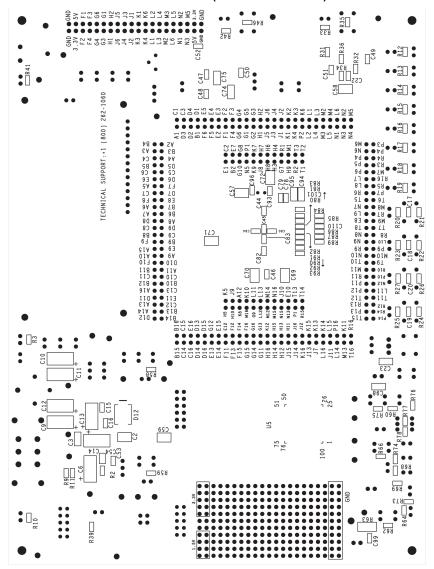

| Figure 2               | Fusion Evaluation Board Top Silkscreen                          |    |

| Figure 3               | Design Block Diagram                                            |    |

| -                      | Data Block Diagram                                              |    |

| Figure 4               | LCD State Diagram                                               |    |

| Figure 5 Figure 6      |                                                                 |    |

| •                      | CoreABC Demo Design Block Diagram                               | 10 |

| Figure 7               | Microsemi Libero IDE New Project Wizard Device Selection        |    |

| Figure 8               | Core Console Component Creation Wizard                          |    |

| Figure 9               | CoreABC Configuration Dialog Box—Parameters Tab                 |    |

| Figure 10              | CoreABC Configuration Dialog Box—Program Tab                    |    |

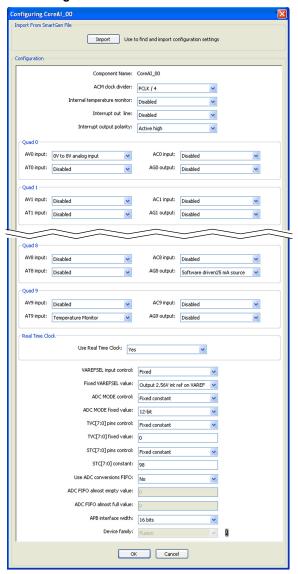

| Figure 11              | CoreAl Configuration Dialog Box                                 |    |

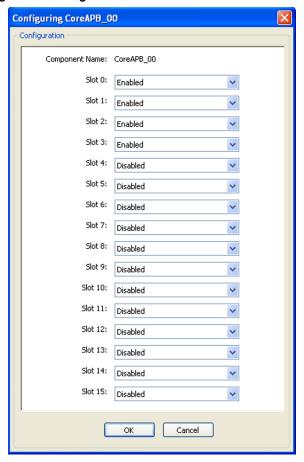

| Figure 12              | CoreAPB Configuration Dialog Box                                |    |

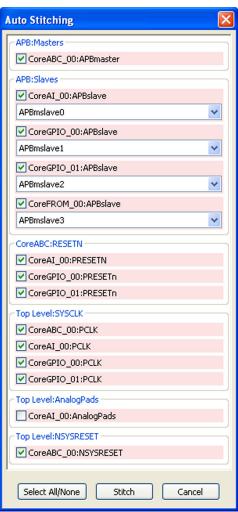

| Figure 13              | Auto Stitch Dialog Box                                          |    |

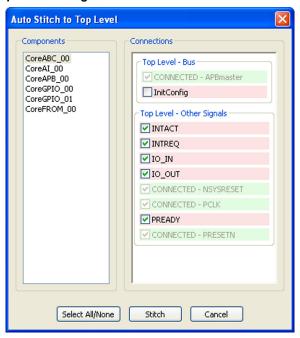

| Figure 14              | Auto Stitch to Top Level Dialog Box                             |    |

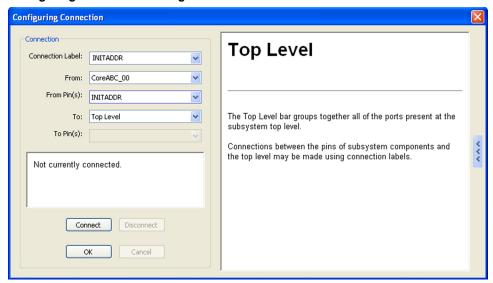

| Figure 15              | Configuring Connection Dialog Box                               |    |

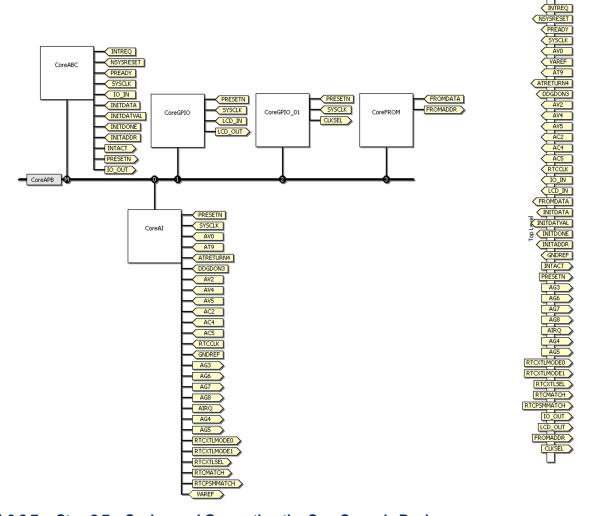

| Figure 16              | CoreABC Subsystem CoreConsole Schematic                         |    |

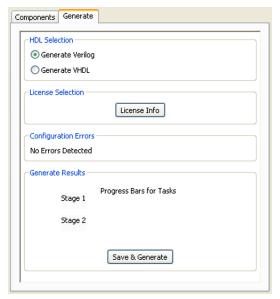

| Figure 17              | CoreConsole Generate Tab                                        |    |

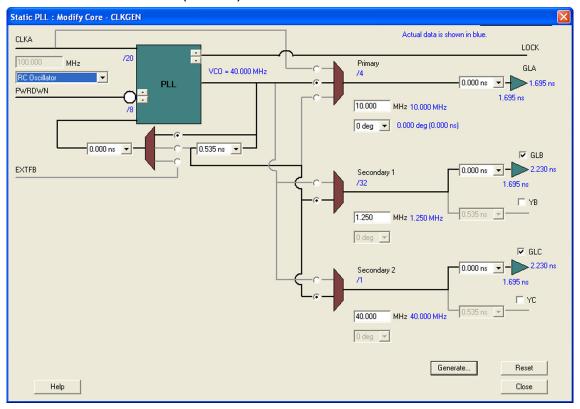

| Figure 18              | Create the PLL Macro (CLKGEN)                                   |    |

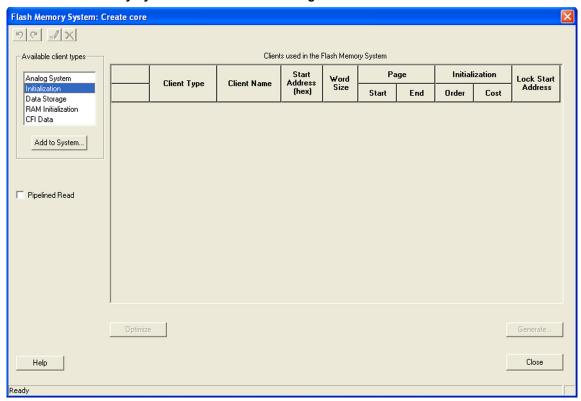

| Figure 19              | Flash Memory System Builder Creation Dialog Box                 |    |

| Figure 20              | Initialization Client Configuration                             |    |

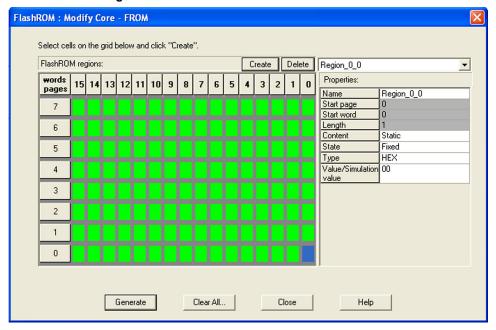

| Figure 21              | FROM Macro Configuration                                        |    |

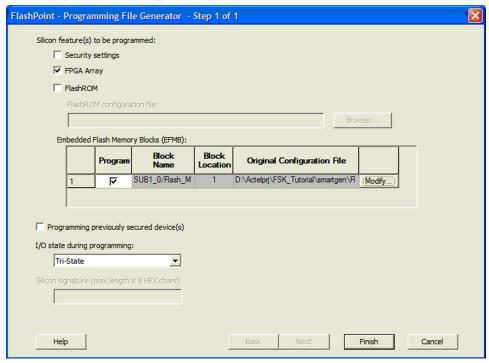

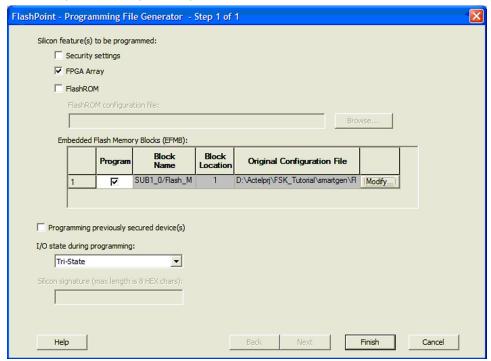

| Figure 22              | Generating the Fusion Programming File                          |    |

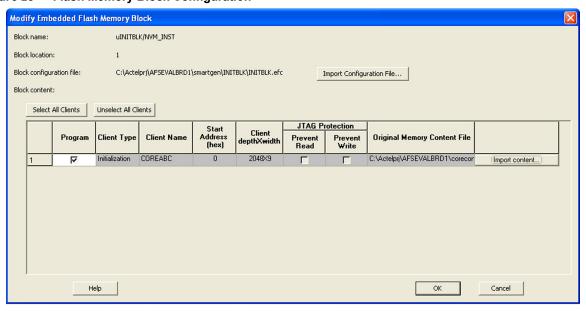

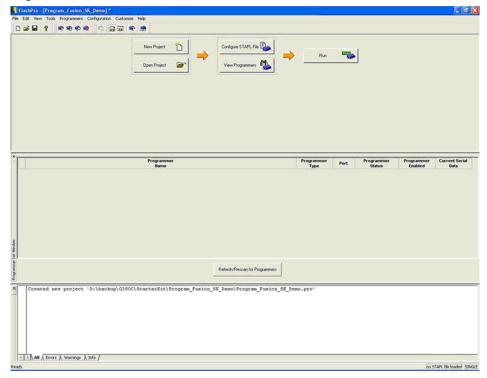

| Figure 23              | Flash Memory Block Configuration                                | 36 |

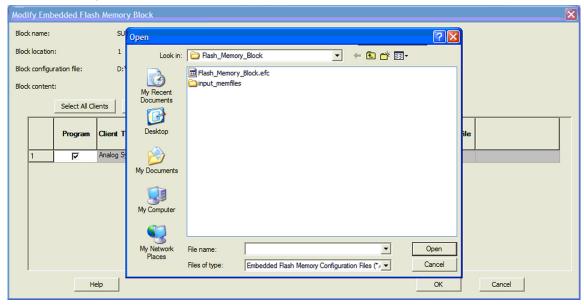

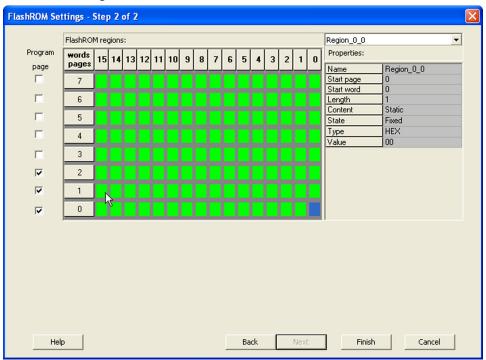

| Figure 24              | Loading the EFC File                                            | 37 |

| Figure 25              | FlashROM Settings                                               | 37 |

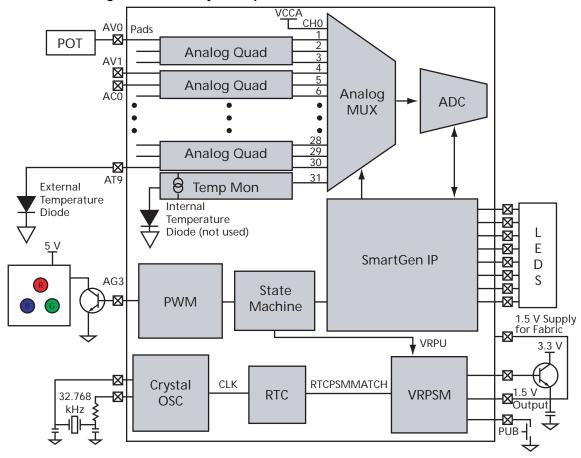

| Figure 26              | Block Diagram Functionality Description                         | 39 |

| Figure 27              | Create Libero IDE Project                                       |    |

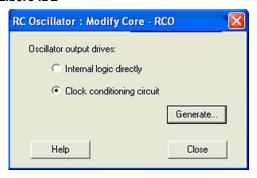

| Figure 28              | RC Oscillator from Libero IDE                                   | 42 |

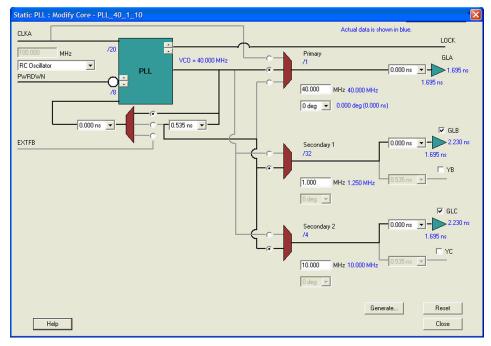

| Figure 29              | Generate PLL Macro from Libero IDE                              | 43 |

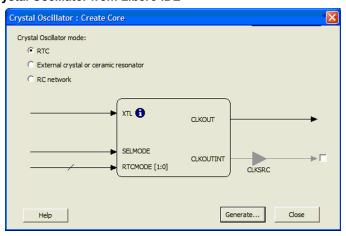

| Figure 30              | Generate Crystal Oscillator from Libero IDE                     | 43 |

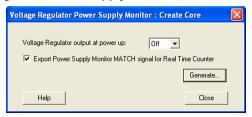

| Figure 31              | Generate Voltage Regulator Power Supply Monitor from Libero IDE |    |

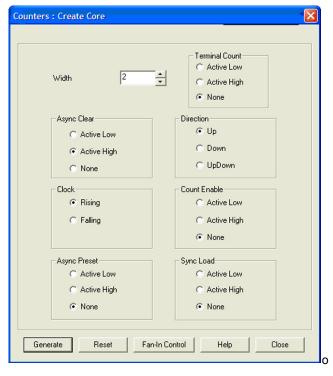

| Figure 32              | Generate 22-Bit Counter from Libero IDE                         | 44 |

| Figure 33              | Generate 2-Bit Counter from Libero IDE                          |    |

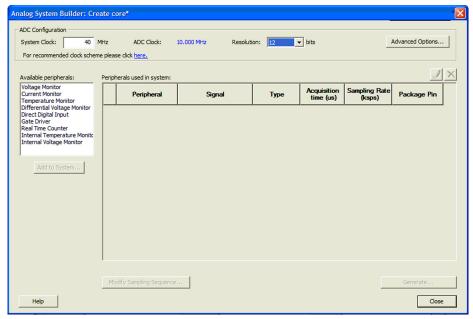

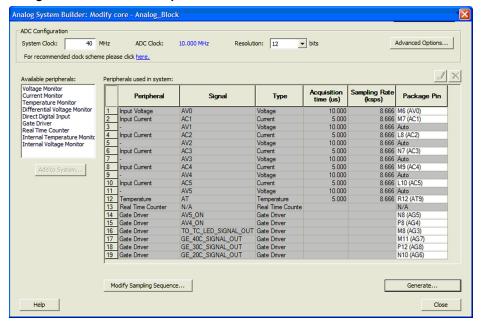

| Figure 34              | Generate Analog System from Libero IDE                          |    |

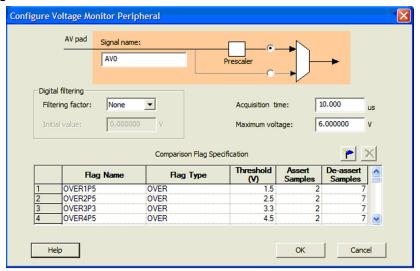

| Figure 35              | Voltage Monitor AV0                                             |    |

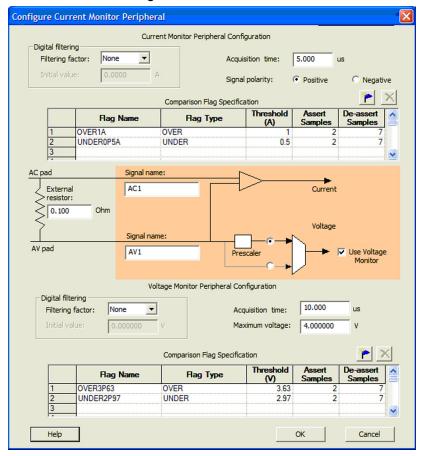

| Figure 36              | Current Monitor AC1 and Voltage Monitor AV1                     |    |

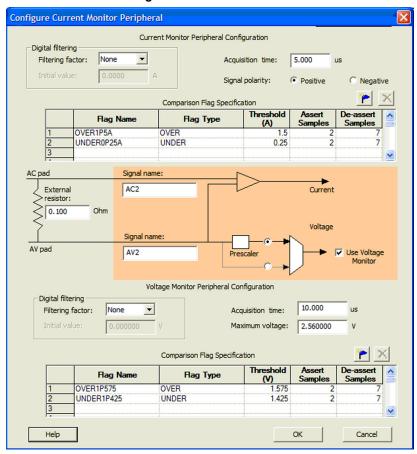

| Figure 37              | Current Monitor AC2 and Voltage Monitor AV2                     |    |

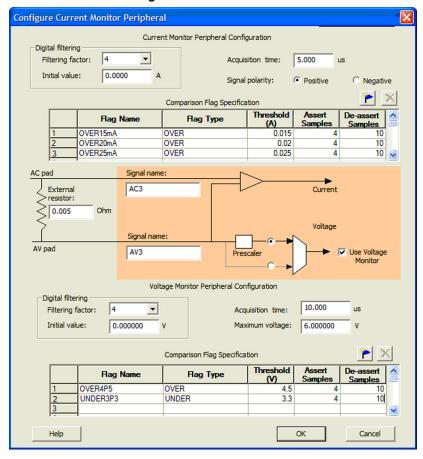

| Figure 38              | Current Monitor AC3 and Voltage Monitor AV3                     |    |

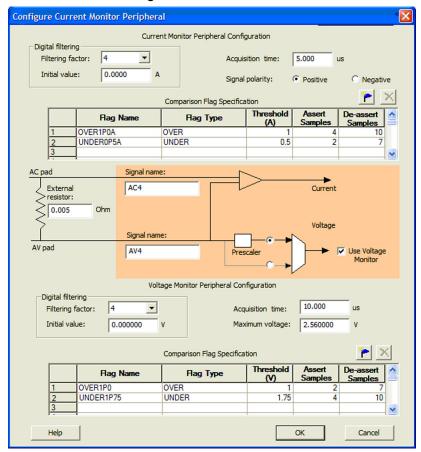

| Figure 39              | Current Monitor AC4 and Voltage Monitor AV4                     |    |

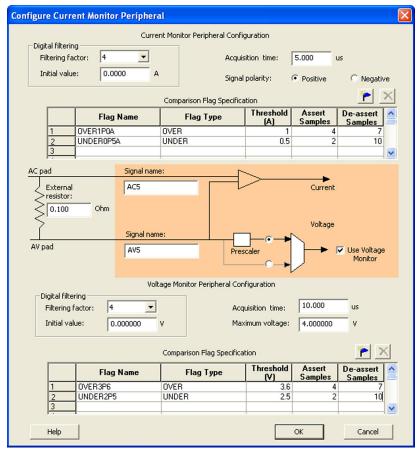

| Figure 40              | Current Monitor AC5 and Voltage Monitor AV5                     |    |

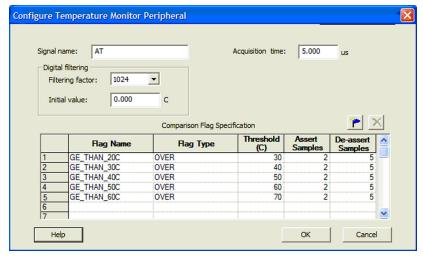

| Figure 41              | · ·                                                             | 51 |

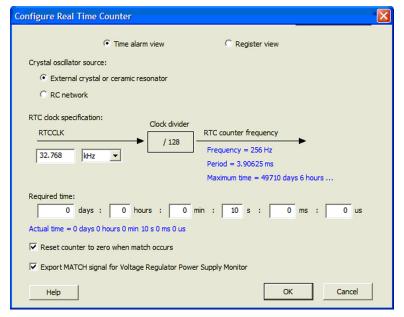

| Figure 42              | Real-Time Counter                                               |    |

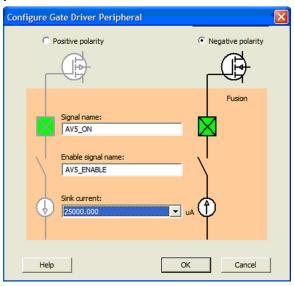

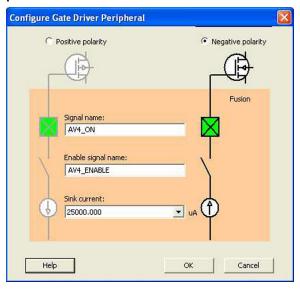

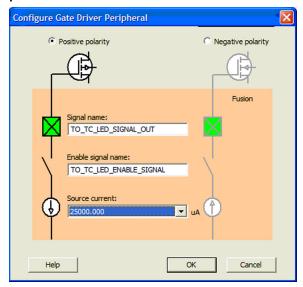

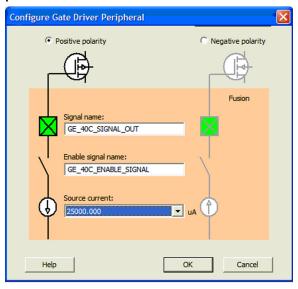

| Figure 43              | Gate Driver – Step 1                                            |    |

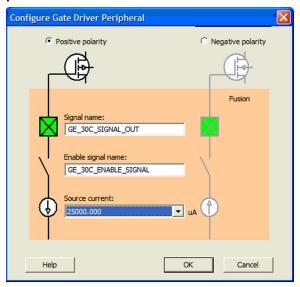

| Figure 44              | Gate Driver – Step 2                                            |    |

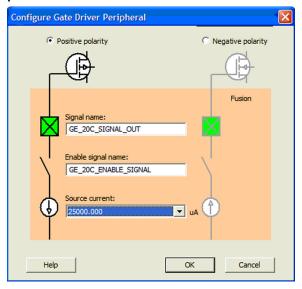

| Figure 45              | Gate Driver – Step 3                                            |    |

| Figure 46              | Gate Driver – Step 4                                            |    |

| Figure 47              | Gate Driver – Step 5                                            |    |

| Figure 48              | Gate Driver – Step 6                                            |    |

| Figure 49              | Advanced Analog System Options Dialog Box                       | 56 |

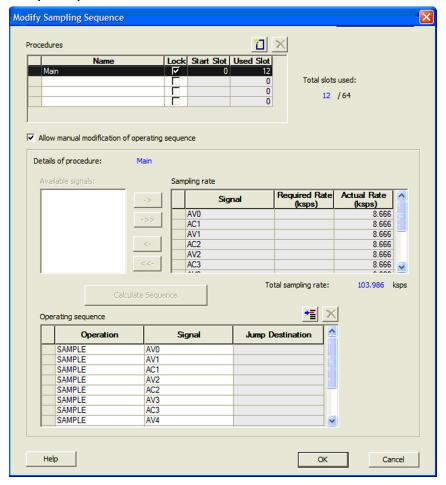

| Figure 50              | ADC Sample Sequence                                             |    |

| Figure 51              | Package Pin Number and Peripheral                               |    |

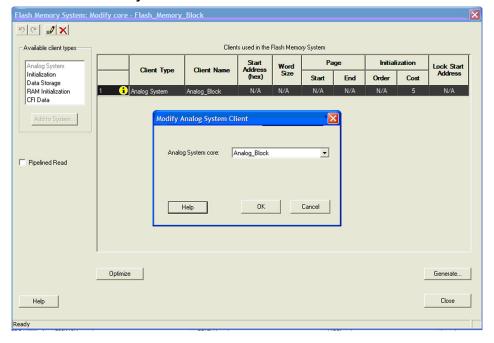

| Figure 51              | Generate Flash Memory Block from Libero IDE                     |    |

| Figure 52<br>Figure 53 | ·                                                               |    |

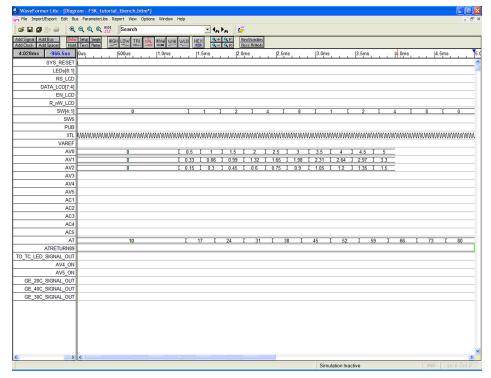

| Figure 53<br>Figure 54 | Create Testbench                                                |    |

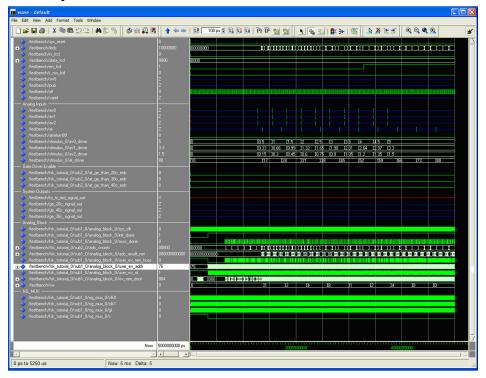

| ı iyul <del>e</del> 54 | Taur re-oynuresis officiation                                   | υı |

| Figure 55 | Generating Fusion Programming File                                 | 62  |

|-----------|--------------------------------------------------------------------|-----|

| Figure 56 | Program the AFS600 on the Fusion Evaluation Board                  |     |

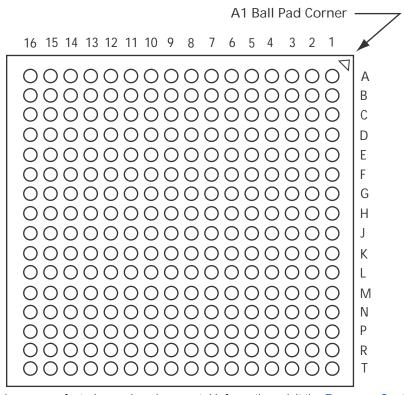

| Figure 57 | 256-Pin FBGA                                                       | 68  |

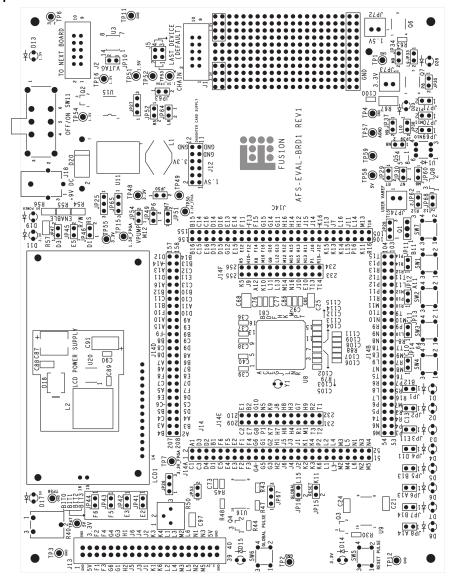

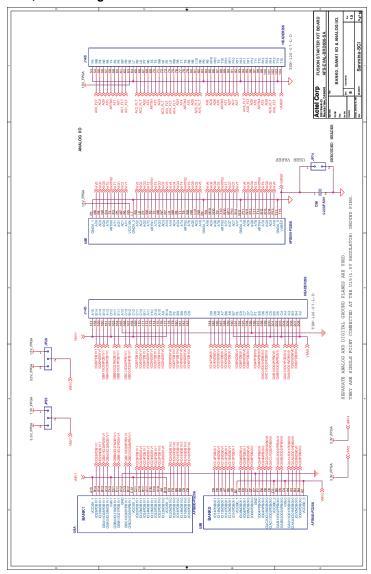

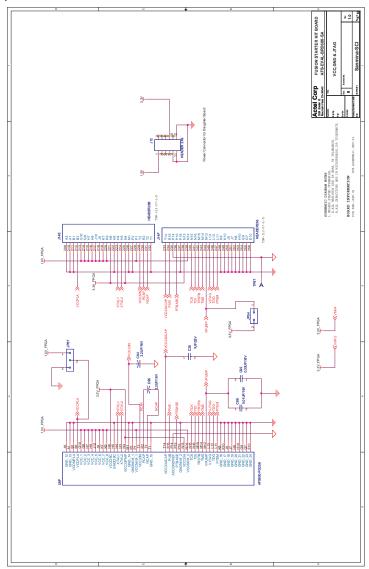

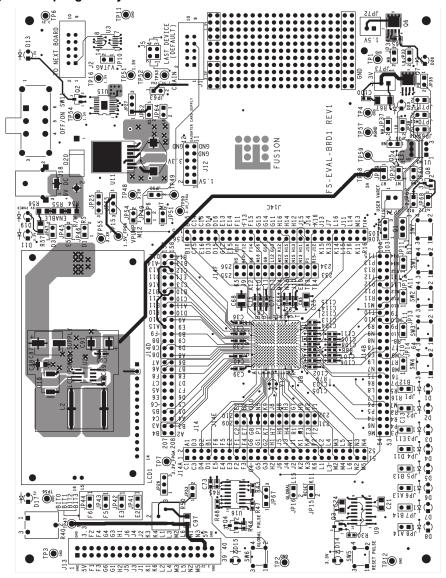

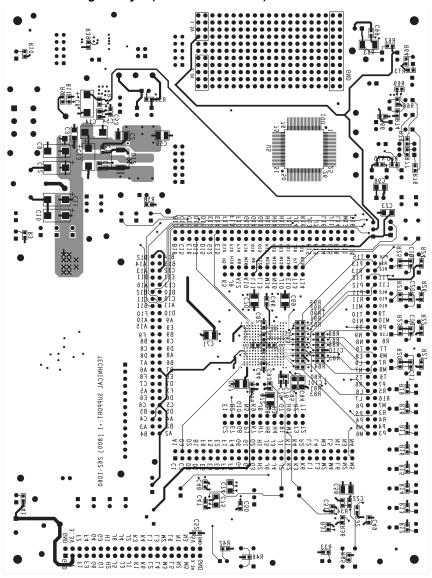

| Figure 58 | Top View of Fusion Evaluation Board                                | 78  |

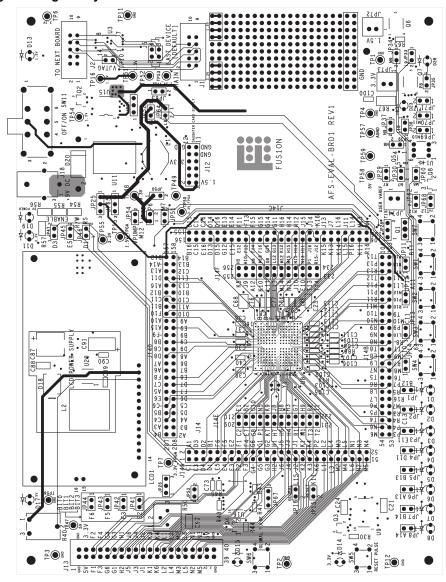

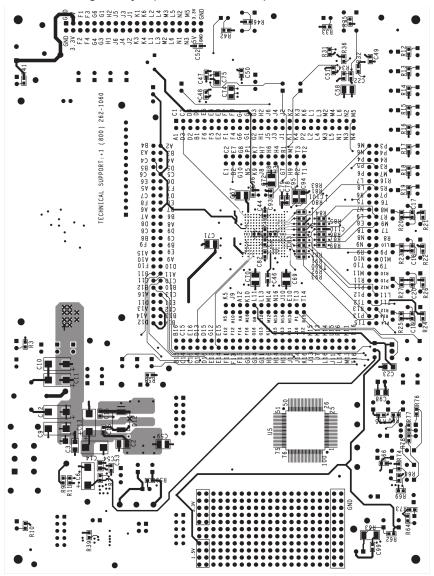

| Figure 59 | Bottom View of Fusion Evaluation Board (viewed from above)         | 79  |

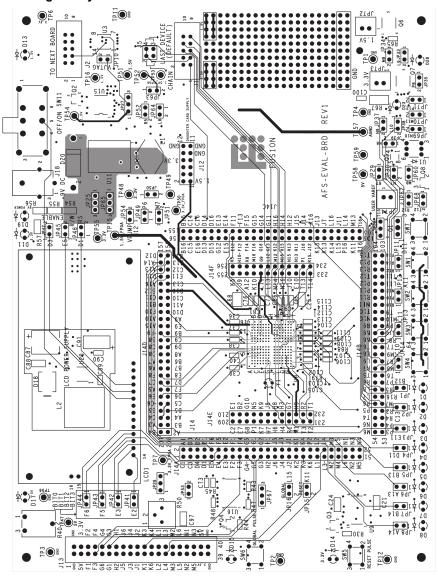

| Figure 60 | Bottom View of Fusion Evaluation Board (viewed from below)         | 80  |

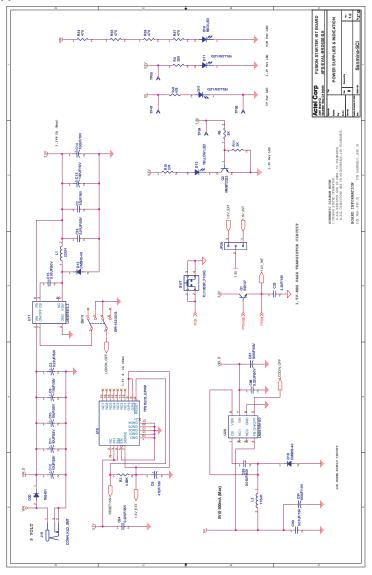

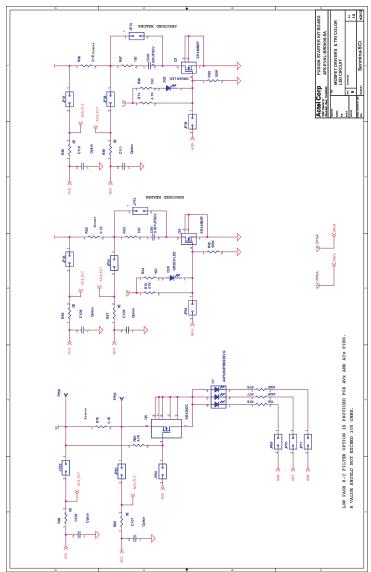

| Figure 61 | Power Supplies and Indication                                      | 8   |

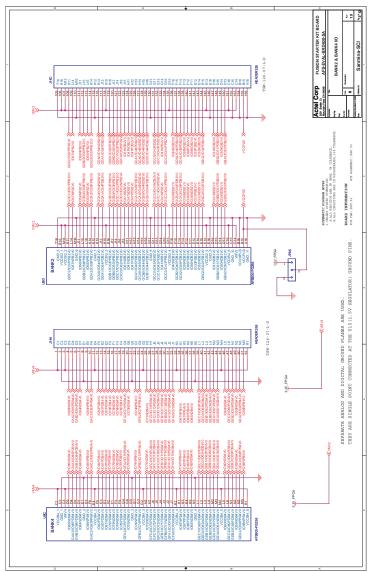

| Figure 62 | Bank 2 and Bank 4 I/O                                              | 82  |

| Figure 63 | Bank 0, Bank 1, and Analog I/O                                     | 83  |

| Figure 64 | VCC, GND, and JTAG                                                 | 84  |

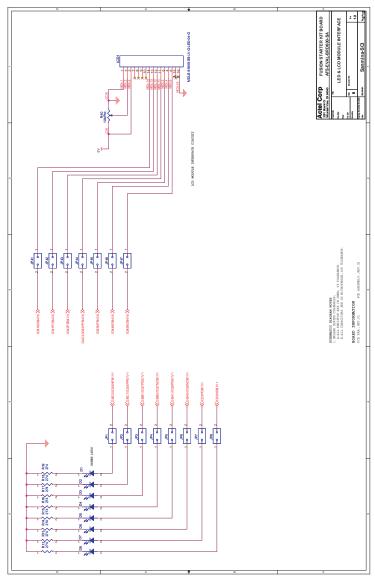

| Figure 65 | LED and LCD Module Interface                                       | 85  |

| Figure 66 | Push Button Interface and 40-Pin Header                            | 86  |

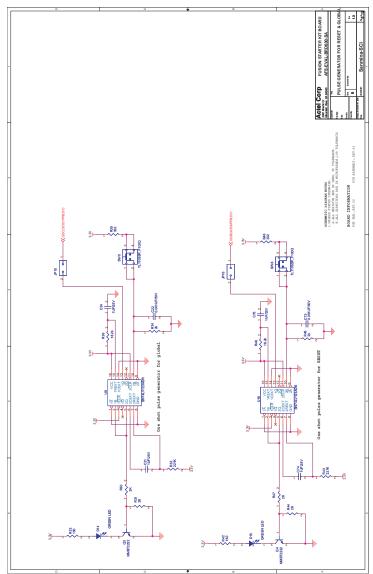

| Figure 67 | Pulse Generator for Reset and Global                               | 87  |

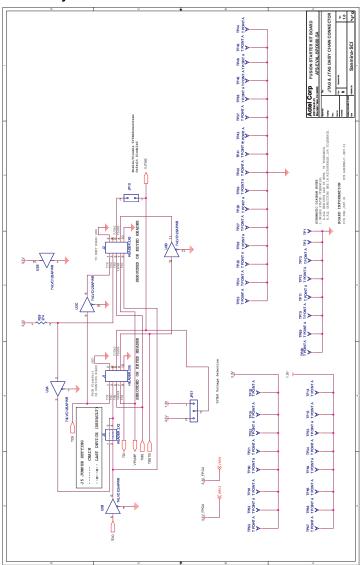

| Figure 68 | JTAG and JTAG Daisy Chain Connector                                | 88  |

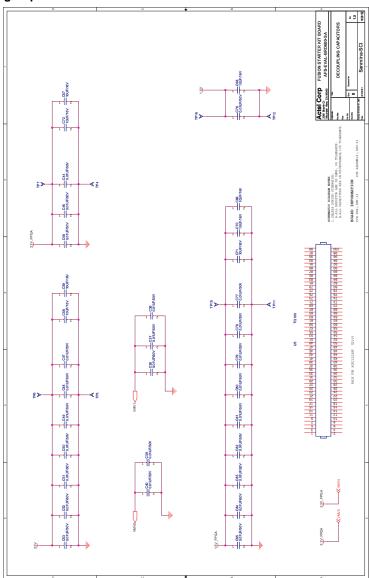

| Figure 69 | Decoupling Capacitors                                              | 89  |

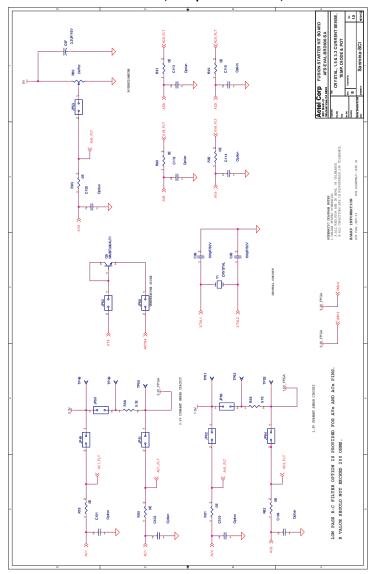

| Figure 70 | Crystal, 1.5 V and 3.3 V Current Sense, Temperature Diode, and Pot |     |

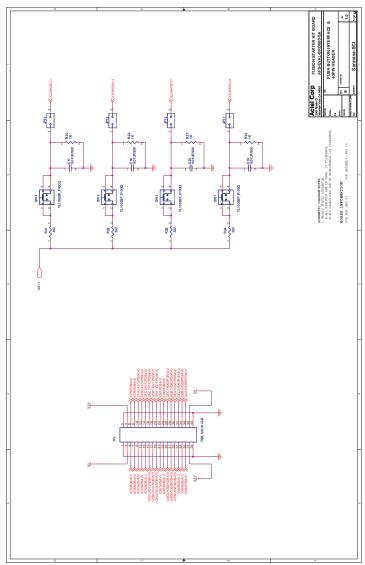

| Figure 71 | MOSFET Drivers and Tricolor LED Circuit                            | 9   |

| Figure 72 | Layer 1 – Top Signal Layer                                         | 93  |

| Figure 73 | Layer 3 – Signal Layer                                             | 94  |

| Figure 74 | Layer 4 – Signal Layer                                             | 95  |

| Figure 75 | Layer 6 – Bottom Signal Layer (viewed from above)                  | 96  |

| Figure 76 | Layer 6 – Bottom Signal Layer (viewed from below)                  | 97  |

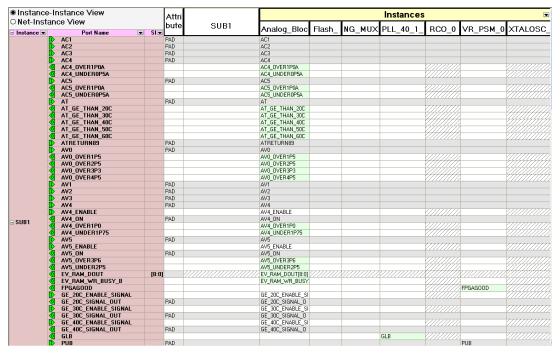

| Figure 77 | SUB1 Connections                                                   | 98  |

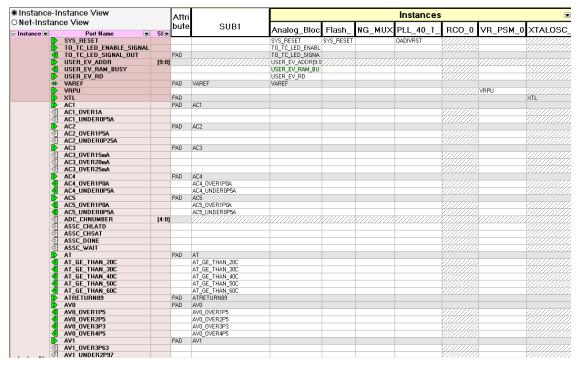

| Figure 78 | SUB1 Connections                                                   | 99  |

| Figure 79 | SUB1 Connections                                                   | 99  |

| Figure 80 | SUB1 Connections                                                   | 100 |

| Figure 81 | FSK_Tutorial Connections                                           | 100 |

| Figure 82 | FSK_Tutorial Connections                                           | 10  |

| Figure 83 | FSK Tutorial Connections                                           | 103 |

# **Tables**

| Table 1  | Kit Contents                                                                         | 2  |

|----------|--------------------------------------------------------------------------------------|----|

| Table 2  | Jumper Function Listings and Silkscreen Grid Locations                               |    |

| Table 3  | Switches                                                                             |    |

| Table 4  | Functionality of the Potentiometer, LEDs and Switches on the Fusion Evaluation Board | 16 |

| Table 5  | Special Jumper/Pin Settings and Their Functionality                                  | 17 |

| Table 6  | CoreABC Configuration Parameters                                                     |    |

| Table 7  | CoreAl Configuration Parameters                                                      | 22 |

| Table 8  | Required Component and Top-Level Signal Name                                         |    |

| Table 9  | Functionality of the Potentiometer, LEDs, and Switches                               | 40 |

| Table 10 | Special Jumper/Pin Settings and Their Functionality                                  | 4  |

| Table 11 | On-Board LED Setup for Voltage Monitor AV0                                           | 46 |

| Table 12 | On-Board Tricolor LED Setup for Temperature Monitor AT                               | 52 |

| Table 13 | AFS600-FG256 Pin Connections for Fusion Starter Kit Board                            | 68 |

| Table 14 | Actual Correspondence between Mismatched Pin Labels                                  | 92 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## **1.1** Revision 6.0

The following is a summary of the changes in revision 6.0 of this document.

- Updated chapter Introduction, page 2.

- Libero SoC software license information was updated from Gold to Silver. For more information, see Software Installation, page 3.

# 2 Introduction

This guide provides the information required to easily evaluate Fusion devices.

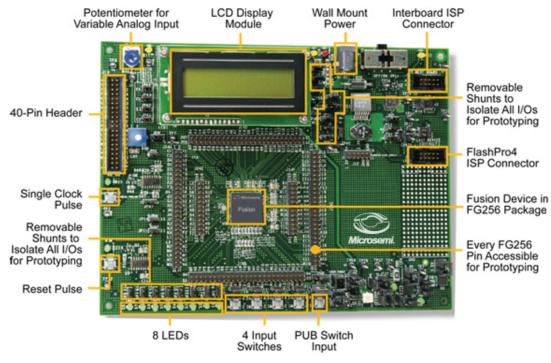

Figure 1 • The Fusion Evaluation Board

## 2.1 Kit Contents

The following table lists the contents of the Fusion Starter Kit.

Table 1 • Kit Contents

| Item                                                | Quantity |

|-----------------------------------------------------|----------|

| Evaluation board with an AFS600-FG256 Fusion device | 1        |

| FlashPro4 programmer                                | 1        |

| 9 V power supply with International adapters        | 1        |

## 3 Installation and Settings

This section provides information about software and hardware settings required to run the pre-programmed demo design in the Fusion Evaluation Board.

### 3.1 Software Installation

Download and install the latest release of Microsemi Libero<sup>®</sup> SoC v11.5 or later, from the Microsemi website and register for your free Silver license. For instructions on how to install Libero SoC and SoftConsole, see the *Libero Software Installation and Licensing Guide*.

#### 3.2 Hardware Installation

FlashPro v4.1 or later is required to use the Fusion Starter Kit. For software and hardware installation instructions, see the *FlashPro for Software User Guide*.

## 3.3 Testing the Evaluation Board

Refer to Test Procedures for Board Testing, page 64.

### 3.4 Programming the Test File

To retest the evaluation board at any time, use the test program to reprogram the board. Use the  $\mathtt{TOP}$   $\mathtt{AFS.stp}$  file with an AFS600-FG256 fitted on the board.

This design is currently implemented for the AFS600 die size. For a device of a different size, it is possible to recompile the design into other device sizes. For information about retargeting the device, see the *Libero IDE User Guide*. The design files are available under

https://www.microsemi.com/products/fpga-soc/design-resources/dev-kits/fusion/fusion-starter-kit#documents.

For instructions on programming the device using FlashPro v4.1, see the *FlashPro for Software User Guide*.

## 4 Hardware Components

This chapter describes the hardware components of the Fusion Evaluation Board.

#### 4.1 Fusion Evaluation Board

The Fusion Evaluation Board consists of the following:

- Wall-mount power supply connector, with switch and LED indicator

- Jumpers to select either 1.5 V or 3.3 V for I/O Bank0 or Bank1

- 10-pin 0.1"-pitch programming connector compatible with Altera connections

- 40 MHz oscillator and two independent manual clock options for global reset and pulse

- Eight LEDs (driven by outputs from the device)

- · Jumpers (allow disconnection of all external circuitry from the FPGA)

- Two monostable pulse generator switches ("global" and "reset")

- · Four switches (provide input to the device)

- · Potentiometer for variable analog input

- Large alphanumeric LCD to facilitate detailed message outputs from the FPGA application

- Multicolor LED for illustrating PWM fan control and temperature measurement

- 1.5 V and 3.3 V MOSFET-driven fan control circuits with shrouded headers for external fans

For further information, refer to the following appendices:

- Appendix: FG256 Package Connections for AFS600 Devices, page 67

- Appendix: Board Schematics, page 78

### 4.2 Board Description and Usage

The Fusion Evaluation Board has various advanced features that are covered in later sections of this chapter. The Fusion architecture provides access to a one-chip flash FPGA solution containing both analog and digital components, including a built-in flash drive.

Note that the AFS600-FG256 Microsemi FPGA is soldered directly to the board. The Fusion Starter Kit board is available only in a directly soldered configuration. Socketed configurations are not available.

Full schematics are available on the Starter Kit at: https://www.microsemi.com/products/fpga-soc/design-resources/dev-kits/fusion/fusion-starter-kit#documents. The electronic schematics can be enlarged on screen to show more detail than will be shown when this manual is printed.

## 4.3 Power Supplies

A 9 V power supply is provided with the kit. There are two power supply components on the board to provide 1.5 V and 3.3 V to the Fusion FPGA. An additional +5 V voltage bank is provided for use by the LCD module and in illustrating an analog voltage input to the analog aspects of the Fusion Evaluation Board.

The external +9 V positive-center power supply provided to the board via connector J18 goes to a voltage regulator chip, U11. This regulator has been protected against application of a reverse supply voltage by a reverse polarity protection diode. As soon as the external voltage is connected to the board, the red "power applied" LED (D19, the only red LED on the board) illuminates to indicate that an external supply has been connected to the board. As soon as switch SW11 is moved to the ON position (to the right, as labeled on the board "OFF/ON"), the disabling ground signal is removed from pin 7 of U11, and the regulator begins to provide power at its output.

The U11 switching voltage regulator provides a dedicated 3.3 V supply at its output. The board's 3.3 V supply feeds a separate regulator that delivers 1.5 V via U15. Although all Fusion FPGAs can also support 1.8 V and 2.5 V I/O standards, these voltages are not provided on the Fusion Evaluation Board. The 1.5 V supply is required for the core voltage of the Fusion family, and the 3.3 V supply is required for extended I/O bank capability, such as for LVTTL. The presence of these voltages is indicated by two yellow LEDs (D13 for 1.5 V and D11 for 3.3 V) located at the top right of the board. Each LED is labeled with the voltage it represents and its component identifier. Both voltages are selectable on I/O banks 0

and 1 (the two northernmost banks on a Fusion device). Note that only the larger Fusion devices (AFS600 and AFS1500) have five I/O banks.

The 3.3 V supply can also be used to provide the VPUMP programming voltage. This VPUMP voltage may be provided to the chip during programming by connecting a FlashPro3 programmer to the J1 interface and selecting VPUMP from the FlashPro v4.1 (or later) programming software, and may also be provided directly to the chip from the board. The user simply leaves the JP54 jumper in place to apply the 3.3 V supply to the VPUMP pin (M12) of the FG256-packaged FPGA. If both FlashPro3 and the board are selected to provide VPUMP, the connection on the board will override; FlashPro3 will detect that a voltage is available, issue an information message in the programming software, and then tristate its VPUMP output pin, allowing the board to provide all the power.

The board must be powered up during programming, as the chip's core voltages must be provided and VJTAG must be detected by the FlashPro3 programmer before it can set its JTAG signal voltages to the right level. The value of VJTAG can be set to 1.5 V or 3.3 V on the board by setting the position of jumper JP27 to join pins 1 and 2 for 1.5 V and pins 2 and 3 for 3.3 V. It is recommended that VJTAG be left at 3.3 V on the Fusion Evaluation Board because an interboard buffer chip is used that has limited low-voltage capability and needs the higher setting of 3.3 V to ensure good signals at the output of the buffer chip array U3.

The LCD has its own dedicated 5 V power supply, all components of which, including the regulator U20, are mounted on the circuit board underneath the LCD module. A yellow LED (D17) representing 5 V supply availability is positioned at the top left of the board.

The external +9 V power supply is rated at 2.2 A maximum. On page 1 of the dedicated schematics and in Figure 61, page 81, it will be noted that the 3.3 V supply is rated at 5 A maximum. The derived power supply of 1.5 V is rated at 2 A maximum, and the LCD 5 V power supply is rated at 500 mA.

The components at U11 (LM2678S-3.3) and U20 (LM2674M-5.0) are rated for an input voltage range of +8 V to +40 V, so a wide range of power supplies may be used with the board with no worry of overvoltage conditions occurring from inadvertent usage of the wrong power supply. It is expected that the voltage provided will be positive at the center pin of connector J18 and grounded on the outside. There is protection on the Fusion Evaluation Board for reverse voltages to prevent damage, but correct polarity must be provided for the board to function. Note that greater heating of the regulator chips will occur with higher voltages. Microsemi recommends that only the included power suply or an equivalent substitute be used with the Fusion Starter Kit, as it has been rated for the Fusion Evaluation Board and any Microsemi daughter cards that may be attached to the board.

## 4.3.1 Daughter Card Power Supply Connections

Limited power may be supplied by the Fusion Evaluation Board to a daughter card. The connector for the daughter card (header J12) is shown on page 5 of the dedicated schematics and in Figure 64, page 84. All the FPGA voltages of 1.5 V and 3.3 V are provided to the daughter card via a 12-pin, 0.1"-pitch connector. The reason for 12 pins is that this is compatible with the 12 pins used on the ProASIC3 Starter Kits and makes the daughter cards potentially compatible between the kits. The voltages are arranged with no-connection pins interspersing the voltage pins to prevent use of a jumper to inadvertently short a supply rail to ground by connecting differing supply rails together. This is not to protect the power supply regulators, as these will go high-impedance when an over-voltage condition is detected, but to protect the FGPA from a higher voltage being unintentionally applied to the 1.5 V core. Three of the 12 pins are ground pins to provide more than sufficient current return capability for future Microsemi daughter cards that will work with the Fusion Evaluation Board. The remaining pins are no-connection to prevent accidental shorting.

## 4.3.2 Power Supplies and Chaining Boards Together

There is a special note to be made of VPUMP connections when chaining boards together. This is detailed here. Microsemi recommends that the reader, unless experienced with Microsemi Starter Kit boards, return to this section after reading Figure 4.4, page 6.

When joining multiple Fusion or ProASIC3 Starter Kit boards together via the chain programming connection, connect J2 on one board to J1 on the next board in the chain using a standard 10-pin, 0.1"-pitch programming cable. Ideally, twisted-pair ribbon cabling should be used for this connection. The length of the cable should be kept as short as possible, as multiple boards connected to form a JTAG

chain of Fusion and ProASIC3/E and/or ARM®-enabled Fusion or ProASIC3 devices will provide much greater noise pick-up and may degrade the TCK clock for devices remote from the FlashPro3 programmer. Microsemi recommends that VJTAG be set at 3.3 V to help with signal integrity when chaining boards together. On all boards the jumper at JP10, if connected, is used for providing VJTAG to a downstream board that needs to know what VJTAG setting is being used by your board (e.g., some arbitrary board of your own design that you wish to supply with the VJTAG voltage used by the Fusion component). In most normal cases, this shunt should be disconnected. The shunt normally in this location can be safely stored across pins 11 and 12 or 9 and 10 of the J12 daughter card power supply connector. For particularly long chains, the value of TCK used during programming should be reduced. The lowest value it can take is 1 MHz.

To date, only one revision of the Fusion Evaluation Board has been produced. This first version of the board is labeled REV1 next to the AFS-EVAL-BRD1 label on the board. If the Fusion Evaluation Board is connected in a chain to ProASIC3/E boards, the documentation relating to the ProASIC3/E board should be read in detail to determine the appropriate connection setting, depending on the version of the ProASIC3/E board being used. The following notes are only for the Fusion Evaluation Board.

#### 4.3.2.1 Procedure for Rev1 Fusion Evaluation Boards

#### 4.3.2.1.1 To determine if the board is a Rev1 board:

To identify a Rev1 board, examine the front of the board and look for the part number located just beneath the large Actel logo silkscreened on the board. The part number will be "AFS-EVAL-BRD1" followed by "REV1".

#### 4.3.2.1.2 To chain Rev1 boards together:

All boards, starting from the board nearest the FlashPro3 programmer, should have the shunt moved from the default location connecting pins 3 and 4 of the J5 header to connect pins 1 and 2 of the J5 header. On the board and schematic this is labeled "CHAIN" (pins 1 and 2) and "LAST DEVICE (DEFAULT)" (pins 3 and 4). Only the very last board in the chain should have the shunt remaining across pins 3 and 4 of the J5 connector.

When connecting these boards together via a connection from J2 of one board to J1 of another board, VPUMP will be connected from one board to another. When powering up one board with a connector in place, notice that the 1.5 V and 3.3 V LEDs will light on the board to which no power has been applied, and the FPGA on that board, if programmed, will start operating. This is clearly an inappropriate situation for a large chain of boards. This is caused by having connector JP54 supplying VPUMP to other boards in the chain, as VPUMP is itself connected to the 3.3 V supply output that is used to generate the other FPGA voltages on a board. To prevent VPUMP from being used as the 3.3 V supply, you should remove the shunt that is in place on the JP54 connector to force JP54 open-circuit. To prevent loss of the shunt, it may safely be stored on the J12 header for the daughter card power supply, as it is impossible to cause a short by joining any adjacent pins.

## 4.4 Programming the AFS-EVAL-BRD1 with a FlashPro3

The base board used for all Fusion starter kits is the AFS-EVAL-BRD1.

In an AFS EVAL KIT the Microsemi part number for the board is AFS-EVAL-BRD600-SA. The part number indicates that the board is fitted with an AFS600-FG256 part, directly soldered (-SA) to the board.

### 4.4.1 Connecting the FlashPro3 Programmer to the Board

Connect the FlashPro3 programmer to your computer via the USB cable. Follow the instructions in the *FlashPro for Software User Guide* to install the software and connect to the FlashPro3 programmer. The amber (yellow) power LED on the FlashPro3 should be illuminated at this stage. If it is not, recheck the procedure in the FlashPro user's guide until you obtain a steady amber (yellow) power LED illumination.

Make sure the board power switch SW11 is in the OFF position and only the red board external power LED is illuminated on the board.

Connect the FlashPro3 programmer to the board via the 10-pin programming cable supplied with the programmer hardware. The connector to use on the board is labeled "FP3" and is the lower shrouded

and keyed header J1. The pin 1 location on the cable indicated by the red ribbon running along the side of the cable will be on the left side as it enters into the board. After connecting the FlashPro3 programmer, using the FlashPro software, select **Analyze Chain** from the **File** menu. If all is well, the appropriate device ID for the Fusion part will appear in the software display on the PC. If you suspect a JTAG communication issue, try changing the VJTAG voltage to 3.3 V using JP27.

### 4.4.2 Programming or Re-Programming the Example Design

On the Fusion Starter Kit CD, you will find a *Designer* directory containing a STAPL file for programming the target design. Select the *TOP\_AFS.STP* file from the CD and use that as the STAPL file in the FlashPro v4.1 software. Clicking **PROGRAM** will erase, program, and verify the part. The total programming time is approximately 2 minutes and 30 seconds.

### 4.4.3 Jumpers for Isolating Switches and LEDs from the FPGA

The many jumpers on the Fusion Evaluation Board are provided to allow the user to disconnect various switch combinations or LEDs from the FPGA I/O banks.

The jumpers are shown in the schematic and are labeled on the top-layer silkscreen as JP\*, where \* is a number. All jumpers are also labeled with the FPGA I/O pin number to which they are connected, e.g., JP54, for 3.3 V connection of VPUMP to the FPGA, is labeled "M12", which indicates that it is connected to pin M12. Similarly, SW4 has a jumper above it called JP14 that is labeled "C10", indicating that SW4 is connected through to pin C10 of the FPGA when this jumper is in place.

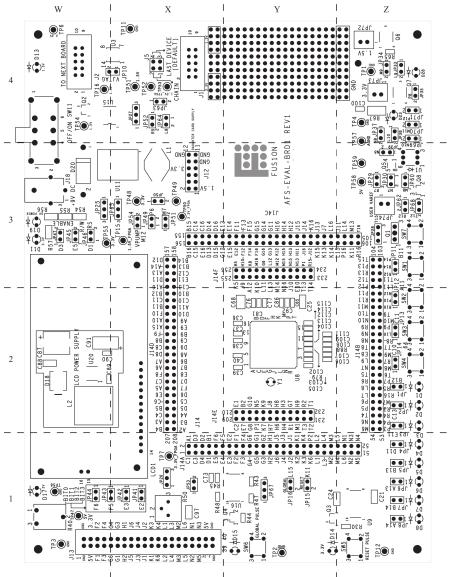

Figure 2, page 8 shows the board's silkscreen layer overlaid with a grid, and Table 2, page 9 describes the function of each jumper and its location.

By disconnecting jumpers JP11, JP12, JP13, and JP14, momentary push button switches SW1, SW2, SW3, and SW4, respectively, can be disconnected from the FPGA such that the I/O pins B11, A11, C11, and C10, respectively, may be used for other purposes. Disconnecting jumpers JP1–JP8 will disconnect LEDs D1–D8 from FPGA I/O pins B12, C13, E11, D11, B13, A13, B14, and A14, respectively.

Momentary push button switches SW5 and SW6, for applying a reset pulse and a global pulse, are connected via jumpers JP15 and JP16 to I/Os K11 and L15, respectively. Again, all labeling is clearly shown on the silkscreen.

The LCD also has associated jumpers for its data, namely JP41, JP42, JP43, and JP44, located on the top left side of the board. These are connected to I/O pins E2, E3, F5, and F6, respectively. The LCD control signals Enable, R/W, and RS are provided from I/O pins D3, E5, and D1 via jumpers JP47, JP45, and JP46, respectively.

## 4.4.4 Analog Circuitry Provided on the Board

A variety of analog inputs and outputs are provided on the Fusion Evaluation Board to show what Fusion can do as a single-chip solution. These components are detailed below and in Table 2, page 9, enumerating all possible connectivity. As with all other components, the FPGA pins may be disconnected from these components to allow the board to be used for other functions.

A potentiometer (R50) is provided on the board for simple user variation of analog input. This input is fed to the AV0 pad.

A multicolor LED, U1, is provided and has three individual color components that can be controlled by a set of AG pins (AG6 – Blue, AG7 – Orange, AG8 – Green). By using the analog outputs, PWM control as well as individual switch control can be effected. The multicolor LED is enabled with a p-channel MOSFET (Q5), where pad AG3 is connected to the gate of the MOSFET.

#### 4.4.4.1 Motor Control

The Fusion Starter Kit board provides connections to two n-channel MOSFETs, Q6 and Q7, that are used to control current fed via the 1.5 V supply and the 3.3 V supply to an externally connected fan. Fans can be connected to the shrouded headers, JP72 and JP73, mounted on the board. An RC network is connected across each of these shrouded headers to filter out the back-EMF pulse that will occur when suddenly switching on or off a motor winding. Current is being measured via the AV and AC pads in each case by monitoring the voltage drop across a 0.1  $\Omega$  resistor (R62 for 1.5 V and R66 for 3.3 V) in each case. The AV and AC pads are tolerant to  $\pm 12$  V DC; however, the voltage spike from a motor winding

being switched off will be much greater than this, so an RC "snubber" network is required to dampen such a voltage pulse and prevent it from reaching the FPGA inputs. Failure to apply an RC circuit across a motor when measuring the current through the field winding via direct connection to the FPGA will almost certainly result in voltages outside the maximum tolerance range of the FPGA's analog inputs, which may result in catastrophic failure of the FPGA.

On the Fusion Evaluation Board, the n-channel MOSFETs are connected to a positive voltage supply. Because they are driven by the AG pads, their operation is inverse to normal. When AG pads on the FPGA are active, they float down or up to 0 V. When inactive they are tristated and switch off an n-channel MOSFET that is connected to the positive supply rail when activated. Normally, n-channel MOSFETs use the AG gate-drivers when the n-channel MOSFET is connected to a negative voltage supply. In this case, activating the AG gate-driver pad to 0 V will switch on the n-channel MOSFET.

Figure 2 • Fusion Evaluation Board Top Silkscreen

The following table lists jumper function listings and silkscreen grid locations.

Table 2 • Jumper Function Listings and Silkscreen Grid Locations

| Jumper | Starter Kit Function                                                     | Notes                                                                       | Grid<br>Location<br>Z2 |  |

|--------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------|--|

| JP1    | Disconnects green LED D1                                                 | Pin 1 to LED, pin 2 to FPGA B12                                             |                        |  |

| JP2    | Disconnects green LED D2                                                 | Pin 1 to LED, pin 2 to FPGA C13                                             | Z2                     |  |

| JP3    | Disconnects green LED D3                                                 | Pin 1 to LED, pin 2 to FPGA E11                                             | Z2                     |  |

| JP4    | Disconnects green LED D4                                                 | Pin 1 to LED, pin 2 to FPGA D11                                             | Z1                     |  |

| JP5    | Disconnects green LED D5                                                 | Pin 1 to LED, pin 2 to FPGA B13                                             | Z1                     |  |

| JP6    | Disconnects green LED D6                                                 | Pin 1 to LED, pin 2 to FPGA A13                                             | Z1                     |  |

| JP7    | Disconnects green LED D7                                                 | Pin 1 to LED, pin 2 to FPGA B14                                             | Z1                     |  |

| JP8    | Disconnects green LED D8                                                 | Pin 1 to LED, pin 2 to FPGA A14                                             | Z1                     |  |

| JP9    | – No such jumper –                                                       | _                                                                           | _                      |  |

| JP10   | Enables VJTAG downstream to next board                                   | Pin 1 to VJTAG of FPGA, pin 2 to programming header J2 pin 6 for next board | W4 and X4              |  |

| JP11   | Disconnects SW1                                                          | Pin 1 to switch, pin 2 to FPGA B11                                          | Z3                     |  |

| JP12   | Disconnects SW2                                                          | Pin 1 to switch, pin 2 to FPGA A11                                          | Z2                     |  |

| JP13   | Disconnects SW3                                                          | Pin 1 to switch, pin 2 to FPGA C11                                          | Z2                     |  |

| JP14   | Disconnects SW4                                                          | Pin 1 to switch, pin 2 to FPGA C10                                          | Z2                     |  |

| JP15   | Disconnects one-shot pulse initiated by SW5                              | Pin 1 to U9 pin 13, pin 2 to FPGA K11                                       | Y1                     |  |

| JP16   | Disconnects one-shot pulse initiated by SW6                              | Pin 1 to U16 pin 13, pin 2 to FPGA L15                                      | Y1                     |  |

| JP17   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP18   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP19   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP20   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP21   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP22   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP23   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP24   | – No such jumper –                                                       | -                                                                           | _                      |  |

| JP25   | Selects value of VMV1                                                    | Pin 1 is 1.5V_FPGA, pin 2 is VMV1, pin 3 is 3.3V_FPGA                       | W3                     |  |

| JP26   | Selects value of VMV0                                                    | Pin 1 is 1.5V_FPGA, pin 2 is VMV0, pin 3 is 3.3V_FPGA                       | X1                     |  |

| JP27   | VJTAG voltage selection                                                  | Pin 1 is 1.5 V, pin 2 is VJTAG, pin 3 is 3.3 V                              | X4                     |  |

| JP28   | Determines whether 1.5 V is internally generated or externally generated | Pin 1 is 1.5V_INT, pin 2 is 1.5 V, pin 3 is 1.5V_EXT                        | Z3                     |  |

| JP29   | Disconnects AV3                                                          | Pin 1 is TP58 (5.0 V), pin 2 is AV3_FLT (filtered to R7)                    | Z3                     |  |

| JP30   | Disconnects AC3                                                          | Pin 1 is TP59, pin 2 is AC3_FLT (filtered to N7)                            | Z3                     |  |

Table 2 • Jumper Function Listings and Silkscreen Grid Locations (continued)

| Jumper | Starter Kit Function                   | Notes                                                                             | Grid<br>Location |

|--------|----------------------------------------|-----------------------------------------------------------------------------------|------------------|

| JP31   | – No such jumper –                     | _                                                                                 | _                |

| JP32   | – No such jumper –                     | _                                                                                 | _                |

| JP33   | Disconnects AV4                        | Pin 1 is 1.5 V, pin 2 is AV4_FLT (filtered to L9)                                 | Z4               |

| JP34   | Disconnects AC4                        | Pin 1 is JP72 pin 1 for external 1.5 V fan, pin 2 is AC4_FLT (filtered to M9)     | Z4               |

| JP35   | Disconnects AG4                        | Pin 1 is gate of n-channel MOSFET Q6 for 1.5 V fan, pin 2 is AG4 (P8)             | Z4               |

| JP36   | – No such jumper –                     | -                                                                                 | _                |

| JP37   | Disconnects AV5                        | Pin 1 is 3.3 V, pin 2 is AV5_FLT (filtered to N9)                                 | Z4               |

| JP38   | Disconnects AC5                        | Pin 1 is JP73 pin 1 for external 1.5 V fan, pin 2 is AC5_FLT (filtered to L10)    | Z4               |

| JP39   | Disconnects AG5                        | Pin 1 is gate of n-channel MOSFET Q7 for 3.3 V fan, pin 2 is AG5 (N8)             | Z3               |

| JP40   | – No such jumper –                     | -                                                                                 | _                |

| JP41   | Disconnects LCD data Bit3              | Pin 1 is MDL14 – Bit3, pin 2 is FPGA E2                                           | X1               |

| JP42   | Disconnects LCD data Bit2              | Pin 1 is MDL13 – Bit2, pin 2 is FPGA E3                                           | X1               |

| JP43   | Disconnects LCD data Bit1              | Pin 1 is MDL12 – Bit1, pin 2 is FPGA F5                                           | W1               |

| JP44   | Disconnects LCD data Bit0              | Pin 1 is MDL11 – Bit0, pin 2 is FPGA F6                                           | W1               |

| JP45   | Disconnects LCD control R/W            | Pin 1 is MDL5 – R/W, pin 2 is FPGA E5                                             | W3               |

| JP46   | Disconnects LCD control RS             | Pin 1 is MDL4 – RS, pin 2 is FPGA D1                                              | W3               |

| JP47   | Disconnects LCD control ENABLE         | Pin 1 is MDL6 – ENABLE, pin 2 is FPGA D3                                          | W3               |

| JP48   | – No such jumper –                     | _                                                                                 | _                |

| JP49   | Disconnects AV1                        | Pin 1 is TP48 (3.3 V), pin 2 is AV1_FLT (filtered to P6)                          | X3               |

| JP50   | Disconnects TP48 and TP49              | Allows ammeter to be connected between TP48 and TP49 to measure 3.3V_FPGA current | Х3               |

| JP51   | Disconnects AC1                        | Pin 1 is TP59, pin 2 is AC1_FLT (filtered to M7)                                  | X3               |

| JP52   | Disconnects AV2                        | Pin 1 is TP51 (1.5V), pin 2 is AV2_FLT (filtered to R5)                           | X4               |

| JP53   | Disconnects AV0 from potentiometer R50 | Pin 1 is center of R50 potentiometer, pin 2 is AV0_FLT (filtered to M6)           | X1               |

| JP54   | Disconnects 3.3V_FPGA from VPUMP       | Pin 1 is VPUMP (M12), pin 2 is 3.3V_FPGA                                          | X3               |

| JP55   | – No such jumper –                     | -                                                                                 | _                |

| JP56   | – No such jumper –                     | -                                                                                 | _                |

| JP57   | – No such jumper –                     | -                                                                                 | _                |

| JP58   | – No such jumper –                     | _                                                                                 | _                |

| JP59   | – No such jumper –                     | -                                                                                 | _                |

Table 2 • Jumper Function Listings and Silkscreen Grid Locations (continued)

| Jumper | Starter Kit Function                    | Notes                                                                             | Grid<br>Location |

|--------|-----------------------------------------|-----------------------------------------------------------------------------------|------------------|

| JP60   | Disconnects AG3 from multicolor LED     | Pin 1 is gate of p-channel MOSFET Q5, pin 2 is AG3 (M8)                           | Z3               |

| JP61   | – No such jumper –                      | -                                                                                 | _                |

| JP62   | Disconnects AT9                         | Pin 1 is base-collector of temperature diode, pin 2 is AT9 (R12)                  | Z3               |

| JP63   | Disconnects TP51 and TP52               | Allows ammeter to be connected between TP51 and TP52 to measure 1.5V_FPGA current | X4               |

| JP64   | Disconnects AC2                         | Pin 1 is TP53, pin 2 is AC2_FLT (filtered to L8)                                  | X4               |

| JP65   | Selects value of VCCPLB                 | Pin 1 is 1.5V_FPGA, pin 2 is VCCPLB (B15), pin 3 is GND                           | Х3               |

| JP66   | – No such jumper –                      | -                                                                                 | _                |

| JP67   | Selects value of VCCPLA                 | Pin 1 is 1.5V_FPGA, pin 2 is VCCPLA (B2), pin 3 is GND                            | Y1               |

| JP68   | Disconnects ARTN4                       | Pin 1 is emitter of temperature diode, pin 2 is ARTN4 (T12)                       | Z3               |

| JP69   | Disconnects AG6 from Blue               | Pin 1 is tricolor LED U1 pin 1 (blue), pin 2 is AG6 (N10)                         | Z3 and Z4        |

| JP70   | Disconnects AG7 from Orange             | Pin 1 is tricolor LED U1 pin 2 (orange), pin 2 is AG7 (M11)                       | Z4               |

| JP71   | Disconnects AG8 from Green              | Pin 1 is tricolor LED U1 pin 3 (green), pin 2 is AG8 (P12)                        | Z4               |

| JP72   | Shrouded header for 1.5 V fan           | Pin 1 is 1.5 V, pin 2 is drain of n-channel MOSFET Q6                             | Z4               |

| JP73   | Shrouded header for 3.3 V fan           | Pin 1 is 3.3 V, pin 2 is drain of n-channel MOSFET Q7                             | Z4               |

| JP74   | Shrouded header for user-supplied VAREF | Pin 1 is VAREF (T15), pin 2 is GND                                                | Z3               |

#### 4.4.4.2 Test Points

All test points on the board are fitted with small test loops. These test points are labeled on the silkscreen as TP1, TP2, etc. All such test points are also labeled on the silkscreen with the voltage expected to be observed at that test point. Voltages will be one of 5.0 V, 3.3 V, 1.5 V, or GND. When measuring the voltage at a test point with a digital voltage multimeter (DVM) the ground lead should be connected to a test point labeled GND and the voltage lead should be connected to the voltage to be tested. All voltage labels on the board are relative to a 0 V ground reference or GND.

#### 4.4.4.3 Prototyping Area

The prototyping area on the right side of the board has the bottom two rows of pins connected to ground, labeled as GND on the silkscreen and enclosed in a box, providing 16 holes connected to 0 V. The top two rows of pins are connected to various power supply rails internally in the board. They are grouped into rectangles of eight pins from left to right as follows: 3.3 V to the left and 1.5 V to the right, giving eight holes for each voltage level and six unconnected holes in the middle. All other holes in the prototyping area are unconnected and may be used to hold various discrete components, as needed for experimentation.

On the reverse side of the board there is an area labeled U5, which is a TQ100 pattern with some surrounding pads. This area may be used to solder a TQ100 part and then connect that part by adding

discrete wires to the pads and connecting them to desired pins on the board. The main purpose of this is to allow a previously programmed TQ100 device to be used to provide more system capability.

#### 4.4.4.4 Layering on Board

The complete board design and manufacturing files are included on the Starter Kit CD. The board file is in Allegro format, which will allow an end user to create the appropriate Gerbers and other board views as needed. Pictures of the layers of the board are included in Appendix: Signal Layers, page 92. For your convenience, high-resolution PDFs of these layers are also provided on the Starter Kit CD.

The board is fabricated with six copper layers. The layers are arranged as follows from top to bottom:

- Layer 1 Top Signal Layer

- · Layer 2 Ground Plane (split into separate digital ground and analog ground joined at a single point)

- Layer 3 Signal Layer 3

- Layer 4 Signal Layer 4

- Layer 5 Power Plane

- Layer 6 Bottom Signal Layer

See the diagrams in Appendix: Signal Layers, page 92.

## 5 Description of Test Design

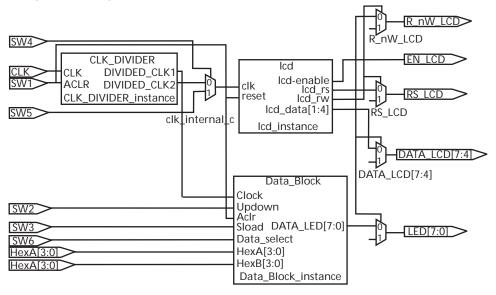

This is a description of the test design provided with the Fusion Starter Kit. The design contains a data generator block for LEDs, a clock divider, and an LCD block. A block diagram of the design is shown in the following figure.

Figure 3 • Design Block Diagram

The clock divider divides the 40 MHz oscillator clock and sends the divided clock to the LCD module and the counter. The data generator (Data\_Block) generates an 8-bit up/down counter and 8-bit flashing signal. The data generator output is displayed on the Fusion Evaluation Board LEDs. You can switch between the data using the SW6 signal. The counter has a synchronous load and an asynchronous clear.

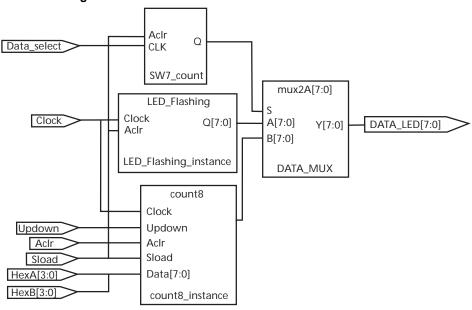

A block diagram of Data\_Block is shown in the following figure.

Figure 4 • Data Block Diagram

A message is generated and displayed on the Evaluation Board LCD. A state machine controls the LCD module.

The following table gives a list of active switches on the board and the functions they perform.

Table 3 • Switches

| Action                                  | Results                                                                                   |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------|--|

| Press SW1                               | Asynchronous clear for the whole design                                                   |  |

| Press SW2                               | Up/down control for the 8-bit counter. Press and hold SW2 for down count.                 |  |

| Press SW3                               | Synchronous load for the 8-bit counter. Press SW3 to load from the hex switches.          |  |

| Press SW4                               | Switches between manual clock (SW5) and 40 MHz oscillator clock.                          |  |

| Press SW5                               | Manual clock (very useful for simulation)                                                 |  |

| Press SW6                               | Select for Data_Block. Allows switching LED output between the counter and flashing data. |  |

| Change hex switch setting (U13 and U14) | Changes the loaded data for the 8-bit counter.                                            |  |

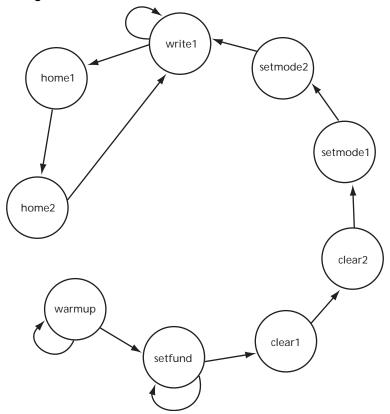

The state diagram is shown in the following figure.

Figure 5 • LCD State Diagram

## 6 Demo Design Tutorial

This section demonstrates two possible implementations of the tutorial design. The first example is based on the Microsemi CoreABC (a flexible and fully programmable AMBA (Advanced Microcontroller Bus Architecture) Peripheral Bus Controller) and CoreAl intellectual property (IP) cores, which are freely available through the Microsemi CoreConsole IP Deployment Platform (IDP). The second example (SmartDesign Demonstration, page 38) implements the design in RTL with component macros generated from the Microsemi SmartGen core generator.

## 6.1 CoreABC Design Description

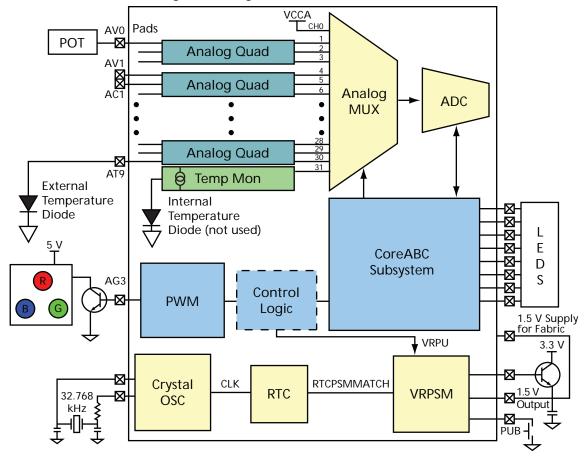

This demo design was created for the Microsemi Fusion Starter Kit. The 5 V, 3.3 V, and 1.5 V on-board power supplies are used in this design. Multiple analog input channels are utilized to sample the voltage and current provided to different loads. The design also samples the temperature through an on-board temperature sensor. Single-color LEDs are used to demonstrate the voltage threshold flags, and the tricolor LED is used to indicate different temperature levels with different colors.

Figure 6 • CoreABC Demo Design Block Diagram

## **6.1.1 Functionality Description**

The following peripherals and functionality are exercised in the demo design:

#### 6.1.1.1 Voltage Monitor

The demo design uses analog channel AV0 (pin M6) to monitor the voltage output from potentiometer R50. By changing the potentiometer, one can see the illumination status of LEDs D5–D8 change as the voltage output from the potentiometer changes. For details, refer to Table 4, page 16.

When the potentiometer is set to a different voltage level, the tricolor LED (U1) will blink at a different rate, from AV0 < 1.5 V, the slowest speed (1 Hz), to AV0 > 4.5 V, the fastest speed (always on).

#### 6.1.1.2 Current Monitor

The following AV and AC pairs are used to monitor the voltage and current of various power supplies. For more details, refer to CoreABC Design Implementation, page 18.

- AV2 and AC2—AFS600 1.5 V power supply

- AV4 and AC4—1.5 V power supply for external load on board

- AV5 and AC5—3.3 V power supply for external load on board

Additionally, AV1 and AC1 can be used to monitor the 3.3 V AFS600 power supply current, and AV3 and AC3 can be used to monitor 5 V power supply current to the tricolor LED (U1).

#### **6.1.1.3** Temperature Monitor

Channel AT9 is used in conjunction with an external temperature sensor to monitor the temperature of the Starter Kit environment. The tricolor LED (U1) will illuminate with different colors based on the temperature level detected.

- When temperature AT9 > 20°C, the LED illuminates blue.

- When temperature AT9 > 30°C, the LED illuminates green.

- When temperature AT9 > 40°C, the LED illuminates red.

- When temperature AT9 > 50°C, the LED illuminates white.

#### 6.1.1.4 Sleep Mode Demonstration

The Real-Time Counter (RTC) is used in this demo to generate a power-on instruction (RTCPSMMATCH) to the Fusion internal voltage regulator. A 2-bit counter built into the control logic of the design generates a power-off instruction (VRPU) so the voltage regulator can be turned off from the Fusion fabric. With the RTC and the counter, one can test the Sleep Mode and wake-up of the Fusion device.

#### 6.1.1.5 LCD

The LCD will show "Microsemi FUS1ON COREABC DEMO" after power-up.

The following table lists the different functionalities of the potentiometer, LEDs, and switches on the Fusion Starter Kit board for the demo design.

Table 4 • Functionality of the Potentiometer, LEDs and Switches on the Fusion Evaluation Board

| On-Board<br>Device | Jumper<br># | Pin<br># | Channel<br>Name | Functionality                                                                                                |

|--------------------|-------------|----------|-----------------|--------------------------------------------------------------------------------------------------------------|

| LED D5             | JP5         | B13      | AV0             | When AV0 > 1.5 V, D5 illuminated                                                                             |

| LED D6             | JP6         | A13      | AV0             | When AV0 > 2.5 V, D6 illuminated                                                                             |

| LED D7             | JP7         | B14      | AV0             | When AV0 > 3.3 V, D7 illuminated                                                                             |

| LED D8             | JP8         | A14      | AV0             | When AV0 > 4.5 V, D8 illuminated                                                                             |

| Potentiometer R50  | JP53        | M6       | AV0             | Turning the potentiometer drives AV0 with an analog voltage 0–5 V                                            |

| Switch SW7         | N/A         | R15      | N/A             | Connects to the PUB pad directly. When depressed, the PUB pad is grounded to power-up the voltage regulator. |

| Switch SW6         | JP16        | L15      | N/A             | Inverted and connects to the active-low RESET signals of the counters, CoreABC Subsystem, and PLL.           |

Table 4 • Functionality of the Potentiometer, LEDs and Switches on the Fusion Evaluation Board

| On-Board<br>Device | Jumper<br># | Pin<br># | Channel<br>Name | Functionality                                                                                                                      |

|--------------------|-------------|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| Switch SW5         | JP17        | K11      | N/A             | Connects to the clock input of the 2-bit counter generating the power-off instruction. When depressed, a clock pulse is generated. |

| Switch SW4         | JP14        | C10      | N/A             | When depressed, the AFS600 core current is displayed on the LCD.                                                                   |

| Switch SW3         | JP13        | C11      | N/A             | When depressed, the AFS600 core voltage is displayed on the LCD.                                                                   |

| Switch SW2         | JP12        | A11      | N/A             | When depressed, the current temperature is displayed on the LCD.                                                                   |

| Switch SW1         | JP11        | B11      | N/A             | When depressed, the potentiometer output voltage is displayed on the LCD.                                                          |

| Tricolor LED U1    | JP69        | AG6      | AT9             | When temperature AT9 > 20°C, the LED illuminates blue.                                                                             |

| Tricolor LED U1    | JP70        | AG7      | AT9             | When temperature AT9 > 30°C, the LED illuminates green.                                                                            |

| Tricolor LED U1    | JP71        | AG8      | AT9             | When temperature AT9 > 40°C, the LED illuminates red.                                                                              |

#### 6.1.2 Demonstration Instructions

There are several special jumpers and pins on the Starter Kit that need attention. Select the appropriate jumper settings for the user design. The following table lists the basic functions of the jumpers.

Table 5 • Special Jumper/Pin Settings and Their Functionality

| JP #/Pin # | Function | JP Setting | Value                               |  |

|------------|----------|------------|-------------------------------------|--|

| JP25       | VMV1     | 1–2        | 1.5 V                               |  |

|            |          | 2–3        | 3.3 V <sup>1</sup>                  |  |

| JP26       | VMV0     | 1–2        | 1.5 V                               |  |

|            |          | 2–3        | 3.3 V <sup>1</sup>                  |  |

| JP27       | VJTAG    | 1–2        | 1.5 V                               |  |

|            |          | 2–3        | 3.3 V <sup>1</sup>                  |  |

| JP28       | PTEM     | 1–2        | 1.5 V_INT <sup>1</sup>              |  |

|            |          | 2–3        | 1.5 V_EXT                           |  |

| Pin M15    | TRSTB    | Floating   | JTAG operations                     |  |

|            |          | Grounded   | Allows voltage regulator power-down |  |

<sup>1.</sup> Required for the Fusion Starter Kit Demo Design.

#### 6.1.2.1 Exercising the Demo Design

To exercise the demo design:

- 1. Power on the Starter Kit using the power switch.

- 2. Turn on the fabric by pushing SW7 (this is only required if the TRSTB pin is grounded).

- Test the voltage monitor by turning the potentiometer to observe whether D5–D8 turn on and off and whether the tricolor LED blinks at different rates.

- 4. Turn on Sleep Mode by turning off the fabric:

- Press SW6 once to reset the system.

- Press SW5 four times to generate a power-down signal.

- 5. Wake up the system via the RTC (at a preset time), or by pushing SW7.

- Test the temperature indicator by warming the temperature diode (Q8) with a finger tip and then checking that the tricolor LED changes from blue to green to red (depending upon the initial room temperature, it may already be blue).

- 7. Press SW1 to show the potentiometer output voltage on the LCD.

- 8. Press SW2 to show the temperature sensed by Q8 on the LCD.

- 9. Press SW3 to show the AFS600 core voltage on the LCD.

- 10. Press SW4 to show the AFS600 core current on the LCD.

### 6.1.3 CoreABC Design Implementation

To implement the above functionalities, an integrated CoreConsole and Microsemi Libero Integrated Design Environment (IDE) project will need to be created with the configuration outlined in this chapter. For more details on creating the integrated CoreConsole and Microsemi Libero IDE project, see the CoreConsole User Guide and the Libero IDE User Guide.

# 6.1.3.1 Step 1 – Create an Integrated CoreConsole and Microsemi Libero IDE Project

Create a new Microsemi Libero IDE project by selecting **Fusion AFS600-FG256** and using CoreConsole and the SmartGen Macro Builder to generate the different functional macros; then instantiate them in the top-level design.

Figure 7 • Microsemi Libero IDE New Project Wizard Device Selection

#### 6.1.3.2 Step 2 – Create a CoreConsole Project within Microsemi Libero IDE

From the Microsemi Libero IDE Project Flow, click the **CoreConsole Design Entry Tools** button to generate a new CoreConsole component with the name **AFSEVALBRD1**, as shown in the following figure. The end result of the CoreConsole component will yield the CoreABC Subsystem shown in Figure 6, page 15.

Figure 8 • CoreConsole Component Creation Wizard

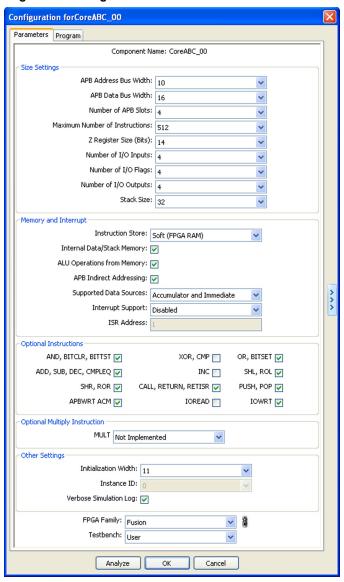

#### 6.1.3.2.1 Step 2.1 – CoreABC Instantiation and Configuration

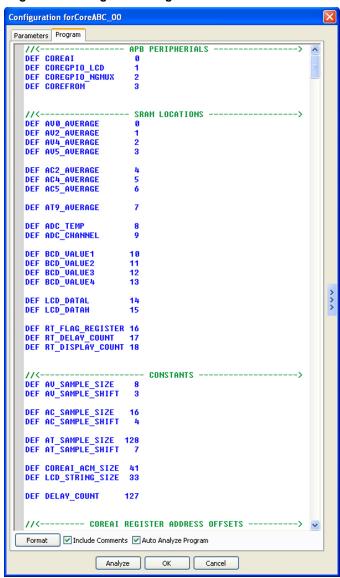

From CoreConsole, instantiate and configure an instance of CoreABC through the **Parameters** tab shown in Table 6, page 19, Figure 9, page 21, and Figure 10, page 22. From the **Program** tab, copy and paste the source code provided in the *CoreABC\_Source.txt* file included with the sample Libero IDE projects. CoreABC is the central controller in this application and is responsible for interfacing to the Analog Block (AB) and processing the results, as well as interfacing to the LCD.

Table 6 • CoreABC Configuration Parameters

| Configuration Paramete | Value                             |                           |

|------------------------|-----------------------------------|---------------------------|

| Size Settings          | APB Address Bus Width             | 10                        |

|                        | APB Data Bus Width                | 16                        |

|                        | Number of APB Slots               | 4                         |

|                        | Maximum Number of<br>Instructions | 512                       |

|                        | Z Register Size (bits)            | 14                        |

|                        | Number of I/O Inputs              | 4                         |

|                        | Number of I/O Flags               | 4                         |

|                        | Number of I/O Outputs             | 4                         |

|                        | Stack Size                        | 32                        |

| Memory and Interrupt   | Instruction Store                 | Soft (FPGA RAM)           |

|                        | Internal Data/Stack Memory        | Enabled                   |

|                        | ALU Operations from Memory        | Enabled                   |

|                        | APB Indirect Addressing           | Enabled                   |

|                        | Supported Data Sources            | Accumulator and Immediate |

|                        | Interrupt Support                 | Disabled                  |

|                        | ISR Address                       | N/A                       |

Table 6 • CoreABC Configuration Parameters (continued)

| Configuration Parameter I          | Value                  |                 |

|------------------------------------|------------------------|-----------------|

| Optional Instructions              | AND, BITCLR, BITTST    | Enabled         |

|                                    | XOR, CMP               | Disabled        |

|                                    | OR, BITSET             | Enabled         |

|                                    | ADD, SUB, DEC, CMPLEQ  | Enabled         |

|                                    | INC                    | Disabled        |

|                                    | SHL, ROL               | Enabled         |

|                                    | SHR, ROR               | Enabled         |

|                                    | CALL, RETURN, RETISR   | Enabled         |

|                                    | PUSH, POP              | Enabled         |

|                                    | APBWRT ACM             | Enabled         |

|                                    | IOREAD                 | Disabled        |

|                                    | IOWRT                  | Enabled         |

| Optional Multiply Instruction MULT |                        | Not Implemented |

| Other Settings                     | Initialization Width   | 11              |

|                                    | Instance ID            | N/A             |

|                                    | Verbose Simulation Log | Enabled         |

| FPGA Family                        |                        | Fusion          |

| Testbench                          |                        | User            |

Figure 9 • CoreABC Configuration Dialog Box—Parameters Tab

Figure 10 • CoreABC Configuration Dialog Box—Program Tab

#### 6.1.3.2.2 Step 2.2 – CoreAl Instantiation and Configuration

From CoreConsole, instantiate and configure an instance of CoreAl as shown in Table 6, page 15 and Figure 11, page 25. CoreAl allows for the simple control of the Fusion analog peripherals via the industry-standard AMBA Advanced Peripheral Bus (APB) interface.

Table 7 • CoreAl Configuration Parameters

| Configuration Parameter Name | Value    |

|------------------------------|----------|

| ACM Clock Divider            | PCLK/4   |

| Internal Temperature Monitor | Disabled |

| Interrupt Out Line           | Disabled |

| Interrupt Output Polarity    | N/A      |

Table 7 • CoreAl Configuration Parameters (continued)

| Configuration Parameter Name |            | Value                        |  |

|------------------------------|------------|------------------------------|--|

| Quad #0                      | AV0 Input  | 0 V to 8 V Analog Input      |  |

|                              | AC0 Input  | Disabled                     |  |

|                              | AT0 Input  | Disabled                     |  |

|                              | AG0 Output | Disabled                     |  |

| Quad #1                      | AV1 Input  | Disabled                     |  |

|                              | AC1 Input  | Disabled                     |  |

|                              | AT1 Input  | Disabled                     |  |

|                              | AG1 Output | Disabled                     |  |

| Quad #2                      | AV2 Input  | 0 V to 2 V Analog Input      |  |

|                              | AC2 Input  | Current Monitor              |  |

|                              | AT2 Input  | Disabled                     |  |

|                              | AG2 Output | Disabled                     |  |

| Quad #3                      | AV3 Input  | Disabled                     |  |

|                              | AC3 Input  | Disabled                     |  |

|                              | AT3 Input  | Disabled                     |  |

|                              | AG3 Output | Hardware Driven 25 mA Source |  |

| Quad #4                      | AV4 Input  | 0 V to 2 V Analog Input      |  |

|                              | AC4 Input  | Current Monitor              |  |

|                              | AT4 Input  | Disabled                     |  |

|                              | AG4 Output | Software Driven 25 mA Source |  |

| Quad #5                      | AV5 Input  | 0 V to 4 V Analog Input      |  |

|                              | AC5 Input  | Current Monitor              |  |

|                              | AT5 Input  | Disabled                     |  |

|                              | AG5 Output | Software Driven 25 mA Source |  |

| Quad #6                      | AV6 Input  | Disabled                     |  |

|                              | AC6 Input  | Disabled                     |  |

|                              | AT6 Input  | Disabled                     |  |

|                              | AG6 Output | Software Driven 25 mA Source |  |

| Quad #7                      | AV7 Input  | Disabled                     |  |

|                              | AC7 Input  | Disabled                     |  |

|                              | AT7 Input  | Disabled                     |  |

|                              | AG7 Output | Software Driven 25 mA Source |  |

| Quad #8                      | AV8 Input  | Disabled                     |  |

|                              | AC8 Input  | Disabled                     |  |

|                              | AT8 Input  | Disabled                     |  |

|                              | AG8 Output | Software Driven 25 mA Source |  |

Table 7 • CoreAl Configuration Parameters (continued)

| Configuration Parameter Name |                     | Value                                   |  |