### Combined IEEE1588 ToP & Synchronous Ethernet Technology

# **PRODUCT** PREVIEW

Zarlinks Timing over Packet (ToP) products allow carriers to confidently support time-critical voice, video and data services over packet networks.

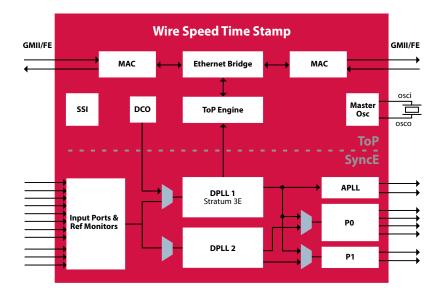

ToP products are a powerful hybrid solution for timing card and line card applications. The single-chip device incorporates an extremely low-jitter frequency synthesizer, capable of generating all the frequencies required for Synchronous Ethernet operation, together with Zarlink's patent-pending ToP technology based on the industry-standard IEEE1588 Precision Time Protocol (PTP). This allows the device to function as a fully-featured digital phase locked loop PLL, and also support the distribution of time, phase and frequency across both Layer 2 and Layer 3 networks using Synchronous Ethernet and IEEE1588 protocols, either alone or in combination.

Zarlink's portfolio of footprint-compatible ToP devices offering the full range of features required for timing and synchronization across the packet network. With Zarlink's ToP technology, carriers can lower costs by migrating to a truly converged network supporting time-critical services.

| Timing over Packet Products |                     |

|-----------------------------|---------------------|

| Timing Card Devices         | Line Card Devices   |

| ZL30310GKG S3E/ToP          | ZL30314GKG SDH/ToP  |

| ZL30312GKG SONET/ToP        | ZL30316GKG S4E/ToP  |

|                             | ZL30320GKG DPLL/ToP |

#### Applications

- IEEE 1588 and Synchronous Ethernet timing

- GSM and UMTS air interface synchronization over a packet network

- Circuit Emulation Services over Packets

- IP-PBX and VoIP gateways

- Video conferencing

- Broadband video distribution

#### Revolutionary Technology for Packet Network Synchronization

- Recovers and transmits network synchronization over Ethernet, IP and MPLS networks

- Simultaneously supports both the IEEE1588 and Synchronous Ethernet industry standard timing protocols

- Capable of server, client and repeater operation

- Integrates two separate digital phase locked loops, with hitless switching between packet and electrical clock references

- Primary DPLL meets Stratum 3E quality

- Targeted for synchronization distribution to better than ITU-T G.8261, G.823, G.824 and ANSI T1.101 synchronization interface standards

- Average frequency accuracy better than ±10 ppb

- Aligns 1 PPS with targeted accuracy better than ±1 μs

- Recovers clocks from two independent servers, with hitless switching between packet streams for redundancy

- Supports holdover if the server stream is lost

- Accepts eight input references, and up to three associated low frequency alignment or framing pulses

- Generates up to four separate output clocks at frequencies between 8 KHz and 100 MHz

- Generates two separate Synchronous Ethernet clocks to drive industry standard Ethernet PHY devices at either 25 MHz or 125 MHz

- Fully configurable solution, enabling performance to be tailored to application/network requirements

- Two independently configurable MAC interfaces, supporting MII, RMII, GMII and TBI standards

- Wire-speed Ethernet Bridge pass through function between the MAC interfaces

- Synchronous serial control interface

- Full demonstration & evaluation platform available

# Combined IEEE1588 ToP & Synchronous Ethernet Technology

### APPLICATION

Carriers rolling out packet-based equipment face a major stumbling block, because many services have critical time dependencies that cannot be met by a "best-effort" infrastructure. For example, TDM services over packet networks using CESoP and wireless base stations using a packet infrastructure require precise synchronization. As a result, carriers rely on costly GPS receivers and/or expensive oscillators, among other methods, to ensure accurate synchronization over packet networks.

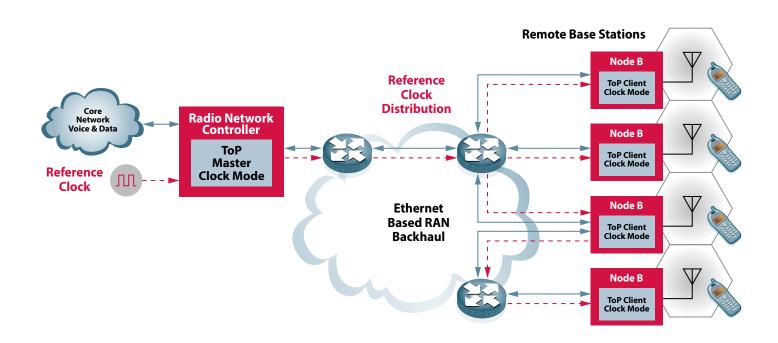

In a wireless infrastructure, as illustrated below, there is a drive to use Ethernet-based backhaul solutions to help reduce operating expenses caused by increasing traffic demands and high backhaul costs over T1/E1 ports. However, ensuring synchronization remains a challenge. By employing Zarlink's ToP technology, carriers can distribute synchronization from the RNC (radio network controller) directly to the remote base stations over an Ethernet network.

ToP functions as a timing master (timing server) and distributes a stable reference clock from the RNC to remote base stations (timing clients) across the packet network. The ToP device also functions as a timing slave by extracting timing from the packet network and creating an output clock traceable to the timing master clock. In repeater mode, the ToP chip extracts timing information from the packet network and creates an output clock that is distributed to other slaves across the network.

Zarlink's ToP technology recovers up to two independent master clocks that are locked to independent sources. Selection of the appropriate source is under management control. The ToP algorithm continuously tracks the frequency offset and phase drift of the Client clock to the Master source clock and provides automatic correction, hence achieving the required MTIE masks.

The device is highly configurable to ensure that generated clocks meet international standards in the presence of network jitter, PDV (Packet Delay Variation), routing changes and even network outages. The ToP device maintains average frequency accuracy better than +/-15 ppb with a Stratum 3 quality TXCO system clock. In the event of packet network failure or severe network congestion, the ToP chip will put the recovered clocks into holdover mode until the flow of timing packets is properly restored.

www.ZARLINK.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries is believed to be reliable. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice ZANUME 7. and the Zarlink lange are trademarked for facilly to project during in this publication.

ZARLINK, ZL, and the Zarlink logo are trademarks of Zarlink Semiconductor Inc.