# MT90528 API Specification

Part Number: MT90528

Revision Number: 1.2

Issue Date: January 2004

PURCHASE OF THIS PRODUCT DOES NOT GRANT THE PURCHASER ANY RIGHTS UNDER PATENT NO. 5,260,978. USE OF THIS PRODUCT OR ITS RE-SALE AS A COMPONENT OF ANOTHER PRODUCT MAY REQUIRE A LICENSE UNDER THE PATENT WHICH IS AVAILABLE FROM TELCORDIA TECHNOLOGIES, INC., 445 SOUTH STREET, MORRISTOWN, NEW JERSEY 07960.

ZARLINK ASSUMES NO RESPONSIBILITY OR LIABILITY THAT MAY RESULT FROM ITS CUSTOMERS' USE OF ZARLINK PRODUCTS WITH RESPECT TO THIS PATENT. IN PARTICULAR, ZARLINK'S PATENT INDEMNITY IN ITS TERMS AND CONDITIONS OF SALES WHICH ARE SET OUT IN ITS SALES ACKNOWLEDGEMENTS AND INVOICES DOES NOT APPLY TO THIS PATENT.

# **Table of Contents**

|       | verview                                                 |                   |

|-------|---------------------------------------------------------|-------------------|

|       | 1 Software Revision                                     |                   |

| 1     | 2 System Architecture                                   | 6                 |

| 2.0 A | PI Function Descriptions                                | 9                 |

|       | 1 Initialization Functions                              |                   |

|       | 2.1.1 Mt90528InitializeApi                              |                   |

|       | 2.1.2 Mt90528ShutDownApi                                |                   |

| 2     | .2 ATM Functions                                        | . 11              |

| _     | 2.2.1 Mt90528ConfigureDeviceForUdt                      | . 12              |

|       | 2.2.2 Mt90528ConfigureDeviceForSdt                      | . 15              |

|       | 2.2.3 Mt90528ConfigureDeviceForUdtAndSdt                | . 17              |

|       | 2.2.4 Mt90528ConfigureDataRxsarModule.                  |                   |

|       | 2.2.5 Mt90528ReadDataRxsarBuffer                        |                   |

|       | 2.2.6 Mt90528EnableDataRxsar.                           |                   |

|       | 2.2.7 Mt90528DisableDataRxsar                           | . 22              |

|       | 2.2.8 Mt90528ConfigureDataTxsarModule.                  | . 23              |

|       | 2.2.9 Mt90528InitializeDataTxsarWritePointer            |                   |

|       | 2.2.10 Mt90528WriteDataTxsarBuffer.                     |                   |

|       | 2.2.11 Mt90528EnableDataTxsar                           |                   |

|       | 2.2.12 Mt90528DisableDataTxsar.                         |                   |

|       | 2.2.13 Mt90528ConfigureTdmPortForUdt.                   |                   |

|       | 2.2.14 Mt90528DeprogramTdmPortForUdt                    |                   |

|       | 2.2.15 Mt90528ConfigureTdmPortForSdt.                   |                   |

|       | 2.2.16 Mt90528DeprogramTdmPortForSdt.                   |                   |

|       | 2.2.17 Mt90528SetTdmPortLinkType                        | . 33              |

|       | 2.2.18 Mt90528TurnOnUtopiaInterfaceLoopback             | . 34              |

|       | 2.2.19 Mt90528TurnOffUtopiaInterfaceLoopback.           |                   |

|       | 2.2.20 Mt90528ConfigureTdmPortForLowLatencyLoopback     |                   |

|       | 2.2.21 Mt90528DeprogramTdmPortForLowLatencyLoopback     |                   |

|       | 2.2.22 Mt90528ConfigureTdmPortForCircularBufferLoopback |                   |

|       | 2.2.23 Mt90528DeprogramTdmPortForCircularBufferLoopback | . 39              |

|       | 2.2.24 Mt90528EnableTxTdmForUdt                         | . 40              |

|       | 2.2.25 Mt90528DisableTxTdmForUdt                        | . 41              |

|       | 2.2.26 Mt90528EnableTxVcForSdt                          |                   |

|       | 2.2.27 Mt90528DisableTxVcForSdt                         |                   |

|       | 2.2.28 Mt90528OpenTxVcForUdt                            |                   |

|       | 2.2.29 Mt90528CloseTxVcForUdt.                          |                   |

|       | 2.2.30 Mt90528OpenRxVcForUdt                            | . 45              |

|       | 2.2.31 Mt90528CloseRxVcForUdt                           |                   |

|       | 2.2.32 Mt90528OpenTxVcForSdt                            | . 48              |

|       | 2.2.33 Mt90528CloseTxVcForSdt                           |                   |

|       | 2.2.34 Mt90528OpenRxVcForSdt                            |                   |

|       | 2.2.35 Mt90528CloseRxVcForSdt                           | . 54              |

|       | 2.2.36 Mt90528EnableTxsar                               |                   |

|       | 2.2.37 Mt90528OpenRxDataVc                              | . <mark>56</mark> |

|       | 2.2.38 Mt90528CloseRxDataVc                             | . 56              |

|       | 2.2.39 Mt90528UpdateCutVcPeriod                         | . 57              |

|       | 2.2.40 Mt90528UpdateCellDelayVariation                  | . 58              |

|       | 2.2.41 Mt90528UpdateReplayNSilence                      |                   |

| 2     | 3 I/O Functions                                         | . 61              |

|       | 2.3.1 Mt90528WriteExternalMemory                        | . 61              |

|       | 2.3.2 Mt90528WriteNoVerifyExternalMemory                |                   |

|       |                                                         |                   |

# **Table of Contents**

| 2.3.3 Mt90528ReadExternalMemory                                     |       |

|---------------------------------------------------------------------|-------|

| 2.3.4 Mt90528WriteInternalMemory                                    |       |

| 2.3.5 Mt90528WriteNoVerifyInternalMemory                            | 64    |

| 2.3.6 Mt90528ReadInternalMemory                                     | 65    |

| 2.3.7 Mt90528WriteRegister                                          | 65    |

| 2.3.8 Mt90528ReadRegister                                           |       |

| 2.4 Interrupt Service Handler                                       | 67    |

| 2.4.1 Mt90528lsrHandler                                             |       |

| 2.4.2 Mt90528lsrHandlerWith2ndThresholds                            |       |

| 2.4.3 Mt90528EnableDisableInterrupt.                                |       |

| 2.5 MIB and Performance Management Statistics and Status            | 73    |

| 2.5.1 Statistics Functions                                          |       |

| 2.5.1.1 Mt90528GetDeviceStatistics                                  |       |

| 2.5.1.2 Mt90528GetTdmPortStatistics                                 |       |

| 2.5.1.3 Mt90528GetCbrVcStatistics                                   |       |

| 2.5.1.4 Mt90528GetCbrVcStatisticsWithAppThresholds                  |       |

| 2.5.1.5 Mt90528EnableDisableCbrVcStatisticsCollection               |       |

| 2.5.1.6 Mt90528GetCbrVcStatIndex.                                   |       |

|                                                                     |       |

| 2.5.1.7 Mt90528SetMibThresholds.                                    |       |

| 2.5.1.8 Mt90528SetMibThresholdsWithAppThresholds                    | 79    |

| 2.5.1.9 Mt90528SetMibCounters32                                     |       |

| 2.5.1.10 Mt90528ReadDeviceMibCounters                               |       |

| 2.5.1.11 Mt90528LoadDeviceMibCounters                               |       |

| 2.5.1.12 Mt90528ReadUdtRxsarCsVcArrival                             |       |

| 2.5.1.13 Mt90528ReadSdtRxsarCsVcArrival                             |       |

| 2.5.1.14 Mt90528ClearUdtRxsarCsVcArrival                            |       |

| 2.5.1.15 Mt90528ClearSdtRxsarCsVcArrival                            |       |

| 2.5.1.16 Mt90528ScanForCellLossTimeoutOnVcs                         |       |

| 2.5.2 Status Functions                                              |       |

| 2.5.2.1 Mt90528GetNextTdmPortStatusIndex                            |       |

| 2.5.2.2 Mt90528GetNextCbrVcStatusIndex                              |       |

| 2.5.2.3 Mt90528GetNextCbrVcCellLossStatusIndex                      | 87    |

| 2.5.3 Secondary Threshold and Counter Functions                     |       |

| 2.5.3.1 Mt90528InitializeThresholdTable                             |       |

| 2.5.3.2 Mt90528AddVcToCbrVcThresholdTable                           |       |

| 2.5.3.3 Mt90528RemoveVcFromCbrVcThresholdTable.                     |       |

| 2.5.3.4 Mt90528GetCbrVcThresholdIndex                               |       |

| 2.5.3.5 Mt90528SetAppThresholds                                     |       |

| 2.5.3.6 Mt90528SetAppCounters32                                     |       |

| 2.5.3.7 Mt90528UpdateAppCounters32                                  |       |

| 2.5.3.8 Mt90528GetCbrVcAppStatistics                                |       |

| 2.5.3.9 Mt90528EnableDisableCbrVcAppStatisticsCollection            |       |

| 2.5.4 Application Examples using Statistics Counters and Thresholds |       |

| 2.5.4.1 MIB statistics only with no Thresholds set                  |       |

| 2.5.4.2 MIB statistics only with MIB Thresholds set                 |       |

| 2.5.4.3 MIB and APP statistics with no Thresholds set               |       |

| 2.5.4.4 MIB and APP statistics with MIB and APP Thresholds set      |       |

| 3.0 Constants                                                       |       |

| 4.0 Configuration Structures                                        | . 110 |

| 4.1 Structure s vc                                                  |       |

| 4.2 Structure s_device_common_params                                |       |

| 4.3 Structure s_device_udt_specific_params                          |       |

|                                                                     |       |

# **Table of Contents**

|     | 4.4 Structure s_device_sdt_specific_params                | 11 | 1  |

|-----|-----------------------------------------------------------|----|----|

|     | 4.5 Structure s_device_udt_params                         | 11 | 2  |

|     | 4.6 Structure s_device_sdt_params                         | 11 | 2  |

|     | 4.7 Structure s_device_udt_and_sdt_params                 | 11 | 3  |

|     | 4.8 Structure s_data_cell_buffer_params                   | 11 | 3  |

|     | 4.9 Structure s_data_tx_sar_enable_params                 | 11 | 3  |

|     | 4.10 Structure s_data_rx_sar_enable_params                | 11 | 3  |

|     | 4.11 Structure s_tdm_port_common_params                   | 11 | 4  |

|     | 4.12 Structure s_tdm_port_udt_specific_params             | 11 | 4  |

|     | 4.13 Structure s_tdm_port_sdt_specific_params             | 11 | 5  |

|     | 4.14 Structure s_tdm_port_udt_params                      | 11 | 6  |

|     | 4.15 Structure s_tdm_port_sdt_params                      | 11 | 6  |

|     | 4.16 Structure s_tdm_loopback_params                      | 11 | 6  |

|     | 4.17 Structure s_atm_channel                              | 11 | 6  |

|     | 4.18 Structure s_atm_channels                             | 11 | 7  |

|     | 4.19 Structure s_atm_cell_header_params                   | 11 | 7  |

|     | 4.20 Structure s_tx_vc_udt_params                         | 11 | 7  |

|     | 4.21 Structure s_tx_vc_sdt_params                         | 11 | 7  |

|     | 4.22 Structure s_rx_vc_udt_params                         |    |    |

|     | 4.23 Structure s_rx_vc_sdt_params                         | 11 | 8  |

|     | 4.24 Structure s memory chunk                             |    |    |

|     | 4.25 Structure a_internal_memory_chunks                   |    |    |

|     | 4.26 Structure a_external_memory_chunks                   |    |    |

| 5.0 | Statistics, Status and Threshold Structures               | 12 | 20 |

| •   | 5.1 Structure s mt90528 device stats entry                |    |    |

|     | 5.2 Structure s_mt90528_tdm_port_stats_entry              |    |    |

|     | 5.3 Structure s_mt90528_cbr_vc_stats_entry.               |    |    |

|     | 5.4 Structure s_mt90528_statistics                        | 12 | 23 |

|     | 5.5 Structure s stats flags                               |    |    |

|     | 5.6 Structure s_hw_udt                                    |    |    |

|     | 5.7 Structure s hw sdt                                    |    |    |

|     | 5.8 Structure s hw dev                                    |    |    |

|     | 5.9 Structure s_hw_load                                   |    |    |

|     | 5.10 Structure s stats 32                                 |    |    |

|     | 5.11 Structure s stats params                             |    |    |

|     | 5.12 Structure s_mt90528_device_status_entry              |    |    |

|     | 5.13 Structure s_mt90528_tdm_port_status_entry            |    |    |

|     | 5.14 Structure s_mt90528_cbr_vc_status_entry              | 12 | 27 |

|     | 5.15 Structure s mt90528 status                           |    |    |

|     | 5.16 Structure s_mt90528_cbr_vc_cell_loss_status_entry    |    |    |

|     | 5.17 Structure s_mt90528_cbr_vc_cell_loss_status          |    |    |

|     | 5.18 Structure s_mt90528_cbr_vc_statistic_threshold_entry | 13 | 31 |

|     | 5.19 Structure s_mt90528_threshold                        | 13 | 32 |

| e 0 | Glossary                                                  |    |    |

| J.U | O103301 y                                                 | 13 | J  |

# 1.0 Overview

This document is intended as a reference guide of API calls and structures for the MT90528 family of AAL1 SAR devices.

# 1.1 Software Revision

The MT90528 software API referred to in this document is at release 3.0

# 1.2 System Architecture

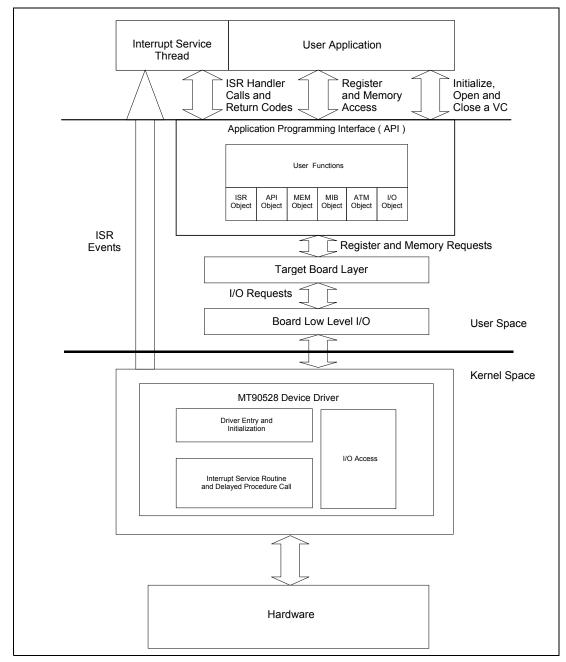

There are six components to the MT90528 API: API, ATM, ISR, MIB, MEM and I/O. The API component contains the generic API routines not specifically related to ATM, ISR, MIB, MEM or I/O which includes the interfaces for initializing and shutting down the API. The ATM part consists of interfaces for configuring the UTOPIA interface and TDM ports and opening and closing virtual channels. For release 3.x & up of the API, all functions are in the context of UDT or SDT modes. The ISR part consists of interfaces which allow for handling of the various categories of device interrupts. The MIB part consists of interfaces that handle statistics and thresholds. The MEM part is internal to the API and these interfaces are used by the ATM component. The I/O part consists of routines for reading and writing device registers and internal and external memory. Figure 1 shows the system architecture indicating the API and the supporting low-level software:

Figure 1 - System Overview

| Module                                 | Description                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| User Application                       | The user application code has to be developed by the user of the API. Example code has been provided on how to initialize the MT90528 device, how to open a VC or multiple VCs, how to close a VC, how to spawn an interrupt service thread and how to shut down the device.                                                                                  |

| Interrupt Service Thread               | The interrupt service thread code has to be developed by the user of the API. Example code has been provided on how to create plus wait for an interrupt event and how to service the interrupt events. Some of this code may need to be moved down to the device driver interrupt service routine due to performance issues for real time operating systems. |

| User Functions                         | These are the API calls that the user application is using. This module is the external interface of the API.                                                                                                                                                                                                                                                 |

| API Object                             | This module in the API initializes the MT90528 device to allow writing to and reading from registers and memory. Specific interrupts are enabled. The module also shuts down the MT90528 device (closes the device driver).                                                                                                                                   |

| ATM Object                             | This module in the API initializes the device and TDM ports. The module also opens and closes CBR and Data VCs.                                                                                                                                                                                                                                               |

| MIB Object                             | This module deals with the statistics structures and MIB counters and flags.                                                                                                                                                                                                                                                                                  |

| MEM Object                             | This module is internal to the API and is used to manage internal and external memory.                                                                                                                                                                                                                                                                        |

| ISR Object                             | This module in the API has routines that handle the MT90528 device interrupts for each of the functional modules on the device (e.g. TXSAR, SDT RXSAR)                                                                                                                                                                                                        |

| I/O Object                             | This module in the API handles the register and memory input/output accesses on the MT90528 device.                                                                                                                                                                                                                                                           |

| Target Board Layer                     | This layer handles the input and output accesses for the MT90528 device and the board on which the MT90528 device is used. All of the board-specific definitions reside in this layer.                                                                                                                                                                        |

| Board Low Level I/O                    | This layer handles the board address-specific input and output accesses to and from any customer device driver. It also has utility routines for opening and closing a device driver, creating and closing interrupt events on the device driver and acquiring a device driver handle/descriptor.                                                             |

| Device Driver Entry and Initialization | The device driver is initialized to reset the board and MT90528 device. The board and MT90528 device interrupts are disabled. The device driver interrupt service routine is enabled.                                                                                                                                                                         |

| Device Driver I/O Access               | The device driver input/output access module provides reading from and writing to the hardware on the board and MT90528 device either using port I/O or memory I/O ISA access.                                                                                                                                                                                |

**Table 1 - System Overview Module Description**

| Module                                     | Description                                                                                                                                                                                                                   |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Driver Interrupt<br>Service Routine | The device driver interrupt service routine services the board and MT90528 device hardware interrupts, checking for valid MT90528 device interrupts and initiating an interrupt event to the user's interrupt service thread. |

| Hardware                                   | Hardware accesses to the board and MT90528 device.                                                                                                                                                                            |

**Table 1 - System Overview Module Description**

# 2.0 API Function Descriptions

# 2.1 Initialization Functions

Initialization functions prepare the chip for operation.

Mt90528InitializeApi is called from the user application main program before any other calls to the API are made.

Mt90528ShutDownApi is called from the main program to clean up the API when the application is shut down.

Mt90528EnableDisableInterrupt is called from Mt90528InitializeApi to initially enable all categories of interrupts on the device. Mt90528EnableDisableInterrupt can be called from the user application to enable/disable specific categories of interrupts.

**NOTE**: the application has to define variables using the structures s\_mt90528\_statistics, a\_internal\_memory\_chunks and a\_external\_memory\_chunks in order to use the following functions. These common variables are also used by the ATM, ISR and MIB functions.

# 2.1.1 Mt90528InitializeApi

# **Prototype**

```

USHORT Mt90528InitializeApi(

UINT Device,

s_mt90528_statistics * pStatistics,

s_memory_chunk * pIntChunkArray,

s_memory_chunk * pExtChunkArray

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES

pStatistics pointer to MIB statistics structure.

See 5.4, "Structure s mt90528 statistics".

plntChunkArray pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure s memory chunk".

pExtChunkArray pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure s\_memory\_chunk".

#### Return values

MT90528\_API\_NO\_ERRORAPI is initializedMT90528\_API\_INIT\_WRITE\_ERRORfailure writing to the chipMT90528\_API\_INIT\_READ\_ERRORfailure reading from the chipMT90528\_API\_INIT\_IRQ\_ERRORfailure enabling/disabling device interruptsMT90528\_API\_INIT\_MEM\_MAN\_ERRORfailure to initialize the memory manager

#### Description

This routine

- · initializes the MIB statistics structures

- · resets each device on the board

- queries the device revision register and updates the DeviceRev field in the device statistics structure

- initializes the Memory Arbiter Configuration Register with the board specific memory configuration and memory type information for each device on the board

- clears the device internal and external memory (memory clearing takes time)

- · disables all PLLs

- enables device specific module interrupts (not TDM port or VC interrupts)

- · enables all categories of main interrupts

- initializes the memory manager using the passed in pointers to user created memory chunk arrays in CPU memory (see mem90528.h for memory chunk array structures to define)

# **Source Files**

api90528.h, api90528.c

# 2.1.2 Mt90528ShutDownApi

# **Prototype**

# **Parameters**

pStatistics pointer to MIB statistics structure.

See 5.4, "Structure s\_mt90528 statistics".

plntChunkArray pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure's memory chunk".

pExtChunkArraypointer passed by caller of memory manager external chunk array.

See 4.24, "Structure s\_memory\_chunk".

# Return values

No return values.

# Description

The routine

- · cleans up after the memory manager

- · cleans up the MIB statistics structures

#### Source File

api90528.h, api90528.c

# 2.2 ATM Functions

ATM routines are used to configure the UTOPIA interface and TDM ports and to open and close TX and RX virtual channels. The ATM module also contains routines which support the Data RX\_SAR and Data TX\_SAR functions of the chip. Routines are available for programming the TDM port and UTOPIA interface loopback modes.

For debugging and board testing the following routines allow the various loopback modes to be turned on and off:

- 1. Mt90528TurnOnUtopiaInterfaceLoopback, Mt90528TurnOffUtopiaInterfaceLoopback

- Mt90528ConfigureTdmPortForLowLatencyLoopback, Mt90528DeprogramTdmPortForLowLatencyLoopback

- 3. Mt90528ConfigureTdmPortForCircularBufferLoopback, Mt90528DeprogramTdmPortForCircularBufferLoopback

For basic ATM cell transmission and reception, the order in which the user application should call the routines is:

- Mt90528ConfigureDeviceForUdt or Mt90528ConfigureDeviceForSdt or Mt90528ConfigureDeviceForUdtAndSdt

- Mt90528ConfigureTdmPortForUdt for each UDT port and Mt90528ConfigureTdmPortForSdt for each SDT port

- 3. Mt90528EnableTxsar

- 4. Mt90528OpenTxVcForUdt for each UDT mode TX VC to be opened

- 5. Mt90528OpenRxVcForUdt for each UDT mode RX VC to be opened

- 6. Mt90528OpenTxVcForSdt for each SDT mode TX VC to be opened

- 7. Mt90528OpenRxVcForSdt for each SDT mode RX VC to be opened

- 8. Mt90528CloseTxVcForUdt and Mt90528CloseRxVcForUdt to close UDT VCs

- 9. Mt90528CloseTxVcForSdt and Mt90528CloseRxVcForSdt to close SDT VCs

For non-CBR data cell transmission these routines should be called sometime after configuring the device:

- Mt90528ConfigureDataTxsarModule to allocate memory for the TXSAR data buffer and initialize the Data TXSAR Registers

- 2. Mt90528InitializeDataTxsarWritePointer to set the write pointer to the beginning of the buffer

- 3. Mt90528WriteDataTxsarBuffer to write one cell to the data buffer

- 4. Mt90528EnableDataTxsar to transmit the contents of the data buffer

- 5. Mt90528DisableDataTxsar to disable the Data TXSAR Module

For data cell reception these routines should be called sometime after configuring the device:

- Mt90528ConfigureDataRxsarModule to allocate memory for the RXSAR data buffer and initialize the Data RXSAR Registers

- 2. Mt90528EnableDataRxsar to enable the Data RXSAR Module

- 3. Mt90528OpenRxDataVc to receive F4 OAM cells for a particular VC

- 4. Mt90528CloseRxDataVc to stop receiving F4 OAM cells for a particular VC

- 5. Mt90528ReadDataRxsarBuffer to read one cell from the data buffer

- 6. Mt90528DisableDataRxsar to disable the Data RXSAR Module

Use the following routines to deprogram ports:

- 1. Mt90528DeprogramTdmPortForUdt

- 2. Mt90528DeprogramTdmPortForSdt

Other routines are:

- 1. Mt90528SetTdmPortLinkType will change the link type of a port

- Mt90528EnableTxTdmForUdt/Mt90528DisableTxTdmForUdt to enable/disable transmission of UDT cells for a particular port

- Mt90528EnableTxVcForSdt/Mt90528DisableTxVcForSdt to enable/disable transmission of cells for a particular SDT VC

- 4. Mt90528UpdateCutVcPeriod to change the value of the Cut Vc Period for a particular device

- 5. Mt90528UpdateCellDelayVariation to change the cell delay variation for a particular VC

- Mt90528UpdateReplayNSilence to change the replay and silence setting for a particular SDT RX VC

**NOTE**: the application has to define variables using the structures s\_mt90528\_statistics, a\_internal\_memory\_chunks and a\_external\_memory\_chunks in order to use the following functions. These common variables are also used by the API, ISR and MIB functions.

# 2.2.1 Mt90528ConfigureDeviceForUdt

#### **Prototype**

```

USHORT Mt90528ConfigureDeviceForUdt (

UINT Device,

s_device_udt_params * pParams,

s_mt90528_statistics * pStats,

s_memory_chunk * pExtChunks

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES

pParams pointer to a structure containing user-programmable UDT settings for the MT90528 device.

See 4.5, "Structure s\_device\_udt\_params".

pStats pointer to MIB statistics structure.

See 5.4, "Structure s\_mt90528\_statistics".

pExtChunks pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure's memory chunk".

#### **Return Values**

MT90528\_ATM\_NO\_ERROR device is configured for UDT

MT90528 ATM DEVICE OUT OF RANGE

device is out of range

MT90528\_ATM\_PORT\_OUT\_OF\_RANGE

primary or secondary clock source port is out of range

MT90528\_ATM\_CHUNK\_OUT\_OF\_RANGE

memory chunk is out of range

MT90528\_ATM\_DEVICE\_ADDRESS\_NEEDS\_PHY\_MODE

device address only applicable to phy mode

MT90528\_ATM\_DEVICE\_ADDRESS\_OUT\_OF\_RANGE

device address is out of range

MT90528\_ATM\_LUT\_ALLOCATE\_MEMORY\_ERROR

failed to allocate memory for look-up table

MT90528\_ATM\_M\_PLUS\_N\_OUT\_OF\_RANGE

M and N values are out of range

MT90528\_ATM\_FATAL\_ERROR API cannot recover

# Description

This routine configures the device for UDT mode and if necessary allocates memory for and initializes the entries in the look-up table based on user specified values for the number of VPI and VCI concatenation bits. The LUT will be initialized if external memory is present.

Parameters are verified as follows:

- · the device id is in range

- · the primary and secondary PLL clock sources specified are valid port ids

- · a non-zero device address is only specified with phy mode

- the device address specified is <= 30</li>

- the chunk of external memory specified for the look-up table is <= MAX ADDRESS EXT MEMORY</li>

- the user specified values for the VCI and VPI number of concatenation bits are verified to be in range, i.e.,

Params.DeviceCommonParams.UncbM in [0..12], Params.DeviceCommonParams.UncbN in [4..16], and

Params.DeviceCommonParams.UncbM + Params.DeviceCommonParams.UncbN <= 16</li>

The UTOPIA Configuration Register fields are configured as follows:

- SDT N UDT is set to UDT mode

- UNI N NNI is set to Params.DeviceCommonParams.UcrUniNNni

- UTO CLK SEL is set to Params.DeviceCommonParams.UcrUtoClkSel

- GLOBAL OAM SEL is set to Params.DeviceCommonParams.UcrGlobalOamSel

- EIGHT N SIXTEEN is set to Params. Device Common Params. Ucr Eight NSixteen

- LEVEL1 N LEVEL2 is set to Params.DeviceCommonParams.UcrLevel1NLevel2

- UKSEL is set to Params.DeviceCommonParams.UcrUkSel

- PHY N ATM is set to Params.DeviceCommonParams.UcrPhyNAtm

- DEVICE ADDRESS is set to Params.DeviceCommonParams.UcrDeviceAddress

The Clock Management Configuration Register fields are configured as follows:

- · SLV N MSTR is set to slave mode

- FNXI1 RATE and FNXI2 RATE are set to 2.43 MHz

- EXT N INT is set to Params. Device Common Params. Cmcr ExtNInt

- 8 KHZ SEL is set to Params. Device Sdt Specific Params. Cmcr8KhzSel

The External PLL Clock Source Register fields are configured as follows:

- PRI SEL bits<4:0> are set to Params.DeviceCommonParams.PllcsPriClkSrcPrt

- PRI SEL bit<5> is set to Params.DeviceCommonParams.PllcsPriClkSrcTyp

- SEC SEL bits<4:0> are set to Params.DeviceCommonParams.PllcsSecClkSrcPrt

- SEC SEL bit<5> is set to Params.DeviceCommonParams.PllcsSecClkSrcTyp

The VC Match and Match Enable and the VP Match and Match Enable Registers are set to Params.DeviceCommonParams.VcMatch,

Params.DeviceCommonParams.VcMatchEnable,

Params.DeviceCommonParams.VpMatchEnable respectively

The look-up table is configured, if and only if external memory is present, as follows:

- 2 (M + N + 1) bytes are allocated for the look-up table in the chunk of external memory specified by Params.DeviceCommonParams.ExtMemChunk where M is Params.DeviceCommonParams.UncbM and N is Params.DeviceCommonParams.UncbN. If 128 Kbytes of memory are required for the look-up table then ExtMemChunk must specify the first of two consecutive empty chunks of memory.

- the look-up table is initialized so that every entry has its Destination of Received Cell field set to LUT DS DISCARDED

- the UTOPIA Number of Concatenated bits Register is programmed with Params.DeviceCommonParams.UncbN and Params.DeviceCommonParams.UncbM

- the 16 most significant bits of the look-up table byte address are stored in the LUT Base Address Register

The UDT Reassembly Control Register fields are configured as follows:

- UDT DUMMY is set to Params.DeviceUdtSpecificParams.UrcrUdtDummy

- UDT\_INSERT\_LOST is set to Params.DeviceUdtSpecificParams.UrcrUdtInsertLost

- CHECK LATE ARRIVALS is set to Params. Device UdtSpecific Params. Urcr CheckLate Arrivals

The MIB Timeout Configuration Register fields are configured as follows:

• CUT\_VC\_PERIOD is set to the user-specified value in *Params.DeviceCommonParams.MtcrCutVcPeriod* The incoming and outgoing UTOPIA FIFOs are cleared.

The UTO\_CLK\_CONFIGURED field of the UTOPIA Configuration Register is set at least one clock cycle after setting the UTO\_CLK\_SEL bit.

#### **Source Files**

atm90528.h, atm90528.c

# 2.2.2 Mt90528ConfigureDeviceForSdt

# **Prototype**

```

USHORT Mt90528ConfigureDeviceForSdt (

UINT Device,

s_device_sdt_params * pParams,

s_mt90528_statistics * pStats,

s_memory_chunk * pIntChunks,

s_memory_chunk * pExtChunks

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES

pParams pointer to a structure containing user-programmable SDT settings for the MT90528 device.

See 4.6, "Structure s device sdt params".

pStats pointer to MIB statistics structure.

See 5.4, "Structure s mt90528 statistics".

plntChunks pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure s\_memory\_chunk".

pExtChunks pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure's memory chunk".

# **Return Values**

```

MT90528 ATM NO ERROR

device is configured for SDT

MT90528_ATM_DEVICE_OUT_OF_RANGE

device id is out of range

MT90528_ATM_PORT_OUT_OF_RANGE

primary or secondary clock source port is out of range

MT90528_ATM_CHUNK_OUT_OF_RANGE

memory chunk out of range

MT90528_ATM_DEVICE_ADDRESS_NEEDS_PHY_MODE

device address only applicable to phy mode

MT90528 ATM DEVICE ADDRESS OUT OF RANGE

device address is out of range

MT90528_ATM_LUT_ALLOCATE_MEMORY_ERROR

failed to allocate memory for look-up table

MT90528_ATM_M_PLUS_N_OUT_OF_RANGE

M and N values out of range

```

API cannot recover

#### Description

This routine configures the device for SDT mode and allocates memory for and initializes the entries in the look-up table based on user specified values for the number of VPI and VCI concatenation bits.

Parameters are verified as follows:

MT90528\_ATM\_FATAL\_ERROR

- the device id is in range

- the primary and secondary PLL clock sources specified are valid port ids

- a non-zero device address is only specified with phy mode

- the device address specified is <= 30</li>

- the chunk of external memory specified for the look-up table is <= MAX\_ADDRESS\_EXT\_MEMORY</li>

- the user specified values for the VCI and VPI number of concatenation bits are verified to be in range, i.e., Params.DeviceCommonParams.UncbM in [0..12], Params.DeviceCommonParams.UncbN in [4..16], and Params.DeviceCommonParams.UncbM + Params.DeviceCommonParams.UncbN <= 16

The UTOPIA Configuration Register fields are configured as follows:

- · SDT N UDT is set to SDT mode

- UNI N NNI is set to Params.DeviceCommonParams.UcrUniNNni

- UTO CLK SEL is set to Params.DeviceCommonParams.UcrUtoClkSel

- GLOBAL\_OAM\_SEL is set to Params.DeviceCommonParams.UcrGlobalOamSel

- EIGHT\_N\_SIXTEEN is set to Params.DeviceCommonParams.UcrEightNSixteen

- LEVEL1 N LEVEL2 is set to Params. Device Common Params. UcrLevel1NLevel2

- UKSEL is set to Params.DeviceCommonParams.UcrUkSel

- PHY N ATM is set to Params.DeviceCommonParams.DeviceCommonParams.UcrPhyNAtm

- DEVICE ADDRESS is set to Params.DeviceCommonParams.UcrDeviceAddress

The Clock Management Configuration Register fields are configured as follows:

- SLV N MSTR is set to Params. DeviceSdtSpecificParams. CmcrSlvNMstr

- F0 MODE is set to Params. Device Sdt Specific Params. Cmcr F0 Mode

- 8 KHZ SEL is set to Params.DeviceSdtSpecificParams.Cmcr8KhzSel

- FNXI1 RATE is set to Params. Device Sdt Specific Params. Cmcr Fnxi1Rate

- FNXI2 RATE is set to Params. Device Sdt Specific Params. CmcrFnxi2Rate

- EXT N INT is set to Params.DeviceCommonParams.CmcrExtNInt

The External PLL Clock Source Register fields are configured as follows:

- PRI SEL bits<4:0> are set to Params.DeviceCommonParams.PllcsPriClkSrcPrt

- PRI\_SEL bit<5> is set to Params.DeviceCommonParams.PllcsPriClkSrcTyp

- SEC SEL bits<4:0> are set to Params.DeviceCommonParams.PllcsSecClkSrcPrt

- SEC\_SEL bit<5> is set to Params.DeviceCommonParams.PllcsSecClkSrcTyp

The VC Match and Match Enable and the VP Match and Match Enable Registers are set to Params.DeviceCommonParams.VcMatch,

Params.DeviceCommonParams.VcMatchEnable,

Params.DeviceCommonParams.VpMatchEnable respectively

The look-up table is configured as follows:

- 2 <sup>(M + N +1)</sup> bytes are allocated for the look-up table in the chunk of external memory specified by Params.DeviceCommonParams.ExtMemChunk where M is Params.DeviceCommonParams.UncbM and N is Params.DeviceCommonParams.UncbN. If 128 Kbytes of memory are required for the look-up table then ExtMemChunk must specify the first of two consecutive empty chunks of memory.

- the look-up table is initialized so that every entry has its Destination of Received Cell field set to LUT\_DS\_DISCARDED

- the UTOPIA Number of Concatenated bits Register is programmed with Params.DeviceCommonParams.UncbN and Params.DeviceCommonParams.UncbM

- the 16 most significant bits of the look-up table byte address are stored in the LUT Base Address Register

The MIB Timeout Configuration Register fields are configured as follows:

CUT\_VC\_PERIOD is set to the user-specified value in Params. Device CommonParams. MtcrCutVcPeriod

The incoming and outgoing UTOPIA FIFOs are cleared.

The SDT Reassembly Control Register fields are configured as follows:

- SDT\_DUMMY is set to Params.DeviceSdtSpecificParams.SrcrSdtDummy

- SDT\_INSERT\_LOST is set to Params.DeviceSdtSpecificParams.SrcrSdtInsertLost

- · CB\_BASE\_ADD is set to 0

The Main TDM Control Register 1 fields are configured as follows:

- IDLE\_DATA is set to Params.DeviceSdtSpecificParams.Maintdm1IdleData

- SILENCE\_DATA is set to Params.DeviceSdtSpecificParams.Maintdm1SilenceData

The Main TDM Control Register 2 fields are configured as follows:

IDLE\_CAS is set to Params.DeviceSdtSpecificParams.Maintdm2IdleCas

The UTO\_CLK\_CONFIGURED field of the UTOPIA Configuration Register is set at least one clock cycle after setting the UTO\_CLK\_SEL bit.

#### **Source Files**

atm90528.h, atm90528.c

# 2.2.3 Mt90528ConfigureDeviceForUdtAndSdt

#### **Prototype**

```

USHORT Mt90528ConfigureDeviceForUdtAndSdt (

UINT Device,

s_device_udt_and_sdt_params * pParams,

s_mt90528_statistics * pStats,

s_memory_chunk * pIntChunks,

s_memory_chunk * pExtChunks

)

```

# **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

pParams pointer to a structure containing user-programmable SDT and UDT settings for the MT90528

device.

See 4.7, "Structure s\_device\_udt\_and\_sdt\_params".

pStats pointer to MIB statistics structure.

See 5.4, "Structure s mt90528 statistics".

plntChunks pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure s\_memory\_chunk".

pExtChunks pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure s\_memory\_chunk".

#### **Return Values**

MT90528\_ATM\_NO\_ERROR device is configured for UDT and SDT

MT90528 ATM DEVICE OUT OF RANGE

device id is out of range

MT90528\_ATM\_PORT\_OUT\_OF\_RANGE

primary or secondary clock source port is out of range

MT90528\_ATM\_CHUNK\_OUT\_OF\_RANGE

memory chunk is out of range

MT90528\_ATM\_DEVICE\_ADDRESS\_NEEDS\_PHY\_MODE

device address only applicable to phy mode

MT90528\_ATM\_DEVICE\_ADDRESS\_OUT\_OF\_RANGE

device address is out of range

MT90528\_ATM\_LUT\_ALLOCATE\_MEMORY\_ERROR

failed to allocate memory for look-up table

MT90528\_ATM\_M\_PLUS\_N\_OUT\_OF\_RANGE

M and N values are out of range

MT90528\_ATM\_FATAL\_ERROR API cannot recover

# Description

This routine configures the device for UDT and SDT mode and allocates memory for and initializes the entries in the look-up table based on user specified values for the number of VPI and VCI concatenation bits.

Parameters are verified as follows:

- · the device id is in range

- · the primary and secondary PLL clock sources specified are valid port ids

- a non-zero device address is only specified with phy mode

- the device address specified is <= 30</li>

- the chunk of external memory specified for the look-up table is <= MAX\_ADDRESS\_EXT\_MEMORY</li>

- the user specified values for the VCI and VPI number of concatenation bits are verified to be in range, i.e.,

Params.DeviceCommonParams.UncbM in [0..12], Params.DeviceCommonParams.UncbN in [4..16], and

Params.DeviceCommonParams.UncbM + Params.DeviceCommonParams.UncbN <= 16</li>

The UTOPIA Configuration Register fields are configured as follows:

- · SDT N UDT is set to UDT mode

- UNI N NNI field is set to Params. Device Common Params. UcrUniNNni

- UTO CLK SEL is set to Params.DeviceCommonParams.UcrUtoClkSel

- GLOBAL\_OAM\_SEL is set to Params.DeviceCommonParams.UcrGlobalOamSel

- EIGHT N SIXTEEN is set to Params. Device Common Params. Ucr Eight NSixteen

- LEVEL1 N LEVEL2 is set to Params. Device Common Params. UcrLevel1NLevel2

- UKSEL is set to Params.DeviceCommonParams.UcrUkSel

- PHY N ATM is set to Params.DeviceCommonParams.DeviceCommonParams.UcrPhyNAtm

- DEVICE ADDRESS is set to Params. Device Common Params. Ucr Device Address

The Clock Management Configuration Register fields are configured as follows:

- SLV N MSTR is set to Params.DeviceSdtSpecificParams.CmcrSlvNMstr

- F0\_MODE is set to Params.DeviceSdtSpecificParams.CmcrF0Mode

- 8 KHZ SEL is set to Params. Device Sdt Specific Params. Cmcr8KhzSel

- FNXI1 RATE is set to Params. Device Sdt Specific Params. Cmcr Fnxi1Rate

- FNXI2 RATE is set to Params.DeviceSdtSpecificParams.CmcrFnxi2Rate

- EXT N INT is set to Params.DeviceCommonParams.CmcrExtNInt

The External PLL Clock Source Register fields are configured as follows:

- PRI SEL bits<4:0> are set to Params.DeviceCommonParams.PllcsPriClkSrcPrt

- PRI SEL bit<5> is set to Params.DeviceCommonParams.PllcsPriClkSrcTyp

- SEC SEL bits<4:0> are set to Params.DeviceCommonParams.PllcsSecClkSrcPrt

- SEC SEL bit<5> is set to Params.DeviceCommonParams.PllcsSecClkSrcTyp

The VC Match and Match Enable and the VP Match and Match Enable Registers are set to Params. Device Common Params. Vc Match, Params. Device Common Params. Vp Match, and Params. Device Common Params. Vp Match Enable, Params. Vp Match Enable respectively

The look-up table is configured as follows:

- 2 (M + N +1) bytes are allocated for the look-up table in the chunk of external memory specified by Params.DeviceCommonParams.ExtMemChunk where M is Params.DeviceCommonParams.UncbM and N is Params.DeviceCommonParams.UncbN. If 128 Kbytes of memory are required for the look-up table then ExtMemChunk must specify the first of two consecutive empty chunks of memory.

- the look-up table is initialized so that every entry has its Destination of Received Cell field set to LUT DS DISCARDED

- the UTOPIA Number of Concatenated bits Register is programmed with Params.DeviceCommonParams.UncbN and Params.DeviceCommonParams.UncbM

- the 16 most significant bits of the look-up table byte address are stored in the LUT Base Address Register

The UDT Reassembly Control Register fields are configured as follows:

- UDT DUMMY is set to Params.DeviceUdtSpecificParams.UrcrUdtDummy

- UDT\_INSERT\_LOST is set to Params.DeviceUdtSpecificParams.UrcrUdtInsertLost

- CHECK LATE ARRIVALS is set to Params. Device UdtSpecific Params. Urcr CheckLate Arrivals

The MIB Timeout Configuration Register fields are configured as follows:

• CUT\_VC\_PERIOD is set to the user-specified value in *Params.DeviceCommonParams.MtcrCutVcPeriod* The incoming and outgoing UTOPIA FIFOs are cleared.

The SDT Reassembly Control Register fields are configured as follows:

- SDT\_DUMMY is set to Params.DeviceSdtSpecificParams.SrcrSdtDummy

- SDT\_INSERT\_LOST is set to Params.DeviceSdtSpecificParams.SrcrSdtInsertLost

- CB BASE ADD is set to 0

The Main TDM Control Register 1 fields are configured as follows:

- IDLE DATA is set to Params.DeviceSdtSpecificParams.Maintdm1IdleData

- SILENCE DATA is set to Params. Device Sdt Specific Params. Maintdm1 Silence Data

The Main TDM Control Register 2 fields are configured as follows:

• IDLE\_CAS is set to the Params.DeviceSdtSpecificParams.Maintdm2IdleCas

The UTO\_CLK\_CONFIGURED field of the UTOPIA Configuration Register is set at least one clock cycle after setting the UTO\_CLK\_SEL bit.

#### **Source Files**

atm90528.h, atm90528.c

# 2.2.4 Mt90528ConfigureDataRxsarModule

# **Prototype**

```

USHORT Mt90528ConfigureDataRxsarModule (

UINT Device,

s_data_cell_buffer_params * pParams,

s_memory_chunk * pExtChunks

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

pParams pointer to a structure containing user-programmable settings for configuring the Data RX SAR

Module.

See 4.8, "Structure s data cell buffer params".

pExtChunks pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure s\_memory\_chunk".

#### **Return Values**

MT90528\_ATM\_NO\_ERRORData RX\_SAR is configuredMT90528\_ATM\_DEVICE\_OUT\_OF\_RANGEdevice id is out of rangeMT90528\_ATM\_CHUNK\_OUT\_OF\_RANGEmemory chunk is out of range

MT90528\_ATM\_DATA\_RXSAR\_BUFFER\_ALLOCATE\_MEMORY\_ERROR

failed to allocate memory for buffer

MT90528\_ATM\_FATAL\_ERROR API cannot recover

#### Description

This routine allocates memory for the RX\_SAR data cell buffer and initializes the registers required for RX\_SAR data cell handling.

Parameters are verified as follows:

- · the device id is in range

- the chunk of external memory specified for the RX\_SAR data buffer is <= MAX\_ADDRESS\_EXT\_MEMORY</li>

The size of the buffer allocated is determined by the user specified value in *Params.BufferSize*. The buffer is allocated in the chunk of external memory specified by *Params.BufferMemoryChunk*.

The size and base address of the buffer is stored in the Data RX SAR Configuration Register.

The Data RX\_SAR Read pointer is initialized to buffer size - 1.

#### Source Files

atm90528.h, atm90528.c

#### 2.2.5 Mt90528ReadDataRxsarBuffer

# **Prototype**

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES pData location where data from the RX\_SAR buffer is to be read into

#### **Return Values**

MT90528\_ATM\_NO\_ERROR MT90528\_ATM\_LAST\_DATA\_CELL MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE MT90528\_ATM\_DATA\_BUFFER\_EMPTY MT90528\_ATM\_FATAL\_ERROR RX\_SAR data cell read successfully, more cells in the buffer RX\_SAR data cell read successfully, no more cells in the buffer device id is out of range

no cells to read

API cannot recover

# Description

This routine reads one data cell from the RX SAR data cell buffer as follows:

- · the read pointer is read from the Data RX SAR Read Pointer Register indicating the last cell read

- the write pointer is read from the Data RX\_SAR Write Pointer Register indicating the location where the next cell will be written

- if the read pointer is one less than the write pointer then the Data RX\_SAR is about to read a cell which has not been written, the error MT90528 ATM DATA BUFFER EMPTY is returned, otherwise

- the next data cell is read from the RX SAR data cell buffer into location in CPU memory specified by pData

- the read pointer in the Data RX SAR Read Pointer Register is incremented

- if the cell read is the last cell in the buffer return MT90528\_ATM\_LAST\_DATA\_CELL, otherwise return MT90528\_ATM\_NO\_ERROR

Parameters are verified as follows:

- the device id is in range

- the buffer is not empty

If a Data RX\_SAR buffer overrun interrupt occurs due to the write pointer catching up to the read pointer, the read pointer will be incremented by one cell by the interrupt handler. This will cause the data cell at the write pointer position to be discarded.

Note: The Data RX\_SAR interrupts are disabled in the main interrupt enable register to prevent this routine from being called by the application and the ISR thread at the same time. Otherwise, the read pointer could become corrupted. The interrupts are re-enabled before the routine returns.

#### **Source Files**

atm90528.h atm90528.c

# 2.2.6 Mt90528EnableDataRxsar

# **Prototype**

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES pParams pointer to structure containing RX\_SAR data interrupt enable flags.

See 4.10, "Structure's data rx sar enable params".

pStats pointer to MIB statistics structure.

See 5.4, "Structure s mt90528 statistics".

#### **Return Values**

MT90528\_ATM\_NO\_ERROR MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE MT90528\_ATM\_FATAL\_ERROR

Data RX\_SAR module is enabled device id is out of range API cannot recover

# Description

This routine

- · optionally enables the cell buffer overrun interrupt in the Data RX\_SAR module

- · optionally enables the cell arrival interrupt in the Data RX SAR module

- optionally enables the buffer half full interrupt in the Data RX\_SAR module

- · enables the Data RX SAR module for cell handling

Parameters are verified as follows:

· the device id is in range

#### **Source Files**

atm90528.h atm90528.c

# 2.2.7 Mt90528DisableDataRxsar

#### **Prototype**

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES

# **Return Values**

MT90528\_ATM\_NO\_ERROR Data RX\_SAR module is disabled MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE device id is out of range

MT90528\_ATM\_FATAL\_ERROR API cannot recover

# Description

This routine disables the Data RX SAR module by clearing the Data RX SAR Control Register.

Parameters are verified as follows:

· the device id is in range

#### **Source Files**

atm90528.h atm90528.c

# 2.2.8 Mt90528ConfigureDataTxsarModule

# **Prototype**

```

USHORT Mt90528ConfigureDataTxsarModule (

UINT Device,

s_data_cell_buffer_params * pParams,

s_memory_chunk * pExtChunks

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

pParams pointer to a structure containing user-programmable settings for configuring the Data TX\_SAR

Module.

See 4.8, "Structure s data cell buffer params".

pExtChunks pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure s memory chunk".

#### **Return Values**

MT90528\_ATM\_NO\_ERRORData TX\_SAR is configuredMT90528\_ATM\_DEVICE\_OUT\_OF\_RANGEdevice id is out of rangeMT90528\_ATM\_CHUNK\_OUT\_OF\_RANGEmemory chunk is out of range

MT90528\_ATM\_DATA\_TXSAR\_BUFFER\_ALLOCATE\_MEMORY\_ERROR

failed to allocate memory for buffer

MT90528\_ATM\_FATAL\_ERROR API cannot recover

#### Description

This routine allocates memory for the TX\_SAR data cell buffer and initializes the registers required for TX\_SAR data cell handling.

Parameters are verified as follows:

- · the device id is in range

- the chunk of external memory specified for the TX\_SAR data buffer is <= MAX\_ADDRESS\_EXT\_MEMORY</li>

The size of the buffer allocated is determined by the user-specified value in *Params.BufferSize*. The buffer is allocated in the chunk of external memory specified by *Params.BufferMemoryChunk*.

The size and base address of the buffer is stored in the Data TX\_SAR Configuration Register.

The Data TX\_SAR Write pointer is initialized to 0.

#### **Source Files**

atm90528.h atm90528.c

# 2.2.9 Mt90528InitializeDataTxsarWritePointer

# **Prototype**

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES

#### **Return Values**

```

MT90528_ATM_NO_ERROR pointer is initialized

MT90528_ATM_DEVICE_OUT_OF_RANGE device id is out of range

MT90528_ATM_FATAL_ERROR API cannot recover

```

# Description

The Data TX\_SAR Write pointer is initialized to point to the first buffer entry.

Parameters are verified as follows:

· the device id is in range

#### **Source Files**

atm90528.h atm90528.c

# 2.2.10 Mt90528WriteDataTxsarBuffer

# **Prototype**

# **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES pDataCell location of the data to be written to the TX\_SAR buffer

# **Return Values**

MT90528\_ATM\_NO\_ERROR MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE MT90528\_ATM\_TXSAR\_FULL MT90528\_ATM\_DATA\_CELL\_DISCARDED MT90528\_ATM\_FATAL\_ERROR cell written successfully, room for more cells device id is out of range cell written successfully, no room for more cells txsar buffer is full, cell has been discarded API cannot recover

#### Description

This routine writes one data cell to the TX\_SAR data cell buffer as follows:

- the read and write pointers are read from the Data TX\_SAR Read and Write Pointer Registers

- if the write pointer is pointing to the cell imediately before the cell that the read pointer is pointing to, the cell is discarded and an error is returned

- otherwise, the cell is written to the buffer at the location indicated by the write pointer

- the write pointer is incremented and stored in the Write Pointer Register

- if the newly incremented write pointer is pointing to the cell imediately before the cell that the read pointer is

pointing to a message is returned indicating that the cell was written successfully and the TX\_SAR buffer is

now full.

Parameters are verified as follows:

the device id is in range

#### **Source Files**

atm90528.h atm90528.c

# 2.2.11 Mt90528EnableDataTxsar

#### **Prototype**

```

USHORT Mt90528EnableDataTxsar (

UINT Device,

s_data_tx_sar_enable_params * pParams

)

```

#### **Parameters**

Device pParams

device identifier, range of values: 0..MAX MT90528 DEVICES

pointer to a structure containing user-programmable settings for enabling the Data TX SAR mod-

ule.

See 4.9, "Structure s data tx sar enable params"

# Return Values

MT90528\_ATM\_NO\_ERROR

Data TX\_SAR module is enabled

MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE

device id is out of range

MT90528\_ATM\_CELL\_GENERATION\_TIMEOUT\_OUT\_OF\_RANGE

timeout value is out of range

MT90528\_ATM\_FATAL\_ERROR

API cannot recover

# Description

This routine enables the Data TX\_SAR.

Parameters are verified as follows:

- · the device id is in range

- Params.CellGenerationTimeout <= 1023</li>

In the Data Cell Generation Timeout Register configure the DCGP field with the user-specified value in Params. Cell Generation Timeout.

If the user specified continuous transmission set the write pointer in the Data TX\_SAR Write Pointer Register to 1 past the last cell.

Program the Data TX SAR Control Register fields as follows:

- · enable TDSENB

- set AUTO to Params.Auto

- set TCBE SE to Params.BufferEmptyService

# **Source Files**

atm90528.h atm90528.c

# 2.2.12 Mt90528DisableDataTxsar

# **Prototype**

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES

# **Return Values**

MT90528\_ATM\_NO\_ERROR MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE MT90528\_ATM\_FATAL\_ERROR

Data TX\_SAR module is disabled device id is out of range API cannot recover

#### Description

This routine disables the Data TX\_SAR module by clearing the Data TX\_SAR Control Register.

Parameters are verified as follows:

· the device id is in range

#### **Source Files**

atm90528.h atm90528.c

# 2.2.13 Mt90528ConfigureTdmPortForUdt

# **Prototype**

```

USHORT Mt90528ConfigureTdmPortForUdt (

UINT Device,

USHORT Port,

s_tdm_port_udt_params * pParams,

s_mt90528_statistics * pStats,

s_memory_chunk * pIntChunks

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

Port TDM port id, range of values: 0..MAX PORTS

pParams pointer to structure containing user-programmable settings for configuring a TDM port for UDT.

See 4.14, "Structure s tdm port udt params".

pStats pointer to MIB statistics structure.

See 5.4, "Structure s mt90528 statistics".

plntChunks pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure's memory chunk".

#### **Return Values**

MT90528\_ATM\_NO\_ERRORport is configured for UDTMT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE\_ERRORdevice id is out of rangeMT90528\_ATM\_PORT\_OUT\_OF\_RANGE\_ERRORport id is out of rangeMT90528\_ATM\_PORT\_ALREADY\_PROGRAMMEDport is already programmedMT90528\_ATM\_PORT\_IN\_LOOPBACKport is in loopback modeMT90528\_ATM\_TXSAR\_ALLOCATE\_MEMORY\_ERRORfailed to allocate memory for the UDT TX SAR

control structure

API cannot recover

MT90528\_ATM\_FATAL\_ERROR

#### Description

This routine configures *Port* for UDT mode.

Parameters are verified as follows:

- Device is in range

- Port is in range and not already programmed or in loopback mode

Memory is allocated for Port's UDT TX SAR Control Structure in the TX SAR Control part of internal memory.

The Timeout Configuration Register fields for *Port* are configured as follows:

LATE CELL PERIOD is set to Params. TdmPortCommonParams. TcrLateCellPeriod

The Clocking Configuration Register fields for Port are configured as follows:

- CLKSEL is set to Params.TdmPortCommonParams.CcrClkSel

- RTSSEL is set to Params.TdmPortCommonParams.CcrRtsSel

- FNXISEL is set to Params.TdmPortCommonParams.CcrFnxiSel

- PLL\_FREQ\_SEL is set to Params.TdmPortCommonParams.CcrPllFreqSel

- PLL MODE SEL is set to Params. TdmPortCommonParams. CcrPlIModeSel

PLL INPUT SEL is set to Params.TdmPortCommonParams.CcrPllInputSel

The PLL Enable Register fields for Port are configured as follows:

• PLL ENABLE is set to Params. TdmPortCommonParams. PllenPllEnable.

The TDM Control Register 1 fields for Port are configured as follows:

- TDM CLK POL is set to Params.TdmPortCommonParams.Tdm1TdmClkPol

- TDM LINK TYPE is set to Params.TdmPortCommonParams.Tdm1TdmLinkType

- TDM CLK RATE is hard-coded to 1.544 MHz for DS1 ports and 2.048 MHz for E1 ports

- TDM LOS CLK is set to Params.TdmPortUdtSpecificParams.Tdm1TdmLosClk

- TDM\_LOS\_POL is set to the board-specific constant BOARD\_TDM1\_TDM\_LOS\_POL

- · TDM CLK MODE is set to independent mode

- · TDM DATA FORMAT is set to UDT mode

- INT LOS ENABLE is set to Params.TdmPortUdtSpecificParams.Tdm1IntLosEnable

The TDM Control Register 4 fields for Port are configured as follows:

- UDT LOS SE is set to Params. TdmPortUdtSpecificParams. Tdm4UdtLosSe

- UDT\_TDM\_OUT\_BUF\_ERROR\_SE is set to Params.TdmPortUdtSpecificParams.Tdm4UdtTdmOutBufErrorSe

The TDM Control Register 3 fields for *Port* are configured as follows:

- TDM REASS CLK POL is set to Params. TdmPortCommonParams. Tdm3TdmReassClkPol

- · TDM REASS INT ENB is enabled

- · TDM REASS PORT CONTROL is enabled

- TDM REASS\_LOS is set to Params.TdmPortUdtSpecificParams.Tdm3TdmReassLos

The TX SAR Pointer Table Base Register fields for Port are configured as follows:

- TXPTB is set to the word offset from the start of TX\_SAR control memory of the Port's TX\_SAR Control Structure

- TXCFG is set to UDT mode

The MIB TDM port statistics table is updated with the TDM port mode and link type.

The MIB device statistics table is updated for number of configured TDM ports.

#### **Source Files**

atm90528.h atm90528.c

# 2.2.14 Mt90528DeprogramTdmPortForUdt

#### **Prototype**

```

USHORT Mt90528DeprogramTdmPortForUdt (

UINT Device,

USHORT Port,

s_mt90528_statistics * pStats,

s_memory_chunk * pIntChunks

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

Port TDM port id, range of values: 0..MAX PORTS

pointer to MIB statistics structure. pStats

See 5.4, "Structure s mt90528 statistics".

pIntChunks pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure's memory chunk".

#### **Return Values**

MT90528 ATM NO ERROR MT90528 ATM DEVICE OUT OF RANGE MT90528\_ATM\_PORT\_OUT\_OF\_RANGE MT90528 ATM PORT NOT UDT

MT90528\_ATM\_FATAL\_ERROR

UDT port is de-programmed device id is out of range

port id is out of range port not programmed for UDT API cannot recover

# Description

This routine de-programs a UDT mode port.

Parameters are verified as follows:

- Device is in range

- Port is in range and programmed for UDT

- no VC is opened against Port

The UDT TX SAR Control Structure is cleared and the memory is de-allocated.

The following port specific registers are cleared:

- **Timeout Configuration Register**

- TDM Control Register 4

- TX SAR Pointer Table Base Register

- Clocking Configuration Register

- · PLL Enable Register

- TDM Control Register 1

- · TDM Control Register 3

The MIB TDM port statistics table entry is removed for the TDM port.

The MIB device statistics table is updated for number of configured TDM ports.

# **Source Files**

atm90528.h, atm90528.c

# 2.2.15 Mt90528ConfigureTdmPortForSdt

# **Prototype**

```

USHORT Mt90528ConfigureTdmPortForSdt (

UINT Device,

USHORT Port,

s_tdm_port_sdt_params * pParams,

s_mt90528_statistics * pStats,

s_memory_chunk * pIntChunks,

s_memory_chunk * pExtChunks

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

Port TDM port id, range of values: 0..MAX\_PORTS

pParams pointer to structure containing user-programmable settings for configuring a TDM port for SDT.

See 4.15, "Structure s tdm port sdt params"

pStats pointer to MIB statistics structure.

See 5.4, "Structure s\_mt90528\_statistics".

plntChunks pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure's memory chunk".

pExtChunks pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure's memory chunk".

#### **Return Values**

MT90528\_ATM\_NO\_ERROR port is configured for SDT

MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE\_ERROR device id is out of range

MT90528\_ATM\_PORT\_OUT\_OF\_RANGE\_ERROR port id is out of range

MT90528\_ATM\_PORT\_ALREADY\_PROGRAMMED port is already programmed

MT90528\_ATM\_PORT\_IN\_LOOPBACK port is in loopback mode

MT90528\_ATM\_TXSAR\_ALLOCATE\_MEMORY\_ERROR

failed to allocate memory for this port's segmentation

pointer table

MT90528\_ATM\_SCB\_ALLOCATE\_MEMORY\_ERROR failed to allocate memory for this port's segmentation cir-

cular buffers

MT90528\_ATM\_FATAL\_ERROR API cannot recover

#### Description

This routine configures a port for SDT mode.

Parameters are verified as follows:

- Device is in range

- Port is in range and not already programmed or in loopback mode

- Params->TdmPortSdtSpecificParams.Tdm1TdmDataFormat is either TDM1\_SDT\_MODE or TDM1\_SDT\_MODE\_NGREATER46

- the chunk of external memory specified for this Port's segmentation circular buffers <= MAX ADDRESS EXT MEMORY

- the chunk of external memory specified for this Port's reassembly circular buffers <= MAX\_ADDRESS\_EXT\_MEMORY

Memory is allocated for the Port's Segmentation Pointer Table in TX SAR Control memory.

Memory is allocated for 24 or 32 (depending on whether *Port* is DS1 or E1) consecutive segmentation circular buffers in the chunk of external memory specified by *Params.TdmPortSdtSpecificParams.ExtMemTxCBChunk*.

The Timeout Configuration Register fields for *Port* are configured as follows:

LATE CELL PERIOD is set to Params. TdmPortCommonParams. TcrLateCellPeriod

The Clocking Configuration Register fields for Port are configured as follows:

- CLKSEL is set to Params. TdmPortCommonParams. CcrClkSel

- RTSSEL is set to Params.TdmPortCommonParams.CcrRtsSel

- FNXISEL is set to Params.TdmPortCommonParams.CcrFnxiSel

- PLL FREQ SEL is set to Params. TdmPortCommonParams. CcrPllFreqSel

- PLL MODE SEL is set to Params. TdmPortCommonParams. CcrPllModeSel

- PLL INPUT SEL is set to Params. TdmPortCommonParams. CcrPllInputSel

The PLL Enable Register fields for Port are configured as follows:

PLL ENABLE is set to ENABLED

The TDM Control Register 1 fields for Port are configured as follows:

- TDM CLK POL is set to Params.TdmPortCommonParams.Tdm1TdmClkPol

- TDM LINK TYPE is set Params.TdmPortCommonParams.Tdm1TdmLinkType

- TDM CLK RATE is set to Params.TdmPortCommonParams.Tdm1TdmClkRate

- TDM CAS LOCATION is set Params. TdmPortSdtSpecificParams. Tdm1CasLocation

- TDM MAPPING SCH is set to Params.TdmPortSdtSpecificParams.Tdm1MappingSch

- TDM\_PULSE\_SEL is set to the Params.TdmPortSdtSpecificParams.Tdm1TdmPulseSel

- TDM PULSE POL is set to the Params.TdmPortSdtSpecificParams.Tdm1TdmPulsePol

- TDM CLK MODE is set to the Params.TdmPortSdtSpecificParams.Tdm1TdmClkMode

- TDM BUS MODE is set to Params.TdmPortSdtSpecificParams.Tdm1TdmBusMode

- TDM DATA FORMAT is set to Params. TdmPortSdtSpecificParams. Tdm1TdmDataFormat

The TDM Control Register 2 fields for *Port* are configured as follows:

- TDM\_SEGMEN\_BASE\_ADD is set to bits <19:11> of the word address in external memroy of the segmentation circular buffers for Port

- TDM SEGMEN PORT CONTROL is enabled

- TDM\_SEGMEN\_INT\_ENB is enabled

- TDM\_SEGMEN\_EXT\_ENB is enabled

The TDM Control Register 3 fields for *Port* are configured as follows:

- TDM\_REASS\_CLK\_POL is set to Params.TdmPortCommonParams.Tdm3TdmReassClkPol

- · TDM REASS INT ENB is enabled

- TDM\_REASS\_EXT\_ENB is enabled

- TDM REASS PORT CONTROL is enabled

- TDM\_REASS\_BASE\_ADD is set to bits <19:15> of the 32 word chunk of external memory where Port's reassembly circular buffers will be allocated

The TDM Control Register 4 fields for Port are configured as follows:

- SDT\_TDM\_OUT\_BUF\_ERROR\_SE is set to Params.TdmPortSdtSpecificParams.Tdm4SdtTdmOutBufErrorSe

- SDT PERM UNDER SE is set to Params.TdmPortSdtSpecificParams.Tdm4SdtPermUnderSe

- SDT SIMPLE UNDER SE is set to Params.TdmPortSdtSpecificParams.Tdm4SdtSimpleUnderSe

If port is in backplane mode and the TX\_SAR is already enabled then wait for 512ms before enabling the port for SDT.

The TX SAR Pointer Table Base Register fields for *Port* are configured as follows:

- TXPTB is set to the word offset from the start of the Port's segmentation pointer table in TX\_SAR control

memory

- TXCFG is set to Params.TdmPortSdtSpecificParams.TxptbTxcfg

The MIB TDM port statistics table is updated with the TDM port mode and link type.

The MIB device statistics table is updated for number of configured TDM ports.

#### **Source Files**

atm90528.h atm90528.c

# 2.2.16 Mt90528DeprogramTdmPortForSdt

# **Prototype**

```

USHORT Mt90528DeprogramTdmPortForSdt (

UINT Device,

USHORT Port,

s_mt90528_statistics * pStats,

s_memory_chunk * pIntChunks

s_memory_chunk * pExtChunks

)

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

Port TDM port id, range of values: 0..MAX PORTS

pStats pointer to MIB statistics structure.

See 5.4, "Structure s\_mt90528\_statistics".

plntChunks pointer passed by caller of memory manager internal chunk array.

See 4.24, "Structure s memory chunk".

pExtChunks pointer passed by caller of memory manager external chunk array.

See 4.24, "Structure s\_memory\_chunk".

#### **Return Values**

MT90528\_ATM\_NO\_ERRORSDT port is de-programmedMT90528\_ATM\_DEVICE\_OUT\_OF\_RANGEdevice id is out or rangeMT90528\_ATM\_PORT\_OUT\_OF\_RANGEport id is out of rangeMT90528\_ATM\_PORT\_NOT\_SDTport not programmed for SDTMT90528\_PORT\_IS\_ASSIGNED\_A\_VCport has a vc assigned to itMT90528\_ATM\_FATAL\_ERRORAPI cannot recover

# Description

This routine de-programs an SDT mode port.

Parameters are verified as follows:

- Device is in range

- *Port* is in range and programmed for SDT mode

- no VCs are opened against Port

The segmentation pointer table for *Port* is cleared and the memory is de-allocated.

The following port specific registers are cleared:

- TDM Control Register 2

- **Timeout Configuration Register**

- TDM Control Register 4

- TX\_SAR Pointer Table Base Register

- Clocking Configuration Register

- PLL Enable Register

- · TDM Control Register 1

- TDM Control Register 3

The segmentation circular buffers for *Port* are cleared and the memory is de-allocated.

The MIB TDM port statistics table entry is removed for the TDM port.

The MIB device statistics table is updated for number of configured TDM ports.

# **Source Files**

atm90528.h, atm90528.c

#### 2.2.17 Mt90528SetTdmPortLinkType

# **Prototype**

```

USHORT Mt90528SetTdmPortLinkType(

UINT

Device,

USHORT

Port,

UCHAR

LinkType,

UCHAR

ClockRate,

s_mt90528_statistics * pStats

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

Port TDM port id, range of values: 0..MAX PORTS

link type to change the port to, i.e., TDM1\_DS1\_LINK or TDM1\_E1\_LINK LinkType ClockRate clock rate to change the port to, i.e., TDM1\_2048\_KHZ or TDM1\_1544\_KHZ pStats

pointer to MIB statistics structure.

See 5.4, "Structure s\_mt90528\_statistics".

#### **Return Values**

MT90528\_ATM\_NO\_ERROR MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE MT90528\_ATM\_PORT\_OUT\_OF\_RANGE MT90528\_ATM\_FATAL\_ERROR port is configured with new link type device id is out of range port id is out of range API cannot recover

# Description

This adjusts the link type and clock rate for Port.

Parameters are verified as follows:

- Device is in range

- · Port is in range

The TDM Control Register 1 fields for *Port* are configured as follows:

- TDM\_LINK\_TYPE is set to LinkType

- TDM\_CLK\_RATE is set to ClockRate

# **Source Files**

atm90528.h atm90528.c

# 2.2.18 Mt90528TurnOnUtopiaInterfaceLoopback

# **Prototype**

```

USHORT Mt90528TurnOnUtopiaInterfaceLoopback (

UINT Device,

s_mt90528_statistics * pStats,

```

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

pStats pointer to MIB statistics structure.

See 5.4, "Structure s mt90528 statistics".

#### **Return Values**

MT90528\_ATM\_NO\_ERROR utopia interface is in loopback mode

MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE

MT90528\_ATM\_FATAL\_ERROR utopia interface is in loopback mode

device id is out of range

API cannot recover

# Description

This routine clears the UTOPIA FIFOs and puts the UTOPIA interface into loopback mode.

UTOPIA interface loopback is a debugging mode and should not be used with the normal transmit and receive operations of the chip.

Parameters are verified as follows:

· Device is in range

The MIB device statistics table is updated to indicate UTOPIA is in loopback mode.

#### **Source Files**

atm90528.h, atm90528.c

# 2.2.19 Mt90528TurnOffUtopiaInterfaceLoopback

# **Prototype**

#### **Parameters**

Device device identifier, range of values: 0..MAX\_MT90528\_DEVICES

pStats pointer to MIB statistics structure.

See 5.4, "Structure s\_mt90528\_statistics".

#### **Return Values**

```

MT90528_ATM_NO_ERROR utopia interface is not in loopback mode

MT90528_ATM_DEVICE_OUT_OF_RANGE device id is out of range

MT90528_ATM_FATAL_ERROR API cannot recover

```

# Description

This routine clears the UTOPIA FIFOs and takes the UTOPIA interface out of loopback mode.

Parameters are verified as follows:

· Device is in range

The MIB device statistics table is updated to indicate UTOPIA is not in loopback mode.

# **Source Files**

atm90528.h, atm90528.c

# 2.2.20 Mt90528ConfigureTdmPortForLowLatencyLoopback

# **Prototype**

#### **Parameters**

Device device identifier, range of values: 0..MAX MT90528 DEVICES

Port TDM port id, range of values: 0..MAX PORTS

pParams pointer to structure containing user-programmable settings for TDM low-latency loopback.

See 4.16, "Structure s\_tdm\_loopback\_params".

pStats pointer to MIB statistics structure.

See 5.4, "Structure s mt90528 statistics".

#### **Return Values**

MT90528\_ATM\_NO\_ERROR MT90528\_ATM\_DEVICE\_OUT\_OF\_RANGE\_ERROR MT90528\_ATM\_PORT\_OUT\_OF\_RANGE\_ERROR

MT90528\_ATM\_PORT\_ALREADY\_PROGRAMMED MT90528\_ATM\_PORT\_IN\_LOOPBACK

MT90528\_ATM\_FATAL\_ERROR

TDM port is in low-latency loopback

Device is out of range Port is out of range

Port is already programmed Port is already in loopback mode

API cannot recover

# Description

This routine puts the specified port into low-latency loopback.

TDM low-latency loopback is a debugging mode and should not be used with the normal transmit and receive operations of the chip.

Parameters are verified as follows:

- · Device is in range

- · Port is in range and not already programmed or in loopback

The Clocking Configuration Register for *Port* is configured as follows:

CLKSEL is set to CCR\_CLKSEL\_STICLK

The TDM Control Register 1 for *Port* is configured as follows:

- TDM\_CLK\_POL is set to Params.Tdm1TdmClkPol

- TDM LOS POL is set to the board-specific constant BOARD TDM1 TDM LOS POL

- · TDM\_LOW\_LATENCY\_LPBK is enabled