# IEEE 1588 Packet Timestamper and Clock and 1Gbps Parallel-to-Serial MII Converter

# **General Description**

The MAX24288 is a flexible, low-cost IEEE 1588 clock and timestamper with an SGMII or 1000BASE-X serial interface and a parallel MII interface that can be configured for GMII, RGMII, or 10/100 MII. The device provides all required hardware support for high-accuracy time and frequency synchronization using the IEEE 1588 Precision Time Protocol. In both the transmit and receive directions 1588 packets are identified and timestamped with high precision. System software makes use of these timestamps to determine the time offset between the system and its timing master. Software can then correct any time error by steering the device's 1588 clock subsystem appropriately. The device provides the necessary I/O to time-synchronize with a 1588 master elsewhere in the same system or to be the master to which slave components can synchronize.

In addition, the MAX24288 is a full-featured, gigabit parallel-to-serial MII converter. It provides full SGMII revision 1.8 compliance and also interfaces directly to 1Gbps 1000BASE-X SFP optical modules.

# **Applications**

1588-Enabled Equipment with 1G Ethernet Ports Wireless Base Stations and Controllers Switches, Routers, DSLAMs, PON Equipment Pseudowire Circuit Emulation Equipment Test and Measurement Systems Industrial and Factory Automation Equipment Medical Equipment

# **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |  |

|--------------|----------------|-------------|--|

| MAX24288ETK+ | -40°C to +85°C | 68 TQFN-EP* |  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

Block Diagram appears on page 8.

Register Map appears on page 64.

# **Highlighted Features**

- **♦** Complete Hardware Support for IEEE 1588

- Ordinary, Boundary, and Transparent Clocks

- ♦ Flexible Block for Any 1588 Architecture

- ♦ 1588 Clock Hardware

- ♦ Steerable by Software with 2<sup>-8</sup>ns Time Resolution and 2<sup>-32</sup>ns Period Resolution

- ◆ 1ns Input Timestamp Accuracy and Output Edge Placement Accuracy

- Three Time/Frequency Controls: Direct Time Write, Time Adjustment, and High-Resolution Frequency Adjustment

- ♦ Programmable Clock and Time-Alignment I/O

- Input Event Timestamper Detects Incoming Time Alignment (e.g., 1 PPS) or Clock Edges

- Output Event Generator Provides Output Clock Signal or Time Alignment Signal

- Built-In Support for Telecom Equipment Timing Architecture with Dual Redundant Timing Cards

#### 1588 Timestamping Hardware

- ♦ 1588 v1 and v2 Packets, Transmit and Receive

- Packet Classifier Supports 1588 Over Ethernet, IPv4/UDP, IPv6/UDP, or MPLS, and Is Programmable for More Complex Stacks

- ♦ Supports 802.1Q VLAN Tags and MAC-in-MAC

- One-Step Operation: On-the-Fly Timestamp Insertion or Transparent Clock Corrections; No Need for Follow-Up Packets

- Can Insert All Timestamps, Receive and Transmit, Into Packets for Easy Software Access

- Optional Two-Step Operation

#### ♦ Parallel-to-Serial MII Conversion

- Bidirectional Wire-Speed Interface Conversion

- ◆ Serial: 1000BASE-X or SGMII v1.8 (4, 6, or 8 Pin)

- ◆ Parallel: GMII, RGMII, or 10/100 MII

- Translates Link Speed and Duplex Mode Negotiation Between MDIO and SGMII PCS

- ♦ Full Support for 1588 + Synchronous Ethernet

- **♦** MDIO and SPI™ Interfaces

- ♦ 1.2V Operation with 3.3V I/O

# **TABLE OF CONTENTS**

| 1. APPLICATION EXAMPLES                                  | 7  |

|----------------------------------------------------------|----|

| 2. BLOCK DIAGRAM                                         | 8  |

| 3. DETAILED FEATURES                                     | 8  |

| 4. ACRONYMS, ABBREVIATIONS, AND GLOSSARY                 | 10 |

| 5. PIN DESCRIPTIONS                                      |    |

| 6. FUNCTIONAL DESCRIPTION                                | 16 |

| 6.1 PIN CONFIGURATION DURING RESET                       | 16 |

| 6.2 GENERAL-PURPOSE I/O                                  |    |

| 6.2.1 Receive Recovered Clock Squelch Criteria           |    |

| 6.3 RESET, POWER DOWN AND PROCESSOR INTERRUPT            |    |

| 6.3.1 Reset.                                             |    |

| 6.3.2 Power Down                                         |    |

| 6.3.3 Processor Interrupts                               |    |

| 6.4 SPI - SERIAL PROCESSOR INTERFACE                     |    |

| 6.5 MDIO INTERFACE                                       |    |

| 6.5.1 MDIO Overview                                      |    |

| 6.5.2 Examples of MAX24288 and PHY Management Using MDIO | 25 |

| 6.6 SERIAL INTERFACE – 1000BASE-X OR SGMII               | 27 |

| 6.7 PARALLEL INTERFACE – GMII, RGMII, MII                | 28 |

| 6.7.1 GMII Mode                                          | 28 |

| 6.7.2 RGMII Mode                                         |    |

| 6.7.3 MII Mode                                           |    |

| 6.8 AUTO-NEGOTIATION (AN)                                |    |

| 6.8.1 1000BASE-X Auto-Negotiation                        |    |

| 6.8.2 SGMII Control Information Transfer                 |    |

| 6.9 DATA PATHS                                           |    |

| 6.9.1 Serial to Parallel Conversion and Decoding         |    |

| 6.9.2 Parallel to Serial Conversion and Encoding         |    |

| 6.10 TIMING PATHS                                        |    |

| 6.10.1 RX PLL                                            |    |

| 6.10.2 TX PLL                                            |    |

| 6.10.3 Input Jitter Tolerance                            |    |

| 6.10.4 Output Jitter Generation.                         |    |

| 6.10.5 TX PLL Jitter Transfer                            |    |

| 6.10.6 GPIO Pins as Clock Outputs                        |    |

| 6.11 LOOPBACKS                                           |    |

| 6.11.1 Diagnostic Loopback                               |    |

| 6.11.2 Terminal Loopback                                 |    |

| 6.11.3 Remote Loopback                                   | 39 |

| 6.12 DIAGNOSTIC AND TEST FUNCTIONS                       | 40 |

| 6.13 1588 HARDWARE                                       | 41 |

| 6.13.1 1588 Time Engine                                  |    |

| 6.13.2 Output Clock Generator                            |    |

| 6.13.3 Programmable Event Generators                     |    |

| 6.13.4 Input Signal Timestamping                         |    |

| 6.13.5 Packet Timestamping                               |    |

| 6.13.6 Packet Classification                             |    |

| 6.13.7 On-the-Fly Packet Modification                    | 54 |

| 6.13.8           | Circuit Emulation Timestamping for Adaptive Clock Recovery | 61 |

|------------------|------------------------------------------------------------|----|

| 6.14             | DATA PATH LATENCIES                                        | 62 |

| 6.15             | POWER SUPPLY CONSIDERATIONS.                               |    |

| 6.16             | STARTUP PROCEDURE                                          |    |

|                  |                                                            |    |

| 7. RE            | GISTER DESCRIPTIONS                                        | 64 |

| 7.1 R            | EGISTER MAP                                                | 64 |

|                  | RECT ACCESS REGISTERS                                      |    |

| 7.2.1            | BMCR                                                       |    |

| 7.2.1            | BMSR                                                       |    |

| 7.2.3            | ID1 and ID2                                                |    |

| 7.2.3            | AN ADV                                                     |    |

| 7.2.4            | AN RX                                                      |    |

| 7.2.6            | AN EXP                                                     |    |

| 7.2.7            | EXT STAT                                                   |    |

| 7.2.7            | JIT DIAG                                                   |    |

| 7.2.9            | PCSCR                                                      |    |

| 7.2.3            |                                                            |    |

| 7.2.10           |                                                            |    |

| 7.2.12           |                                                            |    |

| 7.2.12           |                                                            |    |

| 7.2.13           |                                                            |    |

|                  |                                                            |    |

| 7.2.15           |                                                            |    |

| 7.2.16<br>7.2.17 |                                                            |    |

|                  |                                                            |    |

| 7.2.18<br>7.2.19 |                                                            |    |

|                  |                                                            |    |

| 7.2.20           |                                                            |    |

| 7.2.21           | <del>-</del>                                               |    |

| 7.2.22           |                                                            |    |

| 7.2.23           |                                                            |    |

| 7.2.24           |                                                            |    |

| 7.2.25           |                                                            |    |

| 7.2.26           |                                                            |    |

| 7.2.27           |                                                            |    |

| 7.2.28           |                                                            |    |

| 7.2.29           |                                                            |    |

| 7.2.30           |                                                            |    |

| 7.2.31           |                                                            |    |

| 7.2.32           | <del>-</del>                                               |    |

| 7.2.33           |                                                            |    |

| 7.2.34           | <del>-</del>                                               |    |

| 7.2.35           |                                                            |    |

| 7.2.36           |                                                            |    |

| 7.2.37           |                                                            |    |

| 7.2.38           |                                                            |    |

| 7.2.39           |                                                            |    |

| 7.2.40           |                                                            |    |

| 7.2.41           | <del>-</del>                                               |    |

| 7.2.42           |                                                            |    |

| 7.2.43           | <del>-</del>                                               |    |

| 7.2.44           | <del>-</del>                                               |    |

| 7.2.45           | <del>-</del>                                               |    |

| 7.2.46           |                                                            |    |

| 7.2.47           |                                                            |    |

| 7.2.48           |                                                            |    |

| 7.2.49           |                                                            |    |

| 7250             | ) PHV MATCH                                                | QQ |

| 7.3 | IEE         | E1588 Indirect Registers                               | 100  |

|-----|-------------|--------------------------------------------------------|------|

| 7.  | 3.1         | TIME                                                   | 100  |

| 7.  | 3.2         | PERIOD                                                 | 100  |

| 7.  | 3.3         | PER_ADJ                                                | 100  |

| 7.  | 3.4         | ADJ_CNT                                                |      |

| 7.  | 3.5         | PEG1_FIFO, PEG2_FIFO                                   |      |

| 7.  | 3.6         | TS1_FIFO, TS2_FIFO, TS3_FIFO                           |      |

|     | 3.7         | MEAN_PATH_DELAY                                        |      |

| 7.  | 3.8         | CF_COR1, CF_COR2, CF_COR3                              |      |

|     | 3.9         | Configurable Packet Classifier Criteria                |      |

| 7.  | 3.10        | PTP_OFFSET                                             | 101  |

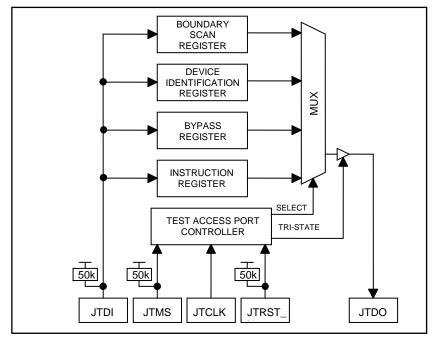

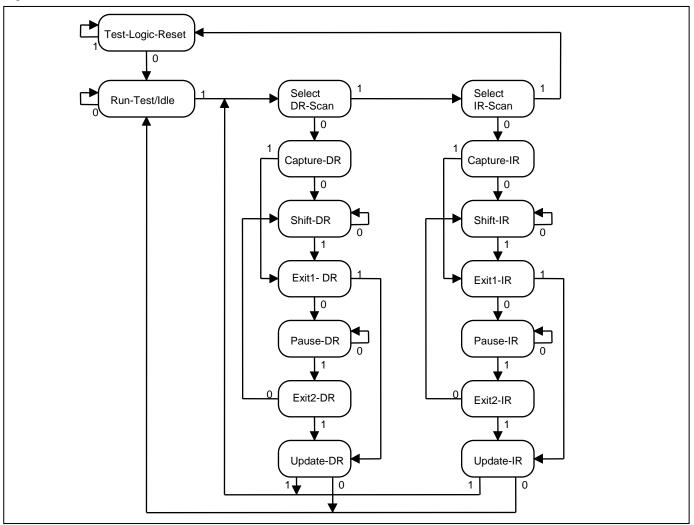

| 8.  | <b>JTAG</b> | TEST ACCESS PORT AND BOUNDARY SCAN                     | 102  |

| 8.1 | JTA         | G DESCRIPTION                                          | 102  |

| 8.2 |             | G TAP CONTROLLER STATE MACHINE DESCRIPTION             |      |

| 8.3 |             | G Instruction Register and Instructions                |      |

| 8.4 |             | G Test Registers                                       |      |

| 9.  | ELEC        | TRICAL CHARACTERISTICS                                 | 106  |

| 9.1 | REC         | COMMENDED OPERATING CONDITIONS                         | 106  |

| 9.2 |             | ELECTRICAL CHARACTERISTICS                             |      |

|     | 2.1         | CMOS/TTL DC Characteristics                            |      |

|     | 2.2         | SGMII/1000BASE-X DC Characteristics                    |      |

| 9.3 | AC          | ELECTRICAL CHARACTERISTICS                             |      |

|     | 3.1         | REFCLK AC Characteristics                              |      |

| 9.  | 3.2         | SGMII/1000BASE-X Interface Receive AC Characteristics  | 108  |

| 9.  | 3.3         | SGMII/1000BASE-X Interface Transmit AC Characteristics |      |

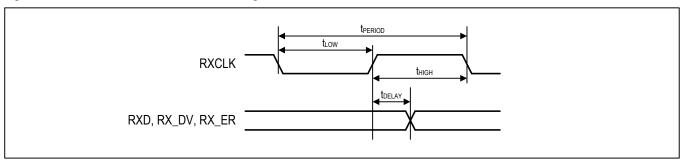

| 9.  | 3. <i>4</i> | Parallel Interface Receive AC Characteristics          | 110  |

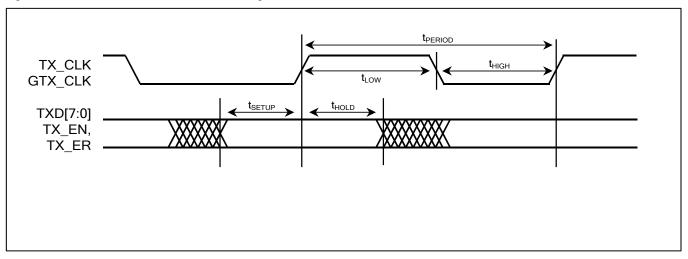

| 9.  | 3.5         | Parallel Interface Transmit AC Characteristics         | 112  |

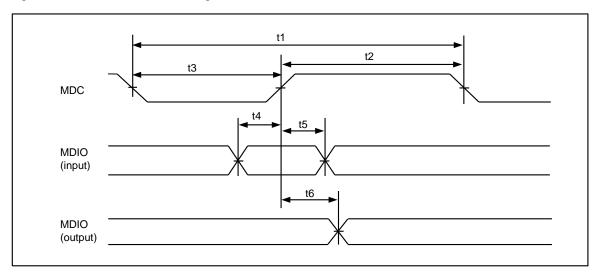

| 9.  | 3.6         | MDIO Interface AC Characteristics                      |      |

|     | 3.7         | SPI Interface AC Characteristics                       |      |

|     | 3.8         | JTAG Interface AC Characteristics                      |      |

| 9.  | 3.9         | 1588 GPIO Propagation Delays                           |      |

| 9.  | 3.10        | Packet Timestamp Latencies                             | 118  |

| 10. | PIN A       | SSIGNMENTS                                             | 119  |

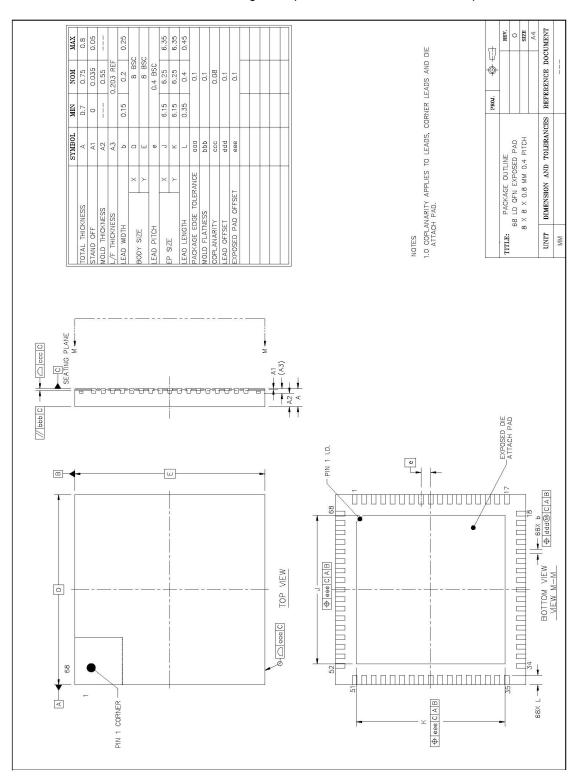

| 11. | PACK        | AGE AND THERMAL INFORMATION                            | 120  |

| 12. | DΔTΔ        | SHEET REVISION HISTORY                                 | 121  |

|     | -/\\/       |                                                        | 14-1 |

# **TABLE OF FIGURES**

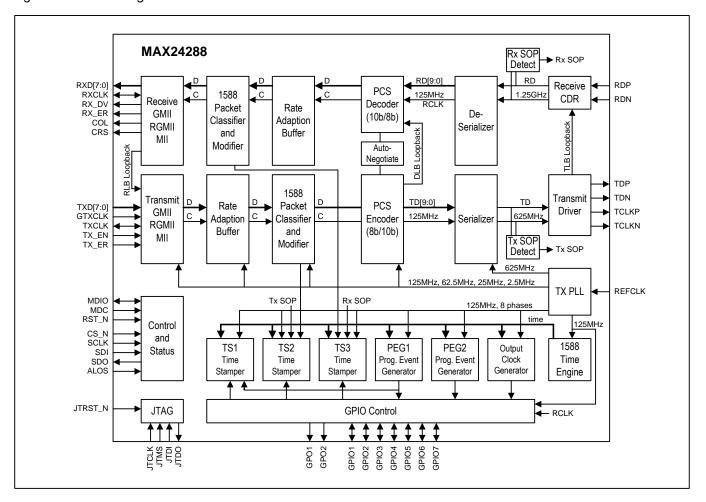

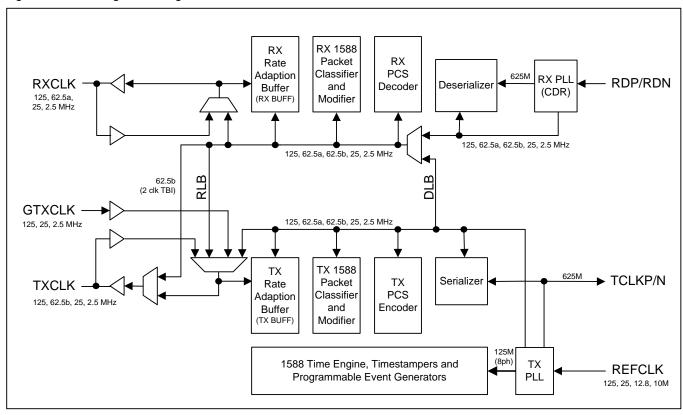

| Figure 2-1. Block Diagram                                                        | 8   |

|----------------------------------------------------------------------------------|-----|

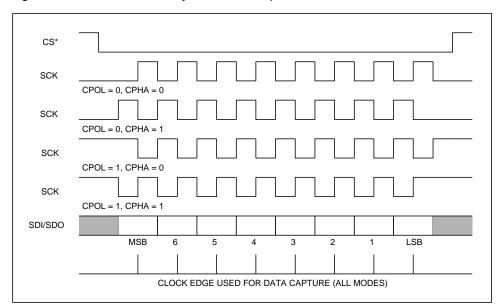

| Figure 6-1. SPI Clock Polarity and Phase Options                                 | 21  |

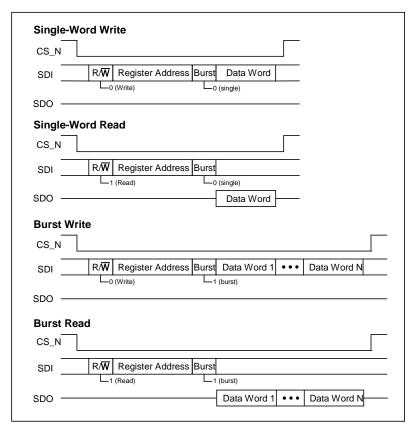

| Figure 6-2. SPI Bus Transactions                                                 |     |

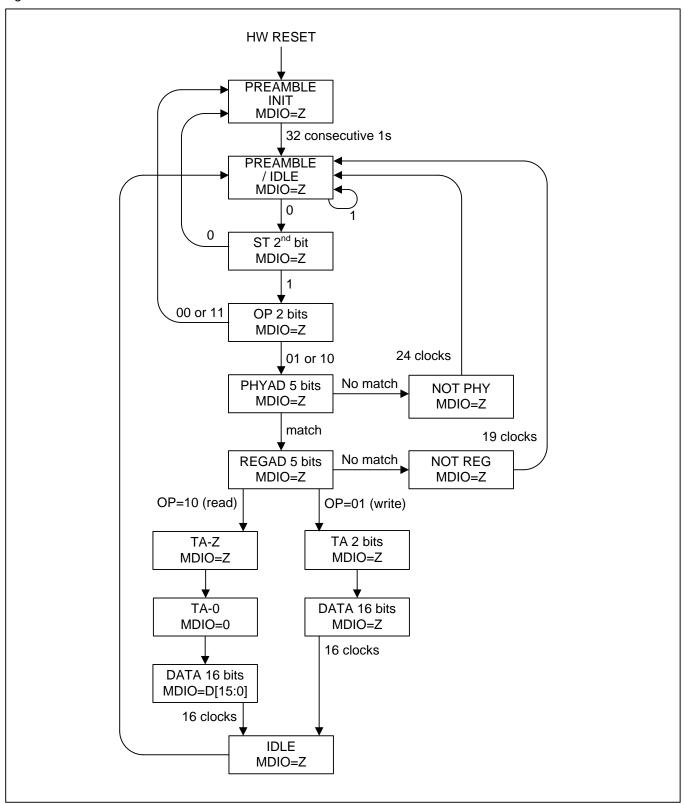

| Figure 6-3. MDIO Slave State Machine                                             | 24  |

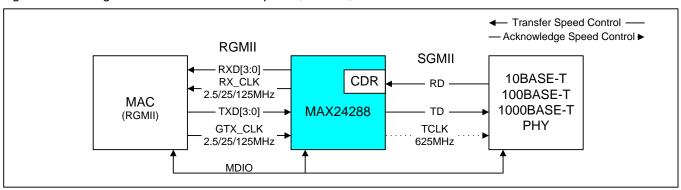

| Figure 6-4. Management Information Flow Options, Case 1,Tri-Mode PHY             | 25  |

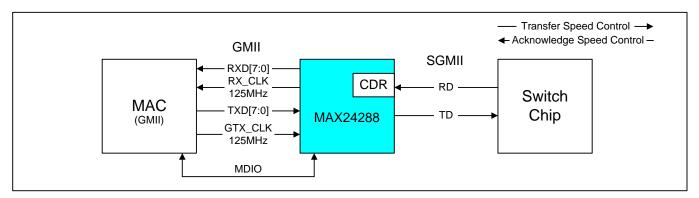

| Figure 6-5. Management Information Flow Options, Case 2, SGMII Switch Chip       | 25  |

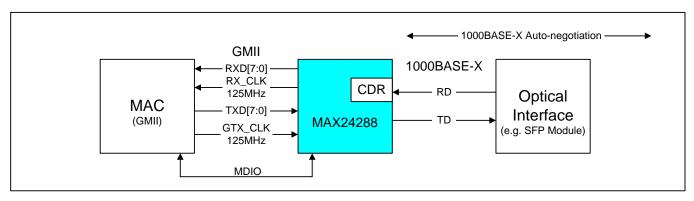

| Figure 6-6. Management Information Flow Options, Case 3, 1000BASE-X Interface    | 26  |

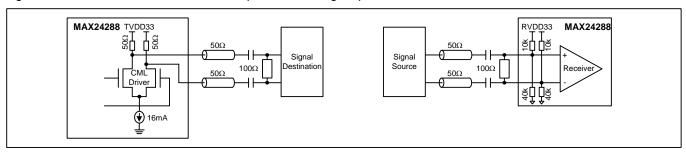

| Figure 6-7. Recommended External Components for High-Speed Serial Interface      | 27  |

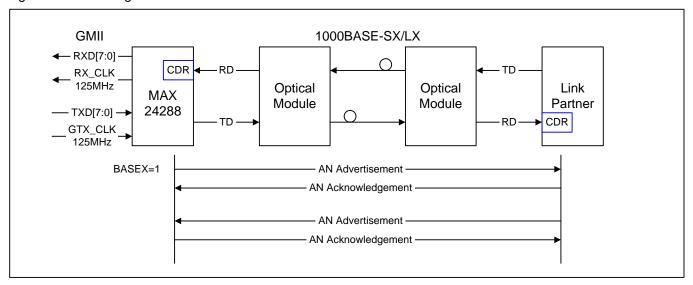

| Figure 6-8. Auto-Negotiation with a Link Partner over 1000BASE-X                 | 32  |

| Figure 6-9. 1000BASE-X Auto-Negotiation tx_Config_Reg and rx_Config_Reg Fields   | 32  |

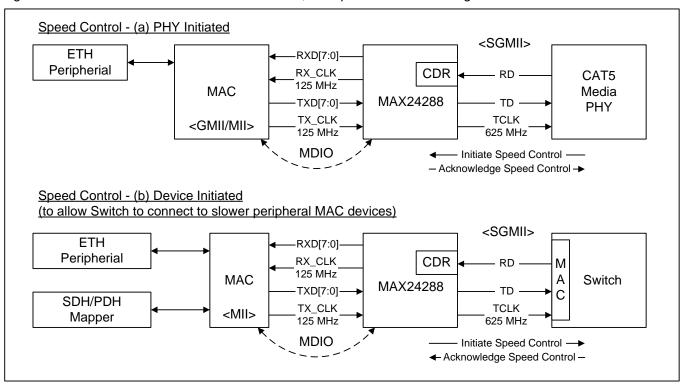

| Figure 6-10. SGMII Control Information Generation, Reception and Acknowledgement | 34  |

| Figure 6-11. SGMII tx_Config_Reg and rx_Config_Reg Fields                        | 34  |

| Figure 6-12. Timing Path Diagram                                                 | 37  |

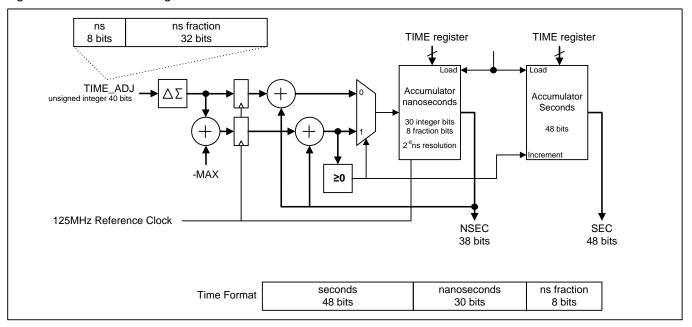

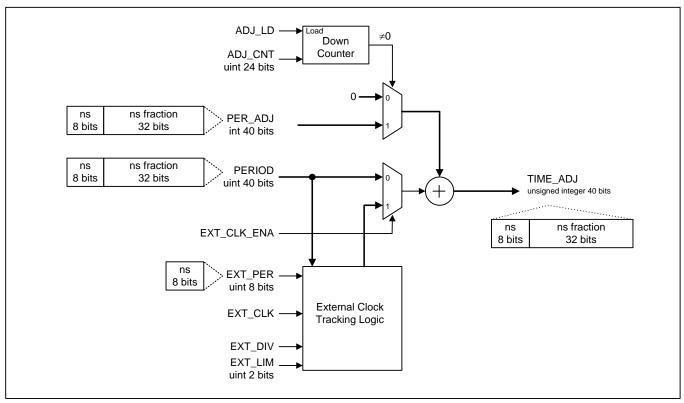

| Figure 6-13. 1588 Time Engine                                                    | 42  |

| Figure 6-14. Time Engine Period Generator                                        | 42  |

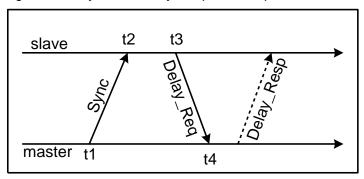

| Figure 6-15. Sync and Delay_Req Tmestamp Points                                  | 56  |

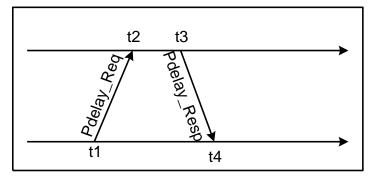

| Figure 6-16. Pdelay Timestamp Points                                             | 57  |

| Figure 8-1. JTAG Block Diagram                                                   |     |

| Figure 8-2. JTAG TAP Controller State Machine                                    | 104 |

| Figure 9-1. MII/GMII/RGMII Receive Timing Waveforms                              |     |

| Figure 9-2. MII/GMII/RGMII Transmit Timing Waveforms                             | 112 |

| Figure 9-3. MDIO Interface Timing                                                | 114 |

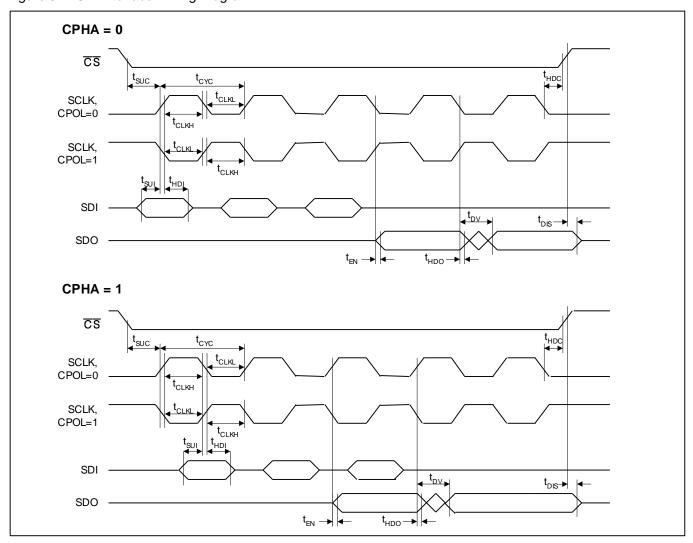

| Figure 9-4. SPI Interface Timing Diagram                                         | 116 |

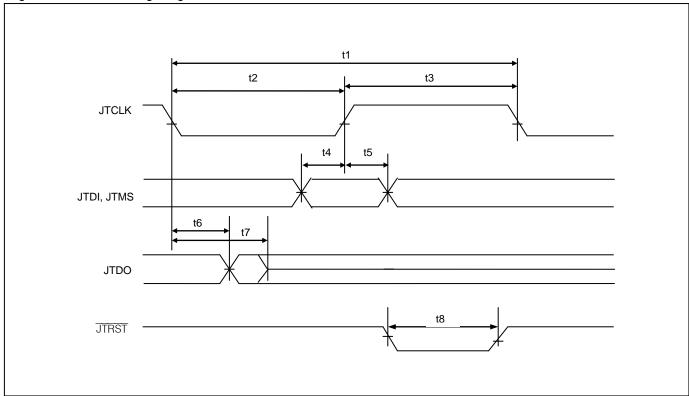

| Figure 9-5. JTAG Timing Diagram                                                  | 117 |

|                                                                                  |     |

|                                                                                  |     |

# TABLE OF TABLES

| Table 5-1. Pin Type Descriptions                                                       | 10 |

|----------------------------------------------------------------------------------------|----|

| Table 5-2. Detailed Pin Descriptions – Global Pins (2 Pins)                            | 10 |

| Table 5-3. Detailed Pin Descriptions – MDIO Interface (2 Pins)                         | 11 |

| Table 5-4. Detailed Pin Descriptions – SPI Interface (4 pins)                          | 11 |

| Table 5-5. Detailed Pin Descriptions – JTAG Interface (5 pins)                         | 11 |

| Table 5-6. Detailed Pin Descriptions – GPIO signals (5 dedicated pins, 4 shared pins)  | 12 |

| Table 5-7. Detailed Pin Descriptions – SGMII/1000BASE-X Serial Interface (7 pins)      | 13 |

| Table 5-8. Detailed Pin Descriptions – Parallel Interface (25 pins)                    | 13 |

| Table 5-9. Detailed Pin Descriptions – Power and Ground Pins (15 pins)                 | 15 |

| Table 6-1. Reset Configuration Pins, 15-Pin Mode (COL=0)                               | 16 |

| Table 6-2. Parallel Interface Configuration                                            | 16 |

| Table 6-3. Reset Configuration Pins, 3-Pin Mode (COL=1)                                | 17 |

| Table 6-4. GPO1, GPIO1 and GPIO3 Configuration Options                                 |    |

| Table 6-5. GPO2 and GPIO2 Configuration Options                                        | 17 |

| Table 6-6. GPIO4, GPIO5, GPIO6 and GPIO7 Configuration Options                         | 18 |

| Table 6-7. Parallel Interface Modes                                                    | 28 |

| Table 6-8. GMII Parallel Bus Pin Naming                                                |    |

| Table 6-9. RGMII Parallel Bus Pin Naming                                               |    |

| Table 6-10. MII Parallel Bus Pin Naming                                                |    |

| Table 6-11. AN_ADV 1000BASE-X Auto-Negotiation Ability Advertisement Register (MDIO 4) |    |

| Table 6-12. AN_RX 1000BASE-X Auto-negotiation Ability Receive Register (MDIO 5)        |    |

| Table 6-13. AN_ADV SGMII Configuration Information Register (MDIO 4)                   |    |

| Table 6-14. AN_RX SGMII Configuration Information Receive Register (MDIO 5)            |    |

| Table 6-15. Timing Path Muxes – No Loopback                                            | 37 |

| Table 6-16. Timing Path Muxes – DLB Loopback                                   | 37  |

|--------------------------------------------------------------------------------|-----|

| Table 6-17. Timing Path Muxes – RLB Loopback                                   | 38  |

| Table 6-18. PEG Command FIFO Fields                                            | 44  |

| Table 6-19. PEG Commands                                                       | 45  |

| Table 6-20. Common Frequencies Using Repeat Command                            | 46  |

| Table 6-21. Common Frequencies Using Fractional Clock Synthesis Repeat Command |     |

| Table 6-22. Configurable Packet Classifier Start Positions                     | 51  |

| Table 6-23. One-Step/On-the-Fly Selection Matrix                               | 54  |

| Table 6-24. Ethernet and IP Multicast Addresses to Check                       | 61  |

| Table 6-25. Source of Unicast Addresses to Overwrite Multicast                 | 61  |

| Table 6-26. GMII Data Path Latencies                                           | 62  |

| Table 7-1. PHY Register Map (MDIO Only)                                        |     |

| Table 7-2. 1588 Register Map (MDIO or SPI)                                     | 65  |

| Table 7-3. TEIO Register Mapping to RDSEL Sources                              | 82  |

| Table 7-4. TEIO Register Mapping to WRSEL Destinations                         | 82  |

| Table 8-1. JTAG Instruction Codes                                              |     |

| Table 8-2. JTAG ID Code                                                        |     |

| Table 9-1. Recommended DC Operating Conditions                                 |     |

| Table 9-2. DC Characteristics                                                  | 106 |

| Table 9-3. DC Characteristics for Parallel, MDIO and SPI Interfaces            |     |

| Table 9-4. SGMII/1000BASE-X Transmit DC Characteristics                        |     |

| Table 9-5. SGMII/1000BASE-X Receive DC Characteristics                         |     |

| Table 9-6. REFCLK AC Characteristics                                           |     |

| Table 9-7. 1000BASE-X and SGMII Receive AC Characteristics                     |     |

| Table 9-8. 1000BASE-X and SGMII Receive Jitter Tolerance                       |     |

| Table 9-9. SGMII and 1000BASE-X Transmit AC Characteristics                    |     |

| Table 9-10. 1000BASE-X Transmit Jitter Characteristics                         |     |

| Table 9-11. GMII Receive AC Characteristics                                    |     |

| Table 9-12. RGMII-1000 Receive AC Characteristics                              |     |

| Table 9-13. RGMII-10/100 Receive AC Characteristics                            |     |

| Table 9-14. MII–DCE Receive AC Characteristics                                 |     |

| Table 9-15. MII–DTE Receive AC Characteristics                                 |     |

| Table 9-16. GMII and RGMII-1000 Transmit AC Characteristics                    |     |

| Table 9-17. RGMII-10/100 Transmit AC Characteristics                           |     |

| Table 9-18. MII–DCE Transmit AC Characteristics                                |     |

| Table 9-19. MII–DTE Transmit AC Characteristics                                |     |

| Table 9-20. MDIO Interface AC Characteristics                                  |     |

| Table 9-21. SPI Interface Timing                                               |     |

| Table 9-22. JTAG Interface Timing                                              |     |

| Table 9-23. 1588 GPIO Propagation Delays                                       |     |

| Table 9-24. Transmit/Egress Packet Timestamp to First Bit After SFD on TDP/TDN |     |

| Table 9-25. Receive/Ingress First Bit After SFD on RDP/RDN to Packet Timestamp |     |

| Table 11-1. Package Thermal Properties, Natural Convection                     | 121 |

# 1. Application Examples

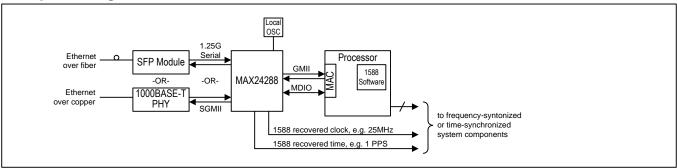

## Example 1: Single-Port 1588 Slave Node

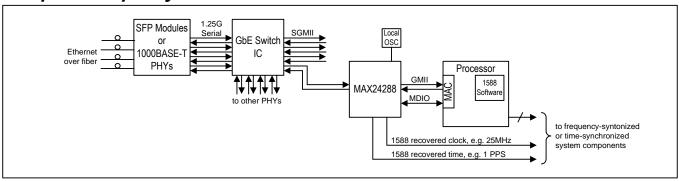

#### Example 2: Multiport System with Switch-Connected 1588 Slave Node

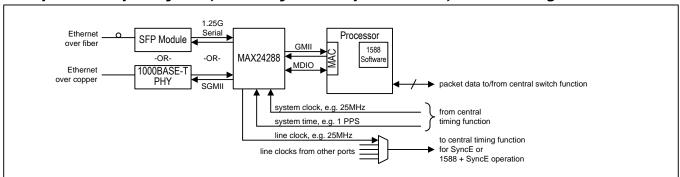

## Example 3: Multiport System, Boundary or Transparent Clock, Port Card Logic

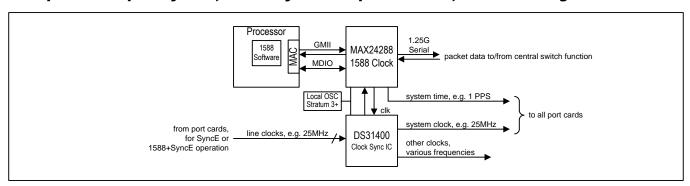

# Example 4: Multiport System, Boundary or Transparent Clock, Central Timing Function

# 2. Block Diagram

Figure 2-1. Block Diagram

#### 3. Detailed Features

#### **General Features**

- Control and status through MDIO interface or SPI interface

- High-speed MDIO interface (12.5MHz slave only) with optional preamble suppression

- Optional SPI 4-wire serial microprocessor interface (25MHz, slave only)

- Operates from a 10, 12.8, 25 or 125MHz reference clock

- Optional 125MHz output clock for MAC to use as GTXCLK

#### Parallel-Serial MII Conversion Features

- Bidirectional wire-speed interface conversion

- Serial Interface: 1000BASE-X or SGMII revision 1.8 (4-, 6- or 8-Pin)

- Parallel Interface: GMII, RGMII (10, 100 and 1000Mbps) or 10/100 MII (DTE or DCE)

- 8-pin source-clocked SGMII mode

- 4-pin 1000BASE-X SERDES mode to interface with optical modules

- Connects processors with parallel MII interfaces to 1000BASE-X SFP optical modules

- Connects processors with parallel MII interfaces to PHY or switch ICs with SGMII interfaces

- Interface conversion is transparent to MAC layer and higher layers

Translates link speed and duplex mode between GMII/MII MDIO and SGMII PCS

#### 1588 Clock Features

- Steerable by software with 2<sup>-8</sup>ns time resolution and 2<sup>-32</sup>ns period resolution

- 1ns input timestamp accuracy and output edge placement accuracy

- Initialized and steered by software on an external processor to follow an external 1588 master

- Three time/frequency controls: direct time write, time adjustment, and high-resolution frequency adjustment

- Programmable clock and time-alignment I/O to synchronize all boards in large systems

- o Can frequency-lock to an input clock signal from elsewhere in the system

- Can timestamp an input time alignment signal to time-lock to a master elsewhere in the system (e.g. 1 PPS)

- o Can provide an output clock signal to slave components elsewhere in the system (125MHz / N , 1≤N≤255)

- o Can provide an output time alignment signal to slave components elsewhere in the system (e.g. 1 PPS)

- Input signal timestamper can stamp rising edges, falling edges or both

- Flexible programmable event generator (PEG) can output 1 PPS, one pulse per period, and a wide variety of clock signals

- Full support for dual redundant timing cards to match architecture used in SONET/SDH

- Full support for switches and routers as transparent clocks or boundary clocks

- Compatible with a wide variety of 1588 system architectures

# 1588 Timestamper Features

- Identifies and timestamps 1588 v1 and v2 packets in both transmit and receive directions

- Programmable packet classifier can identify packets transported by a variety of protocol stacks

- o 1588 over Ethernet

- o 1588 over IPv4/UDP

- o 1588 over IPv6/UDP

- o 1588 over MPLS

- Configurable for more complex stacks as well

- o Recognizes 802.1Q VLAN tags and 802.1ah MAC-in-MAC

- o Can be configured to identify CESoP or SAToP for timing over adaptive-mode circuit emulation

- Transmit and receive timestamping with 1ns resolution

- One-step operation minimizes network bandwidth consumption

- On-the-fly timestamp insertion

- On-the-fly corrections in transparent clocks

- No need for follow-up packets

- Can insert ALL timestamps (receive and transmit) into packets for easy software access

- Three insert methods: direct overwrite, read-add-write, and read-subtract-write

- o Eliminates reads from timestamp FIFOs

- Minimizes processor bus traffic

- Optional two-step operation

- Optional 8-entry timestamp FIFOs

#### Synchronous Ethernet Features

- Full support for 1588 over Synchronous Ethernet

- Receive path bit clock can be output on a GPIO pin to line-time the system from the Ethernet port

- Transmit path can be frequency-locked to a system clock signal connected to the REFCLK pin

# 4. Acronyms, Abbreviations, and Glossary

BC Boundary Clock

DCE Data Communication Equipment

DDR Dual Data Rate (data driven and latched on both clock edges)

DTE Data Terminating Equipment

E2E End to EndOC Ordinary ClockP2P Peer to Peer

PCB Printed Circuit Board

PHY Physical. Refers to either a transceiver device or a protocol layer

• PTP Precision Time Protocol – IEEE1588

• TC Transparent Clock

Ingress The serial (SGMII) to parallel (GMII) direction

Egress The parallel (GMII) to serial (SGMII) direction

Receive The serial (SGMII) to parallel (GMII) direction

Transmit The parallel (GMII) to serial (SGMII) direction

# 5. Pin Descriptions

Note that some pins have different pin names and functions under different configurations.

Table 5-1. Pin Type Descriptions

| Type  | Definition                            |  |  |

|-------|---------------------------------------|--|--|

| I     | Input                                 |  |  |

| Idiff | Input differential                    |  |  |

| IO    | Bi-directional                        |  |  |

| IOr   | Bi-directional, sampled at reset      |  |  |

| lOz   | Bi-directional, can go high impedance |  |  |

| 0     | Output                                |  |  |

| Odiff | Output, differential (CML)            |  |  |

| Oz    | Output, can go hi impedance           |  |  |

Table 5-2. Detailed Pin Descriptions – Global Pins (2 Pins)

| Pin Name | PIN# | Type | Pin Description                                                                                                                                                                                                                                                                      |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_N    | 67   | I    | Reset (active low, asynchronous) This signal resets all logic, state machines and registers in the device. Pin states are sampled and used to set the default values of several register fields as described in 6.1. RST_N should be held low for at least 100μs. See section 6.3.1. |

| Pin Name | PIN# | Туре | Pin Description                                                                                                                                                                                                                                                                         |

|----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK   | 68   | I    | Reference Clock This signal is the reference clock for the device. The frequency can be 10MHz, 12.8MHz, 25MHz or 125MHz ± 100 ppm. At reset the frequency is specified using the RXD[3:2] pins (see section 6.1). The REFCLK signal is the input clock to the TX PLL. See section 6.10. |

|          |      |      | Note: REFCLK frequency cannot be changed dynamically among the frequencies listed above. To change REFCLK frequency, (1) power down MAX24288, (2) change REFCLK frequency, then (3) power up MAX24288.                                                                                  |

|          |      |      | REFCLK is an analog input that is internally biased with a $10k\Omega$ resistor to 1.2V. This support AC-coupling if desired.                                                                                                                                                           |

Table 5-3. Detailed Pin Descriptions – MDIO Interface (2 Pins)

| Pin Name | PIN# | Туре | Pin Description                                                                  |

|----------|------|------|----------------------------------------------------------------------------------|

| MDC      | 41   |      | MDIO Clock.                                                                      |

|          |      |      | MDC is the clock signal of the 2-wire MDIO interface. It can be any frequency up |

|          |      |      | to 12.5MHz. See section 6.5.                                                     |

| MDIO     | 42   | lOz  | MDIO Data.                                                                       |

|          |      |      | This is the bidirectional, half-duplex data signal of the MDIO interface. It is  |

|          |      |      | sampled and updated on positive edges of MDC. IEEE 802.3 requires a 2kΩ±5%       |

|          |      |      | pulldown resistor on this signal at the MAC. See section 6.5.                    |

Table 5-4. Detailed Pin Descriptions - SPI Interface (4 pins)

| Pin Name | PIN# | Type | Pin Description                                                                                                                                                                                                                                                    |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK     | 64   | I    | SPI Clock Input.  SCLK can be any frequency up to 25MHz. By default, SDI and CS_N are sampled on the rising edge of SCLK, and SDO is updated on the falling edge of SCLK. The edge polarity and phase can be changed using PAGESEL.CPHA and CPOL. See section 6.4. |

| CS_N     | 45   | I    | SPI Chip Select. This signal must be asserted (low) to read or write internal registers using the SPI interface. See section 6.4.                                                                                                                                  |

| SDI      | 63   | I    | SPI Data Input. The SPI bus master transmits data to the device on this pin. See section 6.4.                                                                                                                                                                      |

| SDO      | 62   | Oz   | SPI Data Output.  The device transmits data to the SPI bus master on this pin. SDO is high impedance until a read command is clocked into the device on the SDI pin. SDO then outputs the data values and returns to high impedance. See section 6.4.              |

Table 5-5. Detailed Pin Descriptions – JTAG Interface (5 pins)

| Pin Name | PIN# | Type | Pin Description                                                                                                                                                                                                                       |

|----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTRST_N  | 43   | I    | JTAG Test Reset (active low). Asynchronously resets the test access port (TAP) controller. JTRST_N should be held low during device power-up. If not used, JTRST_N can be held low or high after power-up. See section 8.             |

| JTCLK    | 21   | I    | JTAG Test Clock.  This clock signal can be any frequency up to 10MHz. JTDI and JTMS are sampled on the rising edge of JTCLK, and JTDO is updated on the falling edge of JTCLK. If not used, connect to DVDD33 or DVSS. See section 8. |

| JTMS     | 22   | I    | JTAG Test Mode Select.  Sampled on the rising edge of JTCLK. Used to place the port into the various defined IEEE 1149.1 states. If not used, connect to DVDD33. See section 8.                                                       |

| Pin Name | PIN# | Туре | Pin Description                                                                    |

|----------|------|------|------------------------------------------------------------------------------------|

| JTDI     | 23   | ı    | JTAG Test Data Input.                                                              |

|          |      |      | Test instructions and data are clocked in on this pin on the rising edge of JTCLK. |

|          |      |      | If not used, connect to DVDD33. See section 8.                                     |

| JTDO     | 44   | Oz   | JTAG Test Data Output.                                                             |

|          |      |      | Test instructions and data are clocked out on this pin on the falling edge of      |

|          |      |      | JTCLK. If not used leave unconnected. See section 8.                               |

Table 5-6. Detailed Pin Descriptions – GPIO signals (5 dedicated pins, 4 shared pins)

| Pin Name     | PIN# | Туре | Pin Description                                                                                                                                                                                                                                                                                       |  |

|--------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPO1         | 24   | lOr  | General Purpose Output 1.  After reset, default behavior is to output a signal that indicates link status, 0=link down, 1=link up.  The function can be changed after reset. See section 6.2.                                                                                                         |  |

| GPO2         | 25   | lOr  | General Purpose Output 2.  After reset, default behavior is to output the CRS (carrier sense) signal.  The function can be changed after reset. See section 6.2.                                                                                                                                      |  |

| GPIO1        | 61   | lOz  | General Purpose Input or Output 1.  After reset this pin can be either high impedance or generating a 125MHz clock signal.  GPO1=0 at reset: After reset, GPIO1 is high impedance.  GPO1=1 at reset: After reset, GPIO1 is 125MHz clock out The function can be changed after reset. See section 6.2. |  |

| GPIO2        | 60   | lOz  | General Purpose Input or Output 2.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                                                                                                                                 |  |

| GPIO3        | 59   | IOz  | General Purpose Input or Output 3.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                                                                                                                                 |  |

| GPIO4/TXD[4] | 52   | lOz  | General Purpose Input or Output 4.  Available for use as a GPIO pin when the parallel interface is configured for MII or RGMII modes.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                              |  |

| GPIO5/TXD[5] | 53   | lOz  | General Purpose Input or Output 5.  Available for use as a GPIO pin when the parallel interface is configured for MII or RGMII modes.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                              |  |

| GPIO6/TXD[6] | 54   | lOz  | General Purpose Input or Output 6.  Available for use as a GPIO pin when the parallel interface is configured for MII or RGMII modes.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                              |  |

| GPIO7/TXD[7] | 55   | lOz  | General Purpose Input or Output 7.  Available for use as a GPIO pin when the parallel interface is configured for MII or RGMII modes.  After reset this pin is high impedance. The function can be changed after reset. See section 6.2.                                                              |  |

Table 5-7. Detailed Pin Descriptions – SGMII/1000BASE-X Serial Interface (7 pins)

| Pin Name | PIN# | Туре  | Pin Description                                                                |

|----------|------|-------|--------------------------------------------------------------------------------|

| TDP,     | 9    | Odiff | Transmit Data Output                                                           |

| TDN      | 8    |       | These pins form a differential CML output for the 1.25Gbaud SGMII transmit     |

|          |      |       | signal to a neighboring 1000BASE-X optical module (SFP, etc.) or PHY with      |

|          |      |       | SGMII interface. See section 6.6.                                              |

| TCLKP,   | 6    | Odiff | Transmit Clock Output                                                          |

| TCLKN    | 5    |       | These pins form a differential CML output for an optional 625MHz clock for     |

|          |      |       | the SGMII transmit signal on TDP/TDN. This output is disabled at reset but is  |

|          |      |       | enabled by setting CR.TCLK_EN=1. See section 6.6.                              |

| RDP,     | 13   | ldiff | Receive Data Input                                                             |

| RDN      | 14   |       | These pins form a differential input for the 1.25Gbaud SGMII receive signal    |

|          |      |       | from a neighboring 1000BASE-X optical module (SFP, etc.) or PHY with           |

|          |      |       | SGMII interface. A receive clock signal is not necessary because the device    |

|          |      |       | uses a built-in CDR to recover the receive clock from the signal on RDP/RDN.   |

| 41.00    | 40   |       | See section 6.6.                                                               |

| ALOS     | 19   | l     | Analog Loss of Signal                                                          |

|          |      |       | This pin receives analog loss-of-signal from a neighboring optical transceiver |

|          |      |       | module. If the optical module does not have an ALOS output, this pin should    |

|          |      |       | be connected to DVSS for proper operation. See section 6.6.                    |

|          |      |       | 0 = ALOS not detected or not required, normal operation                        |

|          |      |       | 1 = ALOS detected, loss of signal                                              |

Table 5-8. Detailed Pin Descriptions – Parallel Interface (25 pins)

| Pin Name | PIN# | Туре | Pin Description                                                                                                                                     |

|----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| RXCLK    | 40   | Ю    | Receive Clock In all modes the frequency tolerance is ± 100 ppm.                                                                                    |

|          |      |      | GMII Mode: RXCLK is the 125MHz receive clock.                                                                                                       |

|          |      |      | RGMII Modes: RXCLK is the 125MHz (RGMII-1000), 25MHz (RGMII-100) or 2.5MHz (RGMII-10) receive clock (DDR).                                          |

|          |      |      | MII Mode: RXCLK is the 25MHz (100Mbps MII) or 2.5MHz (10Mbps MII) receive clock.                                                                    |

|          |      |      | In DTE mode (DTE_DCE)=1, RXCLK is an input. In DCE mode (DTE_DCE)=0, RXCLK is an output.                                                            |

| RXD[0]   | 38   | lOr  | Receive Data Outputs                                                                                                                                |

| RXD[1]   | 37   | lOr  | During reset these pins are configuration inputs. See section 6.1. After reset they are driven as outputs.                                          |

| RXD[2]   | 36   | lOr  | GMII Mode: receive_data[7:0] is output on RXD[7:0] on the rising edge of RXCLK.                                                                     |

| RXD[3]   | 35   | IOr  | 1002.0                                                                                                                                              |

| RXD[4]   | 34   | lOr  | MII Mode, RGMII-10 and RGMII-100 Modes: receive_data[3:0] is output on RXD[3:0] on the rising edge of RXCLK. RXD[7:4] are high impedance.           |

| RXD[5]   | 33   | lOr  | RGMII-1000 Mode: receive_data[3:0] is output on RXD[3:0] on the rising edge of RXCLK, and receive_data[7:4] is output on the falling edge of RXCLK. |

| RXD[6]   | 32   | IOr  | RXD[7:4] are high impedance.                                                                                                                        |

| RXD[7]   | 31   | lOr  |                                                                                                                                                     |

| Pin Name | PIN# | Туре | Pin Description                                                                                                                                                                                                                                                                                                                            |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_DV    | 29   | lOr  | Receive Data Valid  During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.                                                                                                                                                                                                                |

|          |      |      | MII Mode and GMII Mode: RX_DV is output on the rising edge of RXCLK.                                                                                                                                                                                                                                                                       |

|          |      |      | RGMII Modes: The RX_CTL signal is output on RX_DV on both edges of RXCLK.                                                                                                                                                                                                                                                                  |

| RX_ER    | 28   | IOr  | Receive Error  During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.                                                                                                                                                                                                                     |

|          |      |      | MII Mode and GMII Mode: RX_ER is output on the rising edge of RXCLK.                                                                                                                                                                                                                                                                       |

|          |      |      | RGMII Mode: RX_ER pin is high impedance.                                                                                                                                                                                                                                                                                                   |

| COL      | 27   | IOr  | Collision Detect  During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.                                                                                                                                                                                                                  |

|          |      |      | COL indicates that a Tx/Rx collision is occurring. It is meaningful only in half duplex operation. It is asynchronous to any of the clocks. COL is driven low at all times when BMCR.DLB=1 and BMCR.COL_TEST=0. When BMCR.DLB=1 and BMCR.COL_TEST=1, COL behaves as described in the COL_TEST bit description.  1 = Collision is occurring |

| CDC      | 00   | 10-  | 0 = Collision is not occurring  Carrier Sense                                                                                                                                                                                                                                                                                              |

| CRS      | 26   | IOr  | During reset this pin is a configuration input. See section 6.1. After reset it is driven as an output.                                                                                                                                                                                                                                    |

|          |      |      | CRS is asserted by the device when either the transmit data path or the receive data path is active. This signal is asynchronous to any of the clocks.                                                                                                                                                                                     |

| TXCLK    | 46   | Ю    | MII Transmit Clock When TXCLK is an input, frequency tolerance is ±100ppm.                                                                                                                                                                                                                                                                 |

|          |      |      | MII Mode: TXCLK is the 25MHz (100Mbps MII) or 2.5MHz 10Mbps MII) transmit clock.                                                                                                                                                                                                                                                           |

|          |      |      | In DTE mode (DTE_DCE)=1, TXCLK is an input. In DCE mode (DTE_DCE)=0, TXCLK is an output.                                                                                                                                                                                                                                                   |

|          |      |      | GMII Mode and RGMII Mode: TXCLK can output a 125MHz clock for use by neighboring components (e.g. a MAC) when GMIICR.TXCLK_EN=1 (or TXCLK=1 at reset).                                                                                                                                                                                     |

| GTXCLK   | 66   | I    | GMII/RGMII Transmit Clock In all modes the frequency tolerance is ± 100ppm.                                                                                                                                                                                                                                                                |

|          |      |      | GMII Mode: GTXCLK is the 125MHz transmit clock.                                                                                                                                                                                                                                                                                            |

|          |      |      | RGMII Modes: GTXCLK is the 125MHz (RGMII-1000), 25MHz (RGMII-100) or 2.5MHz (RGMII-10) transmit clock (DDR).                                                                                                                                                                                                                               |

|          |      |      | MII Mode: This pin is not used and should be pulled low. See the TXCLK pin description.                                                                                                                                                                                                                                                    |

| Pin Name     | PIN# | Туре | Pin Description                                                                                                                                                   |

|--------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXD[0]       | 48   | I    | Transmit Data Inputs                                                                                                                                              |

| TXD[1]       | 49   | I    | Depending on the parallel MII interface mode, four or eight of these pins are used to accept transmit data from a neighboring component.                          |

| TXD[2]       | 50   | I    | GMII Mode: The rising edge of GTXCLK latches transmit_data[7:0] from TXD[7:0].                                                                                    |

| TXD[3]       | 51   | I    |                                                                                                                                                                   |

| TXD[4]/GPIO4 | 52   | IOz  | MII Mode, RGMII-10 and RGMII-100 Modes: The rising edge of TXCLK (MII) or GTXCLK (RGMII) latches transmit_data[3:0] from TXD[3:0]. TXD[7:4] become GPIO7 – GPIO4. |

| TXD[5]/GPIO5 | 53   | lOz  | TABILITY DESCRIBE OF THE IT                                                                                                                                       |

| TXD[6]/GPIO6 | 54   | IOz  | RGMII-1000 Mode: The rising edge of GTXCLK latches transmit_data[3:0] from TXD[3:0]. The falling edge of GTXCLK latches transmit_data[7:4] from TXD[3:0].         |

| TXD[7]/GPIO7 | 55   | IOz  | TXD[7:4] become GPIO7 – GPIO4.                                                                                                                                    |

| TX_EN        | 57   | I    | Transmit Enable                                                                                                                                                   |

|              |      |      | MII Mode and GMII Mode: The rising edge of TXCLK (MII) or GTXCLK (GMII) latches the TX_EN signal from this pin.                                                   |

|              |      |      | RGMII Modes: Both edges of GTXCLK latch the TX_CTL signal from this pin.                                                                                          |

| TX_ER        | 58   | I    | Transmit Error                                                                                                                                                    |

|              |      |      | MII Mode and GMII Mode: The rising edge of TXCLK (MII) or GTXCLK (GMII) latches the TX_ER signal from this pin.                                                   |

|              |      |      | RGMII Modes: This pin is not used.                                                                                                                                |

Table 5-9. Detailed Pin Descriptions – Power and Ground Pins (15 pins)

| Pin Name    | PIN#       | Pin Description                                                                                                                                               |

|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVDD12      | 30, 56     | Digital Power Supply, 1.2V (2 pins)                                                                                                                           |

| DVDD33      | 20, 39, 65 | Digital Power Supply, 3.3V                                                                                                                                    |

| DVSS        | 47         | Return for DVDD12 and DVDD33                                                                                                                                  |

| RVDD12      | 16         | 1.25G Receiver Analog Power Supply, 1.2V                                                                                                                      |

| RVDD33      | 12         | 1.25G Receiver Analog Power Supply, 3.3V                                                                                                                      |

| RVSS        | 15         | Return for RVDD12 and RVDD33                                                                                                                                  |

| TVDD12      | 11         | 1.25G Transmitter Analog Power Supply, 1.2V                                                                                                                   |

| TVDD33      | 7          | 1.25G Transmitter Analog Power Supply, 3.3V                                                                                                                   |

| TVSS        | 10         | Return for TVDD12 and TVDD33                                                                                                                                  |

| CVDD12      | 3          | TX PLL Analog Power Supply, 1.2V                                                                                                                              |

| CVDD33      | 2          | TX PLL Analog Power Supply, 3.3V                                                                                                                              |

| CVSS        | 4          | Return for CVDD12 and CVDD33                                                                                                                                  |

| GVDD12      | 18         | Analog Power Supply, 1.2V                                                                                                                                     |

| GVSS        | 1          | Return for GVDD12.                                                                                                                                            |

| Exposed Pad | EP         | Exposed pad (die paddle). Connect to ground plane. EP also functions as a heatsink. Solder to the circuit-board ground plane to maximize thermal dissipation. |

# 6. Functional Description

# 6.1 Pin Configuration During Reset

The MAX24288 initial configuration is determined by pins that are sampled at reset. The values on these pins are used to set the reset values of several register bits.

The pins that are sampled at reset to pin-configure the device are listed described in Table 6-1. During reset these pins are high-impedance inputs and require  $10k\Omega$  pullup or pulldown resistors to set pin-configuration values. After reset, the pins can become outputs if configured to do so and operate as configured. There are two pin configuration modes: 15-pin mode and 3-pin mode.

In 15-pin mode (COL=0 during reset, see Table 6-1) all major settings associated with the PCS block are configurable. In addition, the input reference clock frequency on the REFCLK pin is configured during reset using the RXD[3:2] pins.

Table 6-1. Reset Configuration Pins, 15-Pin Mode (COL=0)

| Pin      | Function                 | Register Bit Affected         | Notes                                                                             |

|----------|--------------------------|-------------------------------|-----------------------------------------------------------------------------------|

| CRS      | Double Date Rate         | GMIICR.DDR=CRS                | See Table 6-2.                                                                    |

| GPO2     | 10/100 MII: DTE or DCE   | 10/100 MII: GMIICR.DTE_DCE    | 0=DCE, 1=DTE<br>(serial interface is configured for<br>SGMII mode, PCSCR.BASEX=0) |

|          | Other: Serial Interface  | Other: PCSCR.BASEX            | 0=SGMII, 1=1000BASE=X                                                             |

| GPO1     | GPIO1 Configuration      | GPIOCR1.GPIO1_SEL[2]          | 0=high impedance<br>1=125MHz from TX PLL                                          |

| RXD[1:0] | Parallel Interface Speed | GMIICR.SPD[1:0]               | See Table 6-2.                                                                    |

| RXD[3:2] | REFCLK Frequency         | None                          | 00=10MHz, 01=12.8MHz,<br>10=25MHz, 11=125MHz                                      |

| RXD[7:4] | MDIO PHYAD[3:0].         | Internal MDIO PHYAD register  | Note: PHYAD[4:0]=11111 enables                                                    |

| RX_ER    | MDIO PHYAD[4].           | (device address on MDIO bus). | factory test mode. Do not use.                                                    |

| RX_DV    | Other: Auto-negotiation  | BMCR.AN_EN                    | 0=Disable, 1=Enable                                                               |

| TXCLK    | TXCLK Enable             | GMIICR.TXCLK_EN               | 0=high impedance<br>1=125MHz from TX PLL<br>Ignored in MII mode                   |

Table 6-2. Parallel Interface Configuration

| SPD[1] | SPD[0] | Speed    | DDR=0    | DDR=1      |

|--------|--------|----------|----------|------------|

| 0      | 0      | 10Mbps   | MII      | RGMII-10   |

| 0      | 1      | 100Mbps  | MII      | RGMII-100  |

| 1      | 0      | 1000Mbps | GMII     | RGMII-1000 |

| 1      | 1      |          | reserved |            |

In 3-pin mode (COL=1 during reset, see Table 6-3) the device is configured for a 1000Mbps RGMII or GMII parallel interface. This mode is targeted to the application of connecting an ASIC, FPGA or processor with an RGMII or GMII interface to a switch device with an SGMII interface or to a 1000BASE-X optical interface. In 3-pin mode, the REFCLK pin is configured for 25MHz, the MDIO interface is enabled (with PHY address set to 0x04), the SPI interface is enabled, 1000BASE-X auto-negotiation (or automatic transmission of SGMII control information) is enabled, TXCLK is configured to output a 125MHz clock, and the TCLKP/TCLKN differential pair is disabled. Note: if RX\_ER and RXD[7:4] are all high when the device exits reset then the device enters factory test mode; for normal operation set these pins to any other combination of values.

Table 6-3. Reset Configuration Pins, 3-Pin Mode (COL=1)

| Pin  | Function         | Register Bit Affected | Notes                 |

|------|------------------|-----------------------|-----------------------|

| CRS  | Double Date Rate | GMIICR.DDR=CRS        | 0=GMII, 1=RGMII       |

| GPO2 | Serial Interface | PCSCR.BASEX           | 0=SGMII, 1=1000BASE=X |

Note: In 3-pin mode register fields are automatically set as follows: REFCLK clock rate to 25MHz, GMIICR.SPD[1:0]=10, MDIO PHYAD is set to 0x04, BMCR.AN\_EN=1, GMIICR.TXCLK\_EN=1, GPIOCR1=0 and GPIOCR2=0. All other registers are reset to normal defaults listed in the register descriptions.

### 6.2 General-Purpose I/O

The MAX24288 has two general-purpose output pins, GPO1, GPO2, and seven general-purpose input/output pins, GPIO1 through GPIO7. Each pin can be configured to drive low or high or be in a high-impedance state. Other uses for the GPO and GPIO pins are listed in Table 6-4 through Table 6-6. The GPO and GPIO pins are each configured using a GPxx\_SEL field in registers GPIOCR1 or GPIOCR2 with values as indicated in the tables below.

When a GPIO pin is configured as high impedance it can be used as an input. The real-time state of GPIOx can be read from GPIOSR.GPIOx. In addition, a latched status bit GPIOSR.GPIOxL is available for each GPIO pin. This latched status bit is set when the transition specified by GPIOCR2.GPIO13\_LSC (for GPIO1 through GPIO3) or by GPIOCR2.GPIO47\_LSC (for GPIO4 through GPIO7) occurs on the pin.

Note that GPIO4 through GPIO7 are alternate pin functions to TXD[7:4] and therefore are only available when the parallel MII is configured for MII or RGMII.

Table 6-4. GPO1, GPIO1 and GPIO3 Configuration Options

| GPxx_SEL | Description                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------|

| 000      | High impedance, not driven, can be used as an input                                                      |

| 001      | Drive logic 0                                                                                            |

| 010      | Drive logic 1                                                                                            |

| 011      | Interrupt output, active low. GPO1 drives low and high, GPIO1 and GPIO3 are open-drain.                  |

| 100      | Output 125MHz from the reference clock PLL                                                               |

| 101      | Output 25MHz or 125MHz from receive clock recovery PLL. Not squelched. Frequency specified by CR.RCFREQ. |

| 110      | Output real-time link status, 0=link down, 1=link up                                                     |

| 111      | Output PEG1 signal from 1588 event generator                                                             |

Table 6-5. GPO2 and GPIO2 Configuration Options

| GPxx_SEL | Description                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000      | High impedance, not driven, can be used as an input                                                                                                                                                                     |

| 001      | Drive logic 0                                                                                                                                                                                                           |

| 010      | Drive logic 1                                                                                                                                                                                                           |

| 011      | Output the PTP_CLKO signal from 1588 time engine                                                                                                                                                                        |

| 100      | Output 125MHz from reference clock PLL                                                                                                                                                                                  |

| 101      | Output 25MHz or 125MHz from receive clock recovery PLL. The frequency is specified by CR.RCFREQ. Signal is automatically squelched (driven low) when CR.RCSQL=1 and any of several conditions occur. See section 6.2.1. |

| 110      | Output CRS (carrier sense) status                                                                                                                                                                                       |

| 111      | Output PEG2 signal                                                                                                                                                                                                      |

Table 6-6. GPIO4, GPIO5, GPIO6 and GPIO7 Configuration Options

| GPxx_SEL | Description                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000      | High impedance, not driven, can be used as an input                                                                                                                                                                     |

| 001      | Drive logic 0                                                                                                                                                                                                           |

| 010      | Drive logic 1                                                                                                                                                                                                           |

| 011      | Output the PTP_CLKO signal from 1588 time engine                                                                                                                                                                        |

| 100      | Output 125MHz from reference clock PLL                                                                                                                                                                                  |

| 101      | Output 25MHz or 125MHz from receive clock recovery PLL. The frequency is specified by CR.RCFREQ. Signal is automatically squelched (driven low) when CR.RCSQL=1 and any of several conditions occur. See section 6.2.1. |

| 110      | Output PEG1 signal                                                                                                                                                                                                      |

| 111      | Output PEG2 signal                                                                                                                                                                                                      |

#### 6.2.1 Receive Recovered Clock Squelch Criteria

A 25MHz or 125MHz clock from the receive clock recovery PLL can be output on any of GPO2, GPIO2 and GPIO4-7. When CR.RCSQL=1, this clock is squelched (driven low) when any of the following conditions occur:

- IR.ALOS=1 (analog loss-of-signal occurred)

- IR.RLOS=1 (CDR loss-of-signal occurred))

- IR.RLOL=1 (CDR PLL loss-of-lock occurred)

- IR.LINK\_ST=0 (auto-negotiation link down occurred, latched low)

Since each of these criteria is a latched status bit, the output clock signal remains squelched until all of these latched status bits go inactive (as described in section 7.2).

# 6.3 Reset, Power Down and Processor Interrupt

#### 6.3.1 Reset

The following reset functions are available in the device:

- Hardware reset pin (RST\_N): This pin asynchronously resets all logic, state machines and registers in the device except the JTAG logic. When the RST\_N pin is low, all internal registers are reset to their default values. Pin states are sampled and used to set the default values of several register fields as described in section 6.1. RST\_N should be asserted for at least 100µs.

- 2. Global reset bit, GPIOCR1.RST: Setting this bit is equivalent to asserting the RST\_N pin. This bit is self-clearing.

- 3. (MDIO interface only) Datapath reset bit, BMCR.DP\_RST. This bit resets the entire datapath from parallel MII interface through PCS encoder and decoder including the packet classifier and modifier blocks. It also resets the deserializer and transmit and receive start-of-packet detectors. It does not reset any registers, GPIO logic, the TX PLL or any block reset by PTPCR1.TE\_RST. The DP\_RST bit is self-clearing.

- 4. Time engine reset bit, PTPCR1.TE\_RST. This bit resets the logic of the 1588 time engine, output clock generator, programmable event generators, timestampers and GPIO. It does not reset any registers, GPIO logic, the TX PLL or any block reset by BMCR.DP\_RST. The TE\_RST bit is self-clearing.

- 5. JTAG reset pin JTRST N. This pin resets the JTAG logic. See section 8 for details about JTAG operation.

TE\_RST does not affect the datapath or packet traffic.

#### 6.3.2 Power Down

When sections of the MAX24288 are not used, they can be powered down to reduce power consumption.

The transmit serializer and the TDP/TDN and TCLKP/TCLN output drivers can be powered down by setting PTPCR1.TX\_PWDN=1. In this mode, the output drivers are placed in a high-impedance state, and the pins are pulled up to 3.3V by their internal  $50\Omega$  termination resistors. See section 6.6.

The RDP/RDN inputs, the clock and data recovery PLL, and the de-serializer can be powered down by setting PTPCR1.RX\_PWDN=1.

The parallel MII (section 6.7), the PCS encoder and decoder and all other parallel datapath logic, both receive and transmit, except the packet classifiers and packet modifiers can be powered down by setting PTPCR1.DP\_PWDN=1.

The packet classifiers (section 6.13.6) and packet modifiers (6.13.7) can be powered down by setting PTPCR1.PKT PWDN=1.

The time engine (section 6.13.1), output clock generator (6.13.2), PEGs (6.13.3) and timestampers (6.13.4) can be disabled by setting PTPCR1.TE\_PWDN=1.

Finally, the TX PLL (section 6.10.2) can be powered down <u>and bypassed</u> by setting PTPCR1.PLL\_PWDN=1. Because the serializer, transmit driver, receive CDR and deserializer do not get the high-speed clocks they need when the TX PLL is disabled, those blocks must be disabled when PLL\_PWDN=1 by setting PTPCR1.TX\_PWDN=1 and PTPCR1.RX\_PWDN=1. In addition, if the frequency of the REFCLK signal is less than 125MHz, all internal logic is clocked at a slower rate, including the MDIO and SPI interfaces. The maximum clock rates for MDIO and SPI are reduced by a factor of (REFCLK\_freq / 125MHz).

In addition, when the TX PLL is powered down, the time engine accumulator (Figure 6-13) is clocked directly from the REFCLK signal. Therefore, the uncertainty of timestamping and PEG edge placement is half a REFCLK cycle (vs. ~1ns when using the TX PLL).

Deasserting a PWDN bit causes the affected circuitry to be reset as described in section 6.3.1.

#### 6.3.3 Processor Interrupts

Any of pins GPO1, GPIO1 and GPIO3 can be configured as an active low interrupt output by setting the appropriate field in GPIOCR1 to 011. GPO1 drives high and low while GPIO1 and GPIO3 are open-drain and require pullup resistors.

Status bits than can cause an interrupt are located in the IR and PTP\_IR registers. The corresponding interrupt enable bits are located in the IR and PTP\_IE registers. Both the PAGESEL register and the PTP\_IR register have top-level IR AND PTP\_IR status bits to indicate which registers have active interrupt sources. The PAGESEL register is available on all pages through the MDIO interface, allowing the interrupt routine to read the register without changing the MDIO page.

#### 6.4 SPI - Serial Processor Interface