# HB0739 Handbook CoreAXI4DMAController v2.1

а 🔨 Міскоснір company

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | Revisi<br>1.1<br>1.2                                   | ion History       1         Revision 2.0       1         Revision 1.0       1                                                                                                                                                                                                                               |

|---|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Introd<br>2.1<br>2.2<br>2.3<br>2.4                     | uction       2         Features       2         Core Version       2         Supported Families       2         Utilization and Performance       3                                                                                                                                                         |

| 3 | Functi<br>3.1                                          | ional Description7Architecture73.1.1AXI4-Lite Slave Interface Controller73.1.2Control and Status Registers73.1.3Buffer Descriptors73.1.4DMA Controller83.1.5Memory Map Cache83.1.6Stream Cache83.1.7Interrupt Controller83.1.8AXI4 Master Interface Controller93.1.9AXI4-Stream Slave Interface Controller9 |

|   | 3.2                                                    | Buffer Descriptors93.2.1Internal Descriptor Support93.2.2External Descriptor Support103.2.3Stream Descriptor Support103.2.4Descriptor Management11                                                                                                                                                          |

|   | 3.3<br>3.4                                             | Flow Control/Throttling       11         DMA Operations       12         3.4.1       Chain Operations (Scatter-gather)       12         3.4.2       Cyclic Operations       13                                                                                                                              |

|   | 3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10                | AXI4-Stream Bridge14Interrupts16Arbitration17AXI Transactions18AXI4-Stream Transactions18Cache Coherence19                                                                                                                                                                                                  |

| 4 | Interfa<br>4.1<br>4.2                                  | ace Descriptions       20         Signal Descriptions       20         Configuration Parameters       25                                                                                                                                                                                                    |

| 5 | Regis<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | ter Map and Descriptions27Version Register29Start Operation Register29Interrupt X Status Register30Interrupt X Mask Register31Interrupt X Clear Register32Interrupt X External Descriptor Register33Descriptor X Configuration Register33                                                                   |

|   | 5.8    | Descriptor X Byte Count Register                     | 35 |

|---|--------|------------------------------------------------------|----|

|   | 5.9    | Descriptor X Source Address Register                 | 36 |

|   | 5.10   | Descriptor X Destination Address Register            | 36 |

|   | 5.11   | Descriptor X Next Descriptor Number/Address Register | 37 |

|   | 5.12   | Stream Address 0 Register                            | 37 |

|   | 5.13   | Stream Address 1 Register                            | 38 |

|   | 5.14   | Stream Address 2 Register                            | 38 |

|   | 5.15   | Stream Address 3 Register                            | 39 |

| 6 | Tool I | Flows                                                | 40 |

|   | 6.1    | Licensing                                            | 40 |

|   | 6.2    | RTL                                                  |    |

|   | 6.3    | SmartDesign                                          | 40 |

|   | 6.4    | Simulation Flows                                     |    |

|   | 6.5    | Synthesis                                            | 42 |

|   | 6.6    | Place-and-Route                                      | 42 |

| 7 | Test-  | bench Operation and Modification                     | 43 |

# **Figures**

| Figure 1  | CoreAXI4DMAController Internal Architecture                | 7  |

|-----------|------------------------------------------------------------|----|

| Figure 2  | Internal Descriptor Format                                 | 9  |

| Figure 3  | Stream Descriptor Support                                  | 10 |

| Figure 4  | Multi Process Flow Control Management                      | 12 |

| Figure 5  | Example Descriptor Chain                                   | 13 |

| Figure 6  | Example Cyclic Descriptor Chain                            |    |

| Figure 7  | Ping-Pong Cyclic Descriptor Chain                          | 14 |

| Figure 8  | AXI4-Stream to AXI4 Memory Map Bridging                    |    |

| Figure 9  | Interrupt Queue Logic                                      | 16 |

| Figure 10 | Descriptor Arbitration                                     | 17 |

| Figure 11 | SmartDesign CoreAXI4DMAController Instance View            | 40 |

| Figure 12 | SmartDesign CoreAXI4DMAController Configuration Dialog Box | 41 |

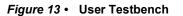

| Figure 13 | User Testbench                                             |    |

# **Tables**

| Table 1  | CoreAXI4DMAController Device Utilization and Performance for PolarFire SoC Family (AXI4-Stream Disabled)   | . 3 |

|----------|------------------------------------------------------------------------------------------------------------|-----|

| Table 2  | CoreAXI4DMAController Device Utilization and Performance for PolarFire SoC<br>Family (AXI4-Stream Enabled) | . 3 |

| Table 3  | CoreÁXI4DMAController Device Utilization and Performance for PolarFire Family (AXI4-Stream Disabled)       |     |

| Table 4  | CoreAXI4DMAController Device Utilization and Performance for PolarFire<br>Family (AXI4-Stream Enabled)     |     |

| Table 5  | CoreAXI4DMAController Device Utilization and Performance for RTG4<br>Family (AXI4-Stream Disabled)         |     |

| Table 6  | CoreAXI4DMAController Device Utilization and Performance for RTG4 Family<br>(AXI4-Stream Enabled)          |     |

| Table 7  | CoreAXI4DMAController Device Utilization and Performance for SmartFusion2<br>Family (AXI4-Stream Disabled) |     |

| Table 8  | CoreAXI4DMAController Device Utilization and Performance for SmartFusion2<br>Family (AXI4-Stream Enabled)  |     |

| Table 9  | CoreAXI4DMAController Device Utilization and Performance for IGLOO2 Family<br>(AXI4-Stream Disabled)       |     |

| Table 10 | CoreAXI4DMAController Device Utilization and Performance for IGLOO2 Family (AXI4-Stream Enabled)           |     |

| Table 11 | CoreAXI4DMA Controller I/O Signals                                                                         |     |

| Table 12 | CoreAXI4DMAController Configuration Options                                                                |     |

| Table 13 | CoreAXI4DMAController Registers                                                                            |     |

| Table 14 | Version Register                                                                                           |     |

| Table 15 | Version Register Bit Definitions                                                                           |     |

| Table 16 | Start Operation Register                                                                                   |     |

| Table 17 | Start Operation Register Bit Definitions                                                                   |     |

| Table 18 | Interrupt X Status Register                                                                                |     |

| Table 19 | Interrupt X Status Register Bit Definitions                                                                |     |

| Table 20 | Interrupt X Mask Register                                                                                  |     |

| Table 21 | Interrupt X Mask Register Bit Definitions                                                                  | 31  |

| Table 22 | Interrupt X Clear Register                                                                                 | 32  |

| Table 23 | Interrupt X Clear Register Bit Definitions                                                                 | 32  |

| Table 24 | Interrupt X External Descriptor Register                                                                   |     |

| Table 25 | Interrupt X External Descriptor Register Bit Definitions                                                   |     |

| Table 26 | Descriptor X Configuration Register                                                                        |     |

| Table 27 | Descriptor X Configuration Register Bit Definitions                                                        |     |

| Table 28 | Descriptor X Byte Count Register                                                                           |     |

| Table 29 | Descriptor X Byte Count Register Bit Definitions                                                           |     |

| Table 30 | Descriptor X Source Address Register                                                                       |     |

| Table 31 | Descriptor X Source Address Register Bit Definitions                                                       |     |

| Table 32 | Descriptor X Destination Address Register                                                                  | 36  |

| Table 33 | Descriptor X Destination Address Register Bit Definitions                                                  |     |

| Table 34 | Descriptor X Next Descriptor Number/Address Register                                                       |     |

| Table 35 | Descriptor X Next Descriptor Number/Address Register Bit Definitions                                       |     |

| Table 36 | Stream Address 0 Register                                                                                  |     |

| Table 37 | Stream Address 0 Register Bit Definitions                                                                  |     |

| Table 38 | Stream Address 1 Register                                                                                  |     |

| Table 39 | Stream Address 1 Register Bit Definitions                                                                  |     |

| Table 40 | Stream Address 2 Register                                                                                  | 38  |

| Table 41 | Stream Address 2 Register Bit Definitions                                                                  |     |

| Table 42 | Stream Address 3 Register                                                                                  |     |

| Table 43 | Stream Address 3 Register Bit Definitions                                                                  | 39  |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Revision 2.0

The following is a summary of the changes in revision 2.0 of this document.

- Updated the document for CoreAXI4DMAController v2.1.

- Updated section Supported Families, page 2.

- Updated section Utilization and Performance, page 3.

- Updated the following tables.

- Table 11, page 20

- Table 12, page 25

- Table 19, page 30

- Added Notes below Table 13, page 27, Table 19, page 30, Table 21, page 31, and Table 27, page 34.

- Removed section Obfuscation, page 40.

- Added section RTL, page 40.

- Updated section SmartDesign, page 40.

- Replaced Figure 11, page 40 and Figure 12, page 41.

## 1.2 **Revision 1.0**

The first publication of this document, created for CoreAXI4DMAController v2.0.

# 2 Introduction

CoreAXI4DMAController is an AXI4 DMA controller designed to perform memory to memory style DMA (Direct Memory Access) transfers in an AXI system. The core provides in-built flow control techniques to ensure that the bandwidth of the AXI interface is optimally utilized. In addition, the core provides a bridge to AXI4 memory-mapped slaves for AXI4-Stream masters.

## 2.1 Features

Following are the key features of CoreAXI4DMAController:

- AXI4-Lite slave control interface

- AXI4 master DMA interface

- AXI4-Stream slave interface to provide a bridge to AXI4 memory map

- Maximum transfer size of 8 MB

- Maximum operating frequency of approximately 200 MHz

- Circular buffer DMA support

- Scatter-gather DMA support

- 2 internal 4 KB (maximum size) store and forward caches

- 1-4 interrupt outputs

- 4-32 internal descriptors

- External descriptor fetching support

- Fixed priority arbiter for DMA requests with configurable number of priority levels

- Configurable DMA bus width from 32- to 512-bit

- Prevents AXI4 transfers from crossing 4 KB boundaries<sup>1</sup>

### 2.2 Core Version

This handbook provides information on CoreAXI4DMAController version 2.1.

## 2.3 Supported Families

- PolarFire<sup>®</sup> SoC

- PolarFire<sup>®</sup>

- RTG4<sup>™</sup>

- IGLOO<sup>®</sup>2

- SmartFusion<sup>®</sup>2

<sup>1.</sup> The AXI4 protocol defines the smallest allocatable slave size as 4 KB. 4 KB boundary protection is required to prevent masters from generating sequential transactions that cross 4 KB boundaries to prevent sequential transactions spanning multiple slaves. Since the address information is sent up-front in an AXI transaction, if a transaction were to span a 4 KB boundary, the slave would be unaware of the type and configuration of the AXI transaction taking place.

## 2.4 Utilization and Performance

Utilization and performance data are listed in the following tables for their respective device families. The data listed in the following tables are indicative only. The overall device utilization and performance of the core is system dependent.

| Logic Elements          |            |               |       |                   |  |  |

|-------------------------|------------|---------------|-------|-------------------|--|--|

| Family                  | Sequential | Combinatorial | Total | Performance (MHz) |  |  |

| PolarFire SoC (32-bit)  | 2743       | 4047          | 6790  | 203.25            |  |  |

| PolarFire SoC (64-bit)  | 2975       | 4213          | 7188  | 202.76            |  |  |

| PolarFire SoC (128-bit) | 3434       | 4614          | 8048  | 198.26            |  |  |

| PolarFire SoC (256-bit) | 4308       | 6088          | 10396 | 194.33            |  |  |

| PolarFire SoC (512-bit) | 6088       | 7080          | 13168 | 197.43            |  |  |

# Table 1 • CoreAXI4DMAController Device Utilization and Performance for PolarFire SoC Family (AXI4-Stream Disabled)

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

| Table 2 • | CoreAXI4DMAController Device Utilization and Performance for PolarFire SoC |

|-----------|----------------------------------------------------------------------------|

|           | Family (AXI4-Stream Enabled)                                               |

| Logic Elements          |            |               |       |                   |  |  |

|-------------------------|------------|---------------|-------|-------------------|--|--|

| Family                  | Sequential | Combinatorial | Total | Performance (MHz) |  |  |

| PolarFire SoC (32-bit)  | 3503       | 5642          | 9145  | 197.01            |  |  |

| PolarFire SoC (64-bit)  | 3891       | 5992          | 9883  | 183.35            |  |  |

| PolarFire SoC (128-bit) | 4588       | 6788          | 11376 | 184.95            |  |  |

| PolarFire SoC (256-bit) | 5941       | 8210          | 14151 | 177.49            |  |  |

| PolarFire SoC (512-bit) | 8735       | 11212         | 19947 | 192.6             |  |  |

The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

# Table 3 • CoreAXI4DMAController Device Utilization and Performance for PolarFire Family (AXI4-Stream Disabled)

| Logic Elements      |            |               |       |                   |  |  |

|---------------------|------------|---------------|-------|-------------------|--|--|

| Family              | Sequential | Combinatorial | Total | Performance (MHz) |  |  |

| PolarFire (32-bit)  | 2743       | 4047          | 6790  | 203.25            |  |  |

| PolarFire (64-bit)  | 2975       | 4213          | 7188  | 202.76            |  |  |

| PolarFire (128-bit) | 3434       | 4614          | 8048  | 198.26            |  |  |

| PolarFire (256-bit) | 4308       | 6088          | 10396 | 194.33            |  |  |

| PolarFire (512-bit) | 6088       | 7080          | 13168 | 197.43            |  |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

# Table 4 • CoreAXI4DMAController Device Utilization and Performance for PolarFire Family (AXI4-Stream Enabled)

| Logic Elements      |            |               |       |                   |  |  |

|---------------------|------------|---------------|-------|-------------------|--|--|

| Family              | Sequential | Combinatorial | Total | Performance (MHz) |  |  |

| PolarFire (32-bit)  | 3503       | 5642          | 9145  | 197.01            |  |  |

| PolarFire (64-bit)  | 3891       | 5992          | 9883  | 183.35            |  |  |

| PolarFire (128-bit) | 4588       | 6788          | 11376 | 184.95            |  |  |

| PolarFire (256-bit) | 5941       | 8210          | 14151 | 177.49            |  |  |

| PolarFire (512-bit) | 8735       | 11212         | 19947 | 192.6             |  |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

#### Table 5 • CoreAXI4DMAController Device Utilization and Performance for RTG4 Family (AXI4-Stream Disabled)

| Logic Elements |            |               |       |                   |  |  |  |

|----------------|------------|---------------|-------|-------------------|--|--|--|

| Family         | Sequential | Combinatorial | Total | Performance (MHz) |  |  |  |

| RTG4 (32-bit)  | 2974       | 4198          | 7172  | 196.309           |  |  |  |

| RTG4 (64-bit)  | 3212       | 4465          | 7677  | 190.512           |  |  |  |

| RTG4 (128-bit) | 3689       | 4953          | 8462  | 185.322           |  |  |  |

| RTG4 (256-bit) | 4628       | 5754          | 10382 | 181.422           |  |  |  |

| RTG4 (512-bit) | 6449       | 7343          | 13792 | 185.357           |  |  |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

#### Table 6 • CoreAXI4DMAController Device Utilization and Performance for RTG4 Family (AXI4-Stream Enabled)

| Logic Elements |            |               |       |                   |  |  |

|----------------|------------|---------------|-------|-------------------|--|--|

| Family         | Sequential | Combinatorial | Total | Performance (MHz) |  |  |

| RTG4 (32-bit)  | 3748       | 5672          | 9420  | 181.061           |  |  |

| RTG4 (64-bit)  | 4119       | 6101          | 10220 | 173.883           |  |  |

| RTG4 (128-bit) | 5251       | 7181          | 12432 | 164.76            |  |  |

| RTG4 (256-bit) | 6384       | 8261          | 14645 | 155.642           |  |  |

| RTG4 (512-bit) | 9249       | 11053         | 20302 | 165.207           |  |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

# Table 7 • CoreAXI4DMAController Device Utilization and Performance for SmartFusion2 Family (AXI4-Stream Disabled)

| Logic Elements        |            |               |       |                   |  |

|-----------------------|------------|---------------|-------|-------------------|--|

| Family                | Sequential | Combinatorial | Total | Performance (MHz) |  |

| SmarFusion2 (32-bit)  | 2964       | 4187          | 7151  | 236.967           |  |

| SmarFusion2 (64-bit)  | 3211       | 4431          | 7642  | 243.072           |  |

| SmarFusion2 (128-bit) | 3693       | 4963          | 8656  | 229.621           |  |

| SmarFusion2 (256-bit) | 4634       | 5777          | 10411 | 233.318           |  |

| SmarFusion2 (512-bit) | 6455       | 7345          | 13800 | 226.193           |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

# Table 8 • CoreAXI4DMAController Device Utilization and Performance for SmartFusion2 Family (AXI4-Stream Enabled)

| Logic Elements        |            |               |       |                   |  |  |  |

|-----------------------|------------|---------------|-------|-------------------|--|--|--|

| Family                | Sequential | Combinatorial | Total | Performance (MHz) |  |  |  |

| SmarFusion2 (32-bit)  | 3736       | 5634          | 9370  | 239.808           |  |  |  |

| SmarFusion2 (64-bit)  | 4125       | 6061          | 10186 | 234.797           |  |  |  |

| SmarFusion2 (128-bit) | 5257       | 7172          | 12429 | 228.333           |  |  |  |

| SmarFusion2 (256-bit) | 6389       | 8283          | 14672 | 221.877           |  |  |  |

| SmarFusion2 (512-bit) | 9255       | 11014         | 20269 | 211.416           |  |  |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

#### Table 9 • CoreAXI4DMAController Device Utilization and Performance for IGLOO2 Family (AXI4-Stream Disabled)

| Logic Elements   |            |               |       |                   |  |  |  |  |

|------------------|------------|---------------|-------|-------------------|--|--|--|--|

| Family           | Sequential | Combinatorial | Total | Performance (MHz) |  |  |  |  |

| IGLOO2 (32-bit)  | 2964       | 4187          | 7151  | 236.967           |  |  |  |  |

| IGLOO2 (64-bit)  | 3211       | 4431          | 7642  | 243.072           |  |  |  |  |

| IGLOO2 (128-bit) | 3693       | 4963          | 8656  | 229.621           |  |  |  |  |

| IGLOO2 (256-bit) | 4634       | 5777          | 10411 | 233.318           |  |  |  |  |

| IGLOO2 (512-bit) | 6455       | 7345          | 13800 | 226.193           |  |  |  |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

# Table 10 • CoreAXI4DMAController Device Utilization and Performance for IGLOO2 Family (AXI4-Stream Enabled)

| Logic Elements   |            |               |       |                   |  |  |  |  |  |

|------------------|------------|---------------|-------|-------------------|--|--|--|--|--|

| Family           | Sequential | Combinatorial | Total | Performance (MHz) |  |  |  |  |  |

| IGLOO2 (32-bit)  | 3736       | 5634          | 9370  | 239.808           |  |  |  |  |  |

| IGLOO2 (64-bit)  | 4125       | 6061          | 10186 | 234.797           |  |  |  |  |  |

| IGLOO2 (128-bit) | 5257       | 7172          | 12429 | 228.333           |  |  |  |  |  |

| IGLOO2 (256-bit) | 6389       | 8283          | 14672 | 221.877           |  |  |  |  |  |

| IGLOO2 (512-bit) | 9255       | 11014         | 20269 | 211.416           |  |  |  |  |  |

**Note:** The data in this table is achieved using Verilog RTL, with the following synthesis and layout settings (Timing-driven mode, high-effort) on a -1 speed grade part.

# **3 Functional Description**

## 3.1 Architecture

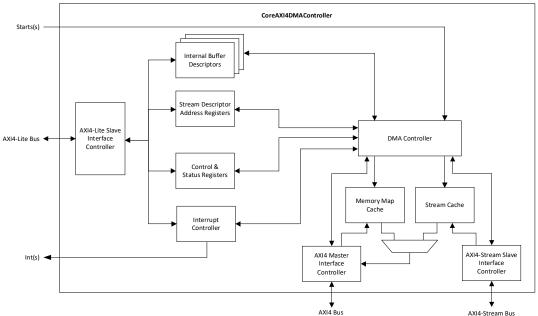

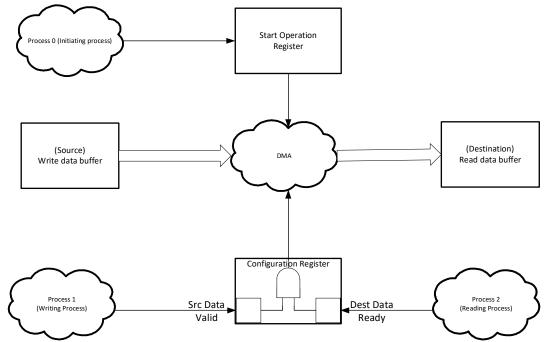

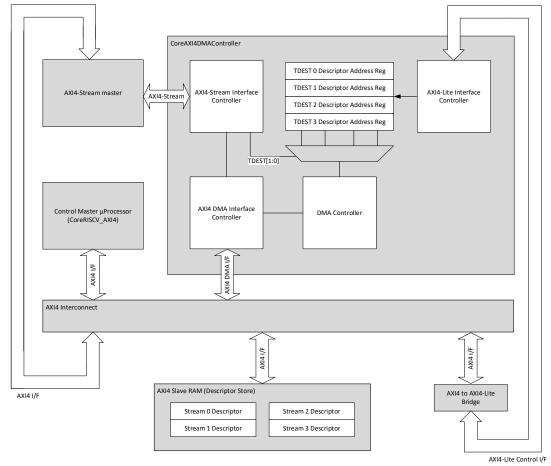

Figure 1 displays a high-level view of the internal architecture of CoreAXI4DMAController.

Figure 1 • CoreAXI4DMAController Internal Architecture

### 3.1.1 AXI4-Lite Slave Interface Controller

The AXI4-Lite slave interface controller is responsible for translating AXI4-Lite write and read transactions into the internal register interface protocol. This provides access to the internal registers (including buffer descriptors) from an AXI4-Lite master, allowing AXI4-Lite masters to initiate and configure DMA transfers.

### 3.1.2 Control and Status Registers

The Control and Status Registers block contains the *Version* register to relay the major, minor, and build number of the core to controlling masters along with providing a register for initiating DMA operations.

### 3.1.3 Buffer Descriptors

The internal buffer descriptors contain the information required to configure a DMA operation including the start and destination addresses, the type of DMA operation and the number of bytes to be transferred. The number of internal descriptors instantiated is configurable through parameter, in the range 4 - 32. Internal descriptors are stored in LSRAM and can be chained together to perform scatter-gather or circular buffer DMA operations. In addition, internal descriptors can be used to point at external descriptors.

### 3.1.4 DMA Controller

CoreAXI4DMAController provides a dedicated external start bit for each internal buffer descriptor (maximum of 32) which allows DMA operations already configured in the core's internal buffer descriptors to be kicked-off from a simple fabric controller. Alternatively, DMA operations can be kicked-off by writing to the corresponding bit in the *Start Operation* register.

Start bits are queued and processed using a round-robin arbiter kicking off one operation per clock cycle. This loads DMA requests into the DMA controller with the DMA operation commencing once control is granted to that operation on the AXI4 master interface. This setup allows multiple operations to be kicked-off in a single control master write preventing conflicts arising from multiple internal and external start bits being asserted in the same cycle.

The arbiter decides the DMA operation that gets serviced on the AXI4 interface. Buffer descriptors are assigned a fixed priority upfront. Since, the largest permitted DMA operation is 8 MB, DMA operations are divided into multiple transactions with the maximum DMA transaction size determined by the priority of the buffer descriptor to which it is associated and the maximum number of beats permitted for this priority level, configured through parameter. As AXI4 transactions must run to completion once initiated, this mechanism allows transactions with higher priorities to have more bandwidth whilst forcing transactions with lower priorities to enter back into the arbitration sequence more frequently to check for higher priority DMA operations in the queue. Round-robin arbitration is performed to service requests with the same priority level. No bandwidth is given to descriptors with a lower priority level if a higher priority descriptor is being processed. The maximum transactions size for the highest level of priority is 4 KB to prevent AXI transactions from crossing 4 KB address boundaries.

When enabled, AXI4-Stream operations shares the highest priority level, priority level 0. It is possible to associate no internal buffer descriptors with priority level 0 at configuration time to allocate the entire bandwidth of the AXI4 DMA interface to AXI4-Stream operations when they exist. Otherwise, AXI4-Stream to memory map forwarding operations will be interleaved with operations of internal descriptors at the highest priority level.

### 3.1.5 Memory Map Cache

CoreAXI4DMAControl contains two 4 KB SRAM caches to allow the core to complete the forward part of an AXI4-memory map store and forward operation whilst performing the store element of the next store and forward operation. The DMA Controller block is responsible for switching between the internal caches autonomously in a round-robin fashion.

#### 3.1.6 Stream Cache

If the AXI4-Stream configuration is selected, the core contains two additional 4 KB store caches allowing stream data received through the AXI4-Stream interface to be buffered before initiating multi-beat AXI4 forward transactions on the AXI4 interface. This allows stream operations to be received asynchronously to other DMA operations as the AXI4-Stream transfer is initiated by the AXI4-Stream master. The DMA Controller block is responsible for switching between the internal stream caches autonomously in a round-robin fashion.

### 3.1.7 Interrupt Controller

CoreAXI4DMAController allows users to enable multiple interrupt outputs and to associate each interrupt output with one or more internal buffer descriptors. The Interrupt Controller block is responsible for routing the events of each descriptor to the associated interrupt output. A configurable depth queue for each interrupt output is contained within this block to allow DMA operations to take place whilst waiting on the Control master to handle and clear previous interrupt events. If an interrupt queue backs up all operations of descriptors associated with this interrupt are suspended until space is freed in the interrupt queue by the Control master. DMA operations of other descriptors not associated with this interrupt queue will still be processed. This setup facilitates multiple processors to use the DMA controller concurrently.

**Note:** The interrupt association for an external descriptor is inherited from the previous internal descriptor in the chain. Interrupt events of Stream descriptors are always associated with Interrupt 0.

### 3.1.8 AXI4 Master Interface Controller

The AXI4 master interface controller is responsible for performing the DMA operation outlined by the DMA Controller block using AXI4 write and read transactions. This block returns a flag to the DMA controller when the requested store and forward operation is completed. If an AXI4 error is returned by a downstream slave during the read/store operation before the write/forward operation for that operation has commenced, the AXI4 Master Interface Controller continues the read/store to completion and reports the error to the control master without performing the write.

### 3.1.9 AXI4-Stream Slave Interface Controller

The AXI4-Stream slave interface controller provides a unidirectional bridge to the AXI4 memory map for AXI4 stream masters. The AXI4-Stream slave interface controller notifies the DMA Controller that a stream operation has commenced and of the position of the external descriptor in AXI4 memory describing the AXI4-Stream operation. Caching of the stream data in one of the internal 4 KB stream caches is performed in parallel to the fetching of the stream descriptor over the AXI4 DMA interface and completion of the previous memory mapped or stream DMA operation.

## 3.2 Buffer Descriptors

### 3.2.1 Internal Descriptor Support

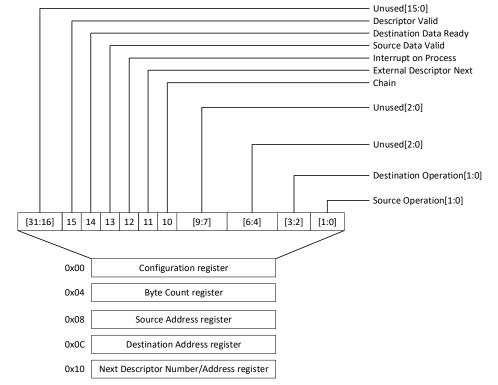

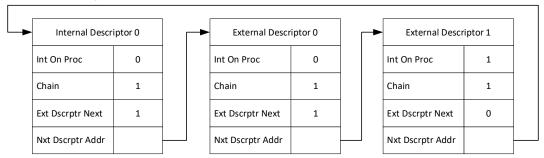

Internal descriptors are implemented using LSRAM with the number of internal descriptors configurable through parameter in the range 4-32. Each internal descriptor has the ability to operate as a competing DMA channel<sup>1</sup>. The format of an internal descriptor is as shown in Figure 2:

#### *Figure 2* • Internal Descriptor Format

Chaining of internal descriptors is supported to perform scatter-gather DMA operations where data is collected from one or more contiguous or non-contiguous locations and forwarded to one or more contiguous or non-contiguous locations. Each descriptor or chain of descriptors can be configured to perform repetitive cyclic operations. Refer to the Scatter-Gather and Cyclic Operations sections of this

1. Each internal descriptor can operate as a competing DMA channel provided that it's not chained with other internal descriptors.

document for information on performing such operations. Fetching of internal descriptors is performed in parallel to DMA data transferring and has no impact on DMA throughput performance provided that the operation described by the current descriptor being operated on is sufficiently large.

The priority level and interrupt output associated with operations of any internal descriptor must be configured at the time of instantiation through parameter.

#### 3.2.2 External Descriptor Support

External descriptors can be defined in the AXI4 address space and fetched over the AXI4 DMA interface. The structure of an external descriptor takes the same format as an internal descriptor, as shown in Figure 2.

External descriptors are pointed to using an internal descriptor with the *Chain* and *External Descriptor* bits set in the internal descriptor's *Configuration* register by passing the base address of the external descriptor to the *Next Descriptor Number/Address* register. Fetching of external descriptors over the DMA interface has a minor impact on overall DMA throughput performance provided that DMA operations are sizeable.

Chaining of external descriptors is supported through this mechanism. An external descriptor can be chained back to an internal descriptor by setting the *Chain* bitwith the *External Descriptor* bit cleared in the external descriptor's *Configuration* register and passing the internal descriptor number to the *Next Descriptor* Number/Address register. Cyclic operations of external descriptors can be achieved linking the last external descriptor in the chain back to the first internal descriptor.

The priority level and interrupt association of an external descriptor is inherited from the previous internal descriptor in the chain.

**Note:** The address of the *Configuration* register of an external descriptor must be aligned to the bus width of the AXI4 DMA interface configured through the *AXI\_DMA\_DWIDTH* parameter.

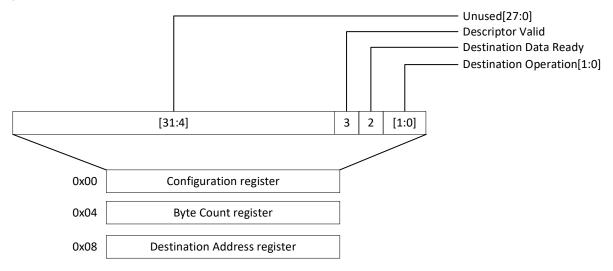

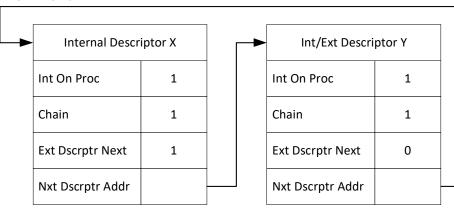

### 3.2.3 Stream Descriptor Support

Stream descriptors describe the AXI4-Stream transaction that is received from the AXI4-Stream master over the AXI4-Stream slave interface. The TDEST signal of the stream interface is used to select the CoreAXI4DMAController *Stream Descriptor Address* register that points to the stream descriptor describing the AXI4-Stream transaction that is in progress. The address of the stream descriptor must be written to the appropriate *Stream Descriptor Address* register prior to the AXI4-Stream transaction being initiated, along with the prior existence of the valid stream descriptor in the AXI4 DMA address space.

The format of stream descriptors is as shown in Figure 3:

#### Figure 3 • Stream Descriptor Support

The *Destination Data Ready bit* is used by control masters to denote when a buffer has been allocated for the reception of the stream data in the AXI4 memory-map address space. The first 4 KB of the stream transaction will be cached whilst the descriptor is being fetched. No further transfers in the AXI4-Stream transaction will be acknowledged until the *Destination Data Ready* bit is asserted, allowing the forwarding operation to the AXI4 memory map to commence when allocated bandwidth by the DMA arbiter.

If the *Descriptor Valid* bit of the stream descriptor that the AXI4-Stream transaction relates to is not set when the stream transaction is initiated and the descriptor is fetched, an invalid descriptor interrupt event will be triggered.

Stream descriptors are fetched over the AXI4 DMA interface when TVALID is asserted for the first transfer in the AXI4-Stream transaction once the current AXI4 or AXI4-Stream transaction completes. The maximum transfer size of a single stream transaction is 8 MB.

**Note:** The address of the *Configuration* register of a stream descriptor must be aligned to the bus width of the AXI4 DMA interface configured through the *AXI\_DMA\_DWIDTH* parameter. The bus width of the AXI4 DMA and stream interfaces are synonymous.

### 3.2.4 Descriptor Management

Since external start inputs exist for each internal descriptor and descriptors can be chained together, it is impossible for firmware to determine if a descriptor is currently involved in a DMA operation as it may have been initiated by a separate or external process. For this reason, it is advised to keep hardware-initiated DMA operations in separate descriptors to dynamically configured, firmware initiated operations. Once a descriptor is initialized by firmware during initial configuration, the *Descriptor Valid* bit must be set in the descriptor's *Configuration* register.

**Note:** If a UIC script is used to initialize internal descriptors in LSRAM, the *Descriptor Valid* bit will need to be set through firmware due to the order in which the UIC script writes the data into LSRAM (writes the *Configuration* register first, followed by the *Byte Count* register, hence the *Descriptor Valid* bit is cleared automatically by the DMA Controller).

If the start input associated with a descriptor is tied off then it is permitted for firmware to modify the descriptor contents on the fly, provided that no firmware initiated operations are being processed on the particular descriptor or which include the descriptor in a chain/cyclic buffer. Once any field in the descriptor is written to, the *Descriptor Valid* bit is automatically cleared by CoreAXI4DMAController. It is the responsibility of the firmware to set this bit only when the descriptor has been reconfigured.

If a DMA operation is initiated through an external start input assertion or a write to the *Start Operation* register on an uninitialized descriptor, an interrupt will be generated reporting the invalid descriptor error.

## 3.3 Flow Control/Throttling

Once an AXI transaction is initiated by a master sending the write/read address it must run to completion. A slave can force a master to wait before sending additional write data or receiving read data using the valid-ready flow control signals built into the AXI4 protocol. However, masters cannot determine up-front that a slave is unable to handle more data and thereby may hog the bus.

To prevent CoreAXI4DMAController relying on AXI slaves always having data in place and room for write data, CoreAXI4DMAController implements separate *Source Data Ready and Destination Data Valid* bits in both internal and external descriptors to support firmware flow control management. In order for a descriptor to be operated on, firmware must set both flow control bits whether or not the descriptor is part of a descriptor chain.

**Note:** Both the *Source Data Valid* and *Destination Data Ready* flow control bits must be set again every time that a descriptor is processed as part of a cyclic chain.

To support the separation of the application into multiple processes, a descriptor can be kicked-off in the *Start Operation* register before either or both flow control bits are set, but no bandwidth will be granted to this descriptor until both bits are subsequently set either together or separately in the same process or in separate processes altogether. The conceptual flow control management of CoreAXI4DMAController is as shown in Figure 4:

Clearing of the *Source Data Valid* and *Destination Data Ready* flow control bits is performed automatically by CoreAXI4DMAController for both internal and external descriptors every time that an operation of the descriptor is completed.

If either the *Source Data Valid* or Destination Data Ready flow control bits are low when an external descriptor is fetched, the external descriptor's *Configuration* register will be fetched again over the AXI4 interface until both bits are detected high every time that this DMA channel is apportioned a time slot by the DMA arbiter. The allotted bandwidth will be passed-over if either bit remains low when fetched. No DMA transfer will be performed whilst arbitration will be re-entered immediately.

Stream descriptors support a *Destination Data Ready* bit for flow control purposes. As with internal and external descriptors, the *Destination Data Ready* bit is cleared by the DMA controller when the AXI4-Stream transaction data described in the stream descriptor has been forwarded to the AXI4 memory-map address space. The *Destination Data Ready* flow control bit will be fetched every time that the stream descriptor is allocated bandwidth by the DMA arbiter in the manner described for external descriptors above.

## 3.4 DMA Operations

### 3.4.1 Chain Operations (Scatter-gather)

Chain operations are typically used to implement scatter-gather DMA operations where data is collected from multiple non-concurrent memory blocks and spread to a number of concurrent or non-concurrent locations. A chain can be formed using a single internal descriptor and multiple external descriptors, multiple internal descriptors or using a mix of internal and external descriptors. The starting point for a descriptor chain must be an internal descriptor.

To configure a chain operation, create a number of buffer descriptors with the *Chain* bit set in each buffer descriptor except the last. The *Next Descriptor* field in all buffer descriptors other than the last should point to the next descriptor in the chain. This field will be ignored for the last descriptor in the chain (denoted by a descriptor without the *Chain* bit set). The *External Descriptor Next* bit is used to denote the type of the next descriptor in the chain. Chain operations can be initiated by writing to the internal start bit or by triggering the start input signal associated with the first descriptor in the chain.

If a chain operation is configured with all descriptors having the *Interrupt on Process* bit cleared, an interrupt will only be generated on error or when the operation described by the last descriptor in the chain has completed.

Alternatively, if the *Interrupt on Process* bit is set for one or more descriptors in a chain, an interrupt will be generated when the operation described in each descriptor with its *Interrupt on Process* bit set is completed, however, this will not stall the next descriptor in the chain from being processed by the DMA controller, unless the associated interrupt queue has backed-up.

Note: Descriptor chaining should only be performed with buffer descriptors of the same priority level.

Figure 5 shows the format of one possible descriptor chain. Notice that the *Chain* bit is set for every descriptor other than the last. In this case, the *Interrupt on Process* bit is set for the first internal descriptor in the chain, Internal BD0 and External BD1. This will generate an interrupt when each of these descriptors are processed. No interrupt will be generated for the processing of External BD0. An interrupt will always be generated when the last descriptor in a chain has been processed, regardless of the Interrupt on Process configuration.

Figure 5 • Example Descriptor Chain

| Internal Descr   | iptor 0 | External Descriptor 0 |   | External Descr   | iptor 1 |

|------------------|---------|-----------------------|---|------------------|---------|

| Int On Proc      | 1       | Int On Proc           | 0 | Int On Proc      | N/A     |

| Chain            | 1       | Chain                 | 1 | Chain            | 0       |

| Ext Dscrptr Next | 1       | Ext Dscrptr Next      | 1 | Ext Dscrptr Next | N/A     |

| Nxt Dscrptr Addr |         | Nxt Dscrptr Addr      |   | Nxt Dscrptr Addr | N/A     |

CoreAXI4DMAController supports a source address and destination no-op feature to allow an internal descriptor to point at an external descriptor without the internal descriptor performing a DMA data transfer. Refer to the *Source* and *Destination Operation* fields of the descriptor's *Configuration* register.

### 3.4.2 Cyclic Operations

Cyclic operations can be set up by creating a number of buffer descriptors with the *Chain* bit set in each buffer descriptor. The *Next Descriptor* field for each descriptor should be assigned the number of the next descriptor in the chain. Unlike standard chain operations, the last descriptor should have the *Chain* bit set and should point back to the first descriptor in order to make the operation cyclic. The cyclic operation is initiated by writing to the associated start bit for the first buffer descriptor in the cyclic chain. The flow control bits must be set again for each descriptor every time that the descriptor has been processed provided that there is valid data at the source and room for data at the destination. If a descriptor is reached without one or both flow control bits set, the DMA operation will be passed over in the DMA arbiter, allowing other DMA operations to proceed while waiting on buffer allocation.

Figure 6 • Example Cyclic Descriptor Chain

Cyclic operations can be terminated by clearing the *Chain* bit in the descriptor to stop at when next reached. When this descriptor is reached and the DMA operation within the descriptor has been carried out, an interrupt will be asserted signifying the completion of the DMA cyclic operation. If external buffer descriptors are included in a descriptor chain, the cycle can only be stopped on an internal descriptor

from the Control interface of CoreAXI4DMAController. The chain can terminate on an external descriptor if the control master clears the *Chain* bit in the external descriptor's *Configuration* register in the AXI4 memory map address space.

It is recommend that the *Interrupt on Process* bit is asserted for at least the last or tail descriptor in a descriptor chain to provide notice to the firmware application that the chain has been processed and that the *Source Data Valid* and *Destination Data Ready* flow control bit will need to be set for each descriptor in the chain before another complete cycle of the chain can take place. The DMA arbiter allows the DMA transfer to continue on each descriptor in the chain provided that both flow control bits are set and that the descriptor is valid. The status of the next descriptor's flow control bits will not impact the current descriptors service.

#### 3.4.2.1 Ping-Pong

Support for ping-pong cyclic DMA operations where data is read from one location and written to two or more memory buffers with an interrupt generated every time that a buffer is filled is provided through use of descriptor chaining and the *Interrupt on Process* bit within buffer descriptors. The *Interrupt on Process* bit causes an interrupt to be raised every time that a descriptor has been processed. This feature is supported for both internal and external buffer descriptors. The resetting of the data valid bit signifies that the buffer can be re-written to by the DMA controller.

#### Figure 7 • Ping-Pong Cyclic Descriptor Chain

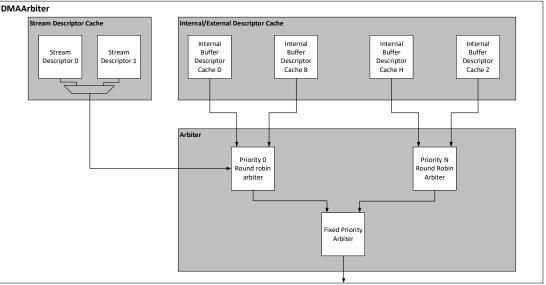

## 3.5 AXI4-Stream Bridge

In addition to AXI4 memory-map to memory-map DMA operations, CoreAXI4DMAController provides a bridge to the AXI4 memory-map address space for AXI4-Stream masters. Before a stream master initiates a stream transaction, the Control master must first write a description of the imminent AXI4-Stream transaction to the AXI4 memory map in the stream descriptor format.

Next the address of the *Configuration* register of this stream descriptor needs to be written to the *Stream Descriptor Address* register within CoreAXI4DMAController associated with the TDEST signal value of the AXI4-Stream transaction. The TDEST signal provides destination routing information, used to multiplex between the 4 *Stream Descriptor Address* registers inside CoreAXI4DMAController, as shown in Figure 8.

Figure 8 • AXI4-Stream to AXI4 Memory Map Bridging

Once the first transfer of the AXI4-Stream transaction is received, the TDEST signal is used to select the *Stream Descriptor Address* register that contains the address of the stream descriptor describing the AXI4-Stream transaction. The stream descriptor is then fetched over the AXI4 DMA interface once the current AXI4 DMA transaction completes, whilst the stream data is cached in parallel. If the stream descriptor is valid then it is loaded into the DMA Arbiter where it competes for bandwidth with other priority 0 requests. Otherwise, an invalid descriptor interrupt event is generated. Once bandwidth is allocated to the stream request, if the *Destination Data Ready* flow control bit was set when the descriptor was fetched, the AXI4 memory map forward operation commences on the AXI4 DMA interface until it is detected as begin set, at which point the AXI4 memory map forward commences.

Once the AXI4 memory-map forward related to the AXI4-Stream read is completed, an interrupt is generated on the Interrupt 0 output.

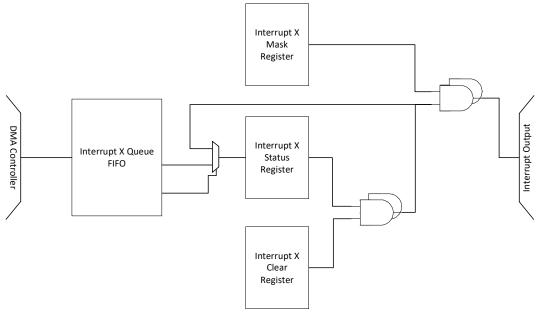

## 3.6 Interrupts

CoreAXI4DMAController provides a configurable number of interrupt outputs, each with independent status, mask and clear registers along with independent configurable depth queues. Descriptors must be associated with interrupt outputs at instantiation time. Multiple descriptors may be associated with a single interrupt output. Figure 9 shows the logic implemented for each enabled interrupt output.

#### Figure 9 • Interrupt Queue Logic

Interrupts are generated on error or completion. When configuring a descriptor, the *Interrupt on Process* field provides the user with a means to generate an interrupt every time that a particular descriptor is processed in a chain or circular buffer configuration, provided that this descriptor is not the last descriptor in the chain. DMA operations are not halted for interrupts of this type and will proceed in the background provided that the associated interrupt queue has not backed-up.

The current interrupt status will remain valid in the *Interrupt X Status* register associated with the interrupt output until all unmasked bits (masked-off using the *Interrupt Mask* register) in the *Interrupt Status* register have been cleared through the *Interrupt Clear* register.

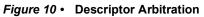

## 3.7 Arbitration

CoreAXI4DMAController supports fixed priority arbitration between multiple priority levels. If multiple requests exist of the same priority level, round-robin arbitration is performed between these requests. Higher priority requests are allowed to perform larger AXI4 burst transfers. This forces faster re-entrance into the arbitration logic by lower priority requests to ensure that higher priority requests are detected sooner.

**Note:** No bandwidth is allotted to lower priority descriptor requests when a request from a higher priority descriptor with both its flow control bits set exists.

Since, a total transfer size of 8 MB is permitted for an operation of a single descriptor, DMA operations are divided into multiple AXI4 transactions, with a maximum permitted transaction size of 4 KB to provide AXI4 boundary protection. Access is re-evaluated every time that an AXI4 transaction completes. If multiple large descriptor requests of the same priority level exist, AXI4 transactions of each descriptor will be interleaved in a round-robin fashion.

**Note:** CoreAXI4DMAController does not support interleaving of transfers within AXI4 transactions (xID signal unused). Only 1 descriptor is serviced per AXI4 transaction.

When enabled, AXI4-Stream requests are interleaved with operations of the highest priority level, priority 0. If the performance of the AXI4-Stream master is paramount, no internal descriptors should be assigned priority 0 priority association at instantiation time to allocate the entire bandwidth of the AXI4 memory map interface to the AXI4-Stream operation. Unlike standard AXI4 DMA operations which enter back into the arbitration algorithm every time that an AXI4 transaction is performed provided that the destination transaction does not span a 4 KB boundary, which is not aligned to the source address (in which case the core will perform multiple AXI writes to empty the read cache which was filled by a single AXI read transaction before entering back into arbitration), whether or not the AXI4 transaction completely services the descriptor request, AXI4-Stream operations do not enter back into arbitration until the entire stream request has been serviced, even if this requires multiple AXI4 write transactions to prevent crossing a 4 KB boundary in a sequential transaction and to empty the stream read cache.

Priority level assignment should be performed in a descending, contiguous fashion. If a priority level is enabled with no descriptors allocated to it (apart from priority 0 when Stream support is enabled), the underlying logic related to this priority level will be removed from the core. For this reason, no priority level should be enabled without descriptors allocated to it when lower priority levels are enabled with descriptors allocated to them.

To reduce the setup overhead on DMA transfers, the core allows multiple descriptors to be kicked-off in a single write to the *Start Operation* register. It is difficult to determine the order that DMA operations will take place in as the core has the facility for multiple start bits to get kicked-off in the same cycle, each

with shared or separate priority levels. All start bits are maintained in an internal register and loaded into the descriptor cache using a non-weighted round-robin arbiter, with only one start bit loaded in any given cycle. The weighted round-robin DMA arbiter then reads out of the descriptor cache and fills a two-stage pipeline to ensure that DMA transfers happen in a back-to-back fashion on the DMA interface and to ensure that read-ahead can be performed for the next DMA operation as there are two internal caches. To ensure that DMA operations happen in order, either wait for an interrupt to be received on the first operation before kicking off the next operation, else form a chain with the descriptors of interest.

## 3.8 AXI Transactions

The source and destination addresses of all DMA operations must be aligned to AXI bus width instantiated.

Note: Unaligned AXI transactions and data realignment are not performed by CoreAXI4DMAController.

The size of the AXI transaction generated is dependent upon the width of the AXI DMA interface instantiated. CoreAXI4DMAController generates transactions with the AxSIZE field set at the maximum for the instantiated bus width exclusively.

The length of the AXI transaction is dependent upon the priority level of the descriptor which the AXI transaction is related to, the maximum permitted burst size at this priority level and the source address, destination address and number of bytes in the DMA operation. If the store DMA operation spans a 4 KB boundary, CoreAXI4DMAController may generate multiple shorter read transactions to prevent crossing the 4 KB boundary in a sequential transfer and vice versa for the forward transactions if the forward DMA operation spans a 4 KB boundary. Arbitration is performed on completion of each read transaction to determine if a higher priority requests exists or if there are other requests at this priority level that need to be serviced. The last transfer of the last transaction of a DMA operation may be narrow by way of the AXI write strobes to provide N-byte DMA transfer support.

A single AXI read transaction may result in multiple AXI write transactions if the source operation is confined within a 4 KB slot and the destination operations spans a 4 KB boundary.

The core supports DMA read ahead to read in the next data to the internal cache whilst the previous write operation is completing. This increases the throughput of the AXI interface significantly for queued AXI DMA operations in busy AXI systems. AXI outstanding address transactions are not generated by CoreAXI4DMAController.

## 3.9 AXI4-Stream Transactions

CoreAXI4DMAController supports AXI4-Stream transactions where each bit of TSTRB mirrors TKEEP, indicating either data or null bytes. Position bytes occur when a TKEEP bit is asserted and the corresponding TSTRB bit is de-asserted. Position bytes are not supported by CoreAXI4DMAController.

The core expects all AXI4-Stream transactions to start from an address aligned to bus width, set through the *AXI\_DMA\_DWIDTH* parameter. The first transfer in the transaction cannot be unaligned through the use of TKEEP and TSTRB.

In addition, the core permits the last transfer in an AXI4-Stream transaction to be narrow by keeping the TKEEP and TSTRB bits low for the associated byte lanes, making N-byte AXI4-Stream to AXI4 memory map bridging possible. An example of this would be where TKEEP and TSTRB are both 0x7F for the last transfer in the transaction and 0xFF for all other transfers in the transaction on a 64-bit bus.

It is expected that all TSTRB and TKEEP bits are asserted for every transfer other than the last transfer in an AXI4-Stream transaction. Sparse strobe assertion is not supported where TSTRB and TKEEP are both 0x55 for instance.

**Note:** AXI4 Stream Transactions should be performed whenever there is no pending request for memory map to memory map data transfer and vice-versa.

## 3.10 Cache Coherence

Data integrity issues can arise where a DMA read is performed on a shared, cacheable memory where the cached memory contents has been updated but not yet written back to memory. To cover such an event, the application must ensure that the contents of the cache is written back to memory before kicking of a DMA read operation in a cacheable region. Processor operations to this memory space should be suspended until the DMA read has completed.

Similarly, where a DMA write is performed on cacheable memory, the application needs to ensure that the contents of the cache is flushed and refilled to prevent the processor from operating on out-of-date data once the memory has been written via the DMA operation. Processor operations to this memory space should be suspended until the DMA write has completed.

**Note:** Cache coherence is not handled by CoreAXI4DMAController and remains the responsibility of the Firmware application.

# 4 Interface Descriptions

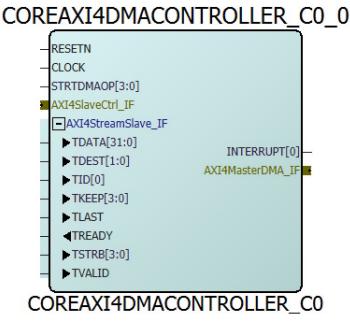

## 4.1 Signal Descriptions

Signal descriptions for CoreAXI4DMAController are defined in Table 11.

#### Table 11 • CoreAXI4DMA Controller I/O Signals

| Port Name         | Width            | Direction         | Description                                                                                                                                                                                                                                          |

|-------------------|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Ports     |                  |                   |                                                                                                                                                                                                                                                      |

| CLOCK             | 1                | Input             | Clock signal to all sequential elements within the core.                                                                                                                                                                                             |

| RESETN            | 1                | Input             | Active-low reset signal to all sequential<br>elements within the core. Reset<br>de-assertion must be synchronous to<br>CLOCK rising edge as per AXI4<br>specification. This reset should be<br>synchronized in the CLOCK clock domain<br>externally. |

|                   | AXI4-Lite Contro | ol Interface Port | S                                                                                                                                                                                                                                                    |

| CTRL_AWVALID      | 1                | Input             | Write address valid. Indicates that the control master is presenting valid write address information.                                                                                                                                                |

| CTRL_AWREADY      | 1                | Output            | Write address ready. Indicates that<br>CoreAXI4DMAController is ready to<br>receive write address information.                                                                                                                                       |

| CTRL_AWADDR[10:0] | 11               | Input             | AXI4-Lite write address bus.                                                                                                                                                                                                                         |

| CTRL_WVALID       | 1                | Input             | Write data valid. Indicates that the control master is presenting write data.                                                                                                                                                                        |

| CTRL_WLAST        | 1                | Input             | Indicates that the current transfer is the last transfer in the write transaction.                                                                                                                                                                   |

| CTRL_WREADY       | 1                | Output            | Indicates that CoreAXI4DMAController<br>is ready to receive write data.                                                                                                                                                                              |

| CTRL_WSTRB[3:0]   | 4                | Input             | Write strobes. Indicates the byte lanes<br>of the WDATA bus, which contain valid<br>write data.                                                                                                                                                      |

| CTRL_WDATA[31:0]  | 32               | Input             | AXI4-Lite write data bus.                                                                                                                                                                                                                            |

| CTRL_BVALID       | 1                | Output            | Write response valid. Indicates that<br>CoreAXI4DMAController is presenting<br>valid write response information. Only<br>occurs at the end of a write transaction.                                                                                   |

| CTRL_BREADY       | 1                | Input             | Indicates that the control master is ready to receive write response information.                                                                                                                                                                    |

| CTRL_BRESP[1:0]        | 2              | Output     | Write response. Indicates the status of a write transaction.                                                                                                                |

|------------------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                |            | Okay and SLVERR responses are<br>returned by the core.                                                                                                                      |

|                        |                |            | The core returns SLVERR when an<br>invalid address is latched on AXI4-Lite<br>write address bus.                                                                            |

| CTRL_ARVALID           | 1              | Input      | Read address valid. Indicates that the<br>control master is presenting valid<br>address information.                                                                        |

| CTRL_ARREADY           | 1              | Output     | Read address ready. Indicates that<br>CoreAXI4DMAController is ready to<br>receive address information.                                                                     |

| CTRL_ARADDR[10:0]      | 11             | Input      | AXI4-Lite read address bus.                                                                                                                                                 |

| CTRL_RVALID            | 1              | Output     | Read data valid. Indicates that<br>CoreAXI4DMAController is presenting<br>valid read data.                                                                                  |

| CTRL_RREADY            | 1              | Input      | Indicates that the control master is ready to receive read data.                                                                                                            |

| CTRL_RDATA[31:0]       | 32             | Output     | AXI4-Lite read data bus.                                                                                                                                                    |

| CTRL_RLAST             | 1              | Output     | Indicates that the current transfer is the last transfer in the read transaction.                                                                                           |

| CTRL_RRESP[1:0]        | 2              | Output     | Read response valid. Indicates that<br>CoreAXI4DMAController is presenting<br>valid read response information. Valid<br>for every transfer in a transaction.                |

|                        |                |            | <b>Okay</b> and <b>SLVERR</b> responses are<br>returned by the core. The core returns<br>SLVERR when an invalid address is<br>latched on the AXI4-Lite read address<br>bus. |

|                        | AXI4 DMA Inter | face Ports |                                                                                                                                                                             |

| DMA_AWVALID            | 1              | Output     | Write address valid. Indicates that<br>CoreAXI4DMAController is presenting<br>valid address information.                                                                    |

| DMA_AWREADY            | 1              | Input      | Write address ready. Indicates that the AXI4 slave is ready to receive address information.                                                                                 |

| DMA_AWADDR[31:0]       | 32             | Output     | DMA write address bus.                                                                                                                                                      |

| DMA_AWID[ID_WIDTH-1:0] | ID_WIDTH       | Output     | Write address ID. Identification tag for write address group of signals.                                                                                                    |

|                        |                |            | Driven out as zeros as ID support not<br>implemented by<br>CoreAXI4DMAController. All<br>transactions are processed in order.                                               |

| DMA_AWLEN[7:0]                    | 8                    | Output | Indicates the number of transfers in the<br>AXI write transaction. Allows for<br>between 1 and 256 transfers per<br>transaction.                               |

|-----------------------------------|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA_AWSIZE[2:0]                   | 3                    | Output | Indicates the size of transfers in the AXI<br>write transaction.<br>CoreAXI4DMAController generates<br>transactions of the data bus width size<br>exclusively. |

|                                   |                      |        | $DMA\_AWSIZE = \frac{\log_2(\frac{AXI\_DMA\_DWIDTH}{8})}{8}$                                                                                                   |

| DMA_AWBURST[1:0]                  | 2                    | Output | Write burst address type. Only fixed and incrementing DMA transfers are generated by CoreAXI4DMAController.                                                    |

| DMA_WVALID                        | 1                    | Output | Write data valid. Indicates that<br>CoreAXI4DMAController is presenting<br>valid write data.                                                                   |

| DMA_WLAST                         | 1                    | Output | Indicates that the current transfer is the last transfer in the write transaction.                                                                             |

| DMA_WREADY                        | 1                    | Input  | Indicates that the AXI4 slave is ready to receive write data.                                                                                                  |

| DMA_WSTRB[(AXI_DMA_DWIDTH/8)-1:0] | AXI_DMA_DW<br>IDTH/8 | Output | Write strobes. Indicates the byte lanes<br>of the WDATA bus which contain valid<br>write data.                                                                 |

| DMA_WDATA[AXI_DMA_DWIDTH-1:0]     | AXI_DMA_DW<br>IDTH   | Output | DMA write data bus.                                                                                                                                            |

| DMA_BVALID                        | 1                    | Input  | Write response valid. Indicates that the AXI4 slave is presenting valid write response information. Only occurs at the end of a transaction.                   |

| DMA_BREADY                        | 1                    | Output | Indicates that CoreAXI4DMAController<br>is ready to receive write response<br>information.                                                                     |

| DMA_BID[ID_WIDTH:0]               | ID_WIDTH             | Input  | Write response ID. Identification tag for write response group of signals.                                                                                     |

| DMA_BRESP[1:0]                    | 2                    | Input  | Write response. Indicates the status of a write transaction.                                                                                                   |

| DMA_ARVALID                       | 1                    | Output | Read address valid. Indicates that<br>CoreAXI4DMAControlleris presenting<br>valid address information.                                                         |

| DMA_ARREADY                       | 1                    | Input  | Read address ready. Indicates that the control master is ready to receive address information.                                                                 |

| DMA_ARADDR[31:0]                  | 32                   | Output | DMA read address bus.                                                                                                                                          |

| DMA_ARID[ID_WIDTH-1:0]        | ID_WIDTH             | Output  | Read ID. Identification tag for read address group of signals.                                                                                                                                         |

|-------------------------------|----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               |                      |         | Driven out as zeros as ID support not<br>implemented<br>byCoreAXI4DMAController. All                                                                                                                   |

|                               |                      |         | transactions are processed in order.                                                                                                                                                                   |

| DMA_ARLEN[7:0]                | 8                    | Output  | Indicates the number of transfers in the AXI read transaction. Allows for between 1 and 256 transfers per transaction.                                                                                 |

| DMA_ARSIZE[2:0]               | 3                    | Output  | Indicates the size of transfers in the AXI read transaction.<br>CoreAXI4DMAController generates transactions of the data bus width size exclusively.<br>DMA_ARSIZE = $log_2(\frac{AXI_DMA_DWIDTH}{8})$ |

| DMA_ARBURST[1:0]              | 2                    | Output  | Read burst address type. Only fixed and incrementing DMA transfers are generated by CoreAXI4DMAController.                                                                                             |

| DMA_RVALID                    | 1                    | Input   | Read data valid. Indicates that the AXI4 slave is presenting read data.                                                                                                                                |

| DMA_RREADY                    | 1                    | Output  | Indicates that the<br>CoreAXI4DMAController is ready to<br>receive read data.                                                                                                                          |

| DMA_RDATA[AXI_DMA_DWIDTH-1:0] | AXI_DMA_DW<br>IDTH   | Input   | DMA read data bus.                                                                                                                                                                                     |