#### Getting Started with the RISC-V Based PolarFire<sup>®</sup> SoC FPGA Webinar Series Session 17 AMP Mode

A Leading Provider of Smart, Connected and Secure Embedded Control Solutions

Hugh Breslin, Design Engineer Thursday Sept. 10, 2020

#### Supporting Content www.microsemi.com/Mi-V "Renode Webinar Series"

#### Webinar 1 (May 2): Discover Renode for PolarFire™ SoC Design and Debug

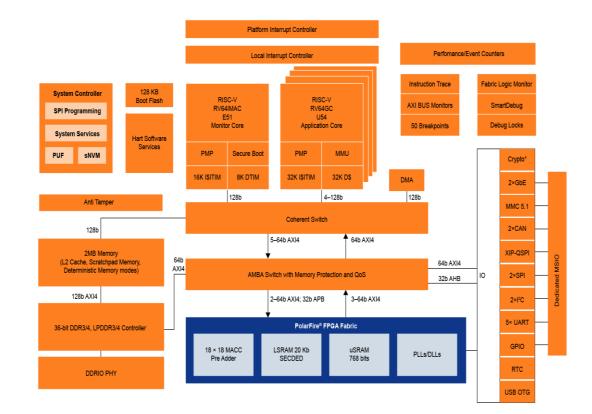

In this introductory session, we will provide you with an overview of SoftConsole 6.0 with Renode™ integration. We will introduce you to the Renode development framework and provide an overview of the platform and its features. You will also learn about the PolarFire™ SoC architecture and how to use Renode to develop your application.

Webinar 1: Discover Renode for PolarFire<sup>®</sup> SoC Design and Debug Webinar 2: How to Get Started with Renode for PolarFire SoC Webinar 3: Learn to Debug a Bare-Metal PolarFire SoC Application with Renode Webinar 4: Tips and Tricks for Even Easier PolarFire SoC Debug with Renode Webinar 5: Add and Debug PolarFire SoC Models with Renode Webinar 6: Add and Debug Pre-Existing Model in PolarFire SoC Webinar 7: How to Write Custom Models Webinar 8: What's New in SoftConsole v6.2 Webinar 9: Getting Started with PolarFire SoC Webinar 10: Introduction to the PolarFire SoC Bare-Metal Library Webinar 11: Handling Binaries Webinar 12: Simple Peripheral as Software Stimulus Webinar 13: Two Baremetal Applications on PolarFire SoC Webinar 14: The PolarFire SoC Icicle Kit Model on Renode Webinar 15: Building and running Linux Webinar 16: Linux on PolarFire SoC

### **Coming Soon! RISC-V® Innovation Unleashed**

- New PolarFire SoC webinar series

- Registrations go live from September 16<sup>th</sup>

- https://www.microchip.com/training/webinars

| Webinars   Microchip Technology × +      |                                   |              |                          |                            |              |       |  |  |  | — | Ć | 7 | ×         |   |

|------------------------------------------|-----------------------------------|--------------|--------------------------|----------------------------|--------------|-------|--|--|--|---|---|---|-----------|---|

| $\leftarrow$ $\rightarrow$ C $\triangle$ | 🗎 microchip.com/training/webinars |              |                          |                            |              |       |  |  |  | ☆ | 8 | * | <b>\$</b> | : |

| <b>Міскосні</b> р                        | Products                          | Applications | Tools<br>and<br>Software | Support<br>and<br>Training | Order<br>Now | About |  |  |  |   | - | } | -         | Q |

| Home / Training                          | g / Webina                        | ars          |                          |                            |              |       |  |  |  |   |   |   |           |   |

|                                          |                                   |              |                          |                            |              |       |  |  |  |   |   |   |           |   |

#### Webinars

#### Design Resources

Discover how to use our ecosystem of hardware tools, software and other resources to simplify and speed up your development.

Development Tools

#### Security

Learn about the latest trends and new developments for safeguarding your designs.

• SHIELDS UP! Webinar Series

## Agenda

- Multiprocessing

- Symmetric Multiprocessing

- Asymmetric Multiprocessing

- Configuring Asymmetric Multiprocessing

## Multiprocessing

## Multiprocessing

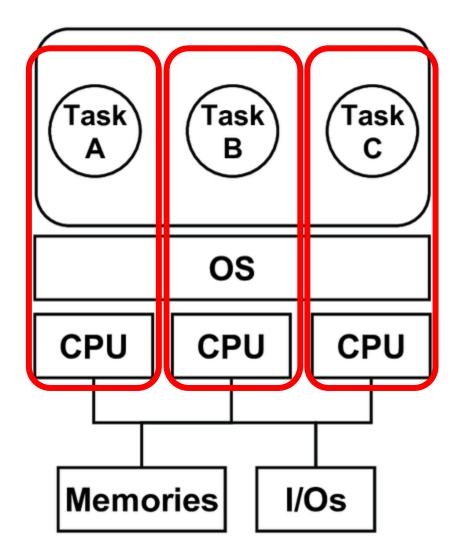

- Multiple CPUs in a single system

- Shared memory and peripherals

- Execute multiple tasks simultaneously

- This is not the same as parallel processing

#### Multiprocessing CPU Affinity

- This binds a process to a core / cores

- Run a process on a subset of cores

- Run a process on a specific core

- Achieved through a system call

✓ Improve cache performance

#### **Multiprocessing** CPU Affinity

- Check affinity with taskset -cp [PID]

- Returns

pid 9726's current affinity list: 0-3

Set affinity with

taskset -cp 0,3 9726

• Returns

pid 9726's current affinity list: 0,1,2,3 pid 9726's new affinity list: 0,3

#### Multiprocessing CPU Affinity

- Launch a process with a certain affinity taskset OxA webserver

- 0xA == 1010 cores 1 and 3

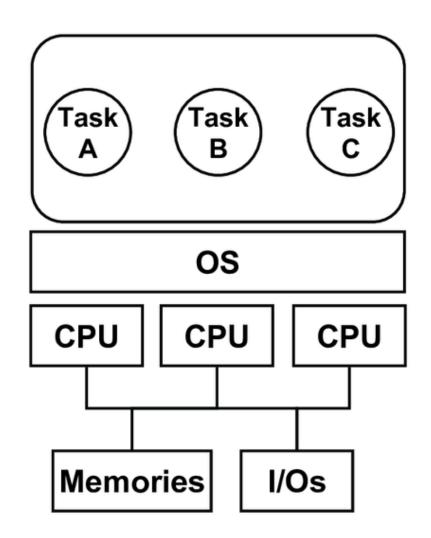

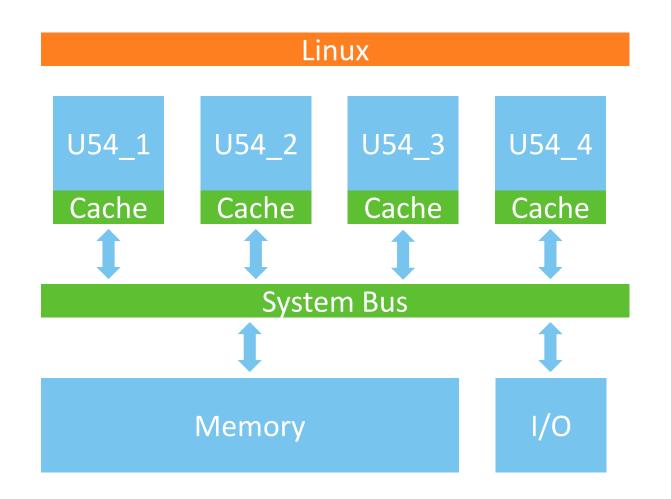

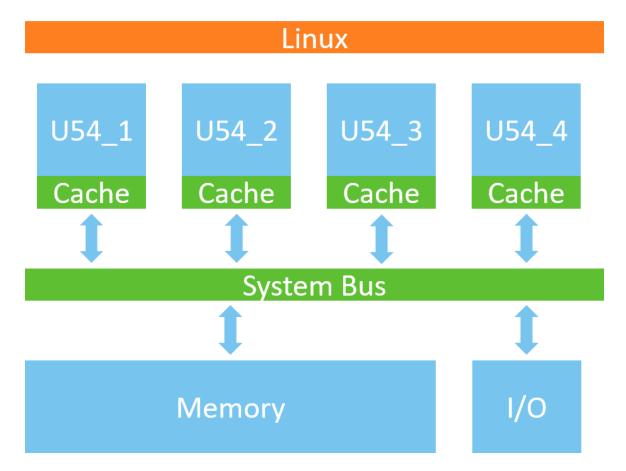

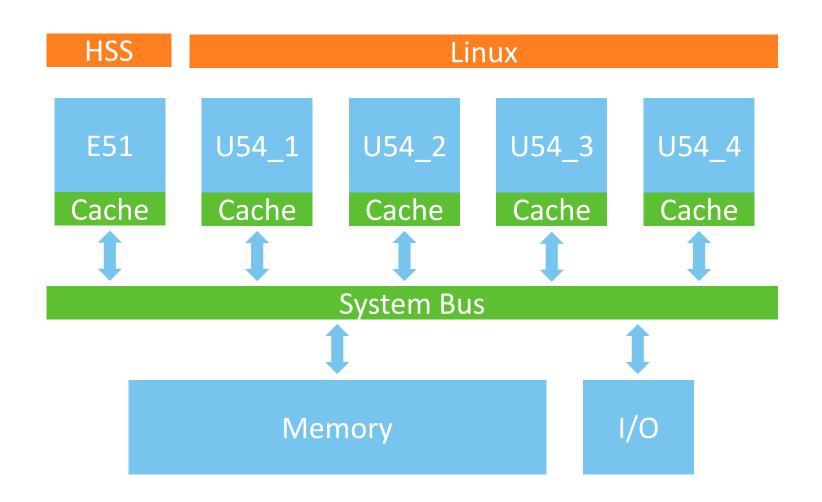

• A single OS with two or more of the same processor

- All processors are treated equally

- Shared memory space

- Tasks can be run on any CPU

- The same task should not be run on 2 CPUs

- If a processor fails, the system stays up

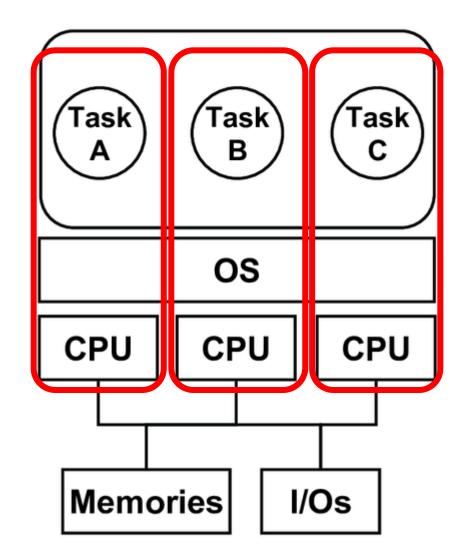

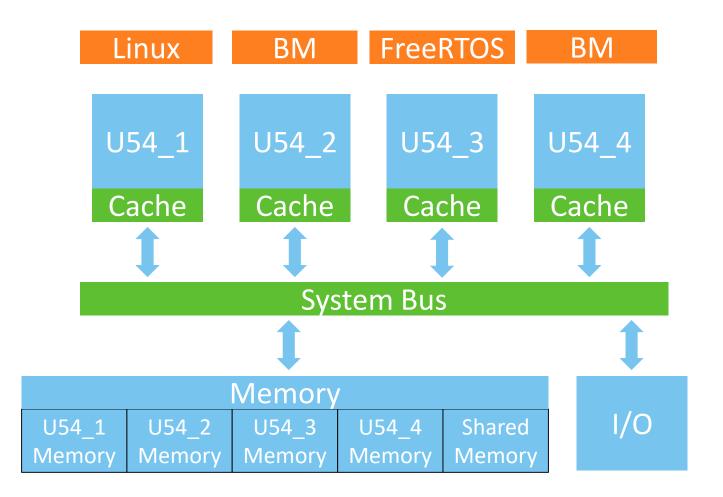

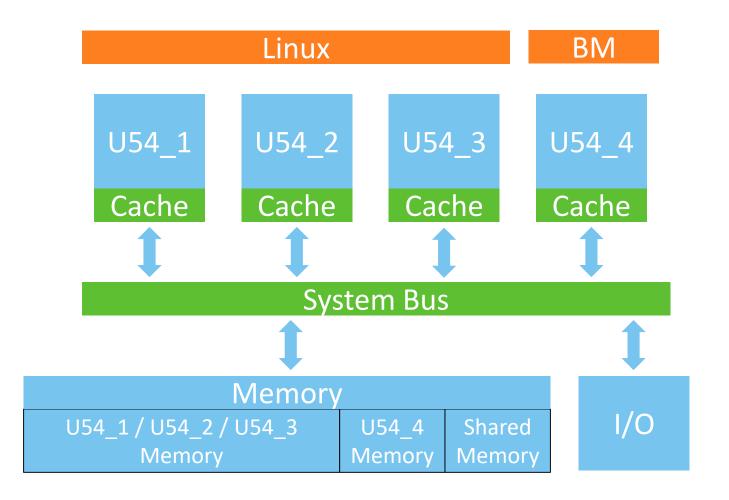

Multiple OS's / bare metal running on separate processors

Multiple OS's / bare metal running on separate processors

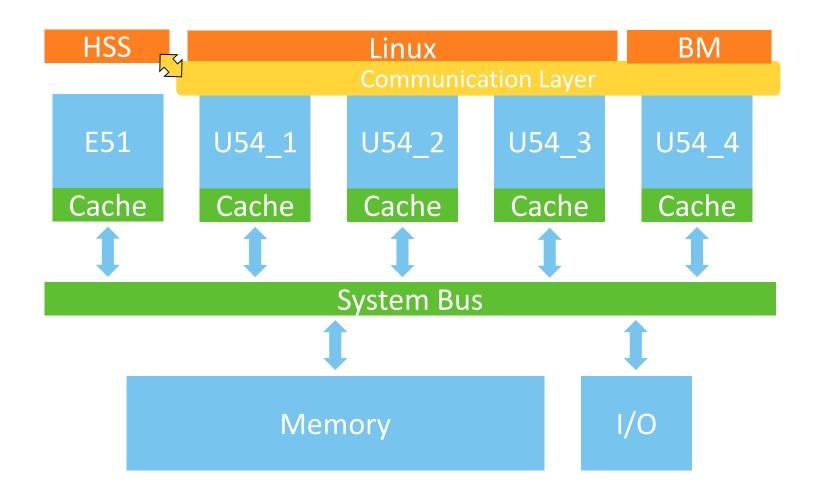

#### Blend SMP system into AMP

#### Inter processor communication

####

# Configuring Asymmetric Multiprocessing

#### Asymmetric Multiprocessing The HSS

- A superloop monitor running on the E51 processor, which receives requests from the individual U54 application processors to perform certain services on their behalf.

- A Machine-Mode software interrupt trap handler, which allows the E51 to send messages to the U54s and request them to perform certain functions for it related to rebooting a U54.

SSMB – "Secure Software Messaging Bus"

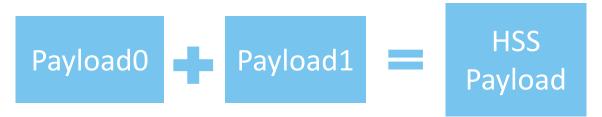

#### Asymmetric Multiprocessing The HSS: Payloads

Payloads are created for the system configuration containing the binaries to be run

• See Webinar 13 "Two Bare-Metal Applications on PolarFire SoC"

#### Asymmetric Multiprocessing The HSS: Payloads

- Payload 0: Linux for harts 1, 2 & 3

- Payload 1: Bare metal for hart 4

#### Asymmetric Multiprocessing The HSS: Linux payload

#### • Linux for harts 1, 2 & 3

• Edit the device tree to remove hart 4 and build

| P master •    polarfire-soc-buildroot-sdk / conf / icicle-kit-es / icicle-kit-es.dts                                                                                                                                                                                                                                                                                                                                                             | meta-polarfire-soc-yocto-bsp / recipes-kernel / linux / files / icicle-kit-es / icicle-kit-es / icicle-kit-es-a000-microchip.dts                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| ConchuOD dts: update dts from yocto                                                                                                                                                                                                                                                                                                                                                                                                              | Ihanlyu Clock Driver remove spaces in names Latest commit 1                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| All contributor                                                                                                                                                                                                                                                                                                                                                                                                                                  | A 1 contributor                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| 325 lines (321 sloc) 10.9 KB Raw Blame                                                                                                                                                                                                                                                                                                                                                                                                           | 351 lines (346 sloc)         11.7 KB         Raw         Blame         Copy File         11.73 K                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

| <pre>// {     // {         #address-cells = &lt;2&gt;;         #size-cells = &lt;2&gt;;         #size-cells = &lt;2&gt;;         compatible = "SiFive,FU540G-dev", "fu540-dev", "sifive-dev";         model = "SiFive,FU540G";         L45: cpus {             #address-cells = &lt;1&gt;;             #size-cells = &lt;1&gt;;             #size-cells = &lt;0&gt;;             timebase-frequency = &lt;1000000&gt;;         L8: cpu@0 {</pre> | <pre>1 /dts-v1/;<br/>2 / {<br/>3      #address-cells = &lt;2&gt;;<br/>4      #size-cells = &lt;2&gt;;<br/>5      compatible = "SiFive,FU540G-dev", "fu540-dev", "sifive-dev";<br/>6      model = "SiFive,FU540G";<br/>7      L45: cpus {<br/>8            #address-cells = &lt;1&gt;;<br/>9            #size-cells = &lt;0&gt;;<br/>10            timebase-frequency = &lt;1000000&gt;;<br/>11           L8: cpu@0 {<br/>12</pre> |  |  |  |  |  |  |  |  |  |  |

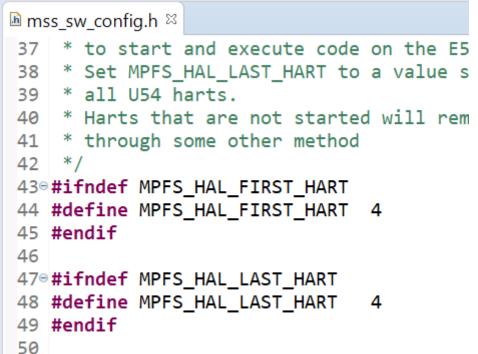

#### **Asymmetric Multiprocessing** The HSS: Bare metal payload

- Set the system "MPFS\_HAL\_FIRST\_HART" to 4

- Target the desired memory in the linker script (e.g LIM / DDR)

• Build

Watch webinar 11 "Handling Binaries"

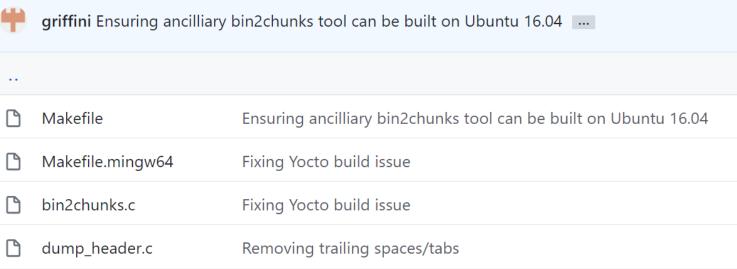

#### Asymmetric Multiprocessing The HSS: Payloads

- Use the payload generator in the HSS to generate a payload

- Currently bin2chunks this will be updated

#### Asymmetric Multiprocessing The HSS: Payloads

- Program the eNVM with the HSS (if not done already)

- Program the target (e.g eMMC / SD)

- Boot

- Voila!

## Agenda

- Multiprocessing

- Symmetric Multiprocessing

- Asymmetric Multiprocessing

- Configuring Asymmetric Multiprocessing

### **Coming Soon! RISC-V® Innovation Unleashed**

- New PolarFire SoC webinar series

- Registrations go live from September 16<sup>th</sup>

- https://www.microchip.com/training/webinars

| Webinars   Microchip Technology × + |       |                                   |              |                          |                            |              |       |  |  | — | ć | ] | ×         |    |  |   |

|-------------------------------------|-------|-----------------------------------|--------------|--------------------------|----------------------------|--------------|-------|--|--|---|---|---|-----------|----|--|---|

| $\leftrightarrow \rightarrow$       | CÒ    | 🗎 microchip.com/training/webinars |              |                          |                            |              |       |  |  | ☆ | 8 | * | <b>\$</b> | :  |  |   |

| <b>Міс</b> я                        | OCHIP | Products                          | Applications | Tools<br>and<br>Software | Support<br>and<br>Training | Order<br>Now | About |  |  |   |   |   | -         | ]_ |  | Q |

| Home / Training / Webinars          |       |                                   |              |                          |                            |              |       |  |  |   |   |   |           |    |  |   |

|                                     |       |                                   |              |                          |                            |              |       |  |  |   |   |   |           |    |  |   |

#### Webinars

#### Design Resources

Discover how to use our ecosystem of hardware tools, software and other resources to simplify and speed up your development.

Development Tools

#### Security

Learn about the latest trends and new developments for safeguarding your designs.

• SHIELDS UP! Webinar Series

# Thank you!

Any questions?