# Core1553BRT\_APB v4.3 Handbook

# **Table of Contents**

|   | Preface       4         About this Document       4         Intended Audience       4                                                                                                   |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Introduction.5General Description5Verification and Compliance6Fail-Safe State Machines7Core Version7Version Compatibility7Device Requirements8                                          |

| 2 | MIL-STD-1553B Bus Overview       9         Message Types       9         Word Formats       11                                                                                          |

| 3 | Operation12Status Word Settings12Transfer Status Words13RT-to-RT Transfer Support13Mode Codes14Loopback Tests15Error Detection16Built-In Test Support17Command Legalization Interface18 |

| 4 | Interface Descriptions.       19         Parameters on Core1553BRT_APB       19         I/O Signal Descriptions       20                                                                |

| 5 | Interface Timing24Specifications24Transceiver Loopback Delays25Clock Requirements25                                                                                                     |

| 6 | Tool Flows26Licensing26Precompiled Libraries26SmartDesign27Simulation Flows29Synthesis in Libero29Place-and-Route in Libero29                                                           |

| 7 | Testbench Operation and Modification.    30      User Testbench    30                                                                                                                   |

| 8  | Software Interface                     |      |

|----|----------------------------------------|------|

|    | Метогу Мар                             |      |

|    | Register Set                           |      |

|    | Memory Buffers                         | . 37 |

| 9  | Implementation Hints                   | 39   |

|    | External Command Word Legality Example | . 39 |

|    | Bus Transceivers                       | . 42 |

| 10 | Ordering Information                   |      |

|    | Ordering Codes                         | . 43 |

| А  | List of Changes                        | 44   |

# Preface

### **About this Document**

This handbook provides details about the Core1553BRT\_APB DirectCore module and how to use it.

## **Intended Audience**

Designers using Libero<sup>®</sup> System-on-Chip (SoC) or Libero Integrated Design Environment (IDE).

# 1 – Introduction

### **General Description**

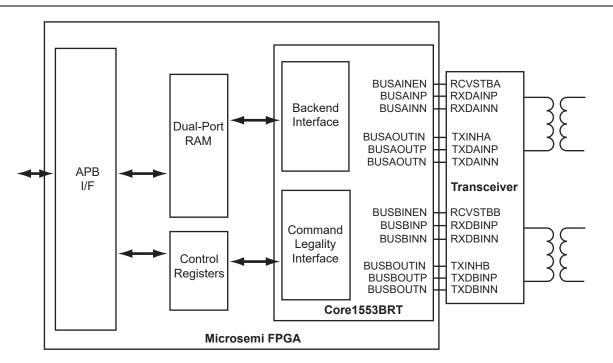

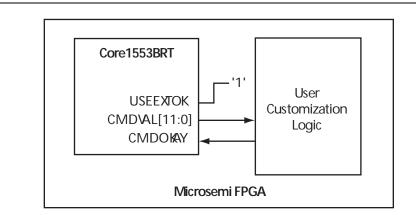

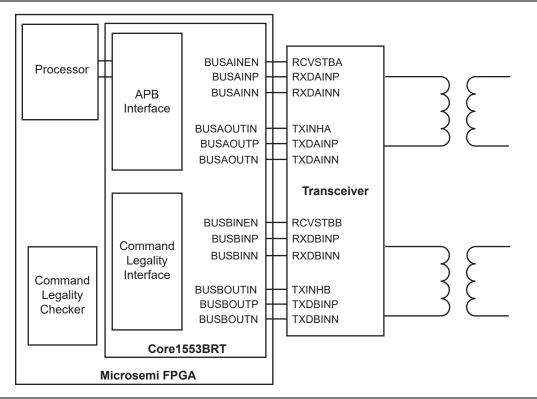

Core1553BRT\_APB provides a complete, dual-redundant MIL-STD-1553B remote terminal (RT), apart from the transceivers required to interface to the bus. A typical system implementation using Core1553BRT\_APB is shown in Figure 1-1 and Figure 1-2 on page 6.

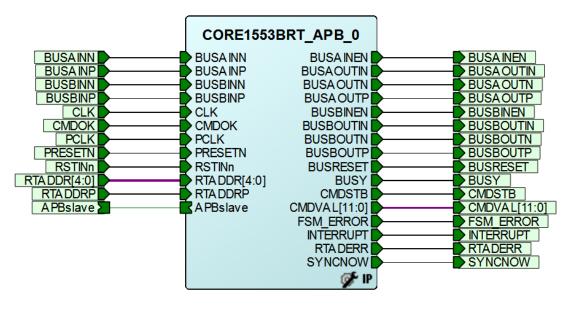

#### Figure 1-1 • Typical Core1553BRT\_APB System

At a high level, Core1553BRT\_APB simply provides a set of memory-mapped subaddresses that "receive data written to" or "transmit data read from." The core has an APB3 slave interface and internal memory buffer to allow simple connection to an AMBA-based processor system.

The core supports all 1553B mode codes and allows the user to designate as illegal any mode code or any particular subaddress for both transmit and receive operations. The command legalization can be done within the core or in an external command legality block via the command legalization interface.

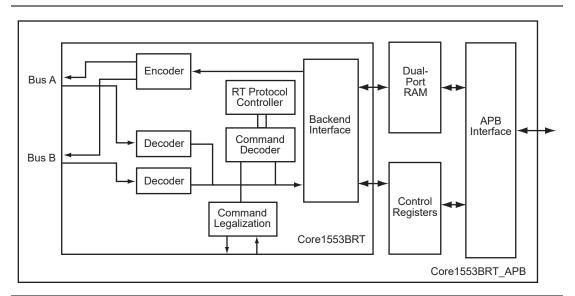

The core consists of six main blocks: 1553B encoder, 1553B decoders, the APB interface, a command decoder, RT controller blocks, and a command legalization block (Figure 1-2 on page 6).

#### Figure 1-2 • Remote Terminal Block Diagram

In Core1553BRT\_APB, a single 1553B encoder is used. This takes each word to be transmitted and serializes it, after which the signal is Manchester-encoded. The encoder also includes logic to prevent the RT from transmitting for longer than the allowed period, and loopback fail logic. The loopback logic monitors the received data and verifies that the core has correctly received every word that it transmits.

The output of the encoder is gated with the bus enable signals to select which buses the RT should use to transmit.

The core includes two 1553B decoders. A decoder takes the serial Manchester data received from the bus and extracts the received data words. A decoder requires a 12, 16, 20, or 24 MHz clock to extract the data and the clock from the serial stream.

The decoder contains a digital PLL that generates a recovery clock used to sample the incoming serial data. The data is then deserialized and the 16-bit word decoded. The decoder detects whether a command or data word is received and also performs Manchester encoding and parity error checking.

The APB interface for Core1553BRT\_APB allows a simple connection to an APB-based processor system. The core contains an internal memory buffer to store incoming and outgoing 1553 messages. The access rates to this memory are slow, with one read or write every 20 µs. At 12 MHz operation, this is one read or write every 240 clock cycles.

The command decoder and RT controller blocks decode the incoming command words, verifying their legality. Then the protocol state machine responds to the command, transmitting or receiving data or processing a mode code.

Core1553BRT\_APB has an internal command legality block that verifies every 1553B command word. A separate interface is provided that, when enabled, allows the command legality decoder to be implemented outside Core1553BRT\_APB.

### **Verification and Compliance**

Core1553BRT\_APB functionality has been verified in simulation and hardware. Full functional verification against the RT test plan, as defined in MIL-HDBK-1553A, has been carried out using Core1553BRT v4.0.

### **Fail-Safe State Machines**

The main 1553B logic implements fail-safe state machines. All state machines include illegal state detection logic. If a state machine should ever enter an illegal state, the core will assert its FSM\_ERROR output and the state machine will reset. If this occurs, Microsemi<sup>®</sup> recommends that the external system reset the core and also assert the TFLAG input to inform the bus controller (BC) that a serious error has occurred within the remote terminal.

The FSM\_ERROR output can be left unconnected if the system is not required to detect and report state machines entering illegal states.

### **Core Version**

This handbook applies to Core1553BRT\_APB v4.3 and later.

## **Version Compatibility**

Core1553BRT\_APB v4.3 adds a new top-level wrapper to the previous Core1553BRT release. The base VHDL and Verilog code used in the APB version for the 1553 function is identical<sup>1</sup> to the code in the standard Core1553BRT release. The new top-level wrapper adds an APB interface and a dual-ported memory. It also converts some of the standard core inputs to parameters, rather than the user tying the inputs to GND or VCC. SmartDesign flows allow this use of parameterized configurable RTL code. This simplifies using the core in the user's design.

<sup>1.</sup> Two small changes, not affecting functionality, have been made. First, a hardwired constant, which was set to FALSE in the command word legality module, is now a generic defaulted to FALSE on the top level of the v4.3 core; this is to enable testing of the legality logic in the verification environment. Second, the version number encoding in the BIT word has been updated.

## **Device Requirements**

Core1553BRT\_APB can be implemented in several Microsemi FPGA devices. Table 1-1 gives the utilization and performance figures for the core implemented in these devices.

The core can operate with a clock of up to 24 MHz. This clock rate is easily met in all silicon families noted in Table 1-1.

| Family                     | Combinatorial | Sequential | Total | RAM<br>Blocks | Device   | Utilization | Performance<br>(CLK and PCLK) |

|----------------------------|---------------|------------|-------|---------------|----------|-------------|-------------------------------|

| IGLOO <sup>®</sup>         | 1,577         | 697        | 2,274 | 8             | AGL600   | 16%         | > 70 MHz                      |

| IGLOOe                     |               |            |       | 8             | AGLE600  |             |                               |

| ProASIC <sup>®</sup> 3     |               |            |       | 8             | A3P600   |             |                               |

| ProASIC3E                  |               |            |       | 8             | A3PE600  |             |                               |

| SmartFusion <sup>®</sup>   |               |            |       | -             | A2F200   | 50%         |                               |

| Fusion <sup>®</sup>        |               |            |       |               | AFS600   | 16%         | > 70 MHz                      |

| ProASIC <sup>PLUS®</sup>   | 2,314         | 731        | 3,045 | 16            | APA450   | 25%         | > 50 MHz                      |

| Axcelerator <sup>®</sup>   | 1,039         | 728        | 1,767 | XX            | AX500    | 21%         | > 70 MHz                      |

| RTAX-S                     |               |            |       | XX            | RTAX250S | 42%         |                               |

| SmartFusion <sup>®</sup> 2 | 1272          | 792        | 2064  | 2             | M2S050   | 1.8%        | 118 MHz                       |

| IGLOO <sup>®</sup> 2       | 1271          | 788        | 2059  | 2             | M2GL050  | 1.82%       | 120 MHz                       |

| RTG4 <sup>™</sup>          | 1350          | 790        | 2140  | 2             | RT4G150  | 0.7%        | 118 MHz                       |

| PolarFire <sup>®</sup>     | 1280          | 788        | 2068  | 2             | MPF100T  | 1%          | 185 MHz                       |

Utilization data was generated using standard Libero tool flows with typical core parameter settings. Utilization data will vary slightly with different parameter settings and tool usage.

# 2 – MIL-STD-1553B Bus Overview

The MIL-STD-1553B bus is a differential serial bus used in military and space equipment. It comprises multiple redundant bus connections and communicates at 1 Mbps.

The bus has a single active BC and up to 31 RTs. The BC manages all data transfers on the bus using the command and status protocol. The bus controller initiates every transfer by sending a command word and data if required. The selected RT will respond with a status word and data if required.

The 1553B command word contains a 5-bit RT address, transmit or receive bit, 5-bit subaddress, and 5-bit word count. This allows for 32 RTs on the bus. However, since RT address 31 is used to indicate a broadcast transfer, only 31 RTs can be connected. Each RT has 30 subaddresses reserved for data transfers. The other two subaddresses (0 and 31) are reserved for mode codes used for bus control functions. Data transfers contain up to thirty-two 16-bit data words. Mode code command words are used for bus control functions such as synchronization.

### Message Types

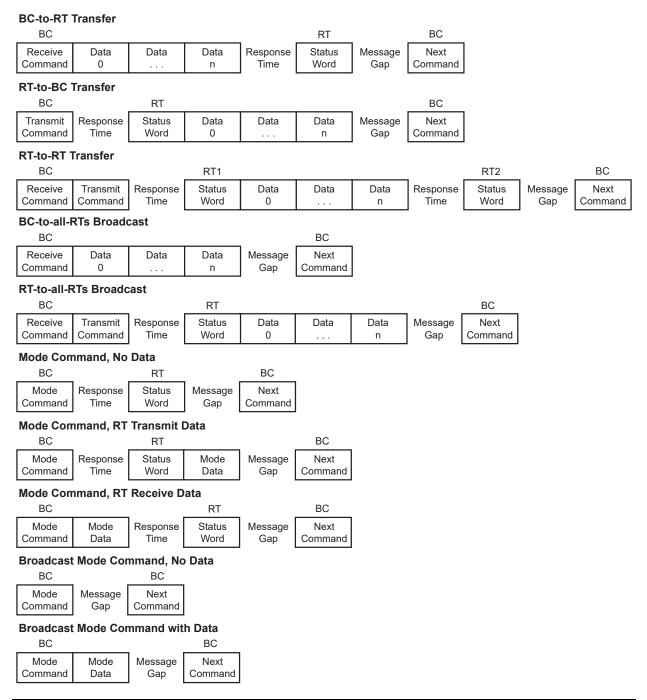

The 1553B bus supports 10 message transfer types, allowing basic point-to-point and broadcast BC-to-RT data transfers, mode code messages, and direct RT-to-RT messages. Figure 2-1 on page 10 shows the message formats.

Figure 2-1 • 1553B Message Formats

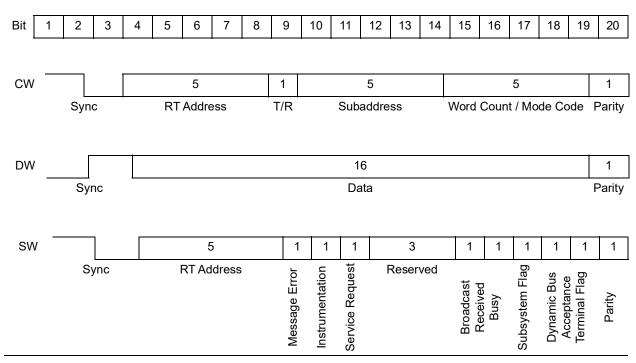

### Word Formats

There are only three types of words in a 1553B message: a command word (CW), a data word (DW), and a status word (SW). Each word consists of a 3-bit sync pattern, 16 bits of data, and a parity bit, providing the 20-bit word (Figure 2-2).

Figure 2-2 • 1553B Word Formats

# 3 – Operation

## **Status Word Settings**

Core1553BRT\_APB sets bits in the 1553B status word in compliance with MIL-STD-1553B. This is summarized in Table 3-1.

| Bit(s) | Function               | Setting                                                                                                |  |  |

|--------|------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| 15:11  | RT Address             | Equals the set RT address.                                                                             |  |  |

| 10     | Message Error          | Set whenever the RT detects a message error.                                                           |  |  |

| 9      | Instrumentation        | Always 0                                                                                               |  |  |

| 8      | Service Request        | Controlled by Control register bit 0.                                                                  |  |  |

| 7:5    | Reserved               | Always 000.                                                                                            |  |  |

| 4      | Broadcast Received     | Set whenever a broadcast message is received.                                                          |  |  |

| 3      | Busy                   | y Controlled by Control register bit 1.                                                                |  |  |

| 2      | Subsystem Flag         | Controlled by Control register bit 2.                                                                  |  |  |

| 1      | Dynamic Bus Acceptance | Always 0. Core1553BRT_APB does not operate as a bus controller.                                        |  |  |

| 0      | Terminal Flag          | Controlled by Control register bit 3. If an "inhibit terminal flag" mode code is in effect, will be 0. |  |  |

## **Transfer Status Words**

At the end of every 1553B bus transfer, a transfer status word is written to the RAM in locations 000–76C for receive operations and F80–FFC for transmit operations. The address used is as follows:

- TSW location, RX commands: '000000' and SA and '00'

- TSW location, TX commands: '011111' and SA and '00'

As an example, the TSW address for a transmit command with subaddress 24 would be '0111111010000' (FD0h). The TSW contains the information in Table 3-2.

| Dit(a) | Bit(s) Name Description |                                                                                                                                                                             |                                                                                        |  |  |  |  |  |

|--------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit(s) | Name                    | Description                                                                                                                                                                 |                                                                                        |  |  |  |  |  |

| 15     | USED                    | Set to 1 at the end of the transmit or receive command.                                                                                                                     |                                                                                        |  |  |  |  |  |

| 14     | OKAY                    | Indicates that                                                                                                                                                              | no errors are detected; i.e., bits 11 to 5 are all 0.                                  |  |  |  |  |  |

| 13     | BUSN                    | Indicates on v                                                                                                                                                              | Indicates on which bus the command was received:                                       |  |  |  |  |  |

|        |                         | 0: BUSA 1: E                                                                                                                                                                | BUSB                                                                                   |  |  |  |  |  |

| 12     | BROADCAST               | Indicates a br                                                                                                                                                              | oadcast command.                                                                       |  |  |  |  |  |

| 11     | LPBKERRB                | Indicates that bus B.                                                                                                                                                       | the loopback logic detected an error in the transmitted data for                       |  |  |  |  |  |

| 10     | LPBKERRA                | Indicates that bus A.                                                                                                                                                       | Indicates that the loopback logic detected an error in the transmitted data for bus A. |  |  |  |  |  |

| 9      | ILLEGAL CMD             | The command was illegal. A request to transmit from either an illegal subaddress or an illegal mode code was received.                                                      |                                                                                        |  |  |  |  |  |

| 8      | MEMIFERR                | Indicates that the DMA memory access failed to complete quickly enough.                                                                                                     |                                                                                        |  |  |  |  |  |

| 7      | MANERR                  | Indicates that a Manchester encoding error was detected in the incoming data.                                                                                               |                                                                                        |  |  |  |  |  |

| 6      | PARERR                  | Indicates that a parity error was detected in the incoming data.                                                                                                            |                                                                                        |  |  |  |  |  |

| 5      | WCNTERR                 | Indicates that an incorrect number of words was received.                                                                                                                   |                                                                                        |  |  |  |  |  |

| 4:0    | COUNT                   | SA1 to SA31 Indicates the number of words received or transmitt<br>subaddress. If WCNTERR is 0, '00000' indicates 32<br>Otherwise, '00000' indicates zero words transferred |                                                                                        |  |  |  |  |  |

|        |                         | SA0 or SA31                                                                                                                                                                 | Indicates which mode code was received or transmitted per the 1553B specification.     |  |  |  |  |  |

#### Table 3-2 • Transfer Status Word

### **RT-to-RT Transfer Support**

The core supports RT-to-RT transfers. If a transmitting core does not start transferring data within the required time, the core will detect this and set the WCNTERR bit in the transfer status word.

## Mode Codes

When the core receives a mode code, it first checks its command validity. If the command is valid, it is processed in accordance with the specification. Otherwise, the message error bit will be set in the 1553B status word. Table 3-3 lists the supported mode codes.

Two mode codes, (1) transmit a vector word and (2) synchronize with data, require external data. The vector word value is set by the VWORD input, and the synchronize with data word is discarded.

| Table 3-3 • Supported | Mode Codes |

|-----------------------|------------|

|-----------------------|------------|

| T/R<br>Bit | Mode<br>Code                                                                                                                                                      | Function and Effect                                                                                                                                                                        | Data<br>Word | Core<br>Supports | Broadcast<br>Allowed |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|----------------------|

| 1          | 00000Dynamic Bus Control0The core does not support bus controller functions, so it will set the<br>Message Error and Dynamic Bus Control bits in the status word. |                                                                                                                                                                                            | No           | No               | No                   |

| 1          | 00001<br>1                                                                                                                                                        | Synchronize<br>The core will assert its SYNCNOW output after the command word<br>has been received.                                                                                        | No           | Yes              | Yes                  |

| 1          | 00010<br>2                                                                                                                                                        | Transmit Status Word<br>The core retransmits the last status word.                                                                                                                         | No           | Yes              | No                   |

| 1          | 00011<br>3                                                                                                                                                        | Initiate Self-Test<br>The core does not support self-test. Since the core supports the<br>transmit BIT word mode code, this command is treated as legal<br>and will not set Message Error. | No           | Yes              | Yes                  |

| 1          | 00100<br>4                                                                                                                                                        | Transmitter Shutdown<br>The core will disable the encoder on the other bus.                                                                                                                | No           | Yes              | Yes                  |

| 1          | 00101<br>5                                                                                                                                                        | Override Shutdown<br>The core will re-enable the encoder on the other bus.                                                                                                                 | No           | Yes              | Yes                  |

| 1          | 00110<br>6                                                                                                                                                        | <ul> <li>Inhibit Terminal Flag</li> <li>The core will mask the TFLAG input, and the Terminal Flag bit in<br/>the status word will be forced to zero.</li> </ul>                            |              | Yes              | Yes                  |

| 1          | 00111<br>7                                                                                                                                                        | Override Inhibit Terminal Flag<br>The core will re-enable the TFLAG input.                                                                                                                 | No           | Yes              | Yes                  |

| 1          | 01000<br>8                                                                                                                                                        | Reset Remote Terminal<br>The core will assert its BUSRESET output after the command word<br>has been received. It will also reset itself.                                                  |              | Yes              | Yes                  |

| 1          | 10000<br>16                                                                                                                                                       | Transmit Vector Word<br>The core will transmit a single data word that contains the value on<br>the VWORD input.                                                                           | Yes          | Yes              | No                   |

| 1          | 10010<br>18                                                                                                                                                       | Transmit Last Command Word<br>The core will transmit a single data word that contains the last<br>command word received.                                                                   | Yes          | Yes              | No                   |

| 1          | 10011<br>19                                                                                                                                                       | Transmit BIT Word<br>The core will transmit a single data word that contains the<br>extended core status information. The value of this word is defined<br>in Table 3-5 on page 17.        |              | Yes              | No                   |

| 0          | 10001<br>17                                                                                                                                                       | Synchronize with Data<br>The core will assert its SYNCNOW output after the data word has<br>been received.                                                                                 | Yes          | Yes              | Yes                  |

#### Table 3-3 • Supported Mode Codes (continued)

| T/R<br>Bit | Mode<br>Code | Function and Effect                                                                                                                                                  | Data<br>Word | Core<br>Supports | Broadcast<br>Allowed |

|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|----------------------|

| 0          | 10100<br>20  | Selected Transmitter Shutdown<br>The core only supports two buses. Hence, this command is illegal.<br>The Message Error bit in the status word will be set.          | Yes          | No               | Yes                  |

| 0          | 10101<br>21  | Override Selected Transmitter Shutdown<br>The core only supports two buses. Hence, this command is illegal.<br>The Message Error bit in the status word will be set. | Yes          | No               | Yes                  |

## **Loopback Tests**

Core1553BRT\_APB performs loopback testing on all of its transmissions. The transmit data is fed back into the receiver, and each transmitted word is compared. If an error is detected, the loopback fail bit is set in the TSW and also in the BIT word.

# **Error Detection**

#### Table 3-4 • Error Detection

| Error  | Condition                                                                                                                                                                                                                                  | Action                                              |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| Comm   | and Word                                                                                                                                                                                                                                   | Command is ignored.                                 |  |  |

| 1.     | Parity or Manchester encoding errors                                                                                                                                                                                                       | No interrupt generated.                             |  |  |

| 2.     | Incorrect SYNC waveform                                                                                                                                                                                                                    |                                                     |  |  |

|        | Codes<br>Illegal mode code or invalid subaddress (from internal or                                                                                                                                                                         | MSGERR in SW is set, and the SW is transmitted.     |  |  |

|        | external legality block)                                                                                                                                                                                                                   | Message Failure interrupt generated.                |  |  |

| Broad  | cast Data Commands                                                                                                                                                                                                                         | Data transfer is aborted.                           |  |  |

| 1.     | TX bit set in command word                                                                                                                                                                                                                 | MSGERR in SW is set, and the SW is not transmitted. |  |  |

|        |                                                                                                                                                                                                                                            | Message Failure interrupt generated.                |  |  |

| Data V | Vord                                                                                                                                                                                                                                       | Data transfer is aborted.                           |  |  |

|        | Parity or Manchester encoding errors<br>Incorrect number of words received                                                                                                                                                                 | MSGERR in SW is set, and the SW is not transmitted. |  |  |

|        | Data words are not continuous/contiguous.                                                                                                                                                                                                  | Message Failure interrupt generated.                |  |  |

|        | Incorrect SYNC waveform                                                                                                                                                                                                                    |                                                     |  |  |

| RT-to- | RT                                                                                                                                                                                                                                         | Data transfer is aborted.                           |  |  |

|        | First command word must be RX.                                                                                                                                                                                                             | MSGERR in SW is set, and the SW is not              |  |  |

| 2.     | Second command word must be TX and non-broadcast.                                                                                                                                                                                          | transmitted.                                        |  |  |

| 3.     | RX RT checks the TX SW and verifies the SYNC pattern, RT address, MSGERR, and BUSY fields.                                                                                                                                                 | Message Failure interrupt generated.                |  |  |

| 4.     | The first data word sync must be received within 57 $\mu s$ of the command word parity bit.                                                                                                                                                |                                                     |  |  |

| Transr | nit Data Error                                                                                                                                                                                                                             | Data transfer is aborted.                           |  |  |

| 1.     | The RT monitors its transmissions on the bus through its decoder and verifies that the correct data is transmitted with                                                                                                                    | MSGERR in SW is set, and the SW is not transmitted. |  |  |

|        | no Manchester or parity errors.                                                                                                                                                                                                            | Message Failure interrupt generated.                |  |  |

| Backe  | nd Failure                                                                                                                                                                                                                                 | Data transfer is aborted.                           |  |  |

| 2.     | The RT makes sure that the backend responds to read and write cycles within the required time.                                                                                                                                             | MSGERR in SW is set, and the SW is not transmitted. |  |  |

|        |                                                                                                                                                                                                                                            | Message Failure interrupt generated.                |  |  |

| BUSY   |                                                                                                                                                                                                                                            | Data transfer is aborted.                           |  |  |

|        | Backend RTBUSY input is active at any point during the                                                                                                                                                                                     | BUSY in SW is set, and the SW is transmitted.       |  |  |

|        | message.                                                                                                                                                                                                                                   | Message Failure interrupt generated.                |  |  |

| Transr | nitter Overrun                                                                                                                                                                                                                             | Core shuts down transmissions on bus.               |  |  |

| 1.     | Transmits for greater than 668 $\mu$ s. The internal state machines prevent this from happening, but the core includes the required timer and functionality. This is implemented separately to the encoder to provide complete protection. |                                                     |  |  |

## **Built-In Test Support**

Core1553BRT\_APB provides a BIT word. This is used to communicate fail information back to the bus controller. The BIT word contains the information in Table 3-5.

#### Table 3-5 • BIT Word

| Bit(s)                                                                         | Function  | Description                                                                                                                                                                                      |  |  |  |

|--------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15 BUSINUSE Indicates on which bus the transmit BIT word command was received: |           | Indicates on which bus the transmit BIT word command was received:                                                                                                                               |  |  |  |

|                                                                                |           | 0: Bus A 1: Bus B                                                                                                                                                                                |  |  |  |

| 14                                                                             | LPBKERRB  | dicates that the loopback logic detected an error on the transmitted data for bus B. This t s cleared by the CLRERR input.                                                                       |  |  |  |

| 13                                                                             | LPBKERRA  | Indicates that the loopback logic detected an error on the transmitted data for bus A. This bit is cleared by the CLRERR input.                                                                  |  |  |  |

| 12                                                                             | SHUTDOWNB | Indicates that bus B is shut down. This occurs after a transmitter shutdown mode code is received or the hardware timer detected that the core transmitted for longer than 668 $\mu$ s on bus B. |  |  |  |

| 11                                                                             | SHUTDOWNA | Indicates that bus A is shut down. This occurs after a transmitter shutdown mode code is received or the hardware timer detected that the core transmitted for longer than 668 $\mu$ s on bus A. |  |  |  |

| 10                                                                             | TFLAGINH  | Terminal flag inhibit setting                                                                                                                                                                    |  |  |  |

| 9                                                                              | WCNTERR   | A word count error has occurred. This bit is cleared by the CLRERR input.                                                                                                                        |  |  |  |

| 8                                                                              | MANERR    | A Manchester encoding error has occurred. This bit is cleared by the CLRERR input.                                                                                                               |  |  |  |

| 7                                                                              | PARERR    | A parity error has occurred. This bit is cleared by the CLRERR input.                                                                                                                            |  |  |  |

| 6                                                                              | RTRTTO    | The transmitting RT did not provide data on RT-to-RT transfer. This bit is cleared by the CLRERR input.                                                                                          |  |  |  |

| 5                                                                              | MEMFAIL   | The backend memory interface failed to complete an access within the required time. This bit is cleared in the CLRERR input.                                                                     |  |  |  |

| 4:0                                                                            | VERSION   | Indicates the core version:<br>'01110': Version 4.3                                                                                                                                              |  |  |  |

## **Command Legalization Interface**

1553B commands can be legalized in three ways with Core1553BRT\_APB. For RTL versions, one of the modules in the source code can be edited to legalize or make illegal command words based on the subaddress, mode code, word count, or broadcast fields of the command word. For Obfuscated and RTL versions, external logic can be used to decode the legal/illegal command words (Figure 3-1). Also, the APB legalization registers can be used to allow software legalization.

#### Figure 3-1 • Command Legalization Logic

The user customization logic block takes in CMDVAL and simply sets CMDOKAY for all legal command words. The CMDVAL encoding is given in Table 3-6. The external logic must implement this function within 3  $\mu$ s.

| Bit(s) | Function                | Description                                                                                                      |  |  |

|--------|-------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| 11     | Broadcast               | '1' indicates broadcast; i.e., the RT address was set to 31 in the 1553B command word.                           |  |  |

| 10     | Transmit or<br>Receive  | TX/RX field from the 1553B command word. '0' indicates receive and '1' transmit.                                 |  |  |

| 9:5    | Subaddress              | Subaddress field from the 1553B command word                                                                     |  |  |

| 4:0    | Word Count<br>Mode Code | Word count field from the 1553B command word. When the subaddress is 0 or 31, this contains the 1553B mode code. |  |  |

#### Table 3-6 • CMDVAL Encoding

# 4 – Interface Descriptions

## Parameters on Core1553BRT\_APB

The parameters given in Table 4-1 are used to configure the core.

| Parameter    | Range             | Description                                                                                                                                                                                                                                                       |  |  |  |

|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FAMILY       | 2 to 26           | Must be set to the required FPGA family:                                                                                                                                                                                                                          |  |  |  |

|              |                   | 11: Axcelerator                                                                                                                                                                                                                                                   |  |  |  |

|              |                   | 12: RTAX-S                                                                                                                                                                                                                                                        |  |  |  |

|              |                   | 14: ProASIC <sup>PLUS</sup>                                                                                                                                                                                                                                       |  |  |  |

|              |                   | 15: ProASIC3                                                                                                                                                                                                                                                      |  |  |  |

|              |                   | 16: ProASIC3E                                                                                                                                                                                                                                                     |  |  |  |

|              |                   | 17: Fusion                                                                                                                                                                                                                                                        |  |  |  |

|              |                   | 18: SmartFusion                                                                                                                                                                                                                                                   |  |  |  |

|              |                   | 19: SmartFusion2                                                                                                                                                                                                                                                  |  |  |  |

|              |                   | 20: IGLOO                                                                                                                                                                                                                                                         |  |  |  |

|              |                   | 21: IGLOOe                                                                                                                                                                                                                                                        |  |  |  |

|              |                   | 24: IGLOO2                                                                                                                                                                                                                                                        |  |  |  |

|              |                   | 25: RTG4                                                                                                                                                                                                                                                          |  |  |  |

|              |                   | 26: PolarFire                                                                                                                                                                                                                                                     |  |  |  |

| CLKSPD       | 12, 16, 20, or 24 | Sets the clock (named CLK) frequency of the 1553B portion of the core to 12, 16, 20, or 24 MHz.                                                                                                                                                                   |  |  |  |

| CLKSYNC      | 0 or 1            | When the CLK and PCLK inputs are asynchronous, this should be 0. When CLK and PCLK are synchronous and driven from the same source, this should be set to 1. Setting this to 1 will remove additional internal clock synchronization logic, lowering tile counts. |  |  |  |

| BCASTEN      | 0 or 1            | This input enables broadcast operation.                                                                                                                                                                                                                           |  |  |  |

|              |                   | When 1, broadcast operations are enabled.                                                                                                                                                                                                                         |  |  |  |

|              |                   | When 0, broadcast messages (i.e., RT address 31) are treated as normal messages. If the RTADDR input is set to 31, the RT will respond to the message.                                                                                                            |  |  |  |

| SA30LOOP     | 0 or 1            | This input alters the backend memory mapping so that subaddress 30 provides automatic loopback.                                                                                                                                                                   |  |  |  |

|              |                   | When 0, the RT does not loop back subaddress 30. Separate memory buffers are used for transmit and receive data buffers.                                                                                                                                          |  |  |  |

|              |                   | When 1, the RT maps the transmit memory buffer for subaddress 30 to the receive memory buffer for subaddress 30; i.e., the upper address line is forced to 0.                                                                                                     |  |  |  |

| INTENBBR     | 0 or 1            | When active (1), the core generates interrupts when both good and bad 1553B messages are received.                                                                                                                                                                |  |  |  |

|              |                   | When inactive (0), the core only generates interrupts when good messages are received.                                                                                                                                                                            |  |  |  |

| TESTTXTOUTEN | 0 or 1            | This enables the TESTTXTOUT input; it is for test use only. This parameter should be set to 0 if it is not required to be able to force transmission overrun for testing the internal transmit timer.                                                             |  |  |  |

#### Table 4-1 • Core1553BRT\_APB Parameters (continued)

| Parameter                                    | Range  | Description                                                                                                                                                                                                                                        |  |  |  |

|----------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ECC                                          | 0 or 1 | When 1, enables the ECC operation in memory. When 0, ECC is not enabled for memory. Option is available for RTG4 family.                                                                                                                           |  |  |  |

| LOCKRT                                       | 0 or 1 | When set to 1, the RT address is set by the RTADDR input and cannot be overridden by the internal registers.                                                                                                                                       |  |  |  |

| INT_POLARITY                                 | 0 or 1 | When 0, the INTERRUPT output is active low; when 1, active high.                                                                                                                                                                                   |  |  |  |

| LEGMODE                                      | 0 to 3 | This controls the RT subaddress and mode code legalization logic:                                                                                                                                                                                  |  |  |  |

|                                              |        | 0: (Internal) Core uses the internal legalization logic inside the 1553B RT core.                                                                                                                                                                  |  |  |  |

|                                              |        | 1: (External) Core uses the external legalization interface, CMDVAL output, and CMDOK input.                                                                                                                                                       |  |  |  |

|                                              |        | 2: (APB registers) Legislation is controlled via software using the Legalization registers, implemented using registers. This option will increase tile counts by approximately 750 tiles.                                                         |  |  |  |

|                                              |        | 3: (APB registers, RAM-based) Legislation is controlled via software using the Legalization registers, implemented using memory.                                                                                                                   |  |  |  |

| INITLASTSW                                   | 0 or 1 | This input controls the last status word.                                                                                                                                                                                                          |  |  |  |

| will respond with an undefined status word s |        | When 0, the first received command is a transmit last status word. The core will respond with an undefined status word since no status word has previously been sent (same function as previous core versions).                                    |  |  |  |

|                                              |        | When 1, the first received command is a transmit last status word. The core will respond with a valid RT address and the all other status bits zero even though no status word was previously sent. It requires PURSTN to be asserted at power-up. |  |  |  |

| EXTERNAL_BIST                                | 0 or 1 | This parameter controls the mode code 19 support.                                                                                                                                                                                                  |  |  |  |

|                                              |        | When 0, the internal BIST value is returned in response to the transmit BIST mode code as shown in Table 4-3 on page 22.                                                                                                                           |  |  |  |

|                                              |        | When 1, the input BITIN [15:0] is returned in response to the transmit BIST mode code.                                                                                                                                                             |  |  |  |

|                                              |        | The default value of EXTERNAL_BIST is 0.                                                                                                                                                                                                           |  |  |  |

## **I/O Signal Descriptions**

Table 4-2 and Table 4-3 on page 22 describe the I/O signals for the bus interface, control, and status.

| Port Name   | Туре | Description                                                                                                                                                                                             |  |

|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RTADDR[4:0] | In   | Sets the RT address; must not be set to '11111'.                                                                                                                                                        |  |

| RTADDRP     | In   | RT address parity input. This input should be set High or Low to achieve odd parity on the RTADDR and RTADDRP inputs. If RTADDR is '00000', the RTADDRP input should be 1.                              |  |

| RTADERR     | Out  | Indicates that the RTADDR and RTADDRP inputs have incorrect parity, or broadcast is enabled, and the RT address is set to 31. When active (High), the RT is disabled and will ignore all 1553B traffic. |  |

| BUSAINEN    | Out  | Active high output that enables for the A receiver                                                                                                                                                      |  |

| BUSAINP     | In   | Positive data input from the A receiver                                                                                                                                                                 |  |

| BUSAINN     | In   | Negative data input from the A receiver                                                                                                                                                                 |  |

| BUSBINEN    | Out  | Active high output that enables for the B receiver                                                                                                                                                      |  |

| BUSBINP     | In   | Positive data input from the bus to the B receiver                                                                                                                                                      |  |

#### Table 4-2 • 1553B Bus Interface

| Port Name Type Description |     |                                                                                |  |  |  |

|----------------------------|-----|--------------------------------------------------------------------------------|--|--|--|

| BUSBINN                    | In  | Negative data input from the bus to the B receiver                             |  |  |  |

| BUSAOUTIN                  | Out | Active high transmitter inhibit for the A transmitter                          |  |  |  |

| BUSAOUTP                   | Out | ositive data output to the bus A transmitter (held High when no transmission)  |  |  |  |

| BUSAOUTN                   | Out | legative data output to the bus A transmitter (held High when no transmission) |  |  |  |

| BUSBOUTIN                  | Out | Active high transmitter inhibits the B transmitter                             |  |  |  |

| BUSBOUTP                   | Out | Positive data output to the bus B transmitter (held High when no transmission) |  |  |  |

| BUSBOUTN                   | Out | Negative data output to the bus B transmitter (held High when no transmission) |  |  |  |

#### Table 4-2 • 1553B Bus Interface (continued)

#### Table 4-3 • Control and Status Signals

| Port Name  | Туре | Description                                                                                                                                                                                                                                    |  |  |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLK        | In   | Master 1553B clock input (12, 16, 20, or 24 MHz)                                                                                                                                                                                               |  |  |

| RSTINn     | In   | Reset input asynchronous (active low)                                                                                                                                                                                                          |  |  |

| BUSY       | Out  | Indicates that the 1553BRT is either receiving or transmitting data or handling a mode command                                                                                                                                                 |  |  |

| SYNCNOW    | Out  | Pulses High for a single clock cycle when the RT receives a synchronize (with or without data mode) command. The pulse occurs just after the 1553B command word (sync with no data) or data word (sync with data mode code) has been received. |  |  |

| BUSRESET   | Out  | Pulses high for a single clock cycle whenever the RT receives a reset mode command. core logic will also automatically reset itself on receipt of this command.                                                                                |  |  |

| FSM_ERROR  | Out  | This output will go High for a single clock cycle if any of the internal state machines enter an illegal state. This output should not go High in normal operation. Should it go High, it is recommended that the core be reset.               |  |  |

| PURSTN     | In   | Asynchronous active low power-up reset.                                                                                                                                                                                                        |  |  |

| BITINEN    | In   | Transmit bit word enable signal. Valid when EXTERNAL_BIST = 1.                                                                                                                                                                                 |  |  |

| BITIN      | In   | 16-bit signal for transmit bit word. Valid when EXTERNAL_BIST = 1.                                                                                                                                                                             |  |  |

| INTERRUPT  | Out  | Core interrupt output signal.                                                                                                                                                                                                                  |  |  |

| SB_CORRECT | Out  | 1-bit error correction flag indicator, enabled when ECC is selected for RTG4.                                                                                                                                                                  |  |  |

| DB_DETECT  | Out  | 2-bit error detection flag indicator, enabled when ECC is selected for RTG4                                                                                                                                                                    |  |  |

Note: All control inputs are synchronous and sampled on the rising edge of the clock. All status outputs are synchronous to the rising edge of the clock.

### **Command Legalization Interface**

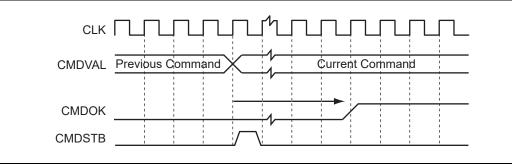

The core checks the validity of all 1553B command words. In RTL and Obfuscated versions of the core, the logic may be implemented externally to the core. The command word is provided, and the logic must generate the command-valid input. The command legalization interface also provides two strobes that are used to latch the command value to enable it to be used for address mapping and interrupt vector extension functions (Table 4-4).

Table 4-4 • Command Legalization Interface

| Port Name    | Туре | Description                                                                                                                                                                                                                                                       |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMDVAL[11:0] | Out  | ActiveCommand                                                                                                                                                                                                                                                     |

|              |      | 11:0: Non-broadcast 1: Broadcast                                                                                                                                                                                                                                  |

|              |      | 10:0: Receive 1: Transmit                                                                                                                                                                                                                                         |

|              |      | 9:5:Subaddress                                                                                                                                                                                                                                                    |

|              |      | 4:0:Word count / mode code                                                                                                                                                                                                                                        |

|              |      | These outputs are valid throughout the complete 1553B message. They can also be used to steer data to particular backend devices. In particular, bit 11 allows non-broadcast and broadcast messages to be differentiated, as required by MIL-STD-1553B, Notice 2. |

| CMDSTB       | Out  | Single-clock-cycle pulse that indicates CMDVAL has changed                                                                                                                                                                                                        |

| CMDOKAY      | In   | Command word is okay (active high). The external logic must set this within 2 $\mu s$ from the CMDVAL output changing.                                                                                                                                            |

### **APB** Interface

The APB interface supports both synchronous operation (to the core clock) and asynchronous operation (Table 4-5).

#### Table 4-5 • APB Signals

| Port Name | Туре       | Description                             |  |

|-----------|------------|-----------------------------------------|--|

| PCLK      | In         | APB clock                               |  |

| PRESETN   | In         | APB reset (active low and asynchronous) |  |

| PSEL      | In         | APB select                              |  |

| PENABLE   | In         | APB enable                              |  |

| PWRITE    | In         | APB write                               |  |

| PADDR     | ln [12:0]  | APB address                             |  |

| PWDATA    | ln [15:0]  | APB write data                          |  |

| PRDATA    | Out [15:0] | APB read data                           |  |

# 5 – Interface Timing

### **Specifications**

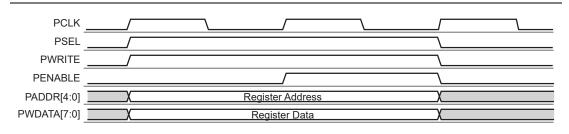

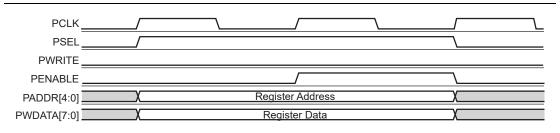

### **APB Interface Timing**

Figure 5-1 and Figure 5-2 depict typical write cycle and read cycle timing relationships relative to the APB system clock, PCLK.

#### Figure 5-1 • Data Write Cycle

#### Figure 5-2 • Data Read Cycle

More detailed descriptions and timing waveforms can be found in the AMBA specification:

http://www.amba.com/products/solutions/AMBA\_Spec.html.

### **Command Word Legality Interface Timing**

Figure 5-3 • Command Word Legality Interface Timing

#### Table 5-1 • Command Word Legality Interface Timing

| Name                 | Description                                         |      |

|----------------------|-----------------------------------------------------|------|

| T <sub>pdCMDOK</sub> | Maximum external command word legality decode delay | 3 µs |

#### **RT Response Times**

RT response time is from the midpoint of the parity bit in the command word to the midpoint of the status word sync (Table 5-2).

#### Table 5-2 • RT Response Times

| Spec                | Description         | At 12 MHz      | At 16 MHz      | At 20 MHz      | At 24 MHz      |

|---------------------|---------------------|----------------|----------------|----------------|----------------|

| T <sub>rtresp</sub> | RT response time    | 4.75 to 7.0 µs |

| T <sub>rtrtto</sub> | RT-to-RT timeout    | 57 µs          | 57 µs          | 57 µs          | 57 µs          |

| T <sub>xxto</sub>   | Transmitter timeout | 704 µs         | 668 µs         | 691 µs         | 693 µs         |

The RT-to-RT timeout is from the first command word parity bit to the expected sync of the first data word.

### **Transceiver Loopback Delays**

Core1553BRT\_APB verifies that all transmitted data words are correctly transmitted. As data is transmitted by the transceiver on the 1553B bus, the data on the bus is monitored by the transceiver and decoded by Core1553BRT\_APB. The core requires that the loopback delay—the time from BUSAOUTP to BUSAINP—be less than the values given in the Table 5-3.

| Clock Speed | Maximum Loopback Delay |

|-------------|------------------------|

| 12 MHz      | 2.3 µs                 |

| 16 MHz      | 2.3 µs                 |

| 20 MHz      | 2.3 µs                 |

| 24 MHz      | 2.3 µs                 |

The loopback delay is a function of the internal FPGA delay, PCB routing delays, and internal transceiver delay as well as transmission effects from the 1553B bus. Additional register stages can be inserted on either the 1553B data input or output within the FPGA, providing the loopback delays in Table 5-3 on page 25 are not violated. This is recommended if additional gating logic is inserted inside the FPGA between the core and transceiver to minimize skew between the differential inputs and outputs.

## **Clock Requirements**

To meet the 1553B transmission bit rate requirements, the Core1553BRT\_APB clock input (CLK) must be 12 MHz, 16 MHz, 20 MHz, or 24 MHz  $\pm$  0.01%.

# 6 – Tool Flows

### Licensing

Core1553BRT\_APB is licensed in three ways. Depending on your license tool flow, functionality may be limited.

#### **Evaluation**

Pre-compiled simulation models are provided, allowing the core to be instantiated with SmartDesign. Simulation can be performed within Libero.

#### Obfuscated

Complete RTL code is provided for the core, allowing the core to be instantiated with SmartDesign. Simulation, Synthesis, and Layout can be performed within Libero. The RTL code for the core is obfuscated<sup>1</sup> and some of the testbench source files are not provided; they are precompiled into the compiled simulation library instead.

### RTL

Complete RTL source code is provided for the core and testbenches.

### **Precompiled Libraries**

Core1553BRT\_APB supports the following precompiled libraries:

- IDE

- Precompiled libraries are built with ModelSim 10.2c for v4.3

- SoC

- Precompiled libraries are built with ModelSim 10.7c for v4.3

1. Obfuscated means the RTL source files have had formatting and comments removed, and all instance and net names have been replaced with random character sequences.

## **SmartDesign**

Core1553BRT\_APB is preinstalled in the SmartDesign IP deployment design environment. The core can be configured using the configuration GUI within SmartDesign, as shown in Figure 6-2. For more information on using SmartDesign to instantiate and generate cores, refer to the *Libero SoC User's Guide*.

Figure 6-1 • Core1553BRT\_APB Full I/O View

| Confi | guration                                   |

|-------|--------------------------------------------|

|       | Clocking                                   |

|       | Clock Speed 16 MHz 🔻                       |

|       | Clocks Synchronous                         |

|       | 1553 Options                               |

|       | Legalization Mode APB Registers            |

|       | Lock RT Address                            |

|       | Broadcast Supported                        |

|       | Sub Address 30 Loopback                    |

|       | Miscellanous Options                       |

|       | Interrupt Polarity High 💌                  |

|       | Enable Bad Block Interrupt                 |

|       | Transmit Overrun Test Enable 📝             |

|       | RT ADDRESS Initialization                  |

|       | EXTERNAL BIST Enable                       |

|       | Testbench:                                 |

|       | License:                                   |

|       | Evaluation Obfuscated Interval Control RTL |

|       |                                            |

Figure 6-2 • Core1553BRT\_APB SmartDesign Configuration

### **Simulation Flows**

The User Testbench for Core1553BRT\_APB is included in all releases.

To run simulations, select the User Testbench flow within SmartDesign and click **Save & Generate** on the Generate pane. The User Testbench is selected through the Core Testbench Configuration GUI.

When SmartDesign generates the Libero project, it will install the user testbench files.

To run the user testbench, set the design root to the **Core1553BRT\_APB instantiation in** the Libero design hierarchy pane and click the **Simulation** icon in the Libero Design Flow window. This will invoke ModelSim<sup>®</sup> and automatically run the simulation.

### **Synthesis in Libero**

After setting the design root appropriately, click the **Synthesis** icon in Libero. The Synthesis window appears, displaying the Synplicity<sup>®</sup> project. Set Synplicity to use the Verilog 2001 standard if Verilog is being used or VHDL 2008 if VHDL. To run Synthesis, select the **Run** icon.

### **Place-and-Route in Libero**

After setting the design root appropriately and run Synthesis, click the **Layout** icon in the Libero to invoke Designer. Core1553BRT\_APB requires no special place-and-route settings.

# 7 – Testbench Operation and Modification

### **User Testbench**

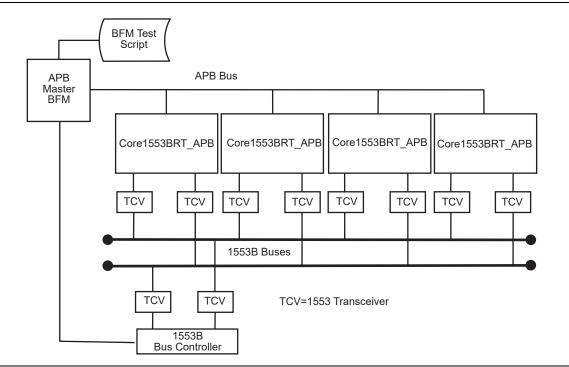

The user testbench (Figure 7-1) is intended to be used as a starting point for the verification of the core when used within the customer application. It consists of an APB master bus functional model (BFM) that creates APB bus cycles, a 1553B bus controller to generate 1553B command sequences, and multiple Core1553BRT\_APB blocks. Having multiple RTs allows RT to RT messages to be tested.

#### Figure 7-1 • User Testbench

The APB master BFM generates APB cycles based on command file core1553brt.bfm. The syntax of these commands is documented in the *DirectCore AMBA BFM User's Guide*.

The 1553B bus controller is connected to AMBAAPB BFM via its external interface. The BFM script can initiate 1553B messages by writing to registers within the bus controller model. The register set is described in the "Bus Controller Model" section on page 31.

The four Core1553BRT\_APB cores are connected via transceiver models to 1553B buses and to the bus controller.

### **Bus Controller Model**