VC-826

Vectron's VC-826 Crystal Oscillator is a quartz stabilized, differential output oscillator, operating off a 2.5 or 3.3 volt power supply in a hermetically sealed 3.2 x 2.5mm ceramic package.

#### **Features**

- Ultra Low Jitter Performance, 3rd OT or Fundamental Crystal Design

- 20MHz -170MHz Output Frequencies

- Low Power

- Excellent Power Supply Rejection Ratio

- · Enable/Disable

- 3.3 or 2.5V operation

- -10/70°C or -40/85°C Operation

- Hermetically Sealed 3.2x2.5mm Ceramic Package

- Product is compliant to RoHS directive and fully compatible with lead free assembly

### **Applications**

- Ethernet, GbE, Synchronous Ethernet

- Fiber Channel

- Enterprise Servers

- Telecom

- Clock source for A/D's, D/A's

- · Driving FPGA's

- Test and Measurement

- PON

- Medical

- COTS

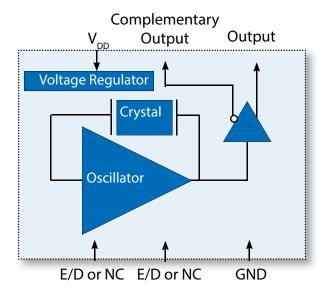

# **Block Diagram**

# **Performance Specifications**

| Table 1. Electrical Performance, LVPECL Option                                       |                                    |                                                  |                                                     |                                                  |        |  |

|--------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|--------|--|

| Parameter                                                                            | Symbol                             | Min                                              | Typical                                             | Maximum                                          | Units  |  |

| Voltage <sup>1</sup> V <sub>DD</sub>                                                 |                                    | 3.135<br>2.375                                   | 3.3<br>2.5                                          | 3.465<br>2.625                                   | V<br>V |  |

| Current <sup>2</sup> , 3.3V<br>2.5V                                                  | I <sub>DD</sub>                    |                                                  |                                                     |                                                  | mA     |  |

|                                                                                      |                                    | Frequency                                        |                                                     |                                                  |        |  |

| Nominal Frequency                                                                    | f <sub>N</sub>                     | 20                                               |                                                     | 170                                              | MHz    |  |

| Stability <sup>3</sup> (Ordering Option)                                             |                                    | ±                                                | 25, ±50 or ±10                                      | 0                                                | ppm    |  |

|                                                                                      |                                    | Outputs                                          |                                                     |                                                  |        |  |

| Output Logic Levels <sup>2</sup><br>Output Logic High<br>Output Logic Low            | V <sub>он</sub><br>V <sub>оь</sub> | V <sub>DD</sub> -1.025<br>V <sub>DD</sub> -1.810 |                                                     | V <sub>DD</sub> -0.880<br>V <sub>DD</sub> -1.620 | V<br>V |  |

| Output Rise and Fall Time <sup>2</sup>                                               | t <sub>R</sub> /t <sub>F</sub>     |                                                  |                                                     | 500                                              | ps     |  |

| Load                                                                                 |                                    | 50                                               | 50 ohms into V <sub>DD</sub> -1.3V                  |                                                  |        |  |

| Duty Cycle⁴                                                                          |                                    | 45                                               |                                                     | 55                                               | %      |  |

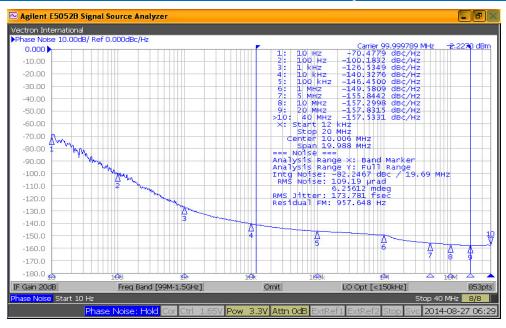

| Phase Noise, 3.3V, 100MHz <sup>5</sup> 10Hz 100Hz 1kHz 10kHz 10kHz 10kHz 20MHz 40MHz |                                    |                                                  | -70<br>-100<br>-126<br>-140<br>-146<br>-149<br>-157 |                                                  | dBc/Hz |  |

| Jitter <sup>5</sup> , 100MHz<br>12kHz -20MHz                                         | фЛ                                 |                                                  | 170                                                 | 200                                              | fs     |  |

|                                                                                      |                                    | ble/Disable                                      | •                                                   |                                                  |        |  |

| Outputs Enabled <sup>6</sup><br>Outputs Disabled                                     | V <sub>IH</sub><br>V <sub>IL</sub> | 0.7*V <sub>DD</sub>                              |                                                     | 0.3*V <sub>DD</sub>                              | V<br>V |  |

| Disable Time                                                                         | t <sub>D</sub>                     |                                                  |                                                     | 200                                              | ns     |  |

| Enable/Disable Leakage Current                                                       |                                    |                                                  |                                                     | ±200                                             | uA     |  |

| Start-Up Time                                                                        | t <sub>su</sub>                    |                                                  |                                                     | 10                                               | ms     |  |

| Operating Temp. (Ordering Option)                                                    | T <sub>OP</sub>                    | -10/70 or -40/85 °C                              |                                                     |                                                  |        |  |

| Package Size                                                                         |                                    |                                                  | 3.2 x 2.5 x 1.05                                    |                                                  | mm     |  |

- 1. The VC-826 power supply pin should be filtered, eg, a 10uf, 0.1uf and 0.01uf capacitor.

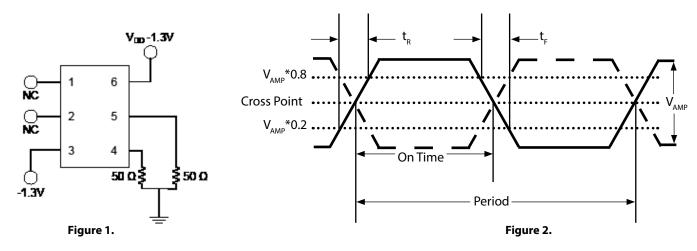

- 2. Figure 1 defines the test circuit and Figure 2 defines these parameters.

- 3. Includes calibration tolerance, operating temperature, supply voltage variations, aging and IR reflow.

- 4. Duty Cycle is defined as the On/Time Period.

- 5. Measured using an Agilent E5052 Signal Source Analyzer at 25 °C.

- 6. Outputs will be Enabled if Enable/Disable is left open.

# **Performance Specifications**

| Table 2. Electrical Performance, LVDS Option                                                      |                                    |                       |                                                     |                     |        |  |  |

|---------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|-----------------------------------------------------|---------------------|--------|--|--|

| Parameter                                                                                         | Symbol                             | Min                   | Typical                                             | Maximum             | Units  |  |  |

| Supply                                                                                            |                                    |                       |                                                     |                     |        |  |  |

| Voltage <sup>1</sup>                                                                              | V <sub>DD</sub>                    | 3.135<br>2.375        | 3.3<br>2.5                                          | 3.465<br>2.625      | V<br>V |  |  |

| Current <sup>2</sup> , 3.3V<br>2.5V                                                               | l <sub>DD</sub>                    |                       |                                                     | 17<br>14            | mA     |  |  |

|                                                                                                   | Frequency                          |                       |                                                     |                     |        |  |  |

| Nominal Frequency                                                                                 | f <sub>N</sub>                     | 20                    |                                                     | 170                 | MHz    |  |  |

| Stability <sup>3</sup> (Ordering Option)                                                          |                                    | ±                     | 25, ±50 or ±10                                      | 0                   | ppm    |  |  |

|                                                                                                   | O                                  | utputs                |                                                     |                     |        |  |  |

| Output Logic Levels <sup>2</sup> Output Logic High Output Logic Low                               | V <sub>OH</sub>                    | 0.9                   | 1.43<br>1.10                                        | 1.6                 | V<br>V |  |  |

| Output Amplitude                                                                                  |                                    | 247                   | 350                                                 | 454                 | mV     |  |  |

| Differential Output Error                                                                         |                                    |                       |                                                     | 50                  | mV     |  |  |

| Offset Voltage                                                                                    |                                    | 1.125                 | 1.25                                                | 1.375               | V      |  |  |

| Offset Voltage Error                                                                              |                                    |                       |                                                     | 50                  | mV     |  |  |

| Output Leakage Current, Outputs Disabled                                                          |                                    |                       |                                                     | 10                  | uA     |  |  |

| Output Rise and Fall Time <sup>3</sup>                                                            | t <sub>R</sub> /t <sub>F</sub>     |                       |                                                     | 500                 | ps     |  |  |

| Load                                                                                              |                                    | 100 ohms differential |                                                     |                     |        |  |  |

| Duty Cycle⁴                                                                                       |                                    | 45                    |                                                     | 55                  | %      |  |  |

| Phase Noise, 3.3V, 100MHz <sup>5</sup> 10Hz 100Hz 1kHz 10kHz 10kHz 100kHz 100kHz 1MHz 20MHz 40MHz |                                    |                       | -73<br>-101<br>-128<br>-140<br>-147<br>-150<br>-156 |                     | dBc/Hz |  |  |

| Jitter⁵, 100MHz<br>12kHz - 20MHz                                                                  | фЈ                                 |                       | 170                                                 | 200                 | fs     |  |  |

|                                                                                                   | 1                                  | e/Disable             |                                                     |                     |        |  |  |

| Outputs Enabled Outputs Disabled                                                                  | V <sub>IH</sub><br>V <sub>IL</sub> | 0.7*V <sub>DD</sub>   |                                                     | 0.3*V <sub>DD</sub> | V<br>V |  |  |

| Disable Time                                                                                      | t <sub>D</sub>                     |                       |                                                     | 200                 | ns     |  |  |

| Enable/Disable Leakage Current                                                                    | I <sub>E/D</sub>                   |                       |                                                     | ±200                | uA     |  |  |

| Start-Up Time                                                                                     | t <sub>su</sub>                    |                       |                                                     | 10                  | ms     |  |  |

| Operating Temp. (Ordering Option)                                                                 | T <sub>OP</sub>                    | -                     | °C                                                  |                     |        |  |  |

| Package Size                                                                                      |                                    | 3.2 x 2.5 x 1.05 mr   |                                                     |                     | mm     |  |  |

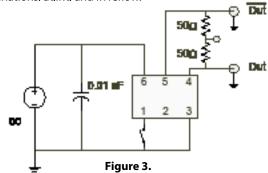

- 1. The VC-826 power supply pin should be filtered, eg, a 10uf, 0.1uf and 0.01uf capacitor.

- 2. Figure 2 defines these parameters and Figure 3 defines the test circuit.

- 3. Includes calibration tolerance, operating temperature, supply voltage variations, aging and IR reflow.

- 4. Duty Cycle is defined as the On/Time Period.

- 5. Measured using an Agilent E5052 Signal Source Analyzer at 25 °C

- 6. Outputs will be Enabled if Enable/Disable is left open.

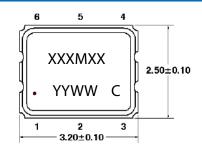

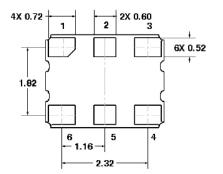

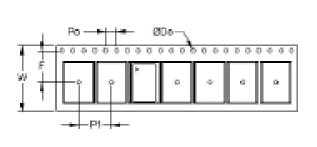

## **Package Outline Drawing**

Dimensions in mm

**Marking Information**

XXXMXX - Frequency (Example: 100M00)

YY - Year of Manufacture

WW - Week of the Year

C - Manufacturing Location

• - Pin 1 Indicator

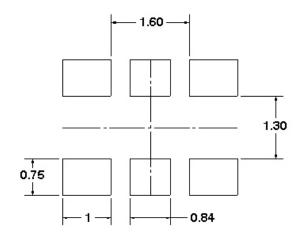

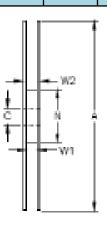

## **Recommended Pad Layout**

# **Pin Diagram**

| Table 3. Pinout |                 |                                 |  |  |  |  |

|-----------------|-----------------|---------------------------------|--|--|--|--|

| Pin #           | Symbol          | Function                        |  |  |  |  |

| 1               | E/D or NC       | Enable/Disable or No Connection |  |  |  |  |

| 2               | E/D or NC       | Enable/Disable or No Connection |  |  |  |  |

| 3               | GND             | Electrical and Lid Ground       |  |  |  |  |

| 4               | $f_{o}$         | Output Frequency                |  |  |  |  |

| 5               | Cf <sub>o</sub> | Complementary Output Frequency  |  |  |  |  |

| 6               | $V_{_{ m DD}}$  | Supply Voltage                  |  |  |  |  |

# **Phase Noise (LV-PECL Output)**

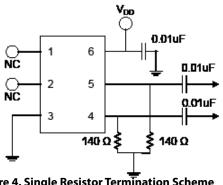

## **LVPECL Application Diagrams**

Figure 4. Single Resistor Termination Scheme

Resistor values are typically 140 ohms for 3.3V operation and 84 ohms for 2.5V operation.

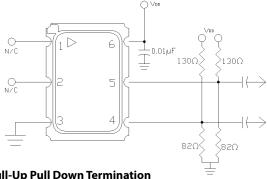

Figure 5. Pull-Up Pull Down Termination

Resistor values shown are typical for 3.3 V operation. For 2.5V operation, the resistor to ground is 62 ohms and the resistor to supply is 250 ohms

The VC-826 incorporates a standard PECL output scheme, which are un-terminated FET drains. There are numerous application notes on terminating and interfacing PECL logic and the two most common methods are a single resistor to ground, Figure 4, or for best 50 ohm matching a pull-up/pull-down scheme as shown in Figure 5 should be used. AC coupling capacitors are optional, depending on the application and the input logic requirements of the next stage.

One of the most important considerations is terminating the Output and Complementary Outputs equally. An unused output should not be left un-terminated, and if it one of the two outputs is left open it will result in excessive jitter on both. PC board layout must take this and 50 ohm impedance matching into account. Load matching and power supply noise are the main contributors to jitter related problems.

#### LVDS Application Diagrams

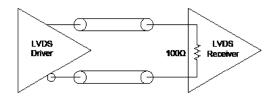

Figure 6. LVDS to LVDS Connection, Internal 100ohm Resistor Some LVDS structures have an internal 100 ohm resistor on the input and do not need additional components. AC blocking capacitors can be used if the DC levels are incompatible.

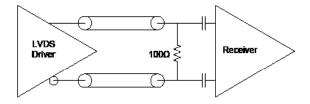

Figure 7. LVDS to LVDS Connection

Some input structures may not have an internal 100 ohm resistor on the input and will need an external 100ohm resistor for impedance matching. Also, the input may have an internal DC bias which may not be compatible with LVDS levels, AC blocking capacitors can be used.

One of the most important considerations is terminating the Output and Complementary Outputs equally. An unused output should not be left un-terminated, and if it one of the two outputs is left open it will result in excessive jitter on both. PC board layout must take this and 50 ohm impedance matching into account. Load matching and power supply noise are the main contributors to jitter related problems.

# **Environmental and IR Compliance**

| Table 4. Environmental Compliance |                              |  |  |  |  |

|-----------------------------------|------------------------------|--|--|--|--|

| Parameter                         | Condition                    |  |  |  |  |

| Mechanical Shock                  | MIL-STD-883 Method 2002      |  |  |  |  |

| Mechanical Vibration              | MIL-STD-883 Method 2007      |  |  |  |  |

| Temperature Cycle                 | MIL-STD-883 Method 1010      |  |  |  |  |

| Solderability                     | MIL-STD-883 Method 2003      |  |  |  |  |

| Fine and Gross Leak               | MIL-STD-883 Method 1014      |  |  |  |  |

| Resistance to Solvents            | MIL-STD-202 Method 215       |  |  |  |  |

| Moisture Sensitivity Level        | MSL1                         |  |  |  |  |

| Contact Pads                      | Gold (0.3-1.0um) over Nickel |  |  |  |  |

| ThetaJC (bottom of case)          | 30 °C/W                      |  |  |  |  |

| Wieght                            | 25 mg                        |  |  |  |  |

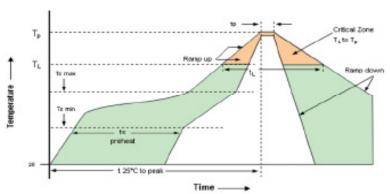

#### **IR Compliance**

#### **Suggested IR Profile**

Devices are built using lead free epoxy and can be subjected to standard lead free IR reflow conditions shown in Table 5. Contact pads are gold over nickel and lower maximum temperatures can also be used, such as 220C.

| Table 5. Reflow Profile  |                      |             |

|--------------------------|----------------------|-------------|

| Parameter                | Symbol               | Value       |

| PreHeat Time             | ts                   | 200 sec Max |

| Ramp Up                  | $R_{UP}$             | 3°C/sec Max |

| Time above 217°C         | tL                   | 150 sec Max |

| Time to Peak Temperature | tAMB-P               | 480 sec Max |

| Time at 260°C            | tP                   | 30 sec Max  |

| Time at 240°C            | tP2                  | 60 sec Max  |

| Ramp down                | $R_{_{\mathrm{DN}}}$ | 6°C/sec Max |

### **Maximum Ratings, Tape & Reel**

#### **Absolute Maximum Ratings and Handling Precautions**

Stresses in excess of the absolute maximum ratings can permanently damage the device. Functional operation is not implied or any other excess of conditions represented in the operational sections of this data sheet. Exposure to absolute maximum ratings for extended periods may adversely affect device reliability. Although ESD protection circuitry has been designed into the VC-826, proper precautions should be taken when handling and mounting, VI employs a Human Body Model and Charged Device Model for ESD susceptibility testing and design evaluation. ESD thresholds are dependent on the circuit parameters used to define the model. Although no industry standard has been adopted for the CDM a standard resistance of 1.5kOhms and capacitance of 100pF is widely used and therefor can be used for comparison purposes.

| Table 6. Maximum Ratings  |                              |      |

|---------------------------|------------------------------|------|

| Parameter                 |                              | Unit |

| Storage Temperature       | -55 to 125                   | °C   |

| Junction Temperature      | 150                          | С    |

| Supply Voltage            | -0.5 to 5.0                  | V    |

| Enable Disable Voltage    | -0.5 to V <sub>DD</sub> +0.5 | V    |

| ESD, Human Body Model     | 1500                         | V    |

| ESD, Charged Device Model | 1500                         | V    |

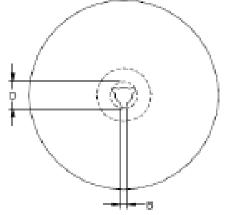

| Table 7.             | Tape and | Reel Info | rmation              |    |     |   |    |    |    |    |    |        |

|----------------------|----------|-----------|----------------------|----|-----|---|----|----|----|----|----|--------|

| Tape Dimensions (mm) |          |           | Reel Dimensions (mm) |    |     |   |    |    |    |    |    |        |

| W                    | F        | Do        | Ро                   | P1 | А   | В | С  | D  | N  | W1 | W2 | #/Reel |

| 8                    | 3.5      | 1.5       | 4                    | 4  | 178 | 2 | 13 | 21 | 60 | 10 | 14 | 1000   |

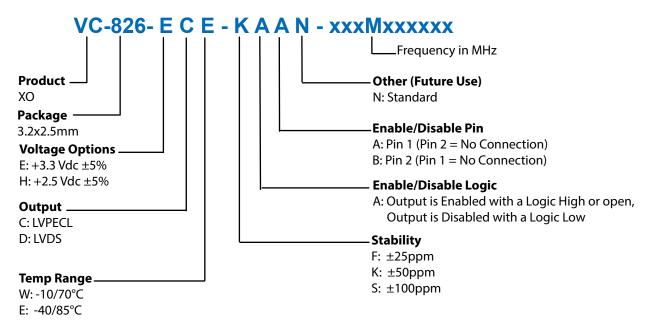

### **Ordering Information**

Example: VC-826-ECE-KAAN-100M000000

\* Add \_SNPBDIP for tin lead solder dip Example: VC-826-ECE-KAAN-100M000000 SNPBDIP

### **Revision History**

| Revision Date | Approved | Description                                                             |

|---------------|----------|-------------------------------------------------------------------------|

| Sep 05, 2014  | VN       | VC-826 Product Initial Release.                                         |

| Dec 12, 2014  | VN       | Added min and max values for LVDS output amplitude.                     |

| Apr 27, 2016  | VN       | Updated LVDS 100MHz noise information and added maximum jitter numbers. |

| Aug 10, 2018  | FB       | Update logo and contact information, add SNPBDIP ordering option        |

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; limiting and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions, Power-over-Ethernet ICs and midspans, as well as custom design capabilities and services. Learn more at www.microsemi.com.

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

Fax: +1 (949) 215-4996 email: sales.support@microsemi.com www.microsemi.com Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or a polications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance sand testing of the products, alone and together with, or installed in, any perd-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products. Buyer shall not rely on any data and performance specifications or provided by Microsemi hereunder is provided by Microsemi hereunder is provided by Microsemi and with all faults, and the entire risk associated with such information in Information provided in Information provided in microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2018 Microsemi, a wholly owned subsidiary of Microsemi Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and senice marks are the property of their respective owners.