# DG0783 Demo Guide PolarFire FPGA: High-Speed Data Transfer in 8b10b Mode Using the LiteFast IP

а 🔨 Міскоснір сотралу

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | Instant         Instant <thinstant< th=""> <th< th=""></th<></thinstant<> |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | ligh-Speed Data Transfer Using the LiteFast IP       2         1       Design Requirements       2         2       Prerequisites       3         3       Demo Design       3         2.3.1       Design Implementation       4         2.3.2       IP Configuration       6         4       Clocking Structure       23         5       Simulating the Design       23         2.5.1       Simulation Flow       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3 | iberoDesign Flow281Synthesize282Place and Route293.2.1Resource Utilization293Verify Timing304Generate FPGA Array Data305Design and Memory Initialization306Generate Bitstream317Run PROGRAM Action32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 | unning the Demo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5 | sing LiteFast For Board-to-Board Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6 | ppendix 1: Programming the Device Using FlashPro Express                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7 | ppendix 2: Running the TCL Script                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8 | ppendix 3: References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **Figures**

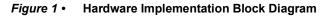

| Figure 1  | Hardware Implementation Block Diagram               | . 4 |

|-----------|-----------------------------------------------------|-----|

| Figure 2  | LiteFast Top-Level Design                           |     |

| Figure 3  | UART_IF_0 Sub-Blocks                                |     |

| Figure 4  | LiteFast_Transmitter_0 Sub-Blocks                   |     |

| Figure 5  | Transceiver_IF_0 Sub-Blocks                         |     |

| Figure 6  | LiteFast_Receiver_0 Sub-Blocks                      |     |

| Figure 7  | PF_CCC_C0_0 Clock Options PLL                       |     |

| Figure 8  | PF_CCC_C0_0 Output Configuration                    | . 8 |

| Figure 9  | COREUART_0 Configurator                             |     |

| Figure 10 | LiteFast_C0_0 Configurator                          |     |

| Figure 11 | COREFIFO_C0_0 Configurator                          |     |

| Figure 12 | PF_TX_PLL Configurator                              |     |

| Figure 13 | PF_XCVR_REF_CLK Configurator                        |     |

| Figure 14 | PF_XCVR_0 Configurator                              |     |

| Figure 15 | PF_CLK_DIV_Configurator                             |     |

| Figure 16 | LiteFast_C1_0 Configurator                          |     |

| Figure 17 | COREFIFO_C3_0 Configurator                          |     |

| Figure 18 | COREFIFO_C4_0 Configurator                          |     |

| Figure 19 | COREFIFO_C1_0 Configurator                          |     |

| Figure 20 | COREFIFO_C2_0 Configurator                          |     |

| Figure 21 | PF_OSC Configurator                                 |     |

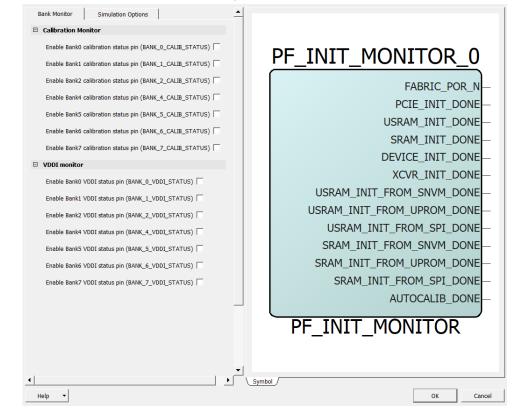

| Figure 22 | PolarFire Initialization Monitor Configurator       |     |

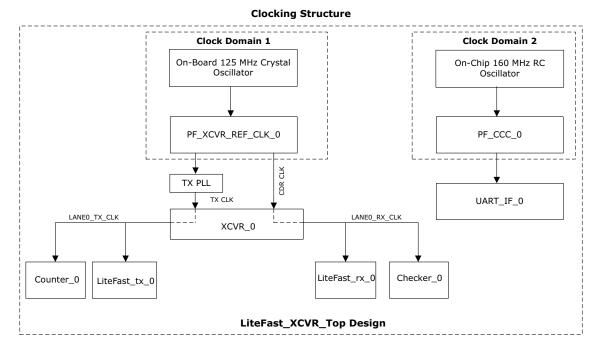

| Figure 23 | Clocking Structure                                  |     |

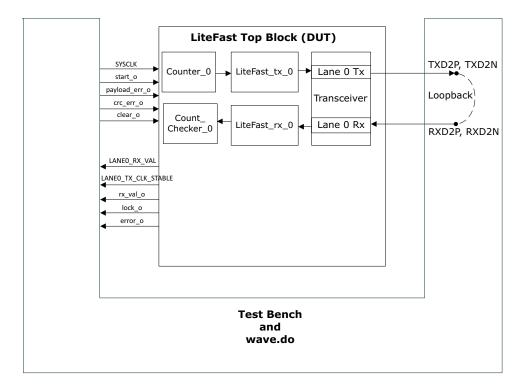

| Figure 24 | Testbench and LiteFast Reference Design Interaction | 24  |

| Figure 25 | Simulating the Design                               |     |

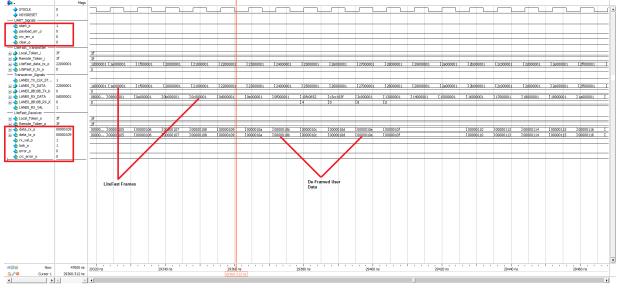

| Figure 26 | Simulation Waveform with No Errors                  |     |

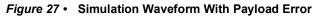

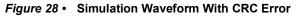

| Figure 27 | Simulation Waveform With Payload Error              |     |

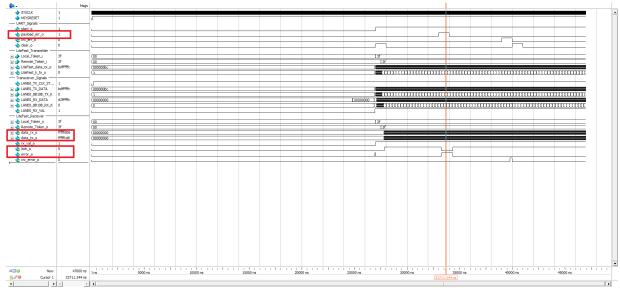

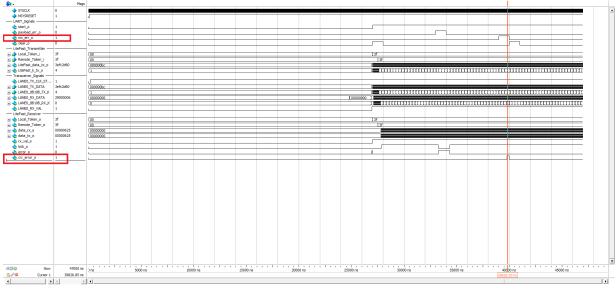

| Figure 28 | Simulation Waveform With CRC Error                  |     |

| Figure 29 | Libero Design Flow Options                          |     |

| Figure 30 | Starting I/O Editor                                 |     |

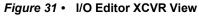

| Figure 31 | I/O Editor XCVR View                                |     |

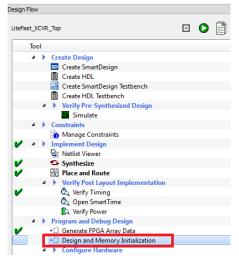

| Figure 32 | Design and Memory Initialization                    |     |

| Figure 33 | Generating XCVR Initialization Client               |     |

| Figure 34 | XCVR Initialization Client Created                  |     |

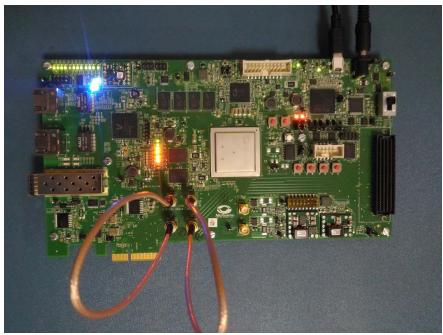

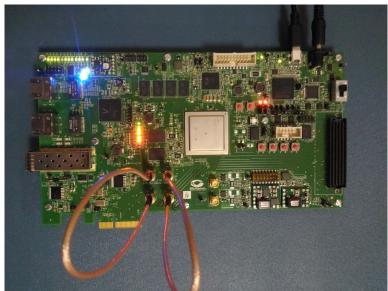

| Figure 35 | Board Setup                                         | 32  |

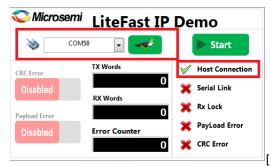

| Figure 36 | Detecting the COM Port and Host Connection Status   |     |

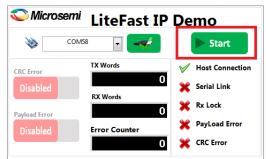

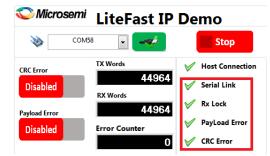

| Figure 37 | Starting the LiteFast Demo                          |     |

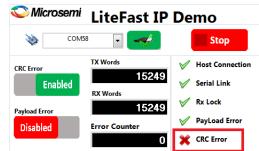

| Figure 38 | Overall Status                                      |     |

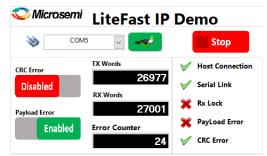

| Figure 39 | Enabling Payload Error                              |     |

| Figure 40 | Checking Payload Error Status                       |     |

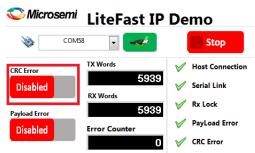

| Figure 41 | Enabling CRC Error                                  |     |

| Figure 42 | Checking CRC Error Status                           |     |

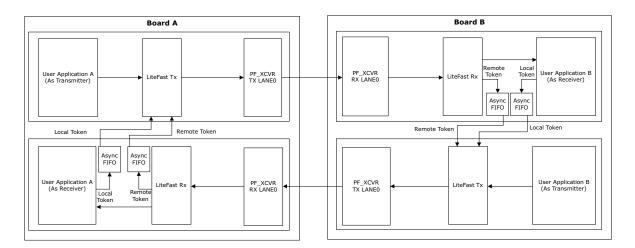

| Figure 43 | Data Transfer Between Board A and B                 |     |

| Figure 44 | Board Setup                                         |     |

| Figure 45 | New project window                                  | 38  |

# **Tables**

| Table 1 | Design Requirements  | 2         |

|---------|----------------------|-----------|

|         | I/O Signals          |           |

| Table 3 | Simulation Signals   | 25        |

| Table 4 | Resource Utilization | <u>29</u> |

|         | Jumper Settings      | 32        |

| Table 6 | Jumper Settings      | 37        |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 3.0

The following is a summary of the changes in revision 3.0 of this document.

- Updated the document for Libero v2021.2.

- Updated Table 1, page 2, Table 2, page 6, and Table 4, page 29.

- The following list of figures are replaced.

- Figure 2, page 4 through Figure 6, page 6

- Figure 7, page 7

- Figure 8, page 8

- Figure 10, page 10

- Figure 12, page 12

- Figure 13, page 13

- Figure 16, page 15

- Figure 17, page 17

- Figure 19, page 19

- Figure 20, page 20

- Figure 45, page 38

- Removed information about PF\_OSC\_0, see PF\_OSC\_0 from this document.

- Added information about PF\_CLK\_DIV\_C0\_0, see PF\_CLK\_DIV\_C0\_0, page 14.

- Updated information about COREFIFO, see COREFIFO, page 16.

- Added Figure 18, page 18.

- Added information about LiteFast\_XCVR\_Top, see LiteFast\_XCVR\_Top, page 21.

- Updated information in chapter Programming the Device Using FlashPro Express, see Appendix 1: Programming the Device Using FlashPro Express, page 37.

- Added Appendix 2: Running the TCL Script, page 39.

# 1.2 Revision 2.0

A note about an inconsistent 125 MHz oscillator that does not supply 125 MHz constantly on few PolarFire Evaluation boards was added, see Table 2, page 6.

# 1.3 Revision 1.0

The first publication of this document.

# 2 High-Speed Data Transfer Using the LiteFast IP

This document describes how to run the LiteFast IP demo on the PolarFire Evaluation Board using the LiteFast GUI application. The GUI application is packaged along with the design files. The reference design is built using the PolarFire high-speed transceiver block in 8b10b mode and the LiteFast IP core. It operates in loopback mode because the TX and RX transceiver lanes are manually looped back on the board. This setup facilitates a standalone demo that does not require another board.

Microsemi's LiteFast IP core implements a serial, point-to-point, and light-weight protocol for high-speed serial communication. LiteFast IP creates a high-speed serial link by connecting to the transceiver block available in Microsemi's PolarFire<sup>®</sup> device. The high-speed transceiver block handles data rates ranging from 250 Mbps to 12.7 Gbps. The transceiver (PF\_XCVR) module integrates several functional blocks to support high-speed serial data transfer within the FPGA.

The LiteFast IP supports data widths of 16, 32, and 64 bits and supports multiple transceiver lanes. In the reference design, the LiteFast IP is configured to 32-bit data width and single lane.

For more information about the LiteFast design implementation, and the necessary blocks and IP cores instantiated in Libero SoC PolarFire, see Demo Design, page 3.

The reference design can be programmed using any of the following options:

- Using the pre-generated .job file: To program the device using the .job file provided along with the reference design, see Appendix 1: Programming the Device Using FlashPro Express, page 37.

- Using Libero SoC PolarFire: To program the device using Libero SoC PolarFire, see Libero Design Flow, page 28.

The reference design can be used on two Microsemi PolarFire boards to implement a full-duplex data transfer application. For more information about the implementation of LiteFast IP for data transfer between two boards, see Using LiteFast For Board-to-Board Data Transfer, page 36.

# 2.1 Design Requirements

The following table lists the hardware and software design requirements for running this demo design.

#### Table 1 • Design Requirements

| Requirement                                                                                                                                                                      | Version       |                                                                          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|--|

| Operating System                                                                                                                                                                 | Windows 7,    | 8.1, or 10                                                               |  |

| Hardware                                                                                                                                                                         |               |                                                                          |  |

| PolarFire Evaluation Kit (MPF300-EVAL-KIT)<br>– PolarFire evaluation board<br>– 12 V/5 A wall-mounted power adapter<br>– USB 2.0 A-male to mini-B cable for UART and programming | Rev B or late | ər                                                                       |  |

| 2 SMA-to-SMA cables (not provided with the kit)                                                                                                                                  |               |                                                                          |  |

| Software                                                                                                                                                                         |               |                                                                          |  |

| FlashPro Express                                                                                                                                                                 | Note:         | Refer to the readme.txt file                                             |  |

| Libero SoC PolarFire                                                                                                                                                             |               | provided in the design files for the<br>software versions used with this |  |

| ModelSim                                                                                                                                                                         |               | reference design.                                                        |  |

| Synplify Pro                                                                                                                                                                     |               |                                                                          |  |

### Table 1 • Design Requirements (continued)

| IP               |  |

|------------------|--|

| LiteFast IP core |  |

| PF XCVR IP core  |  |

| PF_TX_PLL        |  |

| PF_XCVR_REF_CLK  |  |

| CoreUART         |  |

| COREFIFO         |  |

**Note:** Libero SmartDesign and configuration screen shots shown in this guide are for illustration purpose only. Open the Libero design to see the latest updates.

# 2.2 **Prerequisites**

Before you start:

- 1. Download the reference design files from the following location: http://soc.microsemi.com/download/rsc/?f=mpf\_dg0783\_df

- Download and install Libero SoC PolarFire v2021.1 on the host PC from the following location. https://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc-polar-fire#downloads

The latest versions of ModelSim and Synplify Pro are included in the Libero SoC PolarFire installation package.

# 2.3 Demo Design

In the reference design:

- 1. The UART\_IF\_0 block interfaces with the GUI. This block receives RX signals to start and stop the LiteFast demo. This block drives the Counter\_0 and the Count\_Checker\_0 blocks when the start signal is received. When a CRC error or payload error is selected on the GUI, the UART\_IF\_0 block receives that RX signal and passes it to the Counter\_0 block for error injection.

- 2. The Counter\_0 block acts as the application that transfers 32-bit parallel data to the LiteFast\_tx\_0 block.

- 3. The LiteFast\_tx\_0 block is the instantiation of LiteFast IP, configured as transmitter. It receives the 32-bit data, converts the data to LiteFast frames and forwards the data to the PF\_XCVR\_0 block.

- 4. The PF\_XCVR\_0 (transceiver) IP block receives the data on its TX lane, encodes the data in 8b10b format, and serializes the data. The encoded and serialized data is looped back to the RX lane.

- 5. PF\_XCVR\_0 decodes the data in 8b10b format, deserializes the data on its RX lane, and then sends the decoded data to the LiteFast\_rx\_0 block, which is the instantiation of LiteFast IP configured as receiver.

- 6. The Count\_Checker\_0 block generates 32-bit data in sync with Counter\_0, and compares this data with the 32-bit data received from the LiteFast\_rx\_0 block. This block also sends the number of TX words transmitted, status of serial link, CRC error, and payload error to the UART IF 0 block.

- 7. The UART\_IF\_0 block forwards these status and error information on its TX interface to the GUI for display.

The following figure shows the hardware implementation of the high-speed data transfer using the LiteFast IP.

# 2.3.1 Design Implementation

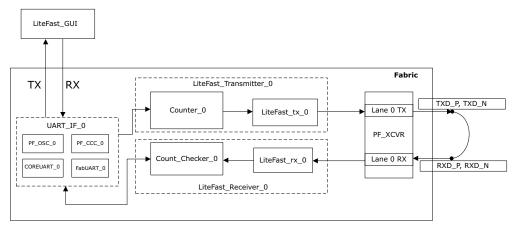

The following figure shows the top-level Libero design of the high-speed data transfer using LiteFast IP.

## Figure 2 • LiteFast Top-Level Design

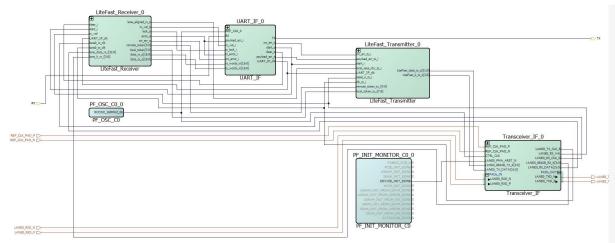

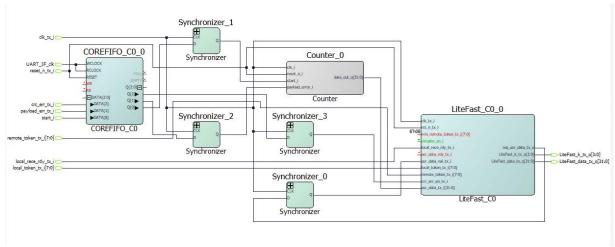

The sub-blocks of UART\_IF\_0 block are shown in the following figure.

## Figure 3 • UART\_IF\_0 Sub-Blocks

The sub-blocks of LiteFast\_Transmitter\_0 block are shown in the following figure.

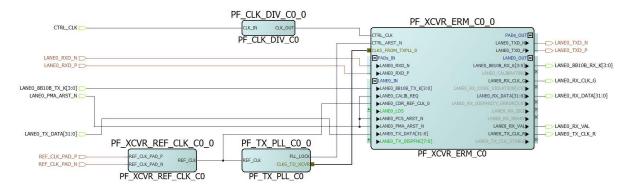

The sub-blocks of Transceiver\_IF\_0 block are shown in the following figure.

Figure 5 • Transceiver\_IF\_0 Sub-Blocks

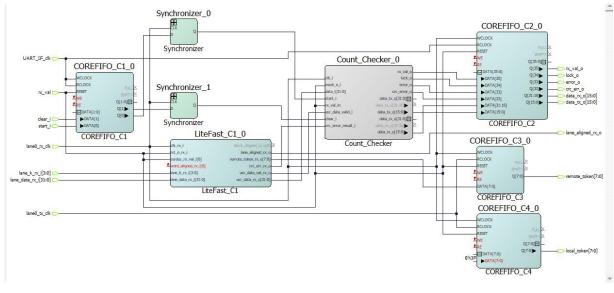

The sub-blocks of LiteFast\_Receiver\_0 block are shown in the following figure.

The following table lists the important I/O signals of the design.

### Table 2 • I/O Signals

| Signal                              | Description                                                                             |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| Input Signals                       |                                                                                         |  |  |

| PADs_IN                             | Transceiver LANE0_RXD_P and LANE0_RXD_N on the board                                    |  |  |

| REF_CLK_PAD_P_0 and REF_CLK_PAD_N_0 | This is the differential reference clock generated from the on-board 125 MHz oscillator |  |  |

| RX                                  | This is the input signal received by the UART interface from the GUI                    |  |  |

| ТХ                                  | This is the output data received by the GUI from the UART interface                     |  |  |

| Output Signals                      |                                                                                         |  |  |

| PADs_OUT                            | LANE0_TXD_P and LANE0_TXD_N looped back to LANE0_RXD_P and LANE0_RXD_N using SMA cables |  |  |

# 2.3.2 IP Configuration

The following sections describe the user-defined blocks, IP blocks, and their configurations for each toplevel block.

# 2.3.2.1 UART\_IF\_0 block

The UART\_IF\_0 block contains the PF\_CCC, CoreUART, Reset\_Synchronizer\_0, and FabUART modules. These modules are described in the following sections.

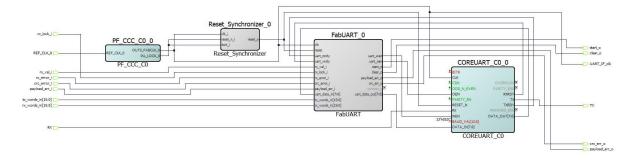

# 2.3.2.1.1 PF\_CCC\_C0\_0

The PF\_CCC\_C0\_0 block provides 125 MHz output fabric clock to COREUART\_C0\_0 and FabUART\_0 modules, which are fabric blocks. The following figures shows the input and output configurations of PF\_CCC\_C0\_0.

| Figure 7 • | PF | CCC | C0 0 | Clock | Options | PLL |

|------------|----|-----|------|-------|---------|-----|

|------------|----|-----|------|-------|---------|-----|

| Configuration PLL-Single                                              |                                                    |

|-----------------------------------------------------------------------|----------------------------------------------------|

| Clock Options PLL   Output Clocks                                     |                                                    |

| Input Frequency                                                       |                                                    |

| Input Frequency 160 MHz Backup Clock Bandwidth Medium-Low = 0.519 MHz |                                                    |

| Delay Line                                                            |                                                    |

| Enable Delay Line                                                     | PF_CCC_0                                           |

| Reference Clock Delay     Feedback Clock Delay Delay Steps: 1         | -REF_CLK_0 OUT0_FABCLK_0-<br>PLL_LOCK_0-<br>PF_CCC |

| Power / Jitter                                                        |                                                    |

| Maximize VCO for Lowest Jitter VCO = 5000 MHz                         |                                                    |

| C Minimize VCO for Lowest Power                                       |                                                    |

| E Feedback Mode                                                       |                                                    |

| Post-VCO 💌                                                            |                                                    |

| Features                                                              |                                                    |

| Integer Mode                                                          | ( )                                                |

|                                                                       | Symbol                                             |

| Log                                                                   |                                                    |

| 🗏 Messages 😵 Errors 🗼 Warnings 🕕 Info                                 |                                                    |

|                                                                       |                                                    |

| Help 🔻                                                                | OK Cancel                                          |

Figure 8 • PF\_CCC\_C0\_0 Output Configuration

| Configuration       PLL-Single         Clock Options       PLL         Output Clocks       Clock Options         For best results, put the highest frequency first.       Clock Options                                                       |                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Output Clock 0                                                                                                                                                                                                                                |                                          |

| ✓ Enabled                                                                                                                                                                                                                                     |                                          |

| Requested Frequency     125     MHz     C     Actual Lower     125     MHz     C     Actual Higher     125     MHz       Requested Phase     0     Degrees     C     Actual Lower     0     Degrees     C     Actual Higher     0     Degrees | PF_CCC_0                                 |

| □ Dynamic Phase Shifting       □ Expose Enable Port         □ Global Clock       □ Global Clock (Gated)       □ HS I/O Clock       □ Dedicated Clock                                                                                          | -REF_CLK_0 OUT0_FABCLK_0-<br>PLL_LOCK_0- |

| <ul> <li>Output Clock 1</li> </ul>                                                                                                                                                                                                            | PF_CCC                                   |

| Enabled                                                                                                                                                                                                                                       |                                          |

| Requested Frequency     160     MHz     C     Actual Lower     MHz     C     Actual Higher     MHz       Requested Phase     0     Degrees     C     Actual Lower     Degrees     C     Actual Higher     Degrees                             |                                          |

| ✓       Dynamic Phase Shifting       ✓       Expose Enable Port         ✓       Global Clock       ✓       Global Clock (Gated)       ✓       HS I/O Clock       ✓       Dedicated Clock                                                      |                                          |

| Output Clock 2                                                                                                                                                                                                                                | Symbol /                                 |

|                                                                                                                                                                                                                                               |                                          |

| ] Messages 🔇 Errors 🔺 Warnings 🕕 Info                                                                                                                                                                                                         |                                          |

|                                                                                                                                                                                                                                               |                                          |

|                                                                                                                                                                                                                                               |                                          |

## 2.3.2.1.2 COREUART\_C0\_0

User inputs from the GUI are received by the COREUART module, which converts this serial input data to parallel data and forwards the data to the FabUART module for further processing. Both COREUART\_C0\_0 and FabUART\_0 modules run at the same frequency. Hence, the TX and RX FIFO options are disabled in the COREUART\_C0\_0 configurator as shown in Figure 9, page 9. For more information about CoreUART, see *HB0095: CoreUART Handbook*.

For more information about PF\_CCC, see UG0684: PolarFire FPGA Clocking Resources User Guide.

## 2.3.2.1.3 Reset\_Synchronizer\_0

The Reset\_Synchronizer\_0 block is a two stage synchronizer, which synchronizes the PLL\_LOCK\_0 signal.

### *Figure* 9 • COREUART\_0 Configurator

| Configuration           |                   |

|-------------------------|-------------------|

| Core Configuration      |                   |

| TX FIFO:                | Disable TX FIFO 🔻 |

| RX FIFO:                | Disable RX FIFO 🔻 |

| RX Legacy Mode:         | Disabled          |

| FIFO Implementation:    | In RAM 👻          |

| Baud Value Precision    |                   |

| Enabled Extra Precision | n: 🔽              |

| Testbench: User 💌       |                   |

| License: 🔘 Obfuscated   | RTL               |

## 2.3.2.1.4 FabUART\_0

The FabUART module drives the Counter\_0 and Count\_Checker\_0 modules, and receives the data and error information from the Count\_Checker\_0 module. The FabUART module passes this data to the CoreUART, which converts this parallel data to serial and forwards the data to the GUI. It is a user-defined module.

## 2.3.2.2 LiteFast\_Transmitter\_0

This block contains the Counter\_0, LiteFast\_tx\_0, Synchronizer\_0, and the COREFIFO\_0 modules. These modules are described in the following sections.

### 2.3.2.2.1 Counter\_0

The counter\_0 module implements a 32-bit counter that transmits incremental data to the LiteFast\_tx\_0 module at each clock cycle.

## 2.3.2.2.2 LiteFast\_C0\_0

LiteFast\_C0\_0 is the instantiation of the LiteFast IP configured as transmitter. This IP core receives the incremental data from Counter\_0 and converts that data to LiteFast frames. These frames are sent to the Transceiver\_IF\_0 block over a single lane. The following figure shows this data width and lane configuration.

### Figure 10 • LiteFast\_C0\_0 Configurator

| Configuration  | ו                |        |

|----------------|------------------|--------|

| g_DATA_WID:    | 32               | _      |

| g_LANE_NUM:    | 1                | _      |

| LiteFast_Mode: | Transmitter Only | •      |

| License        | Obfuscated       |        |

|                |                  |        |

|                |                  |        |

|                |                  |        |

|                |                  |        |

|                |                  |        |

| Help 🔻         | ОК               | Cancel |

# 2.3.2.2.3 Synchronizer

The Synchronizer block is a two stage synchronizer, which synchronizes the clock domain crossing signals.

# 2.3.2.2.4 COREFIFO\_C0\_0

The COREFIFO\_C0\_0 IP is used for clock domain crossing of the crc\_err\_en\_tx\_i, payload\_error\_i, and start\_i signals from UART\_IF\_CLK domain to LANE0\_TX\_CLK. The following figure shows the COREFIFO\_C0\_0 configuration. For more information about CoreFIFO, see *HB0379: CoreFIFO Handbook*.

| Configuration                                                                        |

|--------------------------------------------------------------------------------------|

| FIFO Operation                                                                       |

| Controller Type : With 64x12 uSRAM V Clocks : Dual Clock V                           |

| Memory Pipeline : Pipelined $\checkmark$ Synchronizer Stages : 2 $\checkmark$        |

| ECC: Disabled                                                                        |

| Reset Type : Asynchronous Reset $\checkmark$ Optimized for : High Speed $\checkmark$ |

| Prefetch (Single Clock Cycle Read)  FWFT (First-Word Fall-Through)                   |

| Clock, Enable and Reset                                                              |

| Read Enable : Active High V Write Enable : Active High V                             |

| Read Port                                                                            |

| Width : 3 Depth : 32                                                                 |

| Write Port                                                                           |

| Width : 3 Depth : 32                                                                 |

| Data Handshake                                                                       |

| Read Data Valid Write Acknowledgement                                                |

| Disable Reads when FIFO is Empty Disable Writes when FIFO is Full                    |

| Flags                                                                                |

| Almost EMPTY Almost EMPTY Threshold : 4                                              |

| Almost FULL Almost FULL Threshold : 60                                               |

| Underflow Overflow                                                                   |

| Write Count Read Count                                                               |

|                                                                                      |

| Testbench : User                                                                     |

#### *Figure 11* • COREFIFO\_C0\_0 Configurator

License : RTL

# 2.3.2.3 Transceiver\_IF\_0

This block contains the PF\_TX\_PLL\_C0\_0, PF\_XCVR\_REF\_CLK\_C0\_0, and the PF\_XCVR\_C0\_0 modules. These modules are described in the following sections.

## 2.3.2.3.1 PF\_TX\_PLL\_C0\_0

The PF\_TX\_PLL IP block provides the reference clock to the transceiver lane. This block is configured as shown in the following figure.

### Figure 12 • PF\_TX\_PLL Configurator

|                               | Transmit PLL                                                                   |

|-------------------------------|--------------------------------------------------------------------------------|

| 10GBASE-R                     |                                                                                |

| 10GBASE-KR                    | Clock Inputs/Outputs                                                           |

| SGMI                          |                                                                                |

| QSGMII                        | Configure Tx PLL in Integer Mode                                               |

| CPRI Rate 1                   | Desired Output Bit Clock 12700.000 Mbps Desired Output Bit Clock Frequency 635 |

| CPRI Rate 2                   |                                                                                |

| CPRI Rate 3                   | Reference Clock Frequency 125 MHz                                              |

| CPRI Rate 4                   | Reference Clock Source Dedicated                                               |

| CPRI Rate 5                   | Bandwidth Low V                                                                |

| CPRI Rate 6                   |                                                                                |

| CPRI Rate 7                   | Clock Options                                                                  |

| CPRI Rate 8                   | Cock options     PF_TX_PLL_0                                                   |

| SDI 3G                        | C Normal Mode                                                                  |

| - SDI HD                      | PEE CIV PLL_LOCK-                                                              |

| - SDI SD                      | CLKS_TO_XCVR                                                                   |

| Interlaken 6.25G              | Jitter Cleaning Mode 10G SyncE 32Bit PF_TX_PLL::PF_TX_PLL_C                    |

| Interlaken 10G                | Enable Jitter Attenuation PLL at power-up                                      |

| XAUI                          | Jitter Attenuation PLL Reference Clock Frequency 125                           |

| Apply New preset              | Jitter Attenuation PLL Reference Clock Source Dedicated                        |

|                               | Enable Dynamic Reconfiguration Interface (DRI)                                 |

|                               | Symbol /                                                                       |

| Log                           |                                                                                |

|                               |                                                                                |

| 🔳 Messages 🥸 Errors 🗼 Warning | s 🕕 Info                                                                       |

|                               |                                                                                |

|                               |                                                                                |

|                               |                                                                                |

|                               |                                                                                |

|                               |                                                                                |

| Help 👻                        | OK Cance                                                                       |

# 2.3.2.3.2 PF\_XCVR\_REF\_CLK\_C0\_0

The PF\_XCVR\_REF\_CLK IP block provides the reference clock to PF\_TX\_PLL and CDR PLL. This block is configured as shown in the following figure.

### Figure 13 • PF\_XCVR\_REF\_CLK Configurator

|  | Enable fabric clock output | _XCVR_REF_CLK_0<br>REF_CLK_PAD_P<br>REF_CLK_PAD_N<br>PF_XCVR_REF_CLK |

|--|----------------------------|----------------------------------------------------------------------|

|--|----------------------------|----------------------------------------------------------------------|

# 2.3.2.3.3 PF\_XCVR\_C0\_0

The PolarFire high-speed transceiver (PF XCVR) is a hard IP block that supports high-speed data rates ranging from 250 Mbps to 12.7 Gbps. In this demo, the transceiver block (PF\_XCVR) is configured in 8b10b mode on lane 0 with a CDR reference clock of 125 MHz to support 12.7 Gbps data rate.

PolarFire Transmit PLL (PF\_TX\_PLL) is used to send the reference clock feed to the transceiver. The dedicated reference clock (PF\_XCVR\_REF\_CLK) drives the PF\_TX\_PLL to generate the desired output clock for the 12.7 Gbps data rate. For more information about the PolarFire Transceiver, see *UG0677: PolarFire FPGA Transceiver User Guide*.

The following figure shows the PF\_XCVR\_C0\_0 configuration.

*Figure 14* • **PF\_XCVR\_0** Configurator

| <u></u>                    |                               |                         |          |                                 |                                                                                                                | 1        | - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-------------------------------|-------------------------|----------|---------------------------------|----------------------------------------------------------------------------------------------------------------|----------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10GBASE-R                  | General                       |                         |          |                                 |                                                                                                                |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10GBASE-KR                 | Transceiver mode              | Tx and Rx (Full Duplex) | -        | Enhanced receiver managem       | ent                                                                                                            |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SGMI                       | Number of lanes               | 1                       |          |                                 | On-Demand and First Lock                                                                                       |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| QSGMII                     |                               |                         |          |                                 |                                                                                                                |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CPRI Rate 1                | PMA Settings                  |                         |          |                                 |                                                                                                                |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CPRI Rate 2                | TX data rate                  | 12700                   | Mhos o   | BX data rate                    | 12700 Mbps                                                                                                     |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CPRI Rate 3                |                               | 12700                   | Mbps 🚯   |                                 | And and a second se | <b>n</b> |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CPRI Rate 4                | TX clock division factor      | 1                       | <u> </u> | RX CDR lock mode                | Lock to data                                                                                                   |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CPRI Rate 5<br>CPRI Rate 6 | TX PLL base data rate         | 12700.000               | Mbps     | RX CDR reference clock source   | Dedicated                                                                                                      |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| - CPRI Rate 5              | TX PLL bit clock frequency    | 6350.000                | MHz      | RX CDR reference clock frequent | ry 125.00 • MHz                                                                                                |          |   | PF_XCVR_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| - CPRI Rate 7              |                               |                         |          | RX JA clock frequency           | 317.5 MHz                                                                                                      |          |   | -CTR_CAR MARCATO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |