Power Matters.<sup>™</sup>

#### Post-Integration Reprogramming of RTG4 FPGAs Using DirectC and RISC-V

Ken O'Neill Director of Marketing, Space and Aviation

## Introduction: Why Reprogram after Integration?

- Multiple reasons why it may be necessary to reprogram after integration

- Post-launch bug fix

- Processing algo enhancement/fine tuning after satellite deployment

- Adapt flight hardware to previously unknown target/mission/item of interest

- Repurposing of functioning flight hardware after mission completion

- RTG4 supports reprogramming after integration, during space flight

- Constraints to be aware of:

- Exceeding 200 programming cycles will result in reduced program retention time

- Reprogramming circuits become inoperative after greater than 50 krad of total dose

- Heavy ion radiation can cause non-destructive interruptions to programming (less than 1% probability in GEO)

## How to Accomplish Reprogramming

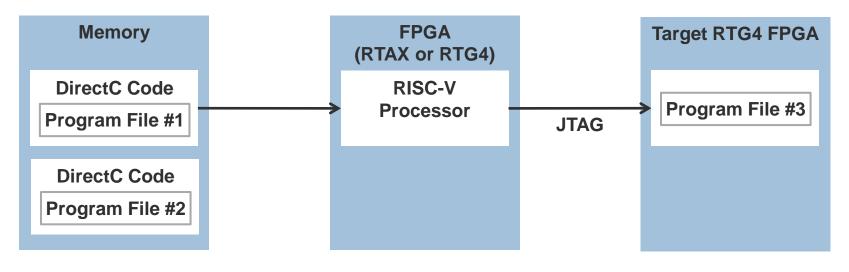

- A controller is required to retrieve the new programming code from memory and to upload the new code into the target RTG4 FPGA

- This requires a microprocessor . . .

- Can use a discrete, standalone radiation-tolerant microprocessor

- Can use a soft-IP microprocessor in another FPGA

- In our example, we use a RISC-V processor running on another RTG4 FPGA

- ... and also requires instruction code for the processor to execute

- In our example, we use Microsemi DirectC embedded in-system programming code

## **Overview of In-System Programming with DirectC**

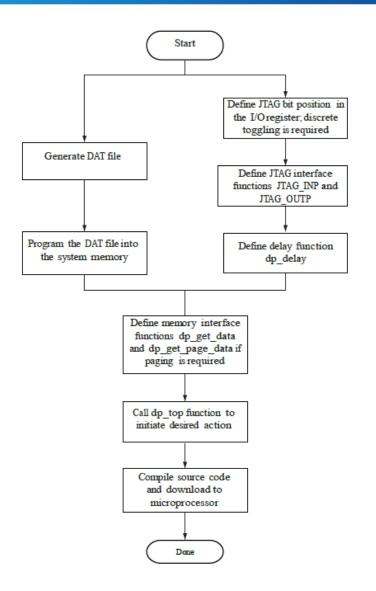

- DirectC is a set of 'C' source code files that support embedded in-system programming for a variety of Microsemi FPGAs, including RTG4

- Must be modified to meet needs of each specific implementation and compiled with an API

- Target FPGA design must be compiled and stored as .dat file

- Microsemi Libero software is used to create the .dat file

- RTG4 .dat files are on the order of 50 Mbits

- RTG4 requires programming through the JTAG interface

- RTG4 requires activation of the JTAG interface in order to disable system controller suspend mode

- Refer to the Microsemi DirectC User Guide for details <u>https://www.microsemi.com/products/fpga-soc/design-</u> <u>resources/programming/directc#documents</u>

4

#### **RISC-V Microprocessor Overview**

- A new free and open ISA developed at UC Berkeley, initiated in 2010 through a permissible BSD license

- RISC-V is not an open-source processor, but open-source implementations will exist

- ISA designed for

- Simplicity

- Longevity (freeze base instructions, your code runs forever)

- Innovation (plenty of opcode space for custom instructions)

- RISC-V Foundation

- To direct future development, to foster adoption, and to protect the ISA

#### **Example RISC-V Implementation in RTG4**

- Flexible, open ISA permits many variations of features and performance

- Open ISA permits inspectable RTL source code

- On-shore US-based RTL developers support RISC-V on RTG4

- Initial RISC-V implementation in RTG4

- Occupies less than 10% of available resources

- Operates at up to 70 MHz over mil temp range

| Core   | тсм | LE's | Pipe | DMIPs | Cache | Mul/Div | SPFP | DPFP | Available |

|--------|-----|------|------|-------|-------|---------|------|------|-----------|

| RV32IM | No  | 12K  | 5    | 1.1   | Yes   | Yes     | No   | No   | Now       |

| Others | TBD |      |      |       |       |         |      |      |           |

#### **Reprogramming Reference Design**

- Reference design for RTG4 reprogramming using two RTG4 Dev Kits

- RTG4 Dev Kit #1 runs a design with embedded RISC-V with DirectC code

- RTG4 Dev Kit #2 hosts the RTG4 being reprogrammed

- Obtain reference design Libero project from Microsemi ken.oneill@microsemi.com minh.u.nguyen@microsemi.com

RTG4 Dev Kit #1 hosts RTG4 with embedded RISC-V processor IP, running DirectC

RTG4 Dev Kit #2 hosts RTG4 to be reprogrammed by RTG4 Dev Kit #2

7

# **Thank You**

#### **Microsemi Corporate Headquarters**

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com www.microsemi.com

©2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.