# PolarFire Evaluation Kit Quickstart Card

#### Kit Contents—MPF300-EVAL-KIT-ES

| Quantity | Description                                                       |  |

|----------|-------------------------------------------------------------------|--|

| 1        | PolarFire FPGA with 300K LE MPF300TS-1FCG1152EES Evaluation Board |  |

| 1        | USB 2.0 A to Mini-B cable                                         |  |

| 1        | 12 V, 5 A AC power adapter and cord                               |  |

| 1        | 1 Year Libero Gold Software License (\$995 value)                 |  |

| 1        | Quickstart card                                                   |  |

#### Overview

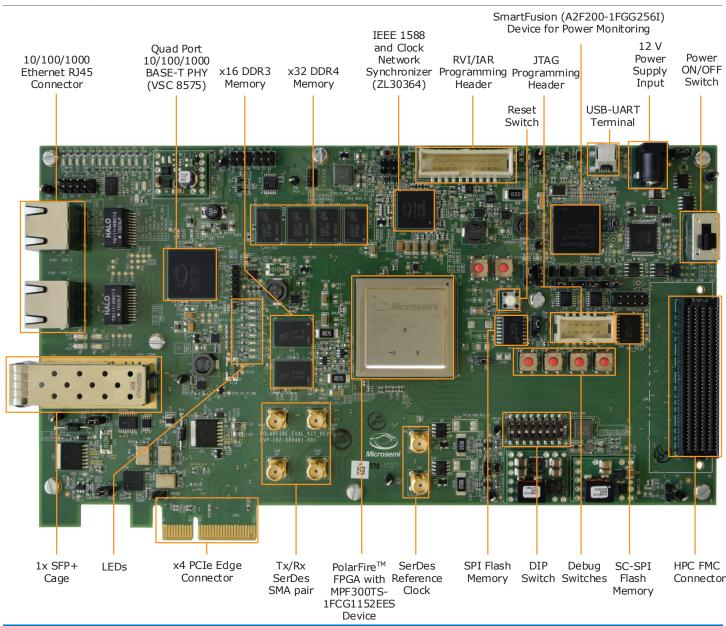

Microsemi's PolarFire Evaluation Kit is an ideal platform for evaluating the lowest power, cost-optimized, non-volatile PolarFire FPGAs. This kit has a full-featured 300K LE PolarFire FPGA, which integrates reliable non-volatile FPGA fabric, 12.7 Gbps transceivers, 1.6 Gbps I/Os, best-in-class-performance, hardened security IP, and crypto processors. The silicon features power optimization with the lowest static power for 28 nm non-volatile FPGAs, its low power mode; Flash\*Freeze yields best-in-class standby power and it has integrated DDR PHY, PCIe endpoint/root port, crypto processor hard IPs.

This kit enables easy design of applications that can include:

- Industrial automation

- Wireline access networks and cellular infrastructure

- Power measurement

- Security applications

- Hardware Features

- 300K LE PolarFire FPGA in an FCG1152 package (MPF300TS-1FCG1152EES)

- 1x SFP+ cage

- IEEE 1588 PLL

- SMA connectors for testing of full-duplex 12.7 Gbps SerDes channel

- 4 GB DDR4 x32 and 2 GB DDR3 x16

- PCI Express (x4) edge connector

- 2x RJ45 for 10/100/1000 Ethernet using SGMII on GPIO

- FMC expansion

- IEEE 1588 applications

- High speed I/O applications

- Universal Serial Bus (USB) applications

- Imaging and video applications

- Dual 10/100/1000BASE-T PHY (VSC8575)

- SATA interface

- Power management unit for 1 V or 1.05 V PolarFire FPGA core voltage

- USB to UART Interface

- Embedded programming and debugging using SPI and JTAG

- On-board power monitoring

- 2x 1 GB SPI flash memory

## **Programming**

Microsemi's PolarFire Evaluation Kit provides feasible programmability using an on-board embedded FlashPro5 programmer.

The board can also be programmed with standalone FlashPro4/5 hardware.

IAP programming and debug support is also provided on the board.

See Documentation Resources for more information about programming procedures.

#### **Jumper Settings**

The PolarFire Evaluation Kit comes with the following default jumper settings.

| Jumper                      | Pin | Factory Default |  |

|-----------------------------|-----|-----------------|--|

| J18, J19, J20, J21, and J22 | 2-3 | Shorted         |  |

| J17                         | 1-2 | Open            |  |

See Documentation Resources for full details about jumper settings.

#### Running the Demo

The PolarFire Evaluation Board comes with a preprogrammed JESD204B standalone demo design. The demo operates in loopback mode to establish a standalone JESD interface demo that does not require analog-to-digital (ADC) or digital-to-analog converters (DAC) by looping data between the TX and RX IP cores for JESD204B.

In order to run the demo, install the JESD204B\_GUI application and set up the board as outlined in the following steps. For detailed instructions, refer to <u>DG0755: PolarFire FPGA JESD204B Standalone</u> Interface Demo Guide.

- 1. Connect the power supply cable to the J9 connector on the board.

- 2. Connect the USB cable from the host PC to the J5 connector (FTDI port) on the board.

- 3. Power on the board using the SW3 slide switch.

# Software and Licensing

The Libero® SoC PolarFire Design Suite is required for designing with the PolarFire Evaluation Kit. Libero® SoC PolarFire Design Suite offers high productivity with its comprehensive, easy-to-learn, easy-to-adopt development tools for designing with Microsemi's low power Flash FPGAs and SoC. The suite integrates industry standard Synopsys Synplify Pro® synthesis and Mentor Graphics ModelSim® simulation with best-in-class constraints management and debug capabilities.

Download the latest Libero SoC PolarFire release www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc-polarfire#downloads

A Gold license is required to program the PolarFire Evaluation Kit. A Software ID letter enclosed with the kit contains Software ID and instructions on how to generate a Libero Gold license. For more information, see www.microsemi.com/products/fpga-soc/design-resources/dev-kits/polarfire/polarfire-eval-kit#licensing

#### **Documentation Resources**

For more information about the PolarFire Evaluation Kit, including schematics and user's guides, see the documentation at https://www.microsemi.com/products/fpga-soc/design-resources/dev-kits/polarfire-eval-kit#documentation.

## Support

Technical support is available online at www.microsemi.com/soc/support and by email at soc\_tech@microsemi.com

Microsemi sales offices, including representatives and distributors are located worldwide. To find your local representative, go to www.microsemi.com/salescontacts

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2015–2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold nereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi, it is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.