# UG0776 User Guide PolarFire FPGA Design Constraints

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-00776-3/05.18

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

# **Table of Contents**

| Design Constraints                  | 7  |

|-------------------------------------|----|

| Families Supported                  | 9  |

| Constraint Support                  |    |

| Constraint File Format              |    |

| Basic Concepts                      |    |

| Naming Conventions                  |    |

| Clock                               |    |

| Region                              |    |

| Location                            |    |

| I/O Attributes                      | 14 |

| I/O Attributes                      | 15 |

| I/O Attributes by Family and Device |    |

|                                     |    |

| Entering Constraints                |    |

| Importing Constraint Files          | 16 |

| Exporting Constraint Files          | 17 |

| Constraints by Name: Timing         |    |

| Create Clock                        |    |

| Create Generated Clock              | 18 |

| Remove Clock Uncertainty            | 19 |

| Set Clock Latency                   | 20 |

| Set Clock Uncertainty Constraint    | 20 |

| Set Disable Timing Constraint       | 21 |

| Set False Path                      | 21 |

| Set Input Delay                     |    |

| Set Maximum Delay                   |    |

| Set Minimum Delay                   |    |

| Set Multicycle Path                 |    |

| Set Output Delay                    |    |

| Assign I/O Macro to Location        |    |

| Assign Macro to Region              |    |

| Assign Net to Region                |    |

| Configure I/O Bank                  |    |

| Create Region                       |    |

| Move Region                         | 28 |

| Constraints by File Format - SDC Command Reference | 29 |

|----------------------------------------------------|----|

| About Synopsys Design Constraints (SDC) Files)     |    |

| SDC Syntax Conventions                             |    |

|                                                    |    |

| Referenced Topics                                  |    |

| create_clock                                       | 32 |

| create_generated_clock                             | 33 |

| set_clock_latency                                  | 35 |

| set_clock_to_output                                | 36 |

| set_clock_uncertainty                              |    |

| set_disable_timing                                 | 39 |

| set_external_check                                 | 40 |

| set_false_path                                     | 40 |

| set_input_delay                                    | 41 |

| set_max_delay (SDC)                                | 43 |

| set_min_delay                                      | 44 |

| set_multicycle_path                                | 45 |

| set_output_delay                                   | 46 |

|                                                    |    |

| Design Object Access Commands                      |    |

| Design Object Access Commands                      |    |

| all_inputs                                         |    |

| all_outputs                                        |    |

| all_registers                                      |    |

| get_cells                                          |    |

| get_clocks                                         |    |

| get_pins                                           |    |

| get_nets                                           |    |

| get_ports                                          |    |

| About Physical Design Constraint (PDC) Files       |    |

| PDC Syntax Conventions                             |    |

| PDC Naming Conventions                             |    |

| assign_net_macros                                  |    |

| assign_region                                      |    |

| define_region                                      |    |

| move_region                                        |    |

| reserve                                            |    |

| set_io                                             |    |

| set_iobank                                         |    |

| set_location                                       |    |

| set_preserve                                       |    |

| Placement Rules for PLLs and DLLs                  | 76 |

# **Design Constraints**

Design constraints are usually either requirements or properties in your design. You use constraints to ensure that your design meets its performance goals and pin assignment requirements.

The Libero SoC software supports both SDC timing and PDC physical constraints. In addition, it supports netlist optimization constraints. You can set constraints by either using Microsemi's interactive tools (I/O Editor, Chip Planner, and Constraint Editor) or by <u>importing</u> constraint files directly into your design session. Use the Constraint Manager to manage all your design constraints.

### **SDC Timing Constraints**

Timing constraints represent the performance goals for your designs. Microsemi software uses timing constraints to guide the timing-driven optimization tools in order to meet these goals.

You can set timing constraints either globally or to a specific set of paths in your design.

You can apply timing constraints to:

- Specify the required minimum speed of a clock domain

- · Set the input and output port timing information

- Define the maximum delay for a specific path

- · Identify paths that are considered false and excluded from the analysis

- Identify paths that require more than one clock cycle to propagate the data

- Provide the external load at a specific port

To get the most effective results from the software, you need to set the timing constraints close to your design goals. Sometimes slightly tightening the timing constraint helps the optimization process to meet the original specifications.

#### **PDC Physical Constraints**

You can specify the physical constraints to define the size, shape, utilization, and pin/pad placement of a design. You can specify these constraints based on the utilization, aspect ratio, and dimensions of the die. The pin/pad placement depends on the external physical environment of the design, such as the placement of the device on the board.

There are three types of physical constraints:

- I/O assignments

- Set location, attributes, and technologies for I/O ports

- Specify special assignments, such as VREF pins and I/O banks

- Location and region assignments

- Set the location of Core, RAM, and FIFO macros

- Create Regions for I/O and Core macros as well as modify those regions

- Clock assignments

- Assign nets to clocks

- Assign global clock constraints to global, quadrant, and local clock resources

### **Netlist Optimization Constraints**

The software enables you to set some advanced design-specific netlist optimizing constraints. You can apply netlist optimization constraints to:

• Delete or restore a buffer tree

- Manage the fan-outs of the nets

- Manage macro combinations (for example, IO-REG combining)

- Optimize a netlist by removing buffers and/or inverters, propagating constants, and so on

#### See Also

Constraint Support by Family Constraint Entry Table Constraint File Format by Family Naming Conventions PolarFire I/O Editor User Guide PolarFire Timing Constraints Editor User Guide PolarFire FPGA User I/O User Guide PolarFire PDC Commands User Guide PolarFire FPGA Timing Constraints User Guide

# **Families Supported**

# **Constraint Support**

Use the Constraint Support table to see which constraints you can use. Click the name of a constraint in the table for more information.

|                              | PolarFire |  |

|------------------------------|-----------|--|

| Timing                       |           |  |

|                              | v         |  |

| Create a clock               | X         |  |

| Create a generated clock     | x         |  |

| Remove clock uncertainty     | х         |  |

| Set clock latency            | х         |  |

| Set clock uncertainty        | x         |  |

| Set disable timing           | х         |  |

| Set false path               | х         |  |

| <u>Set input delay</u>       | x         |  |

| Set load on output port      | х         |  |

| <u>Set maximum delay</u>     | x         |  |

| <u>Set minimum delay</u>     | х         |  |

| Set multicycle path          | x         |  |

| <u>Set output delay</u>      | x         |  |

| Physical Placement           |           |  |

| -Clocks                      |           |  |

| Assign Net to Global Clock   |           |  |

| Assign Net to Local Clock    |           |  |

| Assign Net to Quadrant Clock |           |  |

| -Regions                     |           |  |

| Assign Macro to Region       | x         |  |

| Assign Net to Region         | x         |  |

Table 1 · Constraint Support

|                                             | PolarFire |  |

|---------------------------------------------|-----------|--|

| Timing                                      |           |  |

| Create Region                               | х         |  |

| Delete Regions                              | х         |  |

| Move Region                                 | X         |  |

| Unassign macro(s) driven by net             | X         |  |

| Unassign Macro from Region                  | X         |  |

| -I/Os                                       |           |  |

| Assign I/O to pin                           | x         |  |

| Assign I/O Macro to Location                | x         |  |

| Configure I/O Bank                          | x         |  |

| Reset attributes on I/O to default settings | x         |  |

| Reset I/O bank to default settings          | x         |  |

| Reserve pins                                | x         |  |

| <u>Unreserve pins</u>                       | X         |  |

| -Block                                      |           |  |

| Move Block                                  | x         |  |

| Set Port Block                              | x         |  |

| Set Block Options                           | x         |  |

| -Nets                                       |           |  |

| Assign Net to Global Clock                  |           |  |

| Assign Net to Local Clock                   |           |  |

| Assign Net to Quadrant Clock                |           |  |

| Assign Net to Region                        | x         |  |

| Reset net's criticality to default level    |           |  |

| Set Net's Criticality                       |           |  |

| Unassign macro(s) driven by net             | x         |  |

| Netlist Optimizatio                         | n         |  |

| Delete buffer tree                          |           |  |

|                                   | PolarFire |

|-----------------------------------|-----------|

| Timing                            |           |

| Demote Global Net to Regular Net  |           |

| Promote regular net to global net |           |

| Restore buffer tree               |           |

| Set preserve                      | х         |

### See Also

Constraint Entry Table Constraint File Format by Family

# **Constraint File Format**

Use the File Format table to see which file formats apply to each type of constraint.

| Table 2 · | Constraint | File | Format |

|-----------|------------|------|--------|

|-----------|------------|------|--------|

| Family    | Timing | Physical Placement | Netlist Optimiization |

|-----------|--------|--------------------|-----------------------|

|           | SDC    | PDC                | PDC                   |

| PolarFire | х      | х                  | х                     |

SDC – Synopsys Design Constraints

PDC – Physical Design Constraints

### See Also

Constraint Support by Family Constraint Entry Table

# **Basic Concepts**

# **Naming Conventions**

The names of ports, instances, and nets in an imported netlist are sometimes referred to as their original names. Port names appear exactly as they are defined in a netlist. Instances and nets display the original names plus an escape character (\) before each backslash (/) and each slash (\) that is not a hierarchy separator. For example, the instance named A/B is displayed as A/\\B.

The following components use the Tcl-compliant original names:

- PDC reader/writer

- SDC reader/writer

- Compile report

- SDF/Netlist writer for back annotation

- SmartTime

- SmartPower

#### See Also

PDC Naming Conventions

# Clock

Specifying clock constraints is the most effective way of constraining and verifying the timing behavior of a sequential design. You must use clock constraints to meet your performance goals and to quickly reach timing closure.

Best practice is to specify and constrain all clocks used in the design.

To create a clock constraint, you must provide the following clock information:

Clock source: Specifies the pin or port where the clock signal is defined.

Clock period or frequency: Defines the smallest amount of time after which the signal repeats itself.

Duty cycle: Defines the percentage of time during which the clock period is high.

First edge: Indicates whether the first edge of the clock is rising or falling.

Offset: Indicates the shift of the first edge with respect to instant zero common to all clocks in the design.

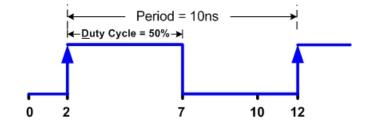

## Example 1:

create\_clock -period 10 -waveform {27}

This example creates a clock with 10ns period, 2ns offset, and 50% duty cycle using the SDC command.

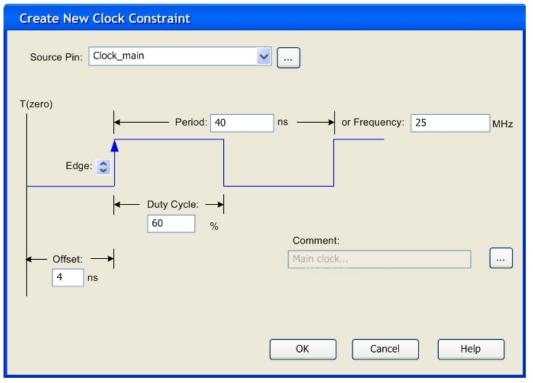

# Example 2:

This example shows how to create a clock with 25MHz frequency, 4ns offset for its first rising edge, and 60% duty cycle using the SmartTime Constraints Editor. Using the Create New Clock Constraint dialog box is equivalent to using the SDC command: create\_clock -period 40 -waveform {4, 28}.

#### See Also

Constraint support by family Constraint entry table create\_clock (SDC) global\_clocks (DCF) Specifying Clock Constraints

# Region

A region is a user-defined area on a chip into which you can constrain the physical placement of one or more macros. You can also constrain macros containing multiple tiles for cores, RAMs, and I/Os. The floorplanning process usually requires you to create several regions and assign logic to them. Logic can include core logic, memory, and I/O modules. When you run the place-and-route tool, it places the logic into their assigned regions.

Some regions are user-defined and others are automatically created by the tools to meet routing requirements (for example, Local clock regions).

You can use region constraints to:

- Create user-defined regions such as Inclusive, Exclusive, Empty, LocalClock, and QuadrantClock

- · Assign and unassign macros to user-defined regions

- Constrain all the macros connected to a net by assigning them to a specific net region

- Move regions from one set of co-ordinates to another

#### See Also

Assign Macro to Region Create Region Delete Region Move Region Unassign macro from region About Floorplanning, Creating Regions, Editing Regions

# Location

Each core, RAM, and I/O macro in the design is associated with a location on the device. When you run the place-and-route tool, it places all of your logic into their assigned locations.

You can use location constraints to:

- Overwrite the existing placements of macros

- · Tell the place-and-route tool where to initially place the macros

- · Assign I/O macros to specific pins to meet your board's requirements

#### See Also

<u>Assign I/O to pin</u> <u>Assign macro to location</u> Assigning Logic to Locations, Moving Logic to Other Locations, Assigning Pins, Unassigning Pins

# I/O Attributes

I/O attributes are the characteristics of logic macros or nets in your design. They indicate placement, implementation, naming, directionality, and other characteristics. This information is used by the design implementation software during the place-and-route of a design.

### See Also

I/O Attributes by Family PolarFire I/O Editor User Guide PolarFire PDC Commands User Guide PolarFire FPGA User I/O User Guide

# **I/O Attributes**

# I/O Attributes by Family and Device

For details about the I/O standards and attributes supported in this PolarFire release, see the following documents:

- PolarFire FPGA User I/Os User Guide

- PolarFire FPGA PDC Commands User Guide

# **Entering Constraints**

You can enter design constraints in the following ways:

- Importing constraint files: You can import PDC or SDC constraint files

- Using constraint editor tools: You can use the PolarFire I/O Editor to create and modify physical, logical, and timing constraints. This enables you to enter constraints without having to understand PDC or other file syntax. The constraints you enter are saved in a PDC or SDC file inside the Libero SoC project.

#### See Also

Constraint Support by Family Constraint Entry Constraint File Format by Family Constraint Manager PolarFire I/O Editor User Guide PolarFire Timing Constraints Editor User Guide PolarFire FPGA User I/O User Guide PolarFire PDC Commands User Guide PolarFire FPGA Timing Constraints User Guide

# **Importing Constraint Files**

For details on how to import Constraint Files into a Libero SoC PolarFire project, see Constraint Manager. For details about how to import Constraint Files into a Libero SoC project, see Constraint Manager.

### **Source File**

Import constraints file as source files if they were created with external tools that will be tracked (audited). This helps to coordinate the design changes better.

The following table shows different constraints format files that can be imported as source files for specific families.

| Source Files                       | File Type Extension | Family    |

|------------------------------------|---------------------|-----------|

| Physical Design<br>Constraint File | *.pdc               | PolarFire |

| Synopsys<br>Constraint File        | *.sdc               | PolarFire |

Table 3 · File Types You Can Import as Source Files

#### See Also

Importing source files Keep Existing Timing Constraints Keep Existing Physical Constraints

# **Exporting Constraint Files**

The following table shows the constraint files that you can export.

| File                       | File Extension | Families  |

|----------------------------|----------------|-----------|

| SDC                        | *.sdc          | PolarFire |

| Physical Design Constraint | *.pdc          | PolarFire |

# **Constraints by Name: Timing**

# **Create Clock**

# **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime |

|-----------|-----|-----------|

| PolarFire | Х   | x         |

#### **Purpose**

Use this constraint to create a clock constraint at a specific source and define its waveform. The static timing analysis tool uses this information to propagate the waveform across the clock network to the clock pins of all sequential elements driven by the defined clock source. The clock information is also used to compute the slacks in the specified clock domain, display setup and hold violations, and drive optimization tools such as place-and-route.

### **Tools /How to Enter**

You can use one or more of the following methods to enter clock constraints:

- SDC create\_clock

- SmartTime Specifying Clock Constraint

#### See Also

<u>Constraint Entry</u> <u>create\_clock</u> (SDC) <u>Clock</u> Definition <u>Specifying Clock Constraint</u>

# **Create Generated Clock**

### **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraint<br>Editor |

|-----------|-----|-----------|----------------------|

| PolarFire | х   |           | Х                    |

### **Purpose**

Use this constraint to create an internally generated clock constraint, such as clock dividers and PLL. The generated clock is defined in terms of multiplication and/or division factors with respect to a reference clock pin. When the reference clock pin changes, the generated clock is updated automatically.

### **Tools /How to Enter**

You can use one or more of the following methods to enter clock constraints:

- SDC create generated clock

- SmartTime <u>Specifying Generated Clock Constraint</u>

#### See Also

<u>Constraint Entry</u> <u>create\_generated\_clock</u> (SDC) <u>Specifying Generated Clock Constraint</u>

# **Remove Clock Uncertainty**

### **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC Constraints | Tcl command passed to SmartTime |

|-----------|-----------------|---------------------------------|

| PolarFire | No              | No                              |

### **Purpose**

Use this constraint to remove the timing uncertainty between two clock waveforms within SmartTime.

You can remove clock uncertainty constraints in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist. Alternatively, you can remove clock uncertainty using the GUI tools in the Designer software.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to remove clock uncertainty:

- SDC remove clock uncertainty

- SmartTime <u>Specifying Clock-to-Clock Uncertainty Constraint</u>

#### See Also

<u>Constraint Entry</u> <u>set\_clock\_uncertainty</u>(SDC) *SmartTime User's Guide*: Specifying Clock-to-Clock Uncertainty Constraint

# Set Clock Latency

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraint Editor |

|-----------|-----|-----------|-------------------|

| PolarFire | х   |           | x                 |

### **Purpose**

Use this constraint to define the delay between an external clock source and the definition pin of a clock within SmartTime.

You can set clock latency constraints in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist. Alternatively, you can set clock latency using the GUI tools in the Designer software when you implement your design.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to set clock latency:

- SDC <u>set clock latency</u>

- SmartTime Specifying Clock Source Latency

#### See Also

<u>Constraint Entry</u> <u>set\_clock\_latency</u> (SDC) Specifying Clock Source Latency

# Set Clock Uncertainty Constraint

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraints<br>Editor |

|-----------|-----|-----------|-----------------------|

| PolarFire | х   |           | х                     |

### **Purpose**

Use this constraint to define the timing uncertainty between two clock waveforms or maximum skew within SmartTime.

You can set clock uncertainty constraints in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist. Alternatively, you can set clock uncertainty using the GUI tools in the Designer software when you implement your design.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to set clock uncertainty:

• SDC - <u>set clock uncertainty</u>

SmartTime - Specifying Clock-to-Clock Uncertainty Constraint

#### See Also

<u>Constraint Entry</u> <u>set\_clock\_uncertainty</u>(SDC)

# Set Disable Timing Constraint

### **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraints Editor |

|-----------|-----|-----------|--------------------|

| PolarFire | х   |           | х                  |

#### **Purpose**

Use this constraint disable the timing arc in the specified ports on a path.

You can disable the timing arc in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist. Alternatively, you can disable the timing arc using the GUI tools in the Designer software when you implement your design.

#### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to set maximum delay exception constraints:

SDC – <u>set\_disable\_timing</u>

#### See Also

<u>Constraint Entry</u> <u>set\_disable\_timing(SDC)</u>

# Set False Path

### **Families Supported**

The following table shows which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraints Editor |

|-----------|-----|-----------|--------------------|

| PolarFire | х   |           | х                  |

#### Purpose

Use this constraint to identify paths in the design that should be disregarded during timing analysis and timing optimization.

By definition, false paths are paths that cannot be sensitized under any input vector pair. Therefore, including false paths in timing calculation may lead to unrealistic results. For accurate static timing analysis, it is important to identify the false paths.

You can set false paths constraints in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist.

## **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to set false paths:

- SDC <u>set\_false\_path</u>

- SmartTime Specifying False Path Constraint

#### See Also

<u>Constraint Entry</u> <u>set\_false\_path</u> (SDC) <u>Breaks Tab</u> <u>Specifying False Path Constraint</u>

# Set Input Delay

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constr<br>aints<br>Editor |

|-----------|-----|-----------|---------------------------|

| PolarFire | х   |           | х                         |

### **Purpose**

Use this constraint to define the arrival time relative to a clock.

## **Tools /How to Enter**

You can use one or more of the following methods to set input delay constraint:

- SDC set input delay

- SmartTime Specifying Input Delay Constraint

#### See Also

<u>Constraint Entry</u> <u>set\_input\_delay</u> (SDC) <u>Specifying Input Delay Constraint</u>

# Set Maximum Delay

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraints<br>Editor |

|-----------|-----|-----------|-----------------------|

| PolarFire | Х   |           | Х                     |

### **Purpose**

Use this constraint to set the maximum delay exception between the specified ports on a path.

You can set maximum delay exception in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist. Alternatively, you can set maximum delay exceptions using the GUI tools in the Designer software when you implement your design.

# **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to set maximum delay exception constraints:

- SDC <u>set\_max\_delay</u>

- SmartTime <u>Specifying Maximum Delay Constraint</u>

#### See Also

<u>Constraint Entry</u> <u>set\_max\_delay</u> (SDC)

# Set Minimum Delay

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constra<br>ints<br>Editor |

|-----------|-----|-----------|---------------------------|

| PolarFire | Х   |           | х                         |

## **Purpose**

Use this constraint to set the minimum delay exception between the specified ports on a path.

You can set minimum delay exception in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist. Alternatively, you can set minimum delay exceptions using the GUI tools in the Designer software when you implement your design.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to set maximum delay exception constraints:

- SDC <u>set min delay</u>

- SmartTime <u>Specifying minimum delay constraint</u>

#### See Also

Constraint Entry

set\_min\_delay (SDC)

# Set Multicycle Path

# **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraints Editor |

|-----------|-----|-----------|--------------------|

| PolarFire | Х   |           | x                  |

## Purpose

Use this constraint to identify paths in the design that take multiple clock cycles.

You can set multicycle path constraints in an SDC file, which you can either create yourself or generate with Synthesis tools, at the same time you import the netlist.

## **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to set multicycle paths constraints:

- SDC <u>set multicycle path</u>

- SmartTime <u>Specifying Input Delay Constraint</u>

#### See Also

<u>Constraint Entry</u> <u>set\_multicycle\_paths</u> (SDC) <u>Specifying Input Delay Constraint</u>

# Set Output Delay

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | SDC | SmartTime | Constraints Editor |

|-----------|-----|-----------|--------------------|

| PolarFire | Х   |           | х                  |

## **Purpose**

Use this constraint to set the output delay of an output relative to a clock.

## **Tools /How to Enter**

You can use one or more of the following methods to set output delay constraints:

- SDC <u>set\_output\_delay</u>

- SmartTime <u>Specifying Output Delay Constraint</u>

#### See Also

Constraint Entry

set\_output\_delay (SDC)

# Assign I/O Macro to Location

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | PDC | ChipPlanner |

|-----------|-----|-------------|

| PolarFire | Х   | х           |

### **Purpose**

Use this constraint to assign one or more I/O macros to a specific location. You can define the location using array co-ordinates.

By confining macros to one area, you can keep the nets connected to that area, resulting in better timing and better floorplanning. Sometimes placing some macros at specific locations can also result in meeting timing closures.

# **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to assign a macro to a location:

- PDC set location

- ChipPlanner -

#### See Also

Constraint Entry

set\_location (PDC)

- : Assigning Logic to Locations

- : Assigning Logic

# Assign Macro to Region

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | PDC | ChipPlanner |

|-----------|-----|-------------|

| PolarFire | Х   | х           |

### **Purpose**

Use this constraint to assign one or more macros to a specific region.

By confining macros to one area, you can keep the nets connected to that area, resulting in better timing and better floorplanning.

You can use the define\_region PDC command to create a region, and then use the assign\_region PDC command to constrain a set of existing macros to that region.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to assign a macro to a region:

- PDC assign\_region

- ChipPlanner Assigning a macro to a region

#### See Also

<u>Constraint Entry</u> <u>assign\_region</u> (PDC) <u>Assigning a Macro to a Region</u>

# Assign Net to Region

### **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | PDC | ChipPlanner |

|-----------|-----|-------------|

| PolarFire | Х   | x           |

### **Purpose**

Use this constraint to place all the loads of a net into a given region. This constraint is useful for high fan-out or critical path nets or bus control logic.

Constraining nets to a region helps to control the connection delays from the net's driver to the logic instances it fans out to. You can adjust the size of the region to pack logic more closely together, hence, improving its net delays.

Suppose you have a global net with loads that span across the whole chip. When you constrain this net to a specific region, you force the loads of this global net into the given region. Forcing loads into a region frees up some areas that were previously used. You can then use these free areas for high-speed local clocks/spines.

Macros connected to a specific net can be assigned to a region in the device. The region can be defined using the define\_region PDC command.

When assigning a net to a region, all of the logic driven by that net will be assigned to that region.

#### Using Regions for Critical Path and High Fan-out Nets

You should assign high fan-out or critical path nets to a region only after you have used up your global routing and clock spine networks. If you have determined, through timing analysis, that certain long delay nets are creating timing violations, assign them to regions to reduce their delays.

Before creating your region, determine if any logic connected to instances spanned by these nets have any timing requirements. Your region could alter the placement of all logic assigned to it. This may have an undesired side effect of altering the timing delays of some logic paths that cross through the region but are not assigned to it. These paths could fail your timing constraints depending on which net delays have been altered.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to assign a net to a region:

- PDC

- Chip Planner

See Also <u>Constraint Entry</u> <u>assign\_net\_macros</u> (PDC) Assigning a Net to a Region

# Configure I/O Bank

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | PDC | ChipPlanner |

|-----------|-----|-------------|

| PolarFire | Х   | х           |

#### **Purpose**

Use this constraint to set the I/O supply voltage (VCCI) for I/O banks.

I/Os are organized into banks. The configuration of these banks determines the I/O standards supported. Since each I/O bank has its own user-assigned input reference voltage (VREF) and an input/output supply voltage, only I/Os with compatible standards can be assigned to the same bank.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to configure I/O banks:

- PDC set\_iobank

- ChipPlanner Manually Assigning Technologies to I/O Banks

#### See Also

Constraint Entry set\_iobank

# **Create Region**

## **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | PDC | ChipPlanner |

|-----------|-----|-------------|

| PolarFire | Х   | x           |

### **Purpose**

Use this constraint to create either a rectangular or rectilinear region on a device.

You can create a region within a device for setting specific physical constraints or for achieving better floorplanning. You can define regions with the array coordinates for that particular device.

You can use the define\_region PDC command to create a rectangular or rectilinear region, and then use the assign\_region PDC command to constrain a set of macros to that region.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to create a region constraint:

- PDC -define\_region

- Chip Planner Creating regions

#### See Also

<u>Constraint Entry</u> <u>define\_region</u> (PDC)

# **Move Region**

# **Families Supported**

The following table shows which families support this constraint and which file formats and tools you can use to enter or modify it:

| Families  | PDC | ChipPlanner |

|-----------|-----|-------------|

| PolarFire | Х   | x           |

### **Purpose**

Use this constraint to move the location of a previously defined region.

### **Tools /How to Enter**

You can use one or more of the following commands or GUI tools to move a region:

- PDC move\_region

- ChipPlanner Editing Regions

#### See Also

<u>Constraint Entry</u> <u>move\_region</u> (PDC)

# **Constraints by File Format - SDC Command Reference**

# About Synopsys Design Constraints (SDC) Files)

Synopsys Design Constraints (SDC) is a Tcl-based format used by Synopsys tools to specify the design intent, including the timing and area constraints for a design. Microsemi tools use a subset of the SDC format to capture supported timing constraints. Any timing constraint that you can enter using Designer tools can also be specified in an SDC file.

Use the SDC-based flow to share timing constraint information between Microsemi tools and third-party EDA tools.

| Command                 | Action                                                                                                |  |

|-------------------------|-------------------------------------------------------------------------------------------------------|--|

| create_clock            | Creates a clock and defines its characteristics                                                       |  |

| create_generated_clock  | Creates an internally generated clock and defines its characteristics                                 |  |

| set clock latency       | Defines the delay between an external clock source and the definition pin of a clock within SmartTime |  |

| set_clock_uncertainty   | Defines the timing uncertainty between two clock waveforms or maximum skew                            |  |

| <u>set false path</u>   | Identifies paths that are to be considered false and excluded from the timing analysis                |  |

| set_input_delay         | Defines the arrival time of an input relative to a clock                                              |  |

| set max delay           | Specifies the maximum delay for the timing paths                                                      |  |

| set_min_delay           | Specifies the minimum delay for the timing paths                                                      |  |

| set_multicycle_path     | Defines a path that takes multiple clock cycles                                                       |  |

| <u>set_output_delay</u> | Defines the output delay of an output relative to a clock                                             |  |

#### See Also

Constraint Entry SDC Syntax Conventions Importing Constraint Files

# **SDC Syntax Conventions**

The following table shows the typographical conventions that are used for the SDC command syntax.

| Syntax<br>Notation    | Description                                                                                                              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|

| command -<br>argument | Commands and arguments appear in Courier New typeface.                                                                   |

| variable              | Variables appear in blue, italic <i>Courier New</i> typeface. You must substitute an appropriate value for the variable. |

| [-argument<br>value]  | Optional arguments begin and end with a square bracket.                                                                  |

Note: SDC commands and arguments are case sensitive.

### **Example**

The following example shows syntax for the create\_clock command and a sample command:

create\_clock -period period\_value [-waveform edge\_list] source

```

create_clock -period 7 -waveform {2 4}{CLK1}

```

## Wildcard Characters

You can use the following wildcard characters in names used in the SDC commands:

| Wildcard | What it does                            |  |

|----------|-----------------------------------------|--|

| ١        | Interprets the next character literally |  |

| *        | Matches any string                      |  |

Note: The matching function requires that you add a backslash (\) before each slash in the pin names in case the slash does not denote the hierarchy in your design.

# Special Characters ([ ], { }, and \)

Square brackets ([]) are part of the command syntax to access ports, pins and clocks. In cases where these netlist objects names themselves contain square brackets (for example, buses), you must either enclose the names with curly brackets ({}) or precede the open and closed square brackets ([]) characters with a backslash (\). If you do not do this, the tool displays an error message.

#### For example:

```

create_clock -period 3 clk[0]

```

set\_max\_delay 1.5 -from [get\_pins ff1\[5\]:CLK] -to [get\_clocks {clk[0]}]

Although not necessary, Microsemi recommends the use of curly brackets around the names, as shown in the following example:

set\_false\_path -from {data1} -to [get\_pins {reg1:D}]

In any case, the use of the curly bracket is mandatory when you have to provide more than one name. For example:

```

set_false_path -from {data3 data4} -to [get_pins {reg2:D reg5:D}]

```

### **Entering Arguments on Separate Lines**

If a command needs to be split on multiple lines, each line except the last must end with a backslash (\) character as shown in the following example:

```

set_multicycle_path 2 -from \

```

[get\_pins {reg1\*}] \

-to {reg2:D}

See Also About SDC Files

# **Referenced Topics**

# create\_clock

SDC command; creates a clock and defines its characteristics.

create\_clock -name clock name -add -period period\_value [-waveform edge\_list] source

### Arguments

#### -name clock\_name

Specifies the name of the clock constraint. This parameter is required for virtual clocks when no clock source is provided.

#### -add

Specifies that a new clock constraint is created at the same source as the existing clock without overriding the existing constraint. The name of the new clock constraint with the -add option must be different than the existing clock constraint. Otherwise, it will override the existing constraint, even with the -add option. The -name option must be specified with the -add option.

#### -period period\_value

Specifies the clock period in nanoseconds. The value you specify is the minimum time over which the clock waveform repeats. The period\_value must be greater than zero.

#### -waveform edge\_list

Specifies the rise and fall times of the clock waveform in ns over a complete clock period. There must be exactly two transitions in the list, a rising transition followed by a falling transition. You can define a clock starting with a falling edge by providing an edge list where fall time is less than rise time. If you do not specify -waveform option, the tool creates a default waveform, with a rising edge at instant 0.0 ns and ©a falling edge at instant (period\_value/2)ns.

#### source

Specifies the source of the clock constraint. The source can be ports or pins in the design. If you specify a clock constraint on a pin that already has a clock, the new clock replaces the existing one. Only one source is accepted. Wildcards are accepted as long as the resolution shows one port or pin.

### **Description**

Creates a clock in the current design at the declared source and defines its period and waveform. The static timing analysis tool uses this information to propagate the waveform across the clock network to the clock pins of all sequential elements driven by this clock source.

The clock information is also used to compute the slacks in the specified clock domain that drive optimization tools such as place-and-route.

#### **Exceptions**

None

### **Examples**

The following example creates two clocks on ports CK1 and CK2 with a period of 6, a rising edge at 0, and a falling edge at 3: create\_clock -name {my\_user\_clock} -period 6 CK1

create\_clock -name {my\_other\_user\_clock} -period 6 -waveform {0 3} {CK2}

The following example creates a clock on port CK3 with a period of 7, a rising edge at 2, and a falling edge at 4:

create\_clock -period 7 -waveform {2 4} [get\_ports {CK3}]

The following example creates a new clock constraint clk2, in addition to clk1, on the same source port clk1 without overriding it.

create\_clock -name clk1 -period 10 -waveform {0 5} [get\_ports clk1]

create\_clock -name clk2 -add -period 20 -waveform {0 10} [get\_ports clk1] The following example does not add a new clock constraint, even with the -add option, but overrides the existing clock constraint because of the same clock names. Note: To add a new clock constraint in addition to the existing clock constraint on the same source port, the clock names must be different.

```

create_clock -name clk1 -period 10 -waveform {0 5} [get_ports clk1]

create_clock -name clk1 -add -period 50 -waveform {0 25} [get_ports clk1]

```

## **Microsemi Implementation Specifics**

- The -waveform in SDC accepts waveforms with multiple edges within a period. In Microsemi design

implementation, only two waveforms are accepted.

- SDC accepts defining a clock on many sources using a single command. In Microsemi design

implementation, only one source is accepted.

- The source argument in SDC create\_clock command is optional. This is in conjunction with the -name argument in SDC to support the concept of virtual clocks. In Microsemi implementation, source is a mandatory argument as -name and virtual clocks concept is not supported.

- The -domain argument in the SDC create\_clock command is not supported.

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions Clock Definition Create Clock Create a New Clock Constraint

# create\_generated\_clock

SDC command; creates an internally generated clock and defines its characteristics.

create\_generated\_clock -name clock\_name [-add] [-master\_clock clock\_name] -source reference\_pin [-divide\_by divide\_factor] [-multiply\_by multiply\_factor] [-invert] source pll\_output pll\_feedback\_clock -pll\_feedback pll\_feedback\_input

## Arguments

```

-name clock_name

```

Specifies the name of the clock constraint. This parameter is required for virtual clocks when no clock source is provided.

-add

Specifies that the generated clock constraint is a new clock constraint in addition to the existing one at the same source. The name of the clock constraint should be different from the existing clock constraint. With this option, -master\_clock option and -name options must be specified.

```

-master_clock clock_name

```

Specifies the master clock used for the generated clock when multiple clocks fan into the master pin. This option must be used in conjuction with -add option of the generated clock.

#### Notes:

- 1. The master\_clock option is used only with the -add option for the generated clocks.

- 2. If there are multiple master clocks fanning into the same reference pin, the first generated clock specified will always use the first master clock as its source clock.

- 3. The subsequent generated clocks specified with the -add option can choose any of the master clocks as their source clock (including the first master clock specified).

#### -source reference\_pin

Specifies the reference pin in the design from which the clock waveform is to be derived.

#### -divide\_bydivide\_factor

Specifies the frequency division factor. For instance if the *divide\_factor* is equal to 2, the generated clock period is twice the reference clock period.

#### -multiply\_by multiply\_factor

Specifies the frequency multiplication factor. For instance if the *multiply\_factor* is equal to 2, the generated clock period is half the reference clock period.

-invert

Specifies that the generated clock waveform is inverted with respect to the reference clock.

source

Specifies the source of the clock constraint on internal pins of the design. If you specify a clock constraint on a pin that already has a clock, the new clock replaces the existing clock. Only one source is accepted. Wildcards are accepted as long as the resolution shows one pin.

-pll\_output pll\_feedback\_clock

Specifies the output pin of the PLL which is used as the external feedback clock. This pin must drive the feedback input pin of the PLL specified using the -pll\_feedback option. The PLL will align the rising edge of the reference input clock to the feedback clock. This is a mandatory argument if the PLL is operating in external feedback mode.

#### -pll\_feedback pll\_feedback\_input

Specifies the feedback input pin of the PLL. This pin must be driven by the output pin of the PLL specified using the -pll\_output option. The PLL will align the rising edge of the reference input clock to the external feedback clock. This is a mandatory argument if the PLL is operating in external feedback mode.

#### Description

Creates a generated clock in the current design at a declared source by defining its frequency with respect to the frequency at the reference pin. The static timing analysis tool uses this information to compute and propagate its waveform across the clock network to the clock pins of all sequential elements driven by this source.

The generated clock information is also used to compute the slacks in the specified clock domain that drive optimization tools such as place-and-route.

#### **Examples**

The following example creates a generated clock on pin U1/reg1:Q with a period twice as long as the period at the reference port CLK.

create\_generated\_clock -name {my\_user\_clock} -divide\_by 2 -source [get\_ports {CLK}]

U1/reg1/Q

The following example creates a generated clock at the primary output of myPLL with a period <sup>3</sup>/<sub>4</sub> of the period at the reference pin clk.

create\_generated\_clock -divide\_by 3 -multiply\_by 4 -source clk [get\_pins {myPLL/CLK1}] The following example creates a new generated clock gen2 in addition to gen1 derived from same master clock as the existing generated clock, and the new constraints is added to pin r1/CLK.

create\_generated\_clock -name gen1 -multiply\_by 1 -source [get\_ports clk1] [get\_pins

r1/CLK]

```

create_generated_clock -name gen2 -add -master_clock clk1 -source [get_ports clk1] -

multiply_by 2 [get_pins r1/CLK]

```

The following example does not create a new generated clock constraint in addition to the existing clock, but will override even with the -add option enabled, because the same names are used.

```

create_generated_clock -name gen2 -source [get_ports clk1] -multiply_by 3 [get_pins

r1/CLK]

```

create\_generated\_clock -name gen2 -source [get\_ports clk1] -multiply\_by 4 -master\_clock

clk1 -add [get\_pins r1/CLK]

The following example creates a generated clock named system\_clk on the GL2 output pin of FCCC\_0 with a period equal to half the period of the source clock. The constraint also identifies GL2 output pin as the external feedback clock source and CLK2 as the feedback input pin for FCCC\_0.

```

create_generated_clock -name { system_clk } \

-multiply_by 2 \

-source { FCCC_0/CCC_INST/CLK3_PAD } \

-pll_output { FCCC_0/CCC_INST/GL2 } \

-pll_feedback { FCCC_0/CCC_INST/CLK2 } \

{ FCCC_0/CCC_INST/GL2 }

```

#### **Microsemi Implementation Specifics**

- SDC accepts either –multiply\_by or –divide\_by option. In Microsemi design implementation, both are

accepted to accurately model the PLL behavior.

- SDC accepts defining a generated clock on many sources using a single command. In Microsemi design implementation, only one source is accepted.

- The -duty\_cycle ,-edges and -edge\_shift options in the SDC create\_generated\_clock command are not supported in Microsemi design implementation.

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions Create Generated Clock Constraint (SDC)

# set\_clock\_latency

SDC command; defines the delay between an external clock source and the definition pin of a clock within SmartTime.

set\_clock\_latency -source [-rise][-fall][-early][-late] delay clock

### Arguments

-source

Specifies a clock source latency on a clock pin.

-rise

Specifies the edge for which this constraint will apply. If neither or both rise are passed, the same latency is applied to both edges.

-fall

Specifies the edge for which this constraint will apply. If neither or both rise are passed, the same latency is applied to both edges.

-invert

Specifies that the generated clock waveform is inverted with respect to the reference clock.

#### -late

Optional. Specifies that the latency is late bound on the latency. The appropriate bound is used to provide the most pessimistic timing scenario. However, if the value of "-late" is less than the value of "-early", optimistic timing takes place which could result in incorrect analysis. If neither or both "-early" and "-late" are provided, the same latency is used for both bounds, which results in the latency having no effect for single clock domain setup and hold checks.

#### -early

Optional. Specifies that the latency is early bound on the latency. The appropriate bound is used to provide the most pessimistic timing scenario. However, if the value of "-late" is less than the value of "-early", optimistic timing takes place which could result in incorrect analysis. If neither or both "-early" and "-late" are provided, the same latency is used for both bounds, which results in the latency having no effect for single clock domain setup and hold checks.

#### delay

Specifies the latency value for the constraint.

#### clock

Specifies the clock to which the constraint is applied. This clock must be constrained.

#### **Description**

Clock source latency defines the delay between an external clock source and the definition pin of a clock within SmartTime. It behaves much like an input delay constraint. You can specify both an "early" delay and a "late" delay for this latency, providing an uncertainty which SmartTime propagates through its calculations. Rising and falling edges of the same clock can have different latencies. If only one value is provided for the clock source latency, it is taken as the exact latency value, for both rising and falling edges.

#### **Exceptions**

None

#### **Examples**

The following example sets an early clock source latency of 0.4 on the rising edge of main\_clock. It also sets a clock source latency of 1.2, for both the early and late values of the falling edge of main\_clock. The late value for the clock source latency for the falling edge of main\_clock remains undefined.

set\_clock\_latency -source -rise -early 0.4 { main\_clock }

set\_clock\_latency -source -fall 1.2 { main\_clock }

#### **Microsemi Implementation Specifics**

SDC accepts a list of clocks to -set\_clock\_latency. In Microsemi design implementation, only one clock pin can have its source latency specified per command.

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions

# set\_clock\_to\_output

SDC command; defines the timing budget available inside the FPGA for an output relative to a clock.

set\_clock\_to\_output delay\_value -clock clock\_ref [-max] [-min] output\_list

#### Arguments

#### delay\_value

Specifies the clock to output delay in nanoseconds. This time represents the amount of time available inside the FPGA between the active clock edge and the data change at the output port.

```

-clock clock_ref

```

Specifies the reference clock to which the specified clock to output is related. This is a mandatory argument.

-max

Specifies that delay\_value refers to the maximum clock to output at the specified output. If you do not specify -max or -min options, the tool assumes maximum and minimum clock to output delays to be equal.

```

-min

```

Specifies that delay\_value refers to the minimum clock to output at the specified output. If you do not specify -max or -min options, the tool assumes maximum and minimum clock to output delays to be equal.

output\_list

Provides a list of output ports in the current design to which delay\_value is assigned. If you need to specify more than one object, enclose the objects in braces ({}).

### **Supported Families**

SmartFusion2, IGLOO2, RTG4, PolarFire, SmartFusion, IGLOO, ProASIC3, Fusion

### **Description**

The set\_clock\_to\_output command specifies the clock to output maximum and minimum delays on output ports relative to a clock edge. This usually represents a combinational path delay from a register internal to the current design to the output port. For in/out (bidirectional) ports, you can specify the path delays for both input and output modes. The tool uses clock to output delays for paths ending at primary outputs.

A clock is a singleton that represents the name of a defined clock constraint. This can be an object accessor that will refer to one clock. For example:

```

[get_clocks {system_clk}]

[get_clocks {sys*_clk}]

```

### **Examples**

The following example sets a maximum clock to output delay of 12 ns and a minimum clock to output delay of 6 ns for port data\_out relative to the rising edge of CLK1:

set\_clock\_to\_output 12 -clock [get\_clocks CLK1] -max [get\_ports data\_out]

set\_clock\_to\_output 6 -clock [get\_clocks CLK1] -min [get\_ports data\_out]

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions

# set\_clock\_uncertainty

SDC command; defines the timing uncertainty between two clock waveforms or maximum skew.

set\_clock\_uncertainty uncertainty (-from | -rise\_from | -fall\_from) from\_clock\_list (-to | rise\_to | -fall\_to) to\_clock\_list [-setup | -hold]

#### Arguments

#### uncertainty

Specifies the time in nanoseconds that represents the amount of variation between two clock edges. The value must be a positive floating point number.

-from

Specifies that the clock-to-clock uncertainty applies to both rising and falling edges of the source clock list. You can specify only one of the -from, -rise\_from, or -fall\_from arguments for the constraint to be valid. This option is the default.

#### -rise from

Specifies that the clock-to-clock uncertainty applies only to rising edges of the source clock list. You can specify only one of the -from, -rise\_from, or -fall\_from arguments for the constraint to be valid. -fall from

Specifies that the clock-to-clock uncertainty applies only to falling edges of the source clock list. You can specify only one of the -from, -rise\_from, or -fall\_from arguments for the constraint to be valid. from\_clock\_list

Specifies the list of clock names as the uncertainty source.

-to

Specifies that the clock-to-clock uncertainty applies to both rising and falling edges of the destination clock list. You can specify only one of the -to, -rise\_to, or -fall\_to arguments for the constraint to be valid.

-rise\_to

Specifies that the clock-to-clock uncertainty applies only to rising edges of the destination clock list. You can specify only one of the -to, -rise\_to, or -fall\_to arguments for the constraint to be valid.

-fall to

Specifies that the clock-to-clock uncertainty applies only to falling edges of the destination clock list. You can specify only one of the -to, -rise\_to, or -fall\_to arguments for the constraint to be valid.

#### to\_clock\_list

Specifies the list of clock names as the uncertainty destination.

-setup

Specifies that the uncertainty applies only to setup checks. If you do not specify either option (-setup or -hold) or if you specify both options, the uncertainty applies to both setup and hold checks.

-hold

Specifies that the uncertainty applies only to hold checks. If you do not specify either option (-setup or hold) or if you specify both options, the uncertainty applies to both setup and hold checks.

#### Description

Clock uncertainty defines the timing between an two clock waveforms or maximum clock skew.

Both setup and hold checks must account for clock skew. However, for setup check, SmartTime looks for the smallest skew. This skew is computed by using the maximum insertion delay to the launching sequential component and the shortest insertion delay to the receiving component.

For hold check, SmartTime looks for the largest skew. This skew is computed by using the shortest insertion delay to the launching sequential component and the largest insertion delay to the receiving component. SmartTime makes this distinction automatically.

#### **Exceptions**

None

#### **Examples**

The following example defines two clocks and sets the uncertainty constraints, which analyzes the interclock domain between clk1 and clk2.

create\_clock -period 10 clk1 create\_generated\_clock -name clk2 -source clk1 -multiply\_by 2 sclk1 set\_clock\_uncertainty 0.4 -rise\_from clk1 -rise\_to clk2

#### **Microsemi Implementation Specifics**

• SDC accepts a list of clocks to -set\_clock\_uncertainty.

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions create\_clock (SDC) create\_generated\_clock (SDC) remove\_clock\_uncertainty

## set\_disable\_timing

SDC command; disables timing arcs within the specified cell and returns the ID of the created constraint if the command succeeded.

set\_disable\_timing [-from from\_port] [-to to\_port] cell\_name

#### Arguments

-from from\_port

Specifies the starting port.

-to to\_port

Specifies the ending port.

cell\_name

Specifies the name of the cell in which timing arcs will be disabled.

#### **Description**

This command disables the timing arcs in the specified cell, and returns the ID of the created constraint if the command succeeded. The –from and –to arguments must either both be present or both omitted for the constraint to be valid.

#### **Examples**

The following example disables the arc between a2:A and a2:Y. set\_disable\_timing -from port1 -to port2 cellname This command ensures that the arc is disabled within a cell instead of between cells.

#### **Microsemi Implementation Specifics**

None

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions

## set\_external\_check

SDC command; defines the external setup and hold delays for an input relative to a clock.

set\_external\_check delay\_value -clock clock\_ref [-setup] [-hold] [-clock\_fall] input\_list

#### Arguments

#### delay\_value

Specifies the external setup or external hold delay in nanoseconds. This time represents the amount of time available inside the FPGA for the specified input after a clock edge.

-clock clock\_ref

Specifies the reference clock to which the specified external check is related. This is a mandatory argument.

-setup

Specifies that delay\_value refers to the setup check at the specified input. This is a mandatory argument if –hold is not used. You must specify either -setup or -hold option.

-clock\_fall

Specifies that the delay is relative to the falling edge of the reference clock. The default is the rising edge. *input\_list*

Provides a list of input ports in the current design to which delay\_value is assigned. If you need to specify more than one object, enclose the objects in braces ({}).

#### **Description**

The set\_external\_check command specifies the external setup and hold times on input ports relative to a clock edge. This usually represents a combinational path delay from the input port to the clock pin of a register internal to the current design. For in/out (bidirectional) ports, you can specify the path delays for both input and output modes. The tool uses external setup and external hold times for paths starting at primary inputs.

A clock is a singleton that represents the name of a defined clock constraint. This can be an object accessor that will refer to one clock. For example:

```

[get_clocks {system_clk}]

[get_clocks {sys*_clk}]

```

#### **Examples**

The following example sets an external setup check of 12 ns and an external hold check of 6 ns for port data\_in relative to the rising edge of CLK1:

```

set_external_check 12 -clock [get_clocks CLK1] -setup [get_ports data_in]

set_external_check 6 -clock [get_clocks CLK1] -hold [get_ports data_in]

```

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions

## set\_false\_path

SDC command; identifies paths that are considered false and excluded from the timing analysis.

set\_false\_path [-from from\_list] [-through through\_list] [-to to\_list]

#### Arguments

#### -from from\_list

Specifies a list of timing path starting points. A valid timing starting point is a clock, a primary input, an inout port, or a clock pin of a sequential cell.

-through through\_list

Specifies a list of pins, ports, cells, or nets through which the disabled paths must pass.

-to to\_list

Specifies a list of timing path ending points. A valid timing ending point is a clock, a primary output, an inout port, or a data pin of a sequential cell.

#### **Description**

The set\_false\_path command identifies specific timing paths as being false. The false timing paths are paths that do not propagate logic level changes. This constraint removes timing requirements on these false paths so that they are not considered during the timing analysis. The path starting points are the input ports or register clock pins, and the path ending points are the register data pins or output ports. This constraint disables setup and hold checking for the specified paths.

The false path information always takes precedence over multiple cycle path information and overrides maximum delay constraints. If more than one object is specified within one -through option, the path can pass through any objects.

#### **Examples**

The following example specifies all paths from clock pins of the registers in clock domain clk1 to data pins of a specific register in clock domain clk2 as false paths:

set\_false\_path -from [get\_clocks {clk1}] -to reg\_2:D

The following example specifies all paths through the pin U0/U1:Y to be false:

set\_false\_path -through U0/U1:Y

#### **Microsemi Implementation Specifics**

SDC accepts multiple -through options in a single constraint to specify paths that traverse multiple points in the design. In Microsemi design implementation, only one -through option is accepted.

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions Set False Path Constraint

## set\_input\_delay

SDC command; defines the arrival time of an input relative to a clock.

```

set_input_delay delay_value -clock clock_ref [-max] [-min] [-clock_fall] [-rise] [-fall]

[-add_delay] input_list

```

#### Arguments

delay\_value

Specifies the arrival time in nanoseconds that represents the amount of time for which the signal is available at the specified input after a clock edge.

-clock clock\_ref

Specifies the clock reference to which the specified input delay is related. This is a mandatory argument. If you do not specify -max or -min options, the tool assumes the maximum and minimum input delays to be equal.

-max

Specifies that delay\_value refers to the longest path arriving at the specified input. If you do not specify - max or -min options, the tool assumes maximum and minimum input delays to be equal.

Specifies that delay\_value refers to the shortest path arriving at the specified input. If you do not specify - max or -min options, the tool assumes maximum and minimum input delays to be equal.

-clock\_fall

Specifies that the delay is relative to the falling edge of the clock reference. The default is the rising edge.

Specifies that the delay is relative to a rising transition on the specified port(s). If -rise or -fall is not specified, then rising and falling delays are assumed to be equal.

-fall

Specifies that the delay is relative to a falling transition on the specified port(s). If -rise or -fall is not specified, then rising and falling delays are assumed to be equal.

-add\_delay

Specifies that this input delay constraint should be added to an existing constraint on the same port(s). The -add\_delay option is used to capture information on multiple paths with different clocks or clock edges leading to the same input port(s).

input\_list

Provides a list of input ports in the current design to which delay\_value is assigned. If you need to specify more than one object, enclose the objects in braces ({}).

#### **Description**

The set\_input\_delay command sets input path delays on input ports relative to a clock edge. This usually represents a combinational path delay from the clock pin of a register external to the current design. For in/out (bidirectional) ports, you can specify the path delays for both input and output modes. The tool adds input delay to path delay for paths starting at primary inputs.

A clock is a singleton that represents the name of a defined clock constraint. This can be:

- a single port name used as source for a clock constraint

- a single pin name used as source for a clock constraint; for instance reg1:CLK. This name can be hierarchical (for instance toplevel/block1/reg2:CLK)

- an object accessor that will refer to one clock: [get\_clocks {clk}]

#### Notes:

- The behavior of the -add\_delay option is identical to that of PrimeTime(TM)

- If, using the -add\_delay mechanism, multiple constraints are otherwise identical, except they specify different -max or -min values

- o the surviving -max constraint will be the maximum of the -max values

- o the surviving -min constraint will be the minimum of the -min values

#### **Examples**

The following example sets an input delay of 1.2ns for port data1 relative to the rising edge of CLK1: set\_input\_delay 1.2 -clock [get\_clocks CLK1] [get\_ports data1]

The following example sets a different maximum and minimum input delay for port IN1 relative to the falling edge of CLK2:

```

set_input_delay 1.0 -clock_fall -clock CLK2 -min {IN1}

set_input_delay 1.4 -clock_fall -clock CLK2 -max {IN1}

```

The next example is almost the same as the previous one, however, in this case, the user has specified - add\_delay, so both constraints will be honored:

set\_input\_delay 1.0 -clock CLK1 -max {IN1}

set\_input\_delay 1.4 -add\_delay -clock CLK2 -max {IN1}

The following example is more complex:

All constraints are for an input to port PAD1 relative to a rising edge clock CLK2. Each combination of {rise, -fall} x {-max, -min} generates an independent constraint. But the max rise delay of 5 and the max rise delay of 7 interfere with each other.For a -max option, the maximum value overrides all lower values. Thus the first constraint will be overridden and the max rise delay of 7 will survive.

set\_input\_delay 5 -max -rise -add\_delay [get\_clocks CLK2] [get\_ports PAD1] # will be

overridden

set\_input\_delay 3 -min -fall -add\_delay [get\_clocks CLK2] [get\_ports PAD1]

set\_input\_delay 3 -max -fall -add\_delay [get\_clocks CLK2] [get\_ports PAD1]

set\_input\_delay 7 -max -rise -add\_delay [get\_clocks CLK2] [get\_ports PAD1]

#### **Microsemi Implementation Specifics**

In SDC, the -clock is an optional argument that allows you to set input delay for combinational designs. Microsemi Implementation currently requires this argument.

#### See Also

Constraint Support by Family Constraint Entry Table SDC Syntax Conventions Set Input Delay

## set\_max\_delay (SDC)

SDC command; specifies the maximum delay for the timing paths.

set\_max\_delay delay\_value [-from from\_list] [-to to\_list]

#### Arguments

#### delay\_value

Specifies a floating point number in nanoseconds that represents the required maximum delay value for specified paths.

- If the path starting point is on a sequential device, the tool includes clock skew in the computed delay.

- If the path starting point has an input delay specified, the tool adds that delay value to the path delay.

- If the path ending point is on a sequential device, the tool includes clock skew and library setup time in the computed delay.

- If the ending point has an output delay specified, the tool adds that delay to the path delay.

#### -from from\_list

Specifies a list of timing path starting points. A valid timing starting point is a clock, a primary input, an inout port, or a clock pin of a sequential cell.

-to to\_list